- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

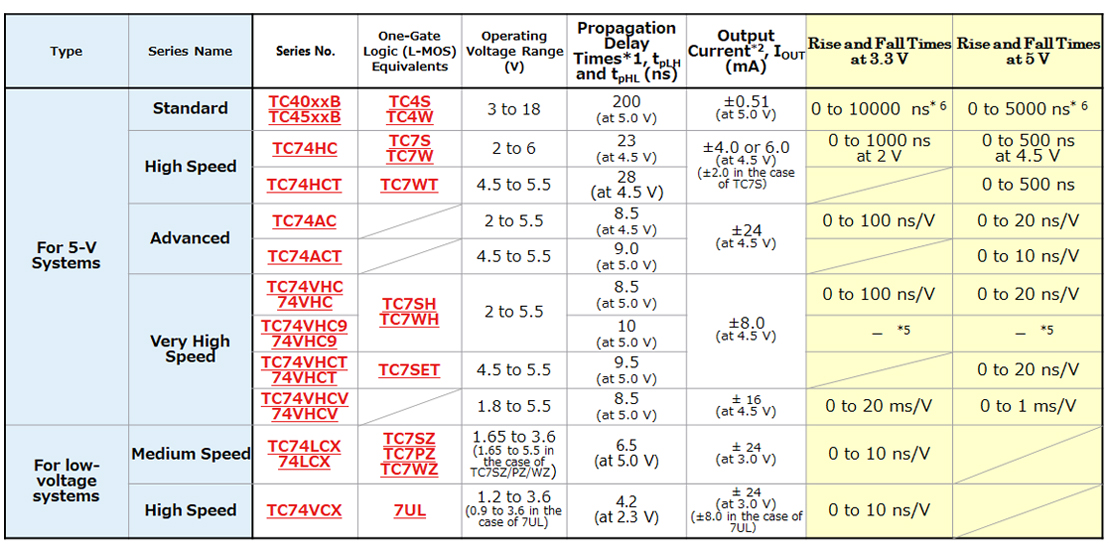

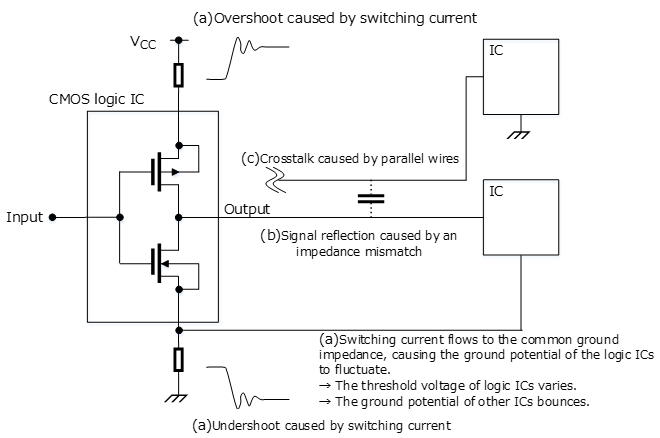

串扰的对策

串扰噪声是由并行延伸的两条相邻传输线路(分别称为干扰线路和受干扰线路)之间的电容或电感耦合引起的。关于串扰,应注意快速上升或下降的信号。当此类信号通过传输线路时,串扰噪声将在相邻的线路(受干扰线路)中产生并且在与干扰信号相同的方向和与干扰信号相反的方向上同时传播。

由于串扰传播的速度与干扰信号的速度相等,因此在与干扰信号相同方向上传播的串扰噪声(称为远端串扰)将显示为脉冲状噪声。

另一方面,当干扰信号沿线路传播时,沿相反方向传播的串扰噪声(称为近端串扰)保持恒定水平。

串扰噪声也沿着干扰线路传播,然后返回到受干扰线路。

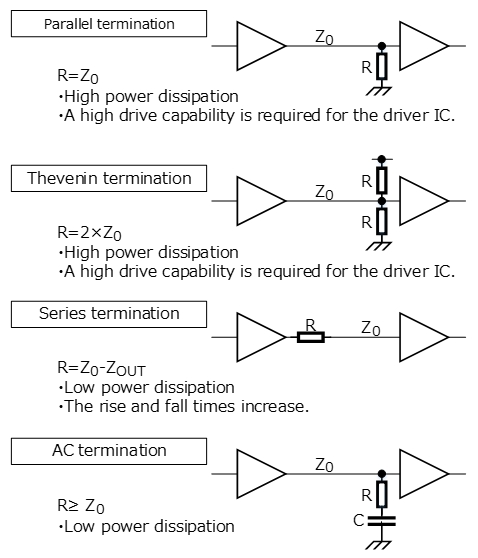

通常,可以按以下方法防止串扰。

串扰应对措施:

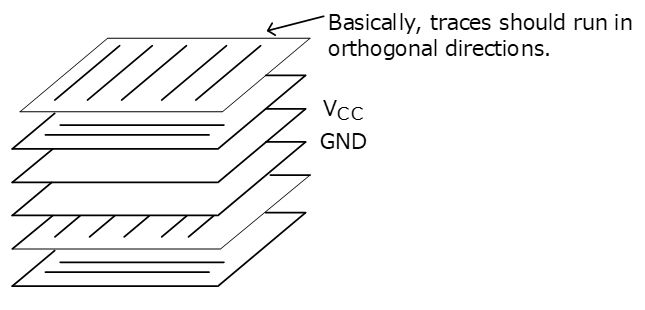

- 在并行走线之间添加接地走线。(或者使用多层电路板,其中低阻抗层(如VCC或GND层)位于信号层之间。)

- 减少并行运行的走线长度。

- 如果是多层电路板,在相互正交的交替层上走线(参见右侧图)。

- 增加走线之间的间距。

下图显示了沿30cm走线传播的典型串扰噪声水平。

这个例子显示的是近端串扰。如果受干扰走线的近端是接收端,则很容易受到串扰影响。