- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

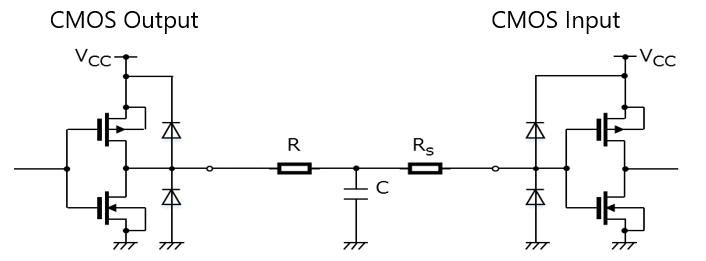

对于未使用输入引脚的处理

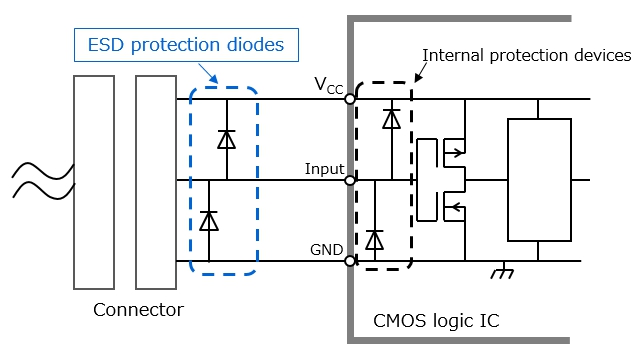

通常而言,所有未使用的输入端都应连接到VCC或GND。

可配置为输出端的双向总线缓冲器(如功能245)的任何引脚(如总线引脚)应通过上拉电阻器连接到VCC或通过下拉电阻器连接到GND。建议将缓冲器两端上拉或下拉至相同电位,以避免不必要的电流流动。但是,请保持总线引脚的输入引脚(如TC74VCXHxxx系列IC的输入引脚)保持为打开状态。即使采用典型的CMOS逻辑IC,在其电源接通时因寄生电容导致的大浪涌电流(几毫安量级)仍然会成为一个问题。为提高系统可靠性,防止器件损坏和其它故障,它们的输入端可通过上拉电阻器连接到VCC或通过下拉电阻器连接到GND。

由于CMOS逻辑具有非常高的输入阻抗,任何开放的输入端都可能由于周围电场的影响而导致错误的输出值。此外,直通电流可能会在VCC和GND的中点流动,从而导致电流增加,并且在最坏的情况下会导致器件损坏。

除非数据手册中另有说明,否则务必将这些注意事项应用至所有不具有总线保持能力的输入端。

- 1/16

- 下一篇