- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

3-2共模输入电压范围(CMVIN)和共模输入信号抑制比(CMRR)

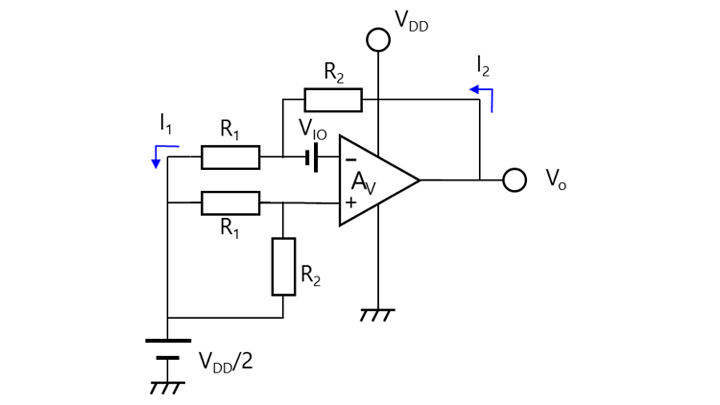

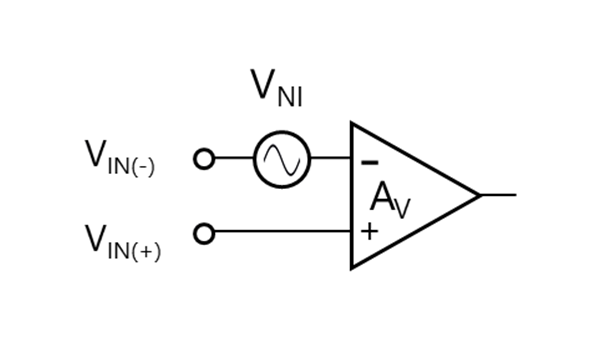

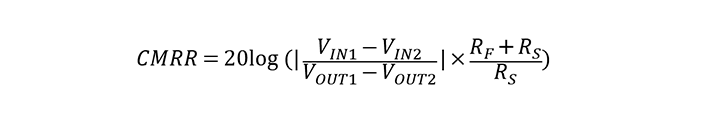

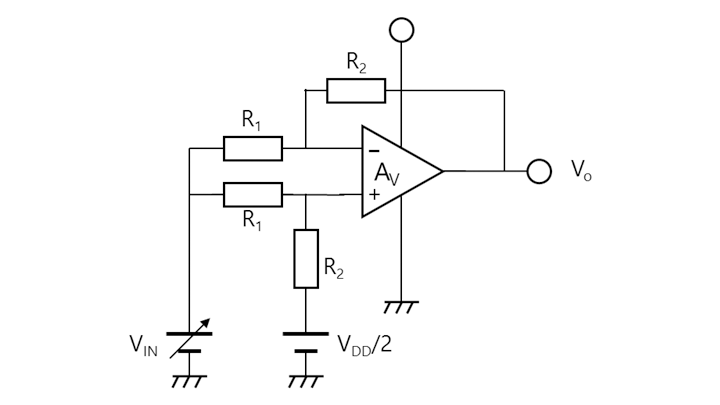

差分放大器的共模输入信号抑制比(CMRR)是一个指标,用于表示其抑制在VIN(-)端和VIN(+)端处具有相同振幅和相位的两个信号或噪声(共模噪声)的能力。用以下等式表示。共模输入信号抑制比的测试电路如图3-5所示。

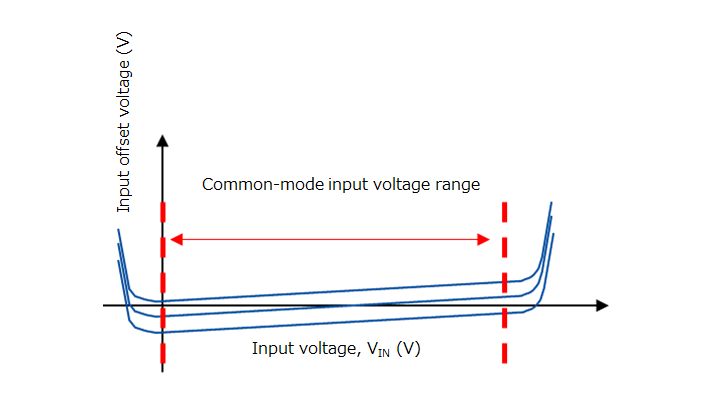

共模输入电压范围(CMVIN)是指在规定条件下满足规定CMRR的输入电压多范围。东芝的运算放大器数据表中列明了直流条件下的CMRR值。

其中,VIN1和VIN2分别表示CMVIN的最大值和最小值,VOUT1和VOUT2分别表示VIN1端和VIN2端的输出(VO)电压。

从图3-5可以看出,上一节介绍的输入补偿电压(VIO)是特殊条件(VIN=VDD/2)下的CMRR值。

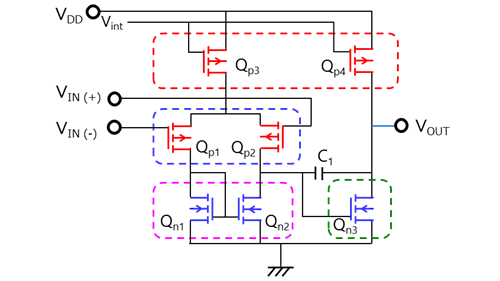

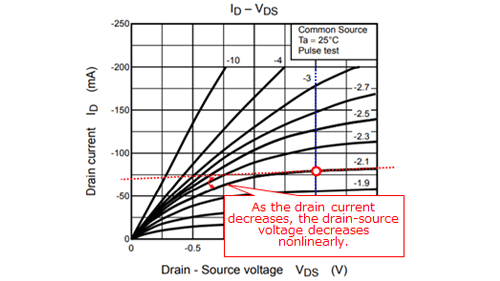

运算放大器的运行方式如第1.2节所述。如图3-6所示,典型运算放大器的差分输入对由P沟道MOSFET组成。随着VIN(+)电压和VIN(-)电压的升高,电流源中Qp3的漏源电压不断降低,导致流向差分输入对和电流镜的电流略微减小。图3-7显示了分立P沟道MOSFET的一个ID-VDS曲线示例。例如,假设最初VDS= -1.5V且ID=80mA。随着MOSFET的漏极电流减小,其漏源电压在饱和区呈非线性变化。

尽管运算放大器IC的内部器件的放置和制造方式保证了MOSFET的均匀性,但其在微观层面并不完全对称。此外,半导体芯片先贴装在封装的金属框架上,再焊接至印刷电路板。因此,施加于运算放大器IC的每个元件上的机械应力略有不同。这些因素导致差分输入对的P沟道MOSFET之间的阈值电压略有不同。因此,漏极电流的减小会导致其漏源电压发生不同的非线性变化。因此,如图3-8所示,输入补偿电压在共模输入电压范围内相对于输入电压(VIN)有一个斜率。因此,CMRR值是在最大和最小共模输入电压下计算得出的。