- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

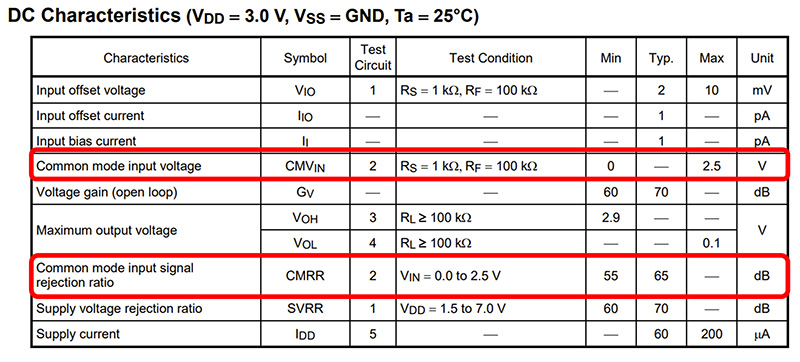

运算放大器的共模输入电压(CMVIN)是多少?

共模输入电压(CMVIN)在运算放大器数据表的电气特性中定义。该特性是当相同的信号施加到IN(+)和 IN(-)端子时,满足数据表的电气特性(CMRR等)的输入电压。

您可能认为共模信号永远不会施加至运算放大器。然而,运算放大器通常都与负反馈联用,这会导致IN(+)和IN(-)端子发生虚拟短路。这相当于向运算放大器施加共模信号(或电压差很小的信号)。

如果运算放大器的输入信号超出规定的共模输入电压范围,则差分放大器的增益会降低,从而导致输出信号失真。如果输入电压更高并超过最大额定差分输入电压,设备性能可能会下降或永久性损坏。

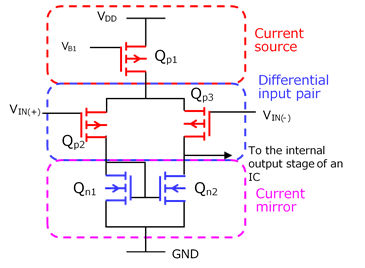

如图1所示,典型运算放大器的等效输入电路由差分输入对、电流源和电流镜像(有源负载)组成。由参考偏置(VB1)确定的电流源决定了流向差分输入对的电量。由于采用电流镜像电路,差分输入对基本上为Qn1和Qn2提供相同的电流。因此,VDS_qn2被传输至运算放大器的输出级。

假设VIN(+)和VIN(-)均降低了ΔV。这会导致Qp2和Qp3的源极-栅极电压(VSG)升高,进而导致其漏极电流增大。由于恒流源提供更多电流,Qp1(VDS_qp1)的漏源电压也升高。故Qp2和Qp3的源极-栅极电压(VSG)回落至此前的电平。

因此,当共模信号施加至运算放大器的差分输入对时,运算放大器的输出保持不变。

上述操作基于MOSFET均位于饱和区的假定。

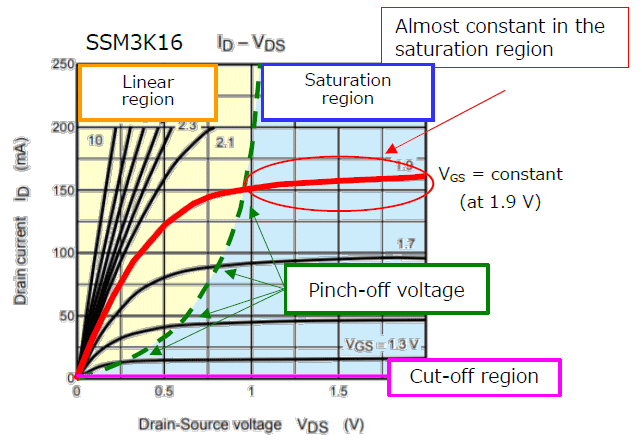

接下来,让我们考虑MOSFET进入饱和区的条件。图2显示了N沟道MOSFET(SSM3K16)的ID-VDS曲线。在饱和区的漏源电压(VDS)范围内,漏极电流几乎保持恒定(ΔV/ΔI=高阻抗)。为使MOSFET在饱和区工作,必须满足以下关系,其中Vth为漏极电流开始流动时的栅极-源极电压(VGS)。

VDS>VGS-Vth(1)

这里我们用一个VIN(+)相对于GND的公式来确定其最小值VIN(+)_min。

VIN(+)=VGS_qn1+VSD_qp2–VSG_qp2(2)

在VIN(+)_min条件下,Qp2的源极-漏极电压降至一个称为“夹断电压”的电平;此时,Qp2即将从饱和区转至线性区域。假设该电压为VSD_qp2_min,漏极电流开始流动时Qp2的阈值电压为Vth_qp2。随后,通过表示饱和条件的方程1得出以下方程:

VSD_qp2_min=VSG_qp2–Vth_Qp2(3)

将方程2代入方程3后得出:

VIN(+)_min=VGS_qn1–Vth_qp2(4)

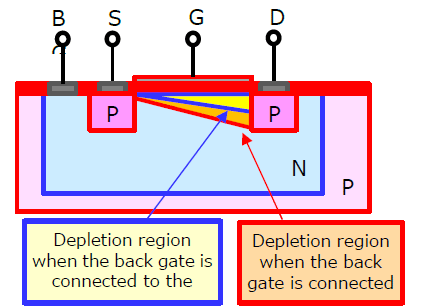

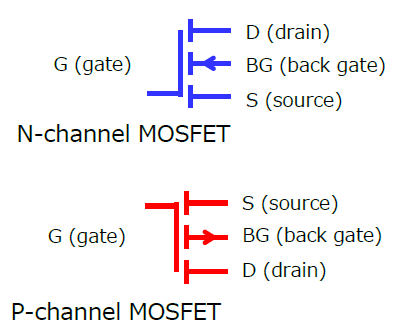

此前我们一直将MOSFET视为三端器件。然而,实际上还有一个称为“背栅”的端子。(如为典型的分立MOSFET,背栅在内部连接至源极端子。)

如为P沟道MOSFET,当背栅的电压高于源极时,耗尽区扩大,导致Vth升高。因此,当Qp2和Qp3的背栅连接至VDD时,公式4中的Vth值会变大。此外,通过工艺优化降低夹断电压(即公式4中的VGS_qn1),可将VIN(+)_min降至零。

接下来,我们用一个VIN(+)相对于VDD的公式来确定其最大值VIN(+)_max。

VIN(+)=VDD–VSD_qp1 – VSG_qp2 (5)

当施加VIN(+)时,Qp2的源漏电压(VSD_qp2)升高,导致VSD_qp1达到最小饱和电压(VSD_qp1_min)。如果VSD_qp2进一步升高,Qp1进入线性区域,导致漏极电流和增益下降。

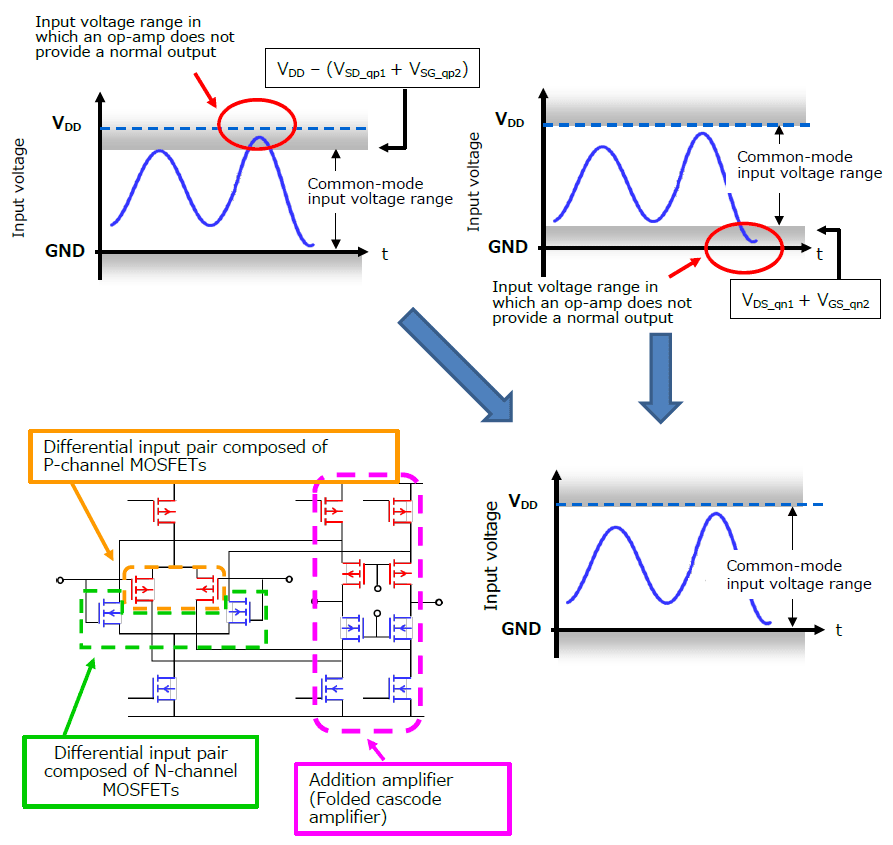

因此,具有由P沟道MOSFET组成的差分输入对的运算放大器可用于GND和VDD – (VSD_qp1 + VSG_qp2)之间的输入电压(共模输入电压),而具有由N沟道MOSFET组成的差分输入对的运算放大器可用于(VDS_qn1 + VGS_qn2)和VDD之间的输入电压。

不同于这些类型的运算放大器,轨对轨运算放大器的输入差分级由并联的N沟道MOSFET对和P沟道MOSFET对组成。轨对轨运算放大器的共模输入电压范围几乎涵盖了GND到VDD的整个范围。

相关链接

以下文档也包含相关信息: