- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

东芝发布采用新封装TO-247-4L(X)的第3代 SiC MOSFET

与目前主流的Si(硅)IGBT和MOSFET相比,使用SiC(碳化硅)的功率MOSFET不仅在低导通损耗和高温环境下工作方面表现出色,而且还通过高速开关降低应用损耗。

TO-247-4L(X)是东芝第3代SiC MOSFET产品的4端子型新封装,通过减少封装内源极线电感的影响,可以提高高速开关性能。这有助于降低服务器、不间断电源(UPS)和光伏逆变器等应用中的损耗。

以下是东芝新型TO-247-4L(X)(4端子型)封装与现有产品TO-247(3端子型)封装特性和开关损耗降低效果的对比。

TO-247-4L(X)封装的特性

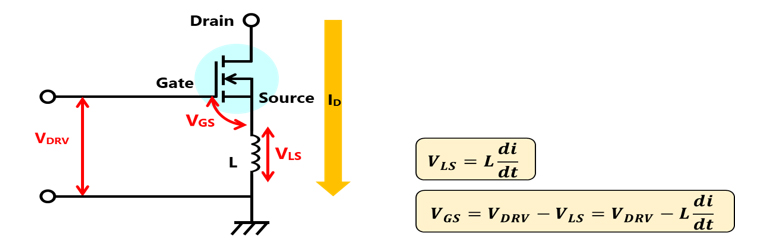

对于3端子型封装,如图1所示,当施加栅极驱动电压VDRV时,源极线的电感分量L和漏极电流ID的斜率dID/dt分量产生反电动势VLS。

因此,栅极驱动电压VDRV在反电动势VLS作用下减小。加在FET芯片栅极和源极之间的电压VGS是栅极驱动电压VDR减去反电动势VLS后的电压。这会导致SiC MOSFET开关速度下降。

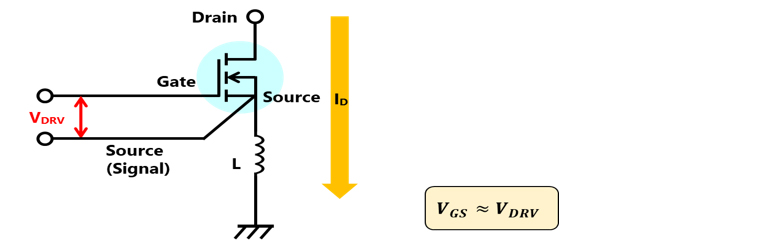

另一方面,如图2所示,4端子型封装通过将栅极驱动信号源端子连接到靠近FET芯片的位置,减少了反电动势VLS的影响。因此,在4端子型封装中,加在栅极和源极之间的电压VGS和栅极驱动电压VDRV 的值近似相同,与3端子型封装相比,提高了SiC MOSFET的开关速度。

开关损耗降低效果

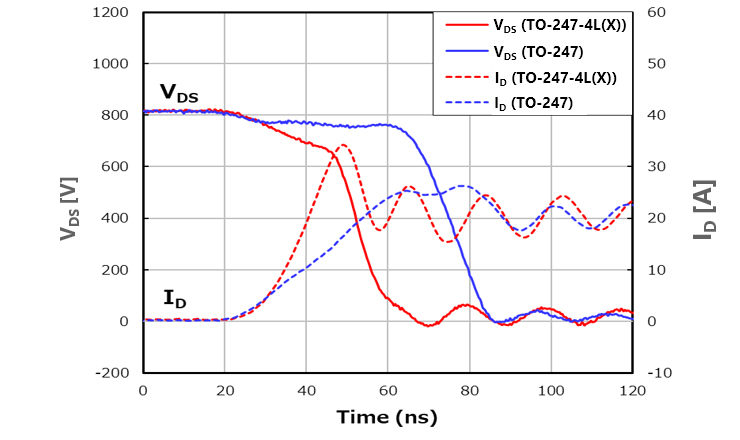

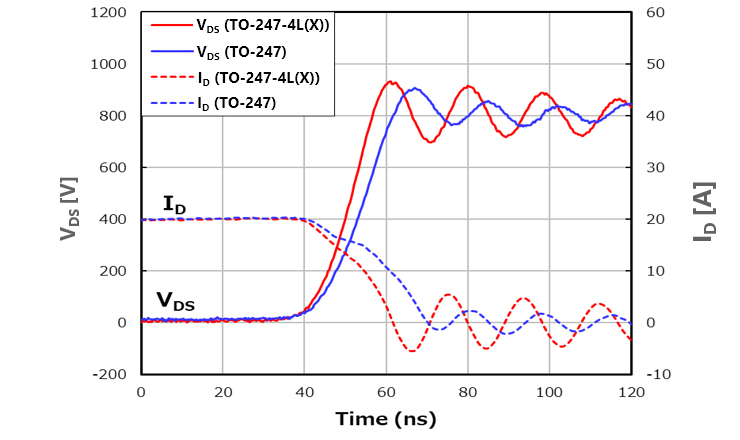

图3通过感性负载开关显示4端子型和3端子型封装的开通开关波形。开通时,4端子型漏极电流ID(红色虚线)比3端子型漏极电流ID(蓝色虚线)上升曲线更陡。

这是因为与3端子型相比,图2所示4端子型减小了源极线电感的影响,并抑制开关过程中栅极驱动电压下降。因此,4端子型开通速度比3端子型更快。

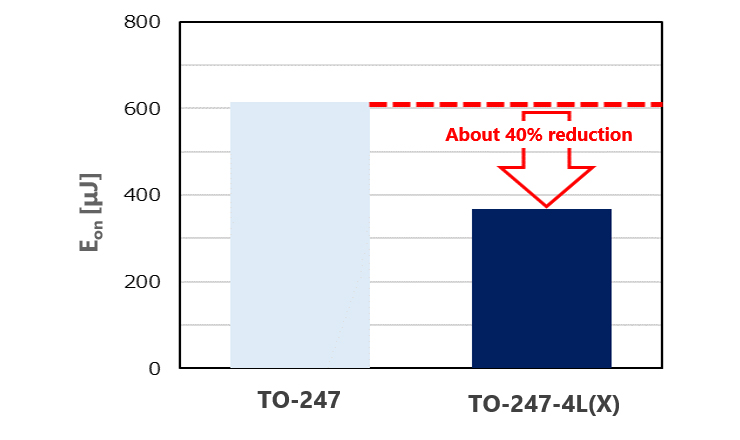

图4还显示4端子型和3端子型开通损耗Eon。4端子型开通损耗Eon比3端子型降低约40%。

测量条件

VDD=800V,VGS=18V/0V,ID=20A,Ta=25℃,L=100μH,Rg(外部栅极电阻)=4.7Ω

续流二极管使用每款产品源极和漏极之间的二极管

(东芝内部对比,2023年7月)

图5显示4端子型和3端子型感性负载开关下的关断开关波形 。关断时,4端子型漏极电流ID(红色虚线)比3端子型漏极电流ID(蓝色虚线)下降更快。换句话说,4端子型关断速度比3端子型快。

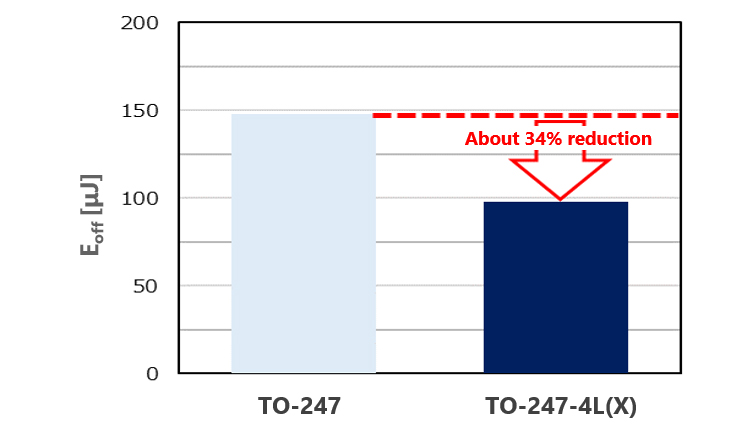

图6还显示4端子型和3端子型关断损耗Eoff。4端子型关断损耗Eoff比3端型关断损耗Eoff降低约34%。

测量条件

VDD=800V,VGS=18V/0V,ID=20A,Ta=25℃,L=100μH,Rg(外部栅极电阻)=4.7Ω

续流二极管使用每款产品源极和漏极之间的二极管。

(东芝内部对比,2023年7月)

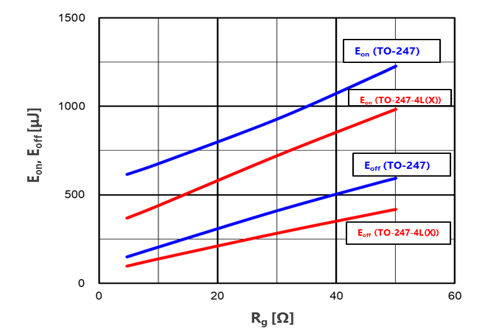

综上所述,图7显示4端子型和3端子型开通损耗Eon和关断损耗Eoff之间相对于外部栅极电阻Rg的关系。

- 随着外部栅极电阻Rg增加,4端子型和3端子型开通损耗Eon和关断损耗Eoff也增加。

- 4端子型开通损耗Eon和关断损耗Eoff小于3端子型。

测量条件

VDD=800V,VGS=18V/0V,ID=20A,Ta=25℃,L=100μH,Rg(外部栅极电阻)=4.7Ω

续流二极管使用每款产品源极和漏极之间的二极管。

(东芝内部对比,2023年6月)

MOSFET

相关信息

有关参考设计请访问:

参考设计

有关解决方案的相关信息,请访问:

服务器

不间断电源

LED照明

有关封装的详细信息,请访问:

封装

有关相关的新闻发布,请访问:

东芝推出用于工业设备的第3代碳化硅MOSFET,采用可降低开关损耗的4引脚封装

可提高碳化硅(SiC)MOSFET可靠性的东芝新器件结构问世

东芝的新型SiC MOSFET具有低导通电阻,可显著降低开关损耗

常见问题

有关常见问题,请访问:

MOSFET

仿真模型

您可以使用各种仿真模型。

*PSpice®是Cadence Design Systems, Inc.的注册商标

*LTspice®是仿真软件,是Analog Devices, Inc.的注册商标

*SIMetrix®是仿真软件,是SIMetrix Technologies Ltd.的注册商标

*本文提及的公司名称,产品名称和服务名称可能是其各自公司的商标。

Queries about purchasing, sampling and IC reliability

库存查询与购买

请输入3个以上字符

Through this website you are able to proceed to the website of our distributors ("Third Party Website") which is not under the control of Toshiba Corporation and its subsidiaries and affiliates (collectively "Toshiba"). The Third Party Website is made available to you as a convenience only and you agree to use the Third Party Website at your own risk. The link of the Third Party Website does not necessarily imply a recommendation or an endorsement by Toshiba of the Third Party Website. Please be aware that Toshiba is not responsible for any transaction done through the Third Party Website, and such transactions shall be subject to terms and conditions which may be provided in the Third Party Website.