- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

有助于降低应用中电源损耗的第3代SiC MOSFET

功率器件是管理和降低各种电子设备电能功耗以及实现碳中和社会的重要元器件。由于与比硅材料相比,碳化硅具有更高的电压和更低的损耗,因此碳化硅(SiC)被广泛视为下一代功率器件的材料。虽然碳化硅功率器件目前主要用于列车逆变器,但其具有极为广泛的应用前景,包括车辆电气化和工业设备小型化。然而,可靠性问题一直制约着SiC器件的普及和市场发展。

因此,东芝第3代SiC MOSFET具有以下特点。

- 内置肖特基势垒二极管(SBD)降低正向电压VDSF,抑制导通电阻RDS(ON)波动

- 降低代表导通损耗与开关损耗之间关系的性能指标RDS(ON)×Qgd

- 宽栅源额定电压VGSS范围

东芝第3代SiC MOSFET推出电压分别为650V和1200V的两款系列产品,可降低服务器、不间断电源(UPS)、光伏逆变器等各种应用的电源损耗。

东芝第3代SiC MOSFET具有以下特性。

第3代SiC MOSFET特性

1.内置肖特基势垒二极管 (SBD) 降低VDSF,抑制导通电阻RDS(ON)波动

东芝第3代SiC MOSFET内置与漏极和源极之间PN二极管并联的肖特基势垒二极管(SBD),可将反向导通正向电压VDSF降低至1.35V(典型值)。

SBD通电时,我们可抑制因SiC晶体缺陷扩散而引起的漏极和源极之间导通电阻RDS(ON) 的波动。

当从源极到漏极施加250A/cm2电流密度1000小时时,在体二极管通电作用下,无内置SBD的SiC MOSFET导通电阻RDS(ON)最大达42%。

然而内置SBD的第3代SiC MOSFET,由于SBD可以通电,我们能够将导通电阻RDS(ON) 的波动抑制在最大3%。

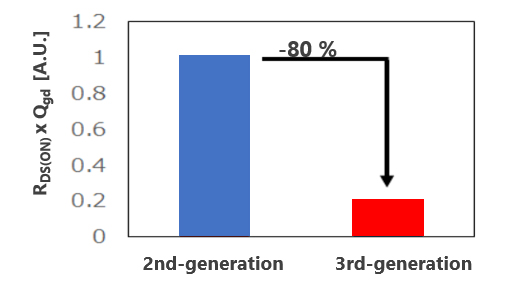

2.降低导通损耗和开关损耗性能指标:RDS(ON)×Qgd

通过优化单元结构,第3代SiC MOSFET代表导通损耗和开关损耗之间关系的性能指标RDS(ON)×Qgd比我们现有第2代产品降低80% [注]。

测量条件

RDS(ON):VGS=18V,ID = 20A,Ta=25℃

Qgd:VDD = 800V,VGS = 18V,ID=20A,Ta=25℃

(东芝内部对比,2022年5月)

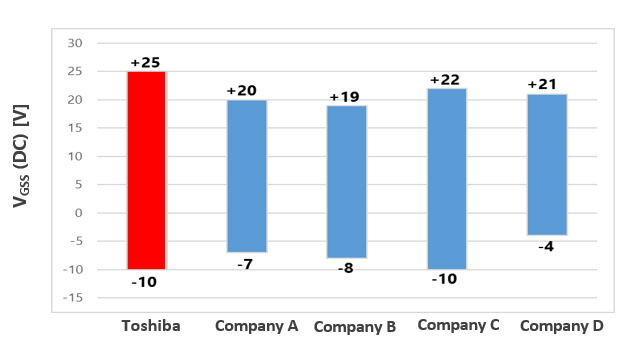

3.栅源电压VGSS范围宽

东芝第3代SiC MOSFET额定栅源电压为-10至25 V,比其他公司产品的电压范围宽,从而提高了驱动电压的裕量,有助于简化栅极驱动设计 (建议驱动电压:VGS_on=18V,VGS_off=0V)。

[注]RDS(ON)×Qgd设为1时,第2代SiC MOSFET中与1200V第3代SiC MOSFET对比。

SiC MOSFET

相关信息

常见问题

有关常见问题,请访问:

MOSFET

仿真模型

您可使用多种仿真模型。

*PSpice®是Cadence Design Systems, Inc.的注册商标

*LTspice®是仿真软件,是Analog Devices, Inc.的注册商标

*SIMetrix®是仿真软件,是SIMetrix Technologies Ltd.的注册商标

*本文提及的公司名称,产品名称和服务名称可能是其各自公司的商标。