- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

时序逻辑:移位寄存器

移位寄存器

示例:74VHC164,74VHC165

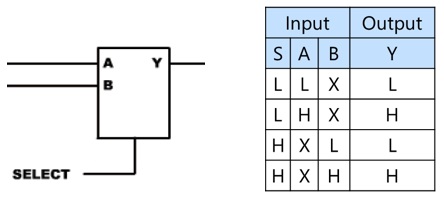

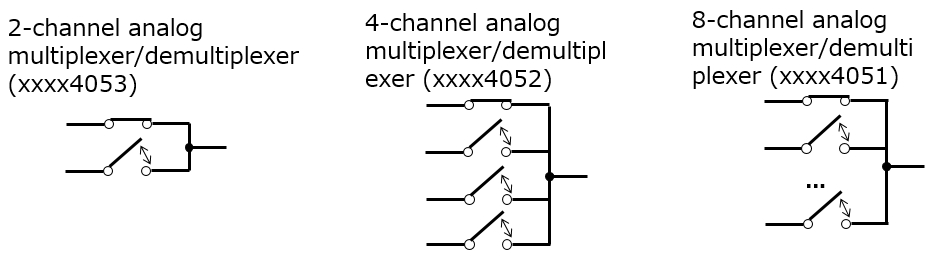

移位寄存器可以配置为串行-并行(SI-PO)或并行-串行(PI-SO)转换。

并行-串行转换有助于减少传输线的数量(即传输位宽度)。某些移位寄存器具有CLR输入,用于将内部状态初始化为已知值。

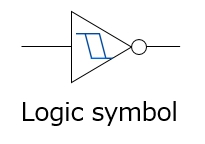

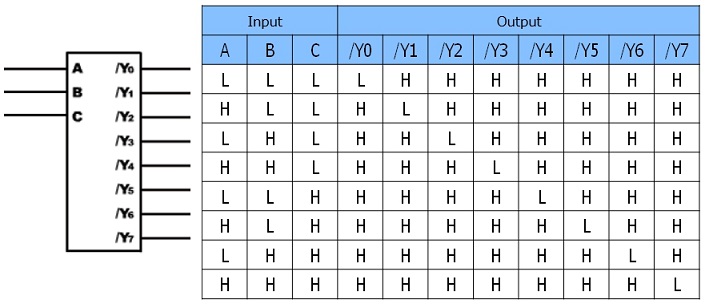

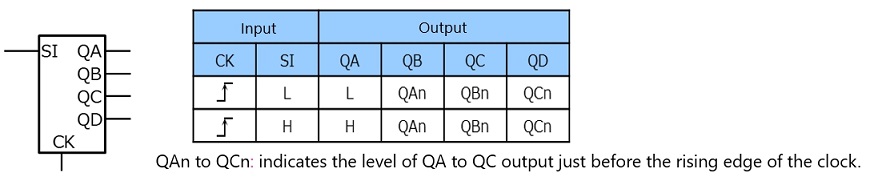

下面显示了移位寄存器的逻辑符号和真值表。

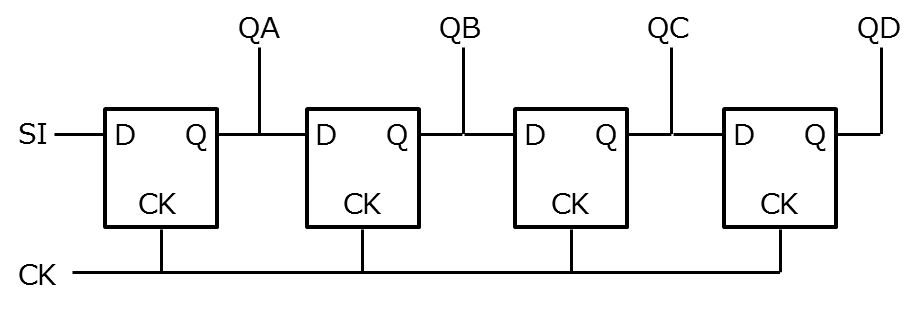

移位寄存器由多个触发器组成。

移位寄存器的操作

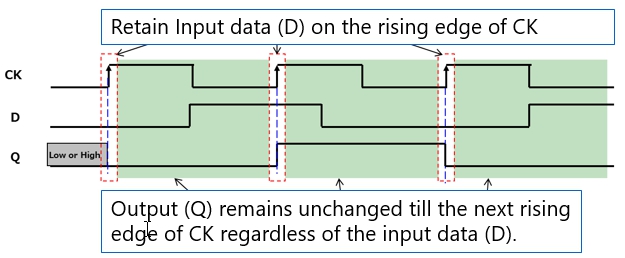

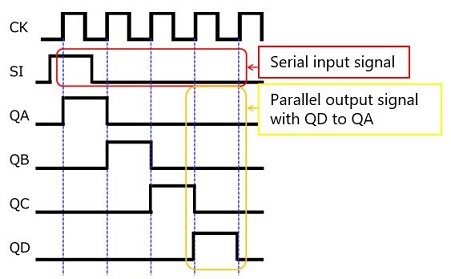

下面通过逻辑示意图和时序图说明移位寄存器的操作。移位寄存器由级联触发器组成,其中每个触发器的输出端(Q)连接至该链中下一个触发器的数据(D)输入端。

串行输入(SI)施加至第一触发器的数据(D)输入端。来自SI的数据在时钟(CK)的上升沿被锁存,并出现在QA处。利用四个时钟脉冲,来自SI的数据被传输到第四个触发器。结果,串行输入(SI)被转换为并行输出数据出现在QD、QC、QB和QA处。

移位寄存器的类型

74VHC164八位SI-PO移位寄存器的逻辑示意图

74VHC165八位PI-SO移位寄存器的逻辑示意图

有串行输入/并行输出和并行输入/串行输出移位寄存器。

- 上一篇

- 12/12