- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

第3代SiC肖特基势垒二极管

第3代 碳化硅(SiC)肖特基势垒二极管(SBD)产品线中,有7款产品采用TO-220-2L封装,5款产品采用DFN8×8封装。新产品采用了一种新型肖特基金属[注1],并搭载了第3代SiC SBD芯片,优化了第2代产品的结势垒肖特基(JBS)结构[注2]。因此,实现了业界领先的1.2V(典型值)低正向电压[注3],比上一代的1.45V(典型值)低17 %。第3代SiC SBD降低了主要用于开关电源的各种设备的功耗,同时提高了输出,新产品具有以下特性。

第3代SiC SBD特性

1、VF×Qc[注5]平衡改善

通过使用新型肖特基金属,改善了正向电压(VF)与总电容电荷(QC)之间的平衡。

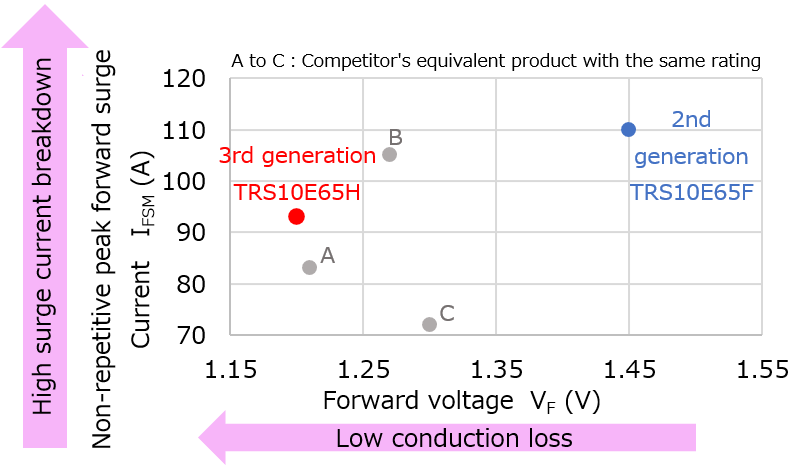

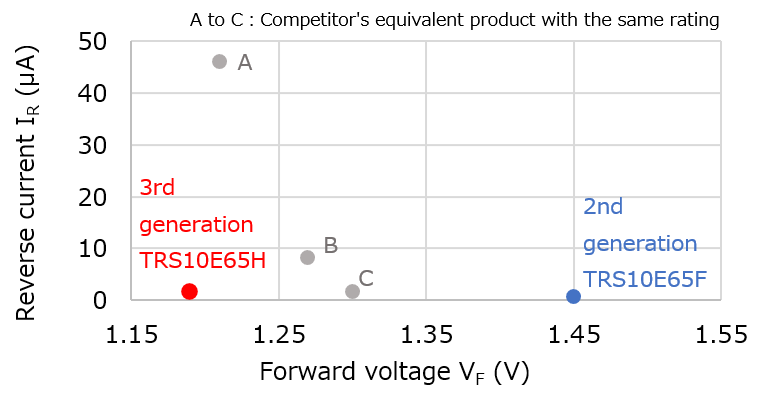

以下是使用我们第3代和第2代的650 V/10A/TO-220-2L额定产品与其他竞品具有代表性的样品[注3],以及我们第3代的1200 V/20 A/TO-247-2L额定产品与其他竞品具有代表性样品[注4]进行的对比评估结果。

![V<sub>F</sub> × Q<sub>C</sub> <sup>[note5]</sup> trade-off improvement](/content/dam/toshiba-ss-v3/master/en/semiconductor/product/diodes/articles/3rd-generation-sic-schottky-barrier-diode_features_1_en.png)

通过改进传统JBS结构,实现更高的非重复峰值正向浪涌电流(IFSM)。

3、低反向电流(漏电流)

通过采用JBS结构,即使低正向电压下,也可以获得低反向电流(IR)。

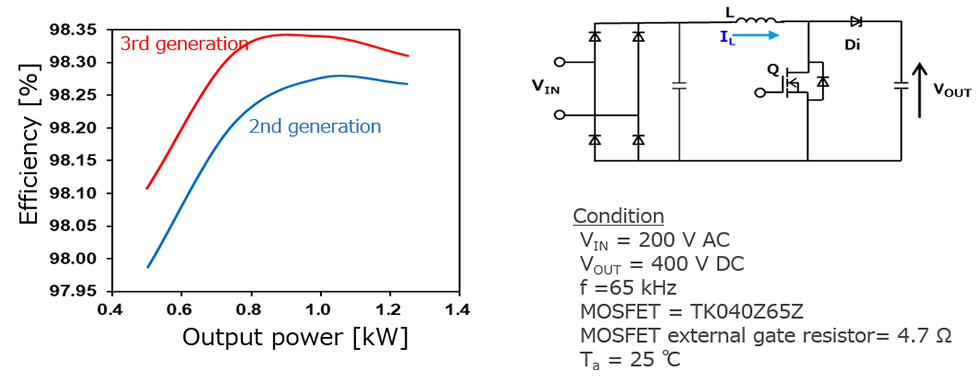

电源效率提升

在升压PFC测试电路中,在800W输出条件下,我们第3代SiC SBD的效率比第2代提高约0.1%。

(Toshiba internal comparison, as of November 2021)

[注1]肖特基势垒二极管采用金属和半导体结合。

[注2]JBS:一种p区嵌入半导体表面n区的结构。当反向偏压增大时,耗尽区在p区和n区之间延伸,从而减少漏电流。

[注3]截至2023年6月。

[注4]截至2024年9月。

[注5]VF×QC:正向电压(VF)×总电容电荷(QC),是SiC SBD损耗性能的指标。相同电流额定值器件比较时,VF×QC越小,损耗越低。

SiC肖特基势垒二极管

相关信息

关于各种应用,请参阅以下页面。

关于应用说明,请参阅以下页面。

FAQ

关于常见问题(FQA),请参阅以下页面

购买、样品、及IC可靠性查询

库存查询与购买

请输入3个以上字符

Through this website you are able to proceed to the website of our distributors ("Third Party Website") which is not under the control of Toshiba Corporation and its subsidiaries and affiliates (collectively "Toshiba"). The Third Party Website is made available to you as a convenience only and you agree to use the Third Party Website at your own risk. The link of the Third Party Website does not necessarily imply a recommendation or an endorsement by Toshiba of the Third Party Website. Please be aware that Toshiba is not responsible for any transaction done through the Third Party Website, and such transactions shall be subject to terms and conditions which may be provided in the Third Party Website.