- 型号 & 关键词搜索

- 交叉搜索

- 参数搜索

- 库存查询与购买

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

请输入3个以上字符 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

请输入3个以上字符

什么是通用逻辑IC的总线保持功能?

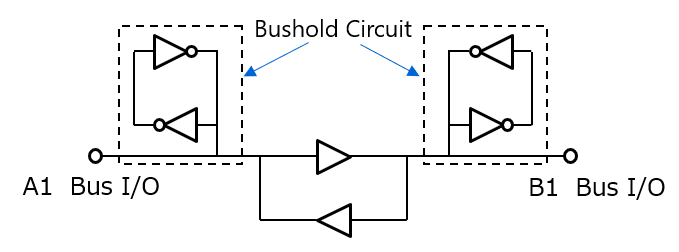

IC的数据输入端增设一个总线保持电路。总线保持电路由反馈环路中的两个反相器组成,只要输入引脚处于开路(即悬空)状态,总线保持电路就会将输入引脚的状态保持在其最后的已知状态。

下图显示了总线保持电路的等效电路。

在通用逻辑电路情况下,如果未使用的输入引脚保持开路或悬空状态,则其会呈现高阻态。通常,可通过连接外部上拉或下拉电阻防止出现这种情况,因为高阻态会导致输入电容逐渐被漏电流充电,最终同时导通P沟道和N沟道MOSFET,从而导致意外电流或异常振荡。

相反,总线保持电路采用连接到输入端的一个弱反馈门来保持最后的输入状态,直至下次改变状态。

因此,具有总线保持电路的IC无需外部上拉和下拉电阻。

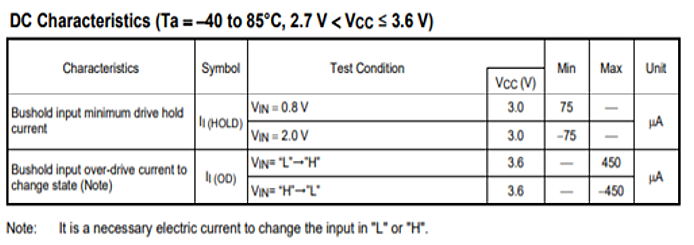

总线保持电路有两个电气特性:1)总线保持输入最小驱动保持电流(II (HOLD) ),规定总线保持电路可提供给器件或总线的最小电流;及2)总线保持输入过驱动电流以改变状态(II (OD) ),规定改变总线保持电路状态所需的最小过驱动电流。下面给出了数据表(表1)中所示的总线保持特性示例。

相关链接

以下文档也包含相关信息。