东芝研发出可降低沟槽型SiC MOSFET和半超结肖特基势垒二极管损耗的新技术

2025年6月9日

东芝电子元件及存储装置株式会社

日本川崎——东芝电子元件及存储装置株式会社(简称“东芝”)研发了一项创新技术,该技术可在增强沟槽型碳化硅(SiC)MOSFET[2]的UIS耐用性[3]的同时,显著降低其因导通电阻[1]而产生的损耗。同时,东芝还研发了半超结[4]肖特基势垒二极管(SJ-SBD),有效解决了高温下导通电阻增大的问题。这两项技术突破有望显著提升功率转换器件的可靠性与效率,尤其在电动汽车和可再生能源系统等领域。

功率半导体为所有电气设备供电并控制电力,对于节能和碳中和的实现至关重要。随着汽车的电气化和工业设备的微型化,预计对功率半导体的需求与日俱增。SiC MOSFET尤其如此。作为下一代器件,SiC MOSFET凭借其远超传统硅(Si)MOSFET的功率转换效率,正获得日益广泛的关注。其中,沟槽型SiC MOSFET以其独特的沟槽式栅极降低了导通电阻,SiC肖特基势垒二极管(SBD)则凭借金属半导体结实现了高效的功率转换,它们均广泛应用于电动汽车和可再生能源系统等高效功率转换领域。然而,这些应用场景通常伴随着高温工作环境,对可靠性和效率提升构成了严峻的考验。

沟槽型SiC MOSFET需要保护栅极氧化层免受高电场的影响。然而,由于电场保护结构[6]的UIS耐用性与接地电阻[5]之间的关系尚不明确,因此要同时实现高栅极氧化层可靠性与低导通电阻便极具挑战。

此外,尽管SiC SBD能承受比传统Si SBD更高的工作温度,但需要面对高温下电阻增加进而造成导通电阻变大的问题。

东芝研发了两项关键技术来解决这些问题。

1.提高沟槽型SiC MOSFET的UIS耐用性的技术

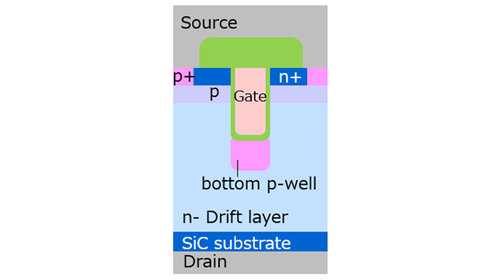

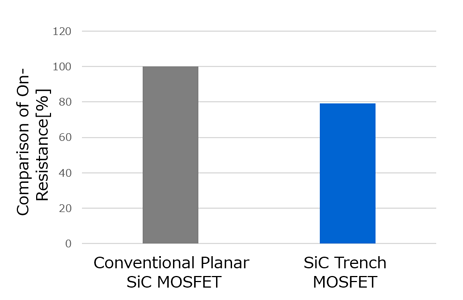

东芝研究发现,通过在沟槽型SiC MOSFET的沟槽中构建保护层(图1),并适当降低底部p阱的接地电阻,可提高UIS耐用性。这一发现明确了以往不确定的UIS耐用性与电场保护结构接地电阻之间的关系。与传统的平面型SiC MOSFET相比,东芝制作的沟槽型SiC MOSFET原型将导通电阻降低了约20%(图2)。

2.SiC SJ-SBD特性的改进

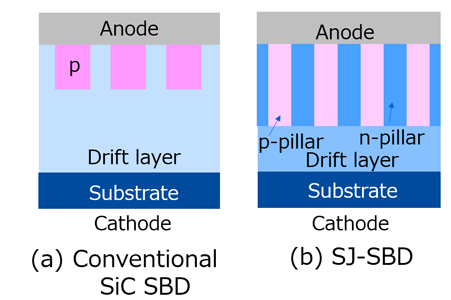

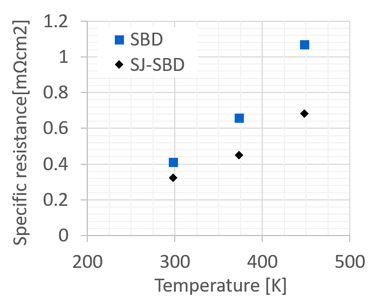

此外,东芝还研发了SiC SJ-SBD,通过在漂移层中置入基极[7]来抑制高温下电阻的增加(图3(b))。通过比较传统的SiC SBD(图3(a))和SiC SJ-SBD在不同温度下的导通电阻变化[8],东芝证实了SiC SJ-SBD在高温下具有更低的导通电阻(图4)。这是由于超级结(SJ)结构实现了平坦的电场分布并降低了导通电阻。与传统的SiC SBD相比,东芝研发的650V SiC SJ-SBD在175℃(448.15K)高温下将导通电阻降低了约35%。

这两项技术进一步降低了沟槽型SiC MOSFET和SiC SBD的损耗,提高了未来用于高效功率转换应用的器件的可靠性和效率,尤其是在电动汽车和可再生能源系统等领域。东芝将致力于进一步优化这些技术并加速其产业化进程。

在6月1日至5日于日本熊本举行的第37届国际功率半导体器件与IC研讨会(ISPSD 2025 ISPSD)上,东芝介绍了这些新技术的详细信息。此项成就基于新能源产业技术综合开发机构(NEDO)的项目补贴而取得。

[1]导通电阻是MOSFET工作时(导通)漏极与源极之间的电阻值。

[2]MOSFET:金属氧化物半导体场效应晶体管,这是一种具有三个电极的开关元件:栅极、漏极和源极。通过向栅极施加电压,它在漏极与源极之间切换导通和关断电流。

[3]UIS(非钳位感性开关)耐用性:功率器件承受开关过程中由感性负载引起的能量浪涌的能力。UIS耐用性越高,在恶劣工作条件下的耐久性和可靠性越高。

[4]超级结(SJ):一种在漂移层中交替形成p型基极和n型基极的结构。

[5]接地电阻:从底部p阱结构延伸至源极金属的总电阻。

[6]电场保护结构:沟槽型MOSFET中的一种结构特征,旨在减轻器件处于关断状态(即不导电)时对栅极氧化层的影响,有助于提高高压条件下栅极氧化层的可靠性。

[7]基极:在漂移层内形成的掺杂半导体材料的基极区域。在SJ-SBD中,p型和n型基极交替排列以构建超级结结构。

[8]SBD的导通电阻:根据电流-电压(I-V)曲线的斜率计算得出,并减去SiC衬底的电阻值。

*本文提及的公司名称,产品名称和服务名称可能是其各自公司的商标。

*本文档中的产品价格和规格、服务内容和联系方式等信息,在公告之日仍为最新信息,如有变更,恕不另行通知。