东芝开发出可减轻SiC功率模块中并联芯片间寄生振荡的技术,该技术具有最小栅极电阻,可支持高速开关

2024年7月26日

东芝电子元件及存储装置株式会社

东芝公司

东芝电子元件及存储装置株式会社和东芝公司(东芝集团)开发出了一种全新技术,即使在栅极电阻[1][2]比典型值小60%的情况下,也可以减轻碳化硅(SiC)MOSFET[3]的功率模块中并联芯片在开关操作期间所发生的寄生振荡[4]。该技术降低了功率模块的功耗,减轻了振荡,实现了高度可靠的开关操作。

推动实现碳中和的过程,在很大程度上刺激了众多产业领域(包括可再生能源、铁路和工业设备)不断提升对于可提高能源效率的技术要求。在这些产业领域,围绕SiC MOSFET为核心所构建的功率模块应用需要将成为支持高电压和大电流高速开关的解决方案,这对于功率转换器的小型化尤为重要,因为开关频率越高,将会导致较高的开关功率损耗率。

在功率模块中并联多个芯片会形成振荡电路,这是芯片之间的接线电感[5]及其寄生电容[6]所产生的结果。如果不加以应对,会降低模块的可靠性,而通常的应对方法是增加栅极电阻。但是这种方法会减缓开关速度,导致了需要考虑与开关损耗的权衡性。对于SiC MOSFET的功率模块执行高速开关,则需要采用另一种方法。

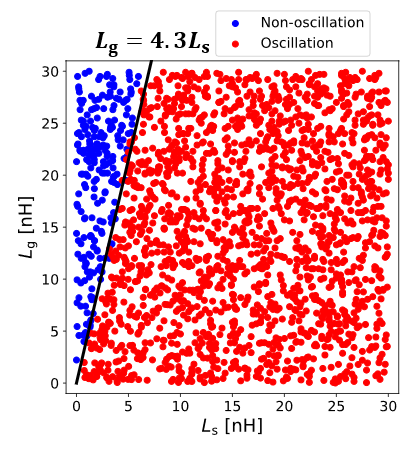

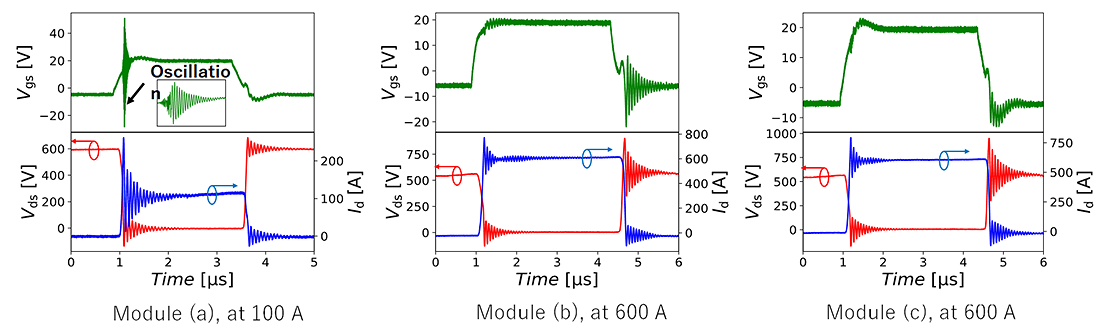

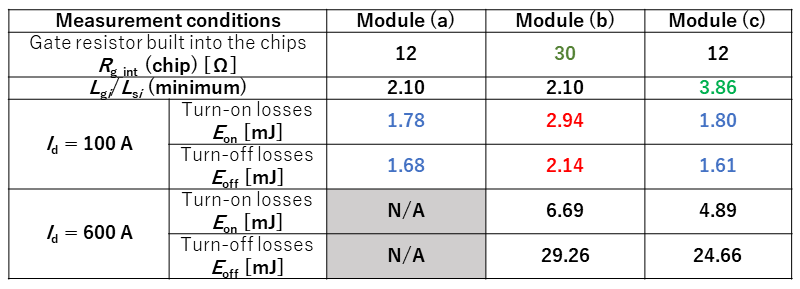

东芝集团使用功率模块的等效电路模型(图1)来确定触发寄生振荡的理论条件,然后开发了一种不太可能导致寄生振荡的布线布局。其具体方法是分析当Lg/Ls(并联芯片的栅极到栅极电感Lg和源极到源极电感Ls的比率)低于某个值时所产生的模拟寄生振荡(图2)。由于增加Lg/Ls是减轻寄生振荡的有效手段,东芝集团制造了具有不同Lg/Ls的原型模块,并且测量了开关速度。经证实,即使所使用的栅极电阻比另一种增加栅极电阻的方法所要求的减小了60%,增加Lg/Ls确实可以减轻振荡(图3)。

对于目前正在开发的功率模块,使用这种方法来抑制其中的振荡,即使使用最小的栅极电阻也不太可能引起寄生振荡,该方法在抑制振荡的同时实现了低功耗,并且提供了高度可靠的开关操作。东芝集团将继续改进模块,以尽早推出产品。东芝集团于2024年6月2日至6日在德国不来梅举行的第36届国际功率半导体器件和IC研讨会(ISPSD)上详细介绍了这项技术。

[1]相比于传统的东芝产品

[2]栅极电阻:MOSFET栅极中的电阻,作用是在施加栅极电压时限制电流流动。该值是决定器件开关特性和信号上升时间的重要因素。

[3]MOSFET:金属氧化物半导体场效应晶体管,它是具有三个电极(栅极、漏极和源极)的开关器件,通过施加栅极电压来开通和关断漏极和源极之间的电流。

[4]寄生振荡:MOSFET开关过程中发生的栅极电压振荡。多个MOSFET并联使用时,发生这种情况的可能性较大。

[5]接线电感:导体固有的工作特性:对于电流变化的抵抗力。这是由于所感应的电动势(电压)与导体周围磁场所引起的电流变化是相反的。

[6]寄生电容:电子电路中的元件或接线之间所不期望的电容。它可以像电容器一样存储电荷,从而会影响电路的运行。在高速电路中,它会导致信号延迟和失真。

Vgs:栅源电压,Vds:漏源电压,Id:漏极电流

*本文提及的公司名称,产品名称和服务名称可能是其各自公司的商标。

*本文档中的产品价格和规格、服务内容和联系方式等信息,在公告之日仍为最新信息,如有变更,恕不另行通知。