东芝成功在降低SBD嵌入式SiC MOSFET的导通电阻的同时确保了其可靠性和短路耐受性

2024年6月3日

东芝电子元件及存储装置株式会社

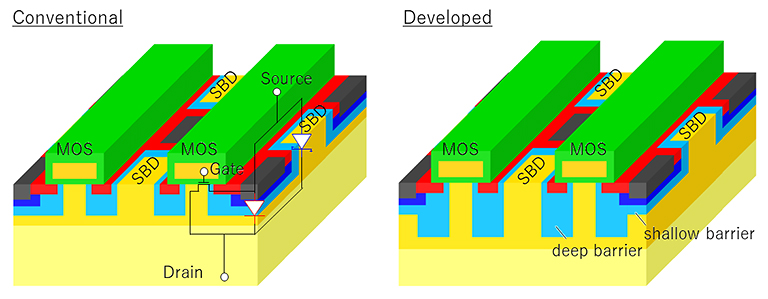

日本川崎——东芝电子元件及存储装置株式会社(简称“东芝”)现已开发出一款肖特基势垒二极管(SBD)[1]嵌入式金属氧化物半导体场效应晶体管(MOSFET)[2]。该产品显著改进当前的器件结构的同时确保了高可靠性和短路耐受性[3]。成功的设计升级是在器件结构中引入了不同深度的一种势垒结构[4]。这种势垒结构不仅可确保集成SBD反向导通操作的可靠性[5],同时还可抑制SBD部分的漏电流,这种漏电流会在短路期间造成器件损坏[6]。通过利用新技术和优化器件结构,新型MOSFET实现了更低的导通电阻[7](RDS(ON)),比现有结构降低了约26%[3]。.

功率半导体在电力供应和控制领域发挥着核心作用,可降低各种电子设备的功耗,是实现碳中和的一种重要工具。随着车辆电气化和工业设备小型化趋势的发展,预计功率半导体需求将继续扩大。在此背景下,SiC MOSFET被视为下一代功率半导体。与Si MOSFET相比,SiC MOSFET的电能转换效率更高,近年来其应用范围迅速扩大。然而,SiC MOSFET存在可靠性问题:由于反向导通操作,RDS(ON)会增大。东芝现已开发出一种内置SBD的SiC MOSFET,可在反向导通条件下工作,并且不会增大RDS(ON)。

减小SiC MOSFET RDS(ON)的同时,会导致短路运行期间过量电流流过MOSFET部分[6],从而降低短路运行的耐久性。然而,如果为提高反向导通操作的可靠性而增强嵌入式SBD的导通性,则会加剧短路运行期间的电流泄漏,这也会降低短路运行的耐久性。引入深势垒结构可抑制短路运行期间MOSFET的过大电流和SBD的漏电流,但它也会阻碍SBD的电流流动,引发对二极管导电可靠性下降的担忧。.

因此,东芝考虑将势垒结构分为浅区和深区。深势垒区可成功抑制短路运行期间来自MOSFET部分的过大电流,并减少SBD电流泄漏,而浅势垒区则可有效扩散来自SBD的电流且不受势垒阻碍。这种方法在保持反向导通操作期间出色可靠性的同时,提高了短路运行期间的耐受性。自2023年12月以来,东芝已向一些客户提供了采用新技术的嵌入式SBD的SiC MOSFET测试样品用以评估,进一步提高性能。

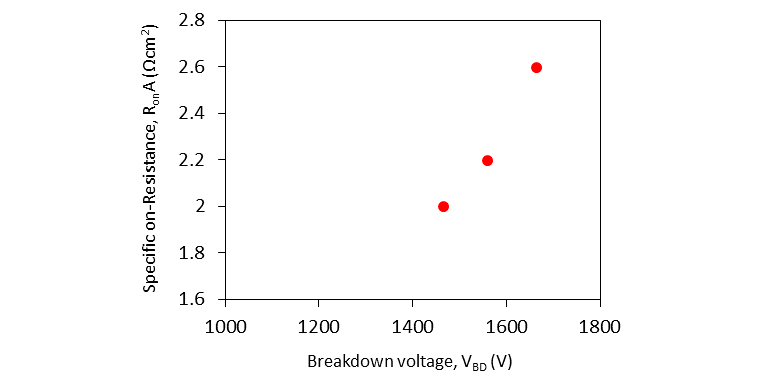

东芝利用其新设计技术并优化器件结构,开发出了一种原型1.2kV级SBD集成式MOSFET。该MOSFET实现了低至2.0mΩcm2的RDS(ON),与现有结构相比,导通电阻降低了约26%[3](图2)。第36届国际功率半导体器件与IC国际会议(ISPSD 2024)将于6月2日至6日在德国不莱梅举行,东芝将于6月3日(当地时间)出席该会议并介绍该技术的详细信息。

[1]SBD:肖特基势垒二极管,一种整流元件,可使电流沿一个方向流动,连接在金属和n型半导体单晶内。

[2]MOSFET:金属氧化物半导体场效应晶体管,这是一种具有三个电极的开关元件:栅极、漏极和源极。通过向栅极施加电压,它在漏极与源极之间切换导通和关断电流。

[3]具有棋盘格图案的SBD分布的器件结构,于2022年12月9日发布。

东芝开发了具有低导通电阻和高可靠性的肖特基势垒二极管内嵌式SiC MOSFE

[4]势垒结构:用于控制由于高压引起的高电场的器件结构元素。它对器件性能有很大影响。

[5]反向导通操作:由于电路中的电流回流,电流从MOSFET的源极流向漏极的一种操作。

[6]短路运行:与正常开关操作期间的短时间导通相比,这是在控制电路故障等异常模式下会发生长时间导通的一种现象。要求具有在一定持续时间的短路运行下不会失效的耐受性。

[7]导通电阻是MOSFET工作时(导通)漏极与源极之间的电阻值。

*本文提及的公司名称、产品名称和服务名称可能是其各自公司的商标。

*本文件中所含信息,包括产品价格和产品规格、服务内容及联系方式,仅于公告当日有效,如有更改,恕不另行通知。