东芝与日本半导体展示新方法,可以同时优化车载模拟IC里高压LDMOS的ESD耐受性和出力效率

2021年6月11日

东芝电子元件及存储装置株式会社

日本半导体公司

东京——东芝电子元件及存储装置株式会社(以下简称“东芝”)和日本半导体公司(以下简称“日本半导体”)共同展示了一种新方法,可同时改善高压横向双扩散 MOS(Laterally Double Diffused MOS,LDMOS)的可靠性与性能。LDMOS是电机控制驱动IC等各种车载应用模拟IC的核心部件。随着汽车电气化的进展,包括ADAS系统(高级驾驶员辅助系统)的广泛部署,东芝和日本半导体将根据所需电压提供改进的LDMOS单元设计。

在IEEE主办的线上2021年功率半导体器件和IC国际研讨会(ISPSD 2021)上,对该成果的详细信息进行了报告。

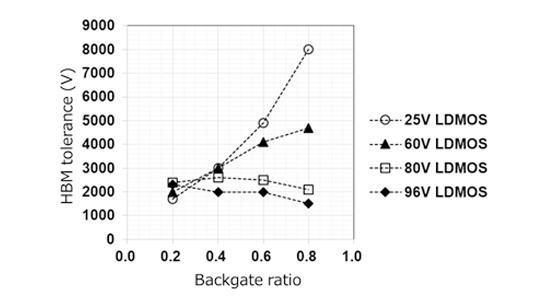

在LDMOS设计时,一直要在可靠性与性能之间进行权衡。众所周知,提高背栅比*1来抑制横向寄生双极效应*2,可以改善ESD(静电放电)耐受性。比如采用人体模型(HBM)测量。然而,背栅比的增加也会使导通电阻增加,从而导致性能降低。到目前为止,LDMOS的设计者不得不在HBM耐受性与更高导通电阻之间进行权衡。

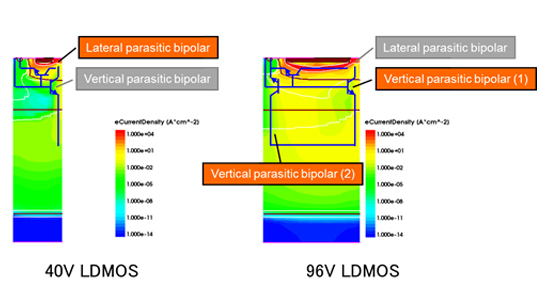

东芝和日本半导体公司对LDMOS中的HBM耐受性进行评估发现,即使增加背栅率,在80V以上时导通电阻也不会增加。他们在2D TCAD仿真中发现,这是因为垂直寄生双极效应与横向寄生效应作用同时出现。由于该现象,设计者在设置HBM和背栅比参数时将拥有更大的自由度。

将该发现与东芝公司的单元参数优化设计(不包括背栅比)的技术*3相结合,东芝和日本半导体提出了一种可提高HBM耐受性并抑制80V及以上LDMOS导通电阻的方法。从而使得LDMOS具有HBM耐受性,且与背栅比无关。该方法适用于应用在发动机、转向系统等车载系统的器件,并将有助于提高可靠性和出力效率。

东芝拥有适用于各种应用的各种电压的LDMOS产品线,并且正在开发集成嵌入式eNVM(非易失性存储器)和高压模拟IC的第五代工艺技术。

东芝电子元件及存储装置株式会社和日本半导体公司致力于半导体工艺的研发,为降低功耗和提高可靠性做贡献。

HBM耐受性与背栅比之间的关系(东芝测试结果)

低压和高压LDMOS HBM测试下的寄生双极效应的差异(东芝测试结果)

在低压LDMOS中,横向寄生双极效应占主导地位。

在高压LDMOS中,垂直寄生双极效应占主导地位。

注

[1]背栅比:东芝LDMOS沿其宽度方向有交替的源极和背栅。背栅比是指背栅的总宽度与源极和背栅的总宽度之比。

[2]寄生双极效应:在HBM测试中观察到的一个现象;当正电压施加到LDMOS漏极时,PN结处会发生碰撞电离。漏极/主体/源极为寄生双极晶体管的集电极/基极/发射极,集电极电流流动。集电极电流集中在硅表面,晶格温度升高,导致器件被损坏。

[3]在ISPSD 2017上报告了该技术的详细信息。(标题:“HBM robustness optimization of fully isolated Nch-LDMOS for negative input voltage using unique index parameter”)

客户问询:

日本总部

中国地区

*本文提及的公司名称,产品名称和服务名称可能是其各自公司的商标。

*本文档中的产品价格和规格、服务内容和联系方式等信息,在公告之日仍为最新信息,如有变更,恕不另行通知。