东芝和日本半导体株式会社研发了具有高耐受性的LDMOS单元阵列,从而可以限制负载流子注入和静电放电的影响

2020年09月23日

东芝电子元件及存储装置株式会社

日本半导体株式会社

东京—东芝电子元件及存储装置株式会社(“东芝”)及其制造生产子公司日本半导体株式会社(Japan Semiconductor Corporation)研发了对于负载流子注入和静电放电(ESD)活动具有高度耐受性的横向双扩散MOS(LDMOS)单元阵列设计。与以往的参考结构相比,新设计所容许负注入电流的耐受性提高了40%。[1]

详情可参见由IEEE主办并在线举行的2020年功率半导体器件和IC国际研讨会(ISPSD 2020)报告。

A模拟IC对于各种消费类电子产品、工业设备和车载设备来说至关重要不可或缺。用在模拟IC中的LDMOS必须具有高度的可靠性,而负载流子注入的耐受性则又是其非常重要的特性之一。当负载流子注入开关器件(注入器)漏极时,寄生双极晶体管导通,少数载流子注入衬底。这一现象会对周围的器件产生不良影响。此外,还要求对导致损坏或故障的ESD活动、静电的耐受性有着较高要求。为提高对于负载流子注入和ESD活动的耐受性,器件可按一定距离分开或在器件之间插入N保护环,但这两种方法都会增加芯片尺寸和生产成本。

当注入器中N保护环电阻较小时负载流子注入的耐受性较高,东芝和日本半导体株式会社正是基于这一实际情况,研究了多个LDMOS阵列设计中负载流子注入和ESD活动的耐受性。

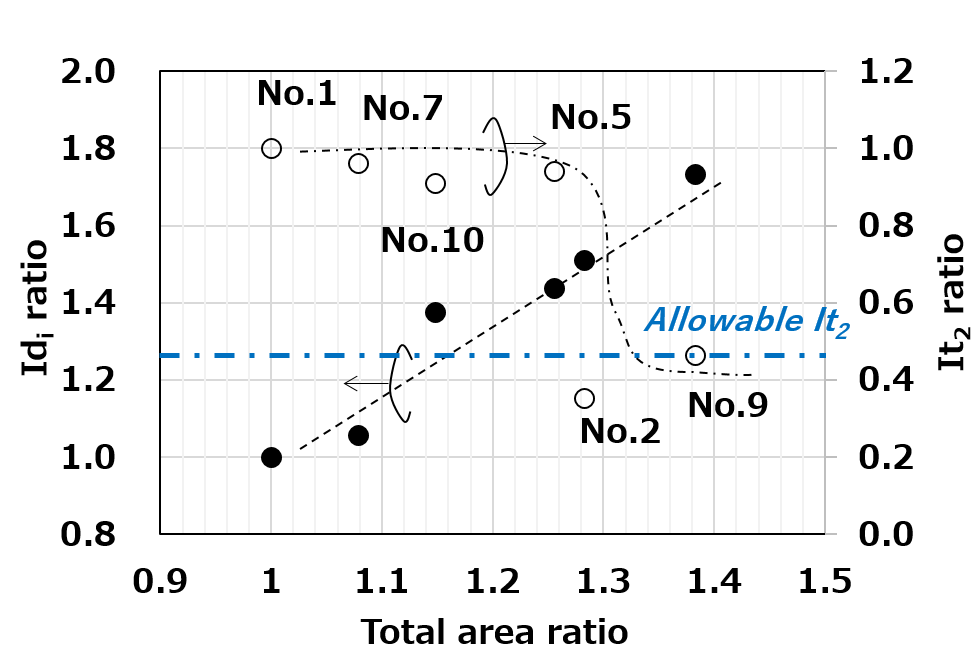

两家公司发现,将N-保护环区域的宽度除以划分阵列的最大面积所得到的参数与负载流子注入的耐受性之间存在正相关。他们还发现该参数与ESD活动的耐受性之间存在负相关。这就表明了负载流子注入和ESD活动的耐受性之间存在折衷关系。这种折衷关系表明,公司的10号设计具有最佳的布局,因为它相对于参考结构增加了40%的负注入电流的耐受性,ESD活动的耐受性下降被抑制到仅为9%,而总面积增加不超过15%。 [1]

两家公司可以将这项新技术应用于已在2019年投入量产的第四代LDMOS产品中。

东芝拥有一系列适用于各种电压和应用的LDMOS,并正在研发第五代LDMOS。它将集成嵌入式非易失性存储器(eNVM)和高压模拟IC。

东芝电子元件及存储装置株式会社和日本半导体株式会社正致力于半导体工艺的研发以实现低功耗和最大限度减小器件尺寸的目标。

N沟道LDMOS横截面图

测量的LDMOS结构(3600个单元)

深粉色区域表示N-保护环,浅粉色区域表示内部单元。

负载流子注入与ESD活动的耐受性与总面积比之间的关系

Idi:负载流子注入的耐受性

It2:ESD的耐受性

这两个值都由1号值作为参考进行规一化。

注:

[1] 最佳结构(10号)和参考结构(1号)对于负载流子注入的耐受性比较。

客户问询:

日本总部

系统器件销售&市场部

销售促进组

电话:+81-3-3457-3332

中国地区

系统LSI市场部(System LSI Marketing)

电话:021-6090-0610/深圳:0755-3661-5889

* 本文档中的产品价格和规格、服务内容和联系方式等信息,在公告之日仍为最新信息,如有变更,恕不另行通知。

* 本文提及的公司名称,产品名称和服务名称可能是其各自公司的商标。