可提高碳化硅(SiC)MOSFET可靠性的东芝新器件结构问世

2020年07月30日

东芝电子元件及存储装置株式会社

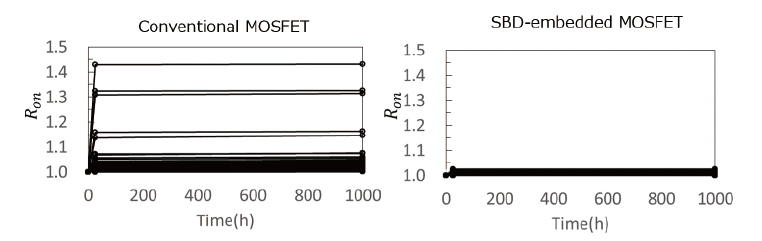

东京——东芝电子元件及存储装置株式会社(简称“东芝”)今日宣布了一种可提高碳化硅(SiC)MOSFET[1]可靠性的新器件结构问世。相较于东芝的典型器件结构,MOSFET内嵌的肖特基势垒二极管[2](SBD)可在抑制导通电阻增大的同时,将器件结构的可靠性提高10倍以上[3]。

功率器件是降低车辆以及工业设备和其它电气设备能耗的重要元器件,而碳化硅相较于有机硅可进一步提高电压并降低损耗,因此业界普遍预期碳化硅将成为新一代的功率器件材料。虽然碳化硅材质的功率器件目前主要用于列车逆变器,但其今后的应用领域非常广泛,包括用于工业设备的各种光伏发电系统(PPS)和电源管理系统(PMS)。

目前可靠性问题是碳化硅器件使用和市场增长的拦路虎,问题之一涉及位于功率MOSFET的电源与漏极之间的PN结二极管[4]。PN结二极管的外施电压使其带电,造成导通电阻变化,进而有损于器件的可靠性。东芝新推出的肖特基势垒二极管(SBD)内嵌式MOSFET器件结构正是此问题的克星。

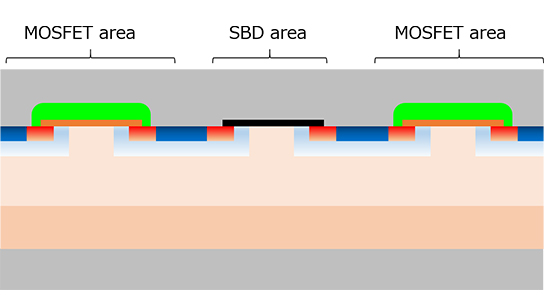

该新结构中有一个与电池单元内的PN结二极管并联的肖特基势垒二极管,可防止PN结二极管带电。相较于PN结二极管,内嵌肖特基势垒二极管的通态电压更低,因此电流会通过内嵌肖特基势垒二极管,进而抑制导通电阻变化和MOSFET可靠性下降等问题。

内嵌肖特基势垒二极管的MOSFET现已投入实际应用,但仅限于3.3kV器件等高压产品;内嵌肖特基势垒二极管通常会使导通电阻升高至仅高压产品能承受的一个电压水平。东芝在调整各个器件参数后发现MOSFET中肖特基势垒二极管的面积比是抑制导通电阻增大的关键因素。东芝通过优化肖特基势垒二极管的这一比例,实现了1.2kV级高可靠型碳化硅(SiC)MOSFET。

东芝计划自今年八月下旬起利用这项新技术开始量产1.2kV级碳化硅(SiC)MOSFET。

2020年7月德国纽伦堡国际电力电子系统及元器件展览会(PCIM Europe)上报道了该新器件结构的详情,这是一次在线举办的国际性功率半导体展会。

注

[1] MOSFET:金属氧化物半导体场效应晶体管

[2] 肖特基势垒二极管(SBD):通过半导体与金属接合形成的一种半导体二极管

[3] 东芝规定当以250A/cm2的电流密度通过电源向某器件的漏极通电1,000小时后才出现导通电阻变化,即视为该器件可靠。东芝的典型MOSFET的导通电阻变化率高达43%,而肖特基势垒二极管(SBD)内嵌式MOSFET的这一变化率仅为3%。

[4] PN结二极管:通过在电源与漏极之间设置PN结形成的一种二极管

肖特基势垒二极管(SBD)内嵌式MOSFET的结构

肖特基势垒二极管(SBD)内嵌式MOSFET可抑制导通电阻变化

客户问询:

日本总部

功率器件销售与市场部

电话:+81-3-3457-3933

中国地区

分立器件市场部(Discrete Marketing)

上海:021-6090-0610/深圳:0755-3661-5889

* 本文提及的公司名称,产品名称和服务名称可能是其各自公司的商标。

* 本文档中的产品价格和规格、服务内容和联系方式等信息,在公告之日仍为最新信息,如有变更,恕不另行通知。