What is Electrostatic discharge (ESD) testing?

Electrostatic discharge (ESD) testing is performed to test the susceptibility of ICs and electronic devices to ESD. ESD tests are broadly divided into device- and system-level tests. These are go/no-go tests that simply determine whether equipment under test (EUT) is destroyed by ESD.

- Device-level ESD tests:

Device-level ESD tests are performed at electronics manufacturing facilities, etc. where ESD is controlled. The purpose of device-level ESD tests is to determine whether devices under test (DUTs) such as ICs are degraded or destroyed by an ESD strike having relatively small energy. Conventional models for the ESD immunity tests include a human body model (HBM), a machine model (MM), and a charged device model (CDM). All DUT pins are subject to ESD tests. Protection circuits in the DUT provide device-level ESD protection. - System-level ESD tests:

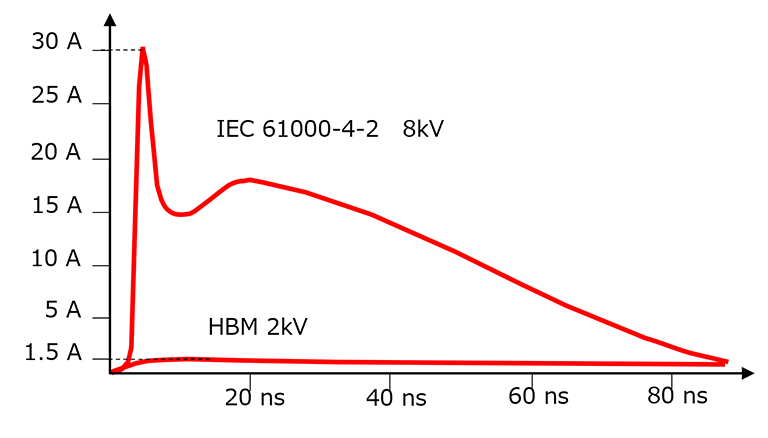

System-level ESD tests are designed to ensure that electronic devices are not degraded or destroyed by ESD strikes that occur in daily life (for example, an ESD strike that occurs when a cable is plugged into a USB port). IEC 61000-4-2 is an ESD immunity standard. In system-level tests, ESD events are applied to the I/O pins that are externally exposed via connectors, touch sensors, and antennas. System-level tests use an ESD waveform with greater energy than device-level tests. Figure 1 compares the test waveforms for device-level (HBM) and system-level (IEC 61000-4-2) ESD tests. Although these waveforms cannot be simply compared because of different test conditions (e.g., impedance), a system-level ESD test applies much higher current than a device-level ESD test. Since it is difficult for the internal protection circuitry alone of an IC to protect against system-level ESD current, you need to add ESD protection diodes externally.

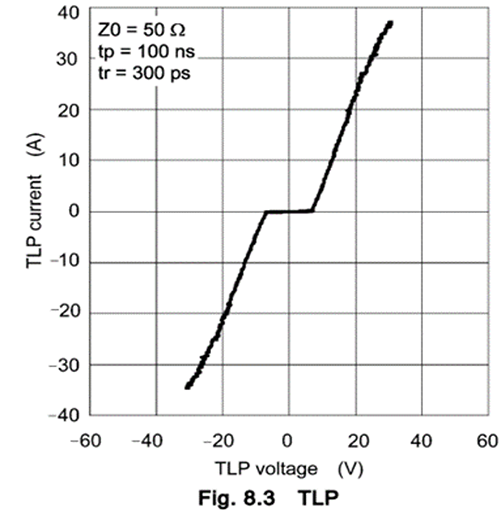

Nowadays, datasheets for ICs and ESD protection devices provide a transmission line pulse (TLP) I-V curve for ESD protection circuitry under short-pulse conditions. The TLP I-V curve helps you evaluate the ESD susceptibility of a system and select the right ESD protection diodes without destroying a DUT.

This type of test is called a TLP test. The datasheets for Toshiba’s new ESD protection diodes also contain TLP I-V curves. See the FAQ entry “What is a TLP test?”

What is a TLP test?

Related Links

For TVS diode (ESD protection diode) products, please refer to the following links.