Countermeasures for Hazards

In the case of multiple-input combinational logic consisting of OR, AND and other gates, a slight difference in the timing of input signal changes causes a brief whisker-like pulse called a hazard.

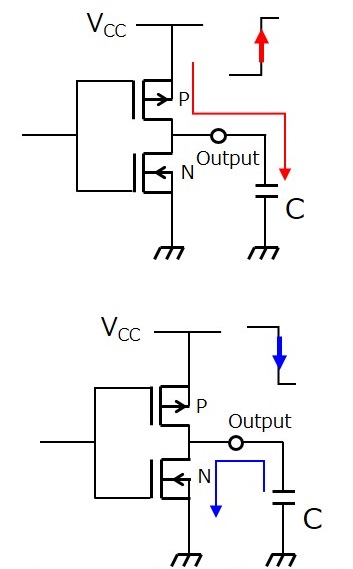

Using the circuit shown in below figure, let’s see how a hazard occurs because of a difference in signal delays. Suppose that a rising signal transition occurs simultaneously at A and B. The signal applied to B reaches the AND gate via an inverter. Since the signal that enters the AND gate from B is delayed by an inverter, the AND gate receives input signals A and C at different timings, potentially producing a High pulse at the Y output.

Countermeasures for hazards

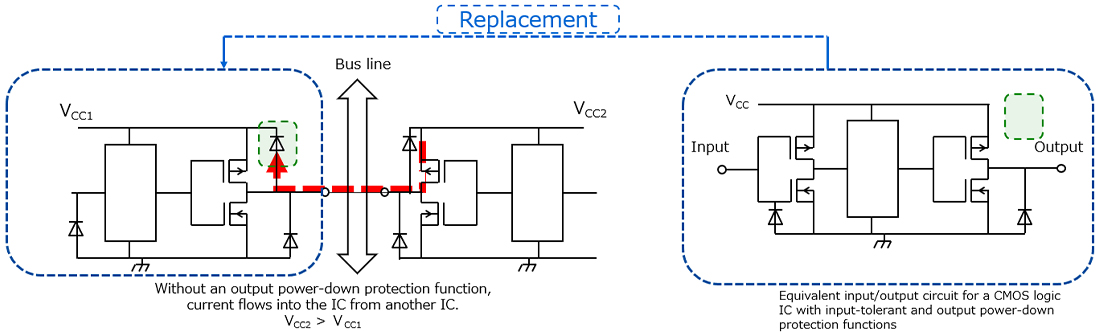

combinational logic should not be designed to produce a desired output value from simultaneous changes in its inputs. Using a flip-flop to adjust the output timing also helps eliminate a hazard.

In addition to a signal timing difference, a slowly changing input can be a cause of a hazard.

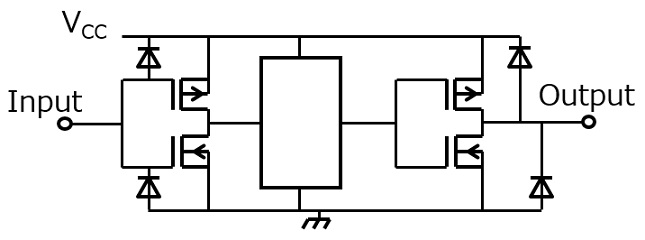

Hazards due to a slowly changing input can be prevented by using a logic gate with a Schmitt-trigger input.

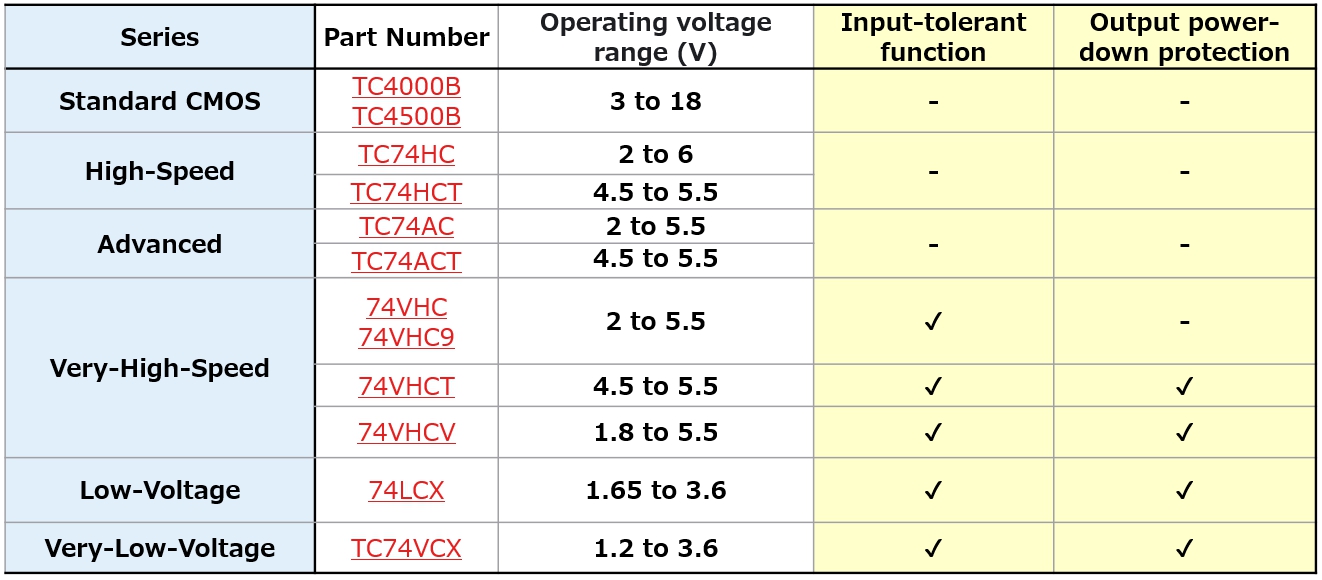

Usage Considerations of CMOS Logic ICs

Products

Related information

- Application Notes

- FAQ