- 品番検索

- クロスリファレンス検索

- キーワード検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。

当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

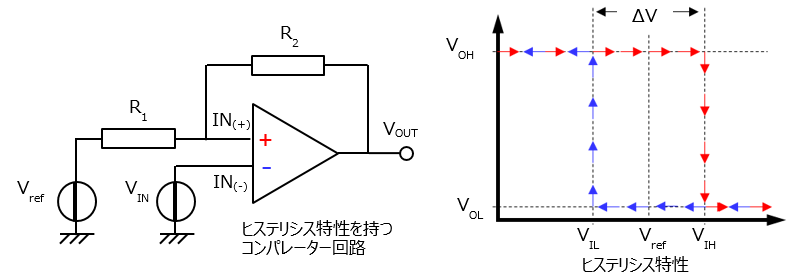

コンパレーターにヒステリシス(シュミットトリガー)を持たせる方法

コンパレーター*は一般的に基準電圧に対して入力電圧が高いか低いかを判定するときに使用されます。ノイズが多い環境で立ち上がり/立ち下がりの早くない信号 (スロー入力) や、スレッシュホールド電圧 (基準しきい値電圧) 付近の信号を入力する場合、出力が “VOH” “VOL” を繰り返す望ましくない状態となることがあります。このようなときに、”L” ⇒ “H” に遷移するスレッシュホールド電圧VIHと “H” ⇒ “L” に遷移するスレッシュホールド電圧VILの2値を持つヒステリシス特性 (図-1) を入力に持たせ、遷移の生じない不感帯 ΔV を設けることでこの望ましくない出力を改善することが可能となります。

このヒステリシス (シュミットトリガー) 特性をコンパレーターに持たせる回路はいくつかありますが、全てに共通することはコンパレーターの出力から入力に正帰還をかけることです。最も簡素な回路を図-2に示します。ただし、コンパレーターはプッシュプル出力で理想的な特性 (入力インピーダンスは無限大、出力インピーダンスはゼロ)を持ち 、基準電源Vrefの出力インピーダンスはゼロとします。

まず、IN(-)端子にVILより低い電圧が印加されているとします (①) 。この時出力電圧はVOHとなります。この電圧はR2を通ってIN(+)端子に帰還されます。同時にIN(+)端子はR1を経由して電圧Vrefも印加されています。コンパレーターの入力インピーダンスは無限大なのでIN(+)端子の電圧VIN(+)は下記となります。

VIN(+) = ( VOH – Vref ) x R1 / ( R1 + R2 ) + Vref ・・・(1)

理想状態ではコンパレーターの出力電圧は、VOH = VCC なので、Vrefよりも電圧が高くなっていることがわかります。従って、一旦 “H” になった状態から “L” 状態への遷移はしにくくなっていることがわかります。この電圧をVIHとします。

次に、VIHよりも高い電圧がIN(-)端子に加えられたとします。VOUTは ”L” 状態 (VOL) へ遷移します (②)。

同様にIN(+)端子の電圧VIN(+)を計算すると

VIN(+) = ( VOL – Vref ) x R1 / ( R1 + R2 ) + Vref ・・・(2)

VOLはVrefよりも低い電圧なので、(2)式の右辺の第一項はマイナスとなり、Vrefよりも低い電圧になります。

このため、一旦 “L” 状態になると、“H”への遷移はより低い電圧を印加しなければならないことがわかります。

このように、正帰還をかけることで簡単にヒステリシス特性を得ることが可能となります。

(1)式と(2)式からヒステリシス幅ΔVはリファレンス電圧Vrefを中心に幅 ( VOH – VOL ) x R1 / ( R1 + R2 ) となります。

*:オペアンプとコンパレーターの内部回路構成はほとんど同じですが、コンパレーターにはオペアンプに必須の位相補償用のコンデンサが内蔵されていません。コンパレーターは負帰還での使用を想定していないので、負帰還での発振が起こりにくくするためのコンデンサがありません。このコンデンサは応答スピードを遅らせる作用があります。オペアンプをコンパレーターとして使用する場合、この点に注意が必要です。

関連リンク

以下の資料にも関連する説明がありますので、ご参照ください。