ハザードの対策

多数の信号線の論理和や論理積をとって結果を出すような論理回路において、入力信号の遅延による微妙なズレによって、微小なヒゲ状のパルスが出力されることがあります。このヒゲ状のパルスをハザードと呼びます。

信号遅延によってハザードが起こる例として下図を用いて説明します。図のようにAとBに同じ立ち上がりの信号を入力し、Bに入力した信号はインバーターを介してAND回路に入力します。AND回路に入力されるBからの信号はインバーターで遅延するため、出力Yに予期しない論理状態である”ハイ”が出力される可能性があります。

< ハザードの対策 >

入力信号を同時に変化させて出力を変化させるように設計しないことや、フリップフロップなどを使用して出力のタイミングを調整することです。

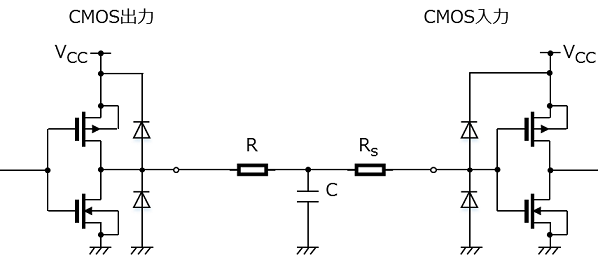

このような信号遅延の他に、立ち上がり、立ち下がり時間の遅い入力(スロー入力)が原因でハザードが起こる場合もあります。この場合はシュミット・トリガー入力のロジックICを使用することで対策できます。

製品ページ

関連情報

別ウインドウにて開きます