順序論理回路(フリップフロップ)

フリップフロップ

(例:74VHC74)

フリップフロップは、データをある条件下で保持することが出来ます。フリップフロップ(Flip-Flop)は、頭文字をとってFFと表記されることもあります。フリップフロップにはDタイプフリップフロップ、JKタイプフリップフロップなどの種類があります。ここではDタイプフリップフロップを例に動作を説明します。

Dラッチとの差はクロックが立ち下がった時にも出力データが保持されていることです。(DラッチはLE入力がHの場合、入力論理と同じの論理が出力される。)

入力(D)、クロック(CK)、出力(Q)で構成される製品の場合、クロック(CK)の立ち上がりにより、入力 (D)が保持されその信号が出力されます。次のクロック(CK)の立ち上がりが入力されるまで、入力(D)が変化しても出力(Q)は変わりません。クロック(CK)が立ち上がり以外の時には、直前の立ち上がりクロック(CK)で保持した入力(D)が出力され続けます。以下にタイミングチャートを示します。内部保持信号を初期化出来るCLR、PR付きの製品もあります。

* CLR:クリア機能,PR:プリセット機能

フリップフロップの応用例として非同期信号の同期化、デジタル信号の遅延回路、カウンター、分周回路などがあります。

Dタイプフリップフロップの動作について

論理回路図を用いてDタイプフリップフロップの動作について説明します。

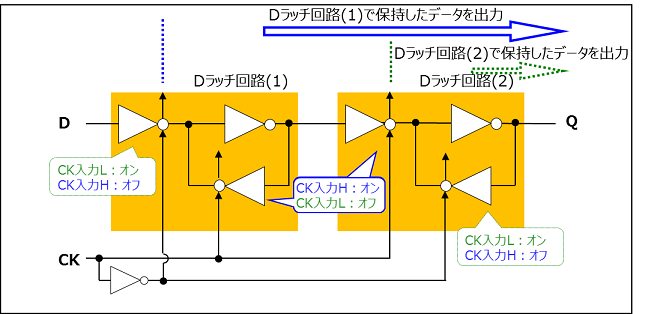

DタイプフリップフロップはDラッチの回路を2段接続して構成しています。

Dタイプフリップフロップは、クロック(CK)に立ち上がりが入力されると、ラッチ回路(1)が動作します。クロック(CK)がHの時には、ラッチ回路(1)が動作しつづけ、ラッチ回路(2)の初段のクロックドインバーターも動作しているため、ラッチ回路(1)で保持しているデータを出力(Q)に出力します(システム図中青矢印)。入力信号が変わっても出力は変化しません。クロック(CK)に立ち下がりが入力されると、ラッチ回路(2)が動作し、ラッチ回路(1)が保持したデータを出力し続けます(システム図中緑矢印)。この時も入力信号が変わっても出力は変化しません。

クロック(CK)の立ち上がりを読み込む前の出力(Q)は不明であることに注意が必要です。