1-9.3端子レギュレーター (標準レギュレーター、ボルテージレギュレーター) とLDOレギュレーターとの違い

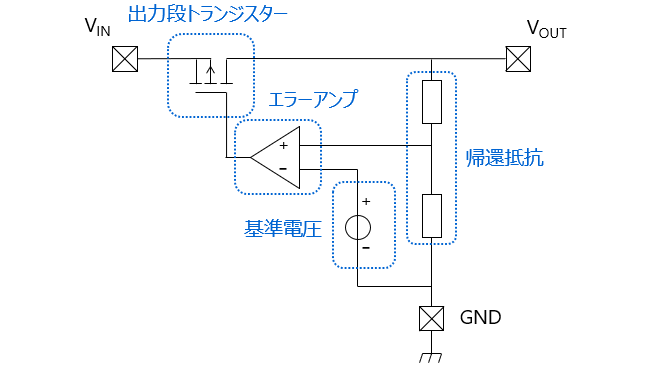

古くから使用されている3端子レギュレーター (標準レギュレーター) では、出力段のトランジスターにNPNトランジスターやN-ch MOSFETが使用されています。

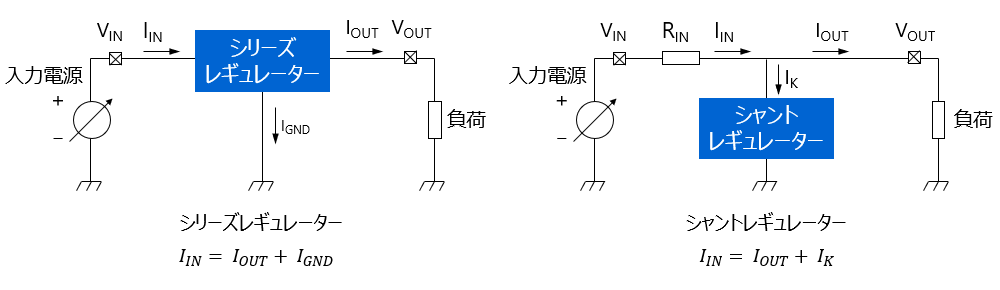

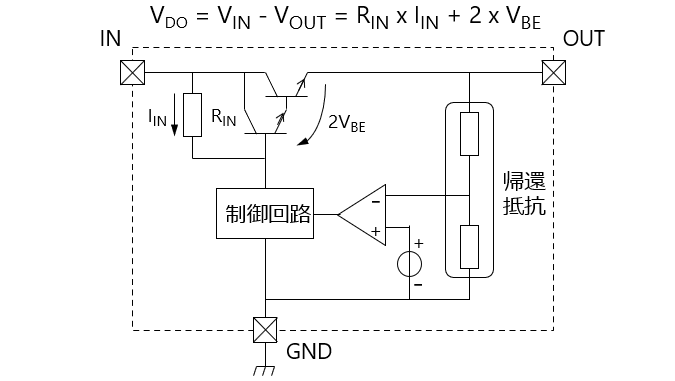

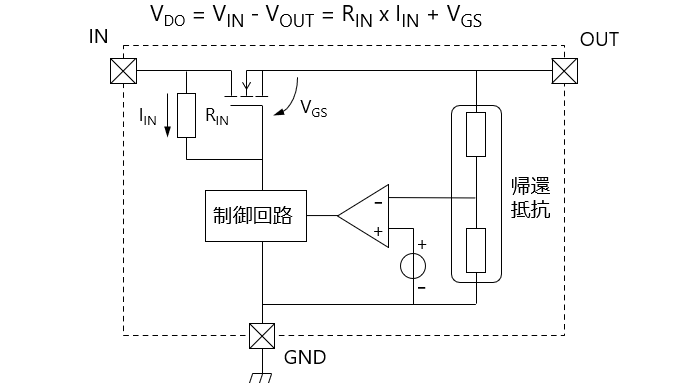

この回路方式では下図に示すように、レギュレーターとして動作するためにドロップアウト電圧 VDO と呼ばれる入力と出力間の電圧差が必要です。

VDO の最小値は

- NPNトランジスター方式ではVIN - VOUT > RIN x IIN + 2 x VBE

- N-ch MOSFET方式では、 VIN - VOUT > RIN x IIN + VGS

を満足する必要があります。

ここで、RIN = 1 kΩ、IIN = 1 mA、VBE = 0.7 V、VGS = 1 Vと仮定すると、5 Vの電圧を出力させるために必要な入力電圧の最小値は、NPN方式で7.4 V、N-ch MOSFET方式では7 Vとなります。

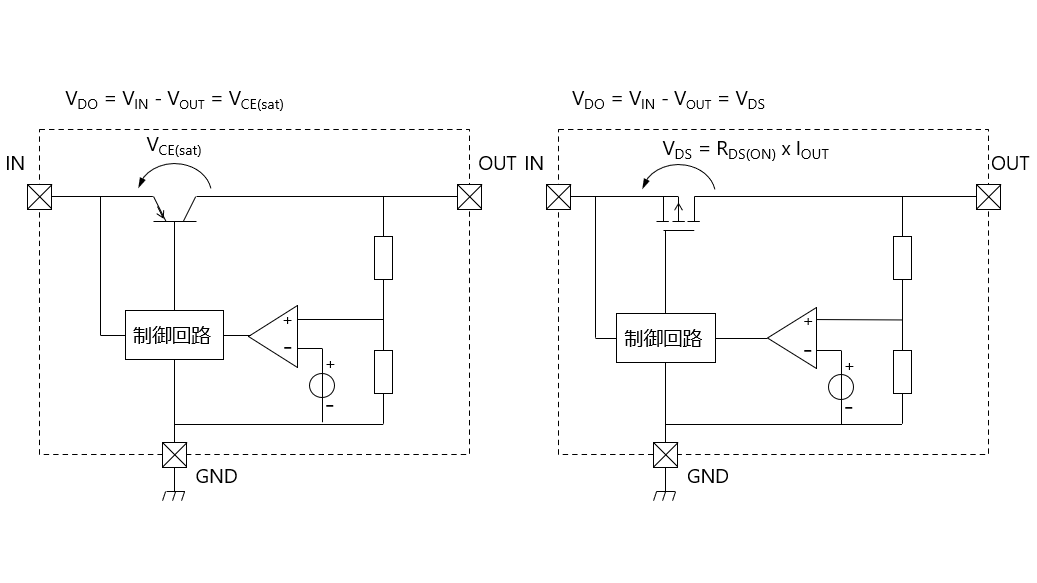

これに対して、LDOレギュレーターの出力段トランジスターは主にPNPトランジスターやP-ch MOSFETが使用されます。PNPトランジスターやP-ch MOSFETでは、ドロップアウト電圧の最小値はコレクタ・エミッター間電圧 VCE(sat) やドレイン・ソース間電圧 VDS (= RDS(ON) x ID) で決定します。このため、LDOレギュレーターは3端子レギュレーターよりも小さいドロップアウト電圧で動作することが可能です。

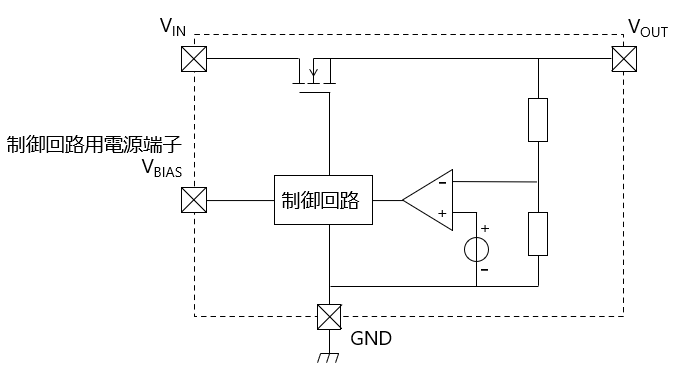

ドロップアウト電圧の更なる低減を目的として、P-ch MOSFETよりもオン抵抗を小さくできるN-ch MOSFETを出力段に使用し、N-ch MOSFETの駆動回路を含めた制御回路へ専用端子から電源を供給して動作するLDOレギュレーターも開発されています。

また、よりドロップアウト電圧の低減を目的として、P-ch MOSFETよりもオン抵抗を小さくできるN-ch MOSFETを出力段に使用し、制御回路用に設けられた専用端子から電源を供給して動作するLDOレギュレーターも開発されています。

- 前へ

- 9/9

関連情報

- 製品ページ

LDOレギュレーター - アプリケーションノート

アプリケーションノート - LDOのFAQ

LDOのFAQ - LDOのパラメトリックサーチはこちら

LDOパラメトリックサーチ - LDOの購入はこちら

Stock Check & Purchase