## **TOSHIBA**

32 ビット TX System RISC TX19 ファミリー TMP19A43FD/FZXBG

Rev2.1 2007年4月09日

# 32 ビットRISC マイクロプロセッサ TX19 ファミリーTMP19A43FZXBG. FDXBG

## 1. 概要と特長

TMP19A43 に搭載されている TX19A プロセッサコアは、米国 MIPS グループの高性能な 32 ビットの命令セットである MIPS32ISA と高コード効率の命令セットである MIPS16eISA に当社で命令を追加した拡張命令セットの MIPS16e-TX ™ASE (Application Specific Extension) を追加して、当社で独自開発した高性能な 32 ビット RISC プロッセサファミリーです。

TMP19A43 は、TX19A プロセッサコアをベースに各種周辺機能を内蔵した低電圧/低消費電力動作が可能な32 ビット RISC マイクロプロセッサです。

TMP19A43 の特長は次の通りです。

- (1) TX19A プロセッサコア (詳細は別冊の TX19A コアアーキテクチャを参照してください)

- ①16 ビットと 32 ビットの 2 つの ISA (Instruction Set Architecture) モードで、コード効率と演算性能の向上を実現

- 16 ビット ISA モードの命令は、コード効率の優れた MIPS16™ASE とオブジェクトレベルで互換

- 32 ビット ISA モードの命令は、演算性能の優れた TX39 とオブジェクトレベルで互換

- ②高性能化と低消費電力化を同時に実現

#### ●高性能化

- SAVE/RESTORE/ジャンプ・分岐命令を除き1クロックで実行

- 3オペランドの演算命令により高性能を実現

- 5段パイプライン

- 高速メモリを内蔵

- ▶ DSP 機能: 32 ビット積和演算(32×32+64=64 ビット)を1クロックで実行

#### ●低消費電力化

- 低消費電カライブラリを使用した最適化設計

- プロセッサコアの動作を停止させるスタンバイ機能

- ③リアルタイム制御に向いた高速割り込み応答

- エントリーアドレスを独立化

- 要因別のベクタアドレスを自動生成

- 割り込みマスクレベルを自動更新

060629TBA

- 当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり故障することがあります。当社半導体製品をご使用いただく場合は、半導体製品の誤作動や故障により、生命・身体・財産が侵害されることのないように、購入者側の責任において、機器の安全設計を行うことをお願いします。

- なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用いただくと共に、考慮されるべき注意事項や条件について「東芝 半導体製品の取り扱い上のご注意とお願い」「半導体信頼性ハンドブック」などでご確認ください。 021023\_A

- 本資料に掲載されている製品は、一般的電子機器 (コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電機器など) に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や誤作動が直接人命を脅かしたり、人体に危害を及ぼす恐れのある機器 (原子力制御機器、航空宇宙機器、輸送機器、交通信号機器、燃焼制御、医療機器、各種安全装置など) にこれらの製品を使用すること (以下 "特定用途" という) は意図もされていませんし、また保証もされていません。本資料に掲載されている製品を当該特定用途に使用することは、お客様の責任でなされることとなります。 021023\_B

- 本資料に掲載されている製品を、国内外の法令、規則及び命令により製造、使用、販売を禁止されている応用製品に使用することはできません。 060106 Q

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。021023\_C

- 本資料に掲載されている製品は、外国為替及び外国貿易法により、輸出または海外への提供が規制されているものです。 021023\_E

- 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。 021023\_D

(2) 内蔵プログラムメモリ/データメモリ

※※企画中

| 製品名            | 内蔵 ROM             | 内蔵 RAM  |  |

|----------------|--------------------|---------|--|

| TMP19A43CZXBG  | 384Kbyte           | 20Kbyte |  |

| TMP19A43CZFG** | 304NDYLE           |         |  |

| TMP19A43CDXBG  | 512Kbyte           | 24Kbyte |  |

| TMP19A43FZXBG  | 384Kbyte(Flash)    | 20Kbyte |  |

| TMP19A43FZFG** | JOHNUY LE (FTASII) | ZUNDYLE |  |

| TMP19A43FDXBG  | 512Kbyte(Flash)    | 24Kbyte |  |

• ROM コレクション機能: 1word×8block、8word×4block

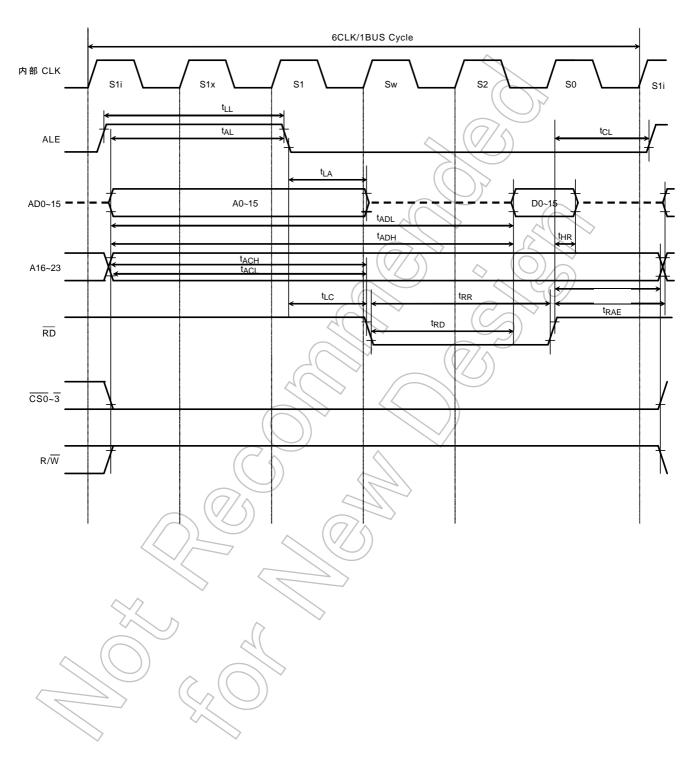

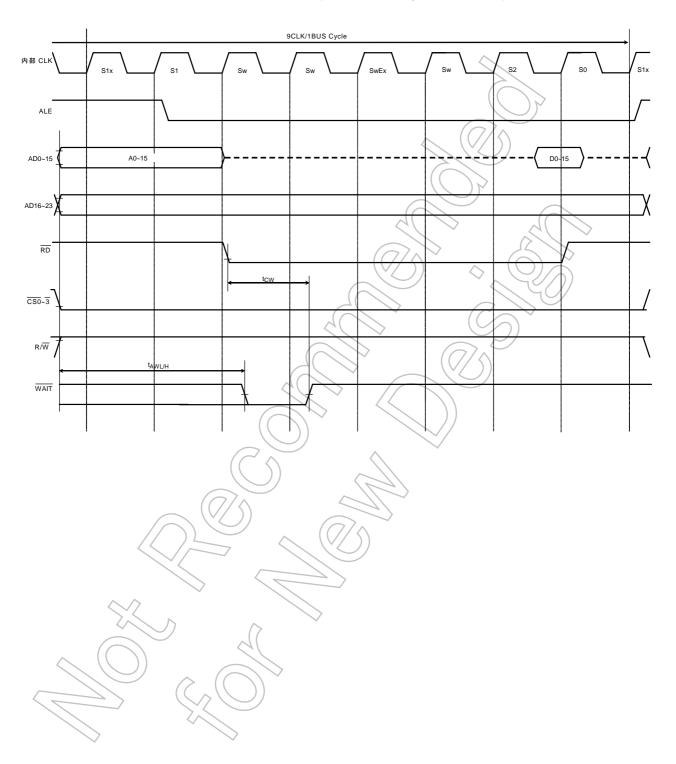

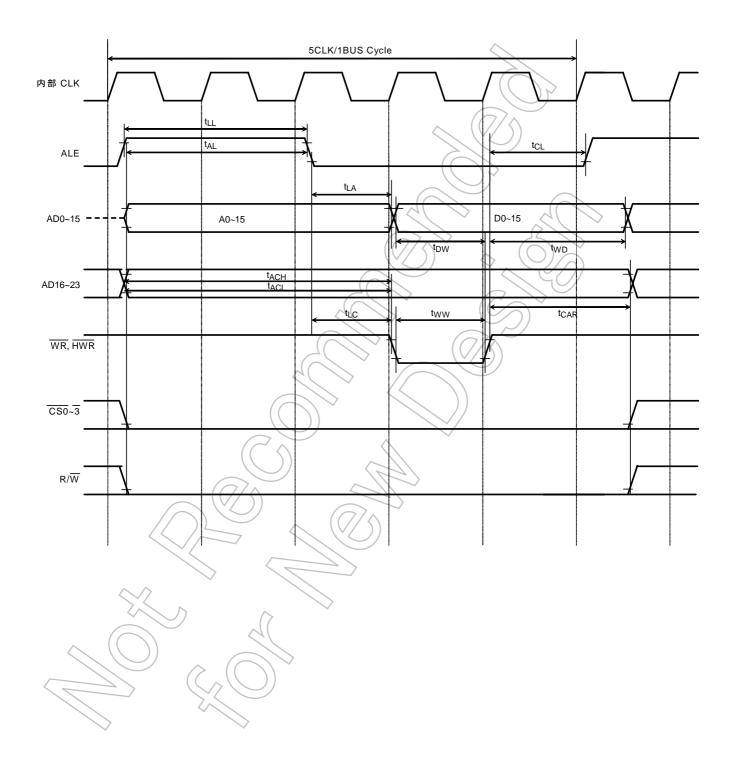

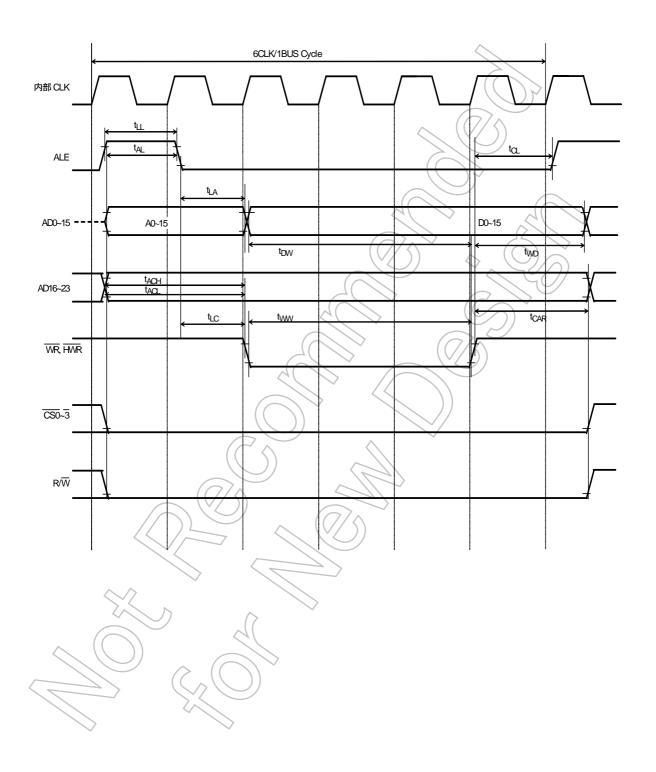

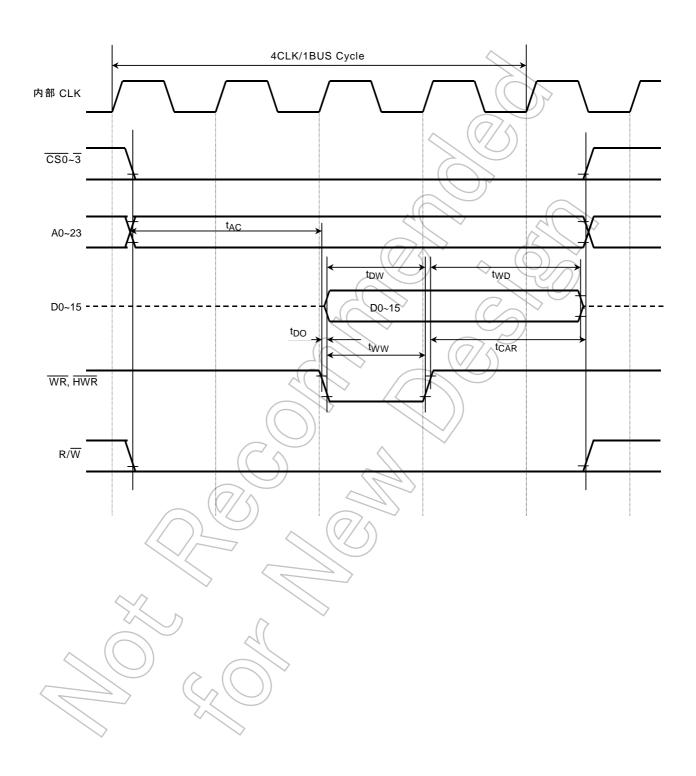

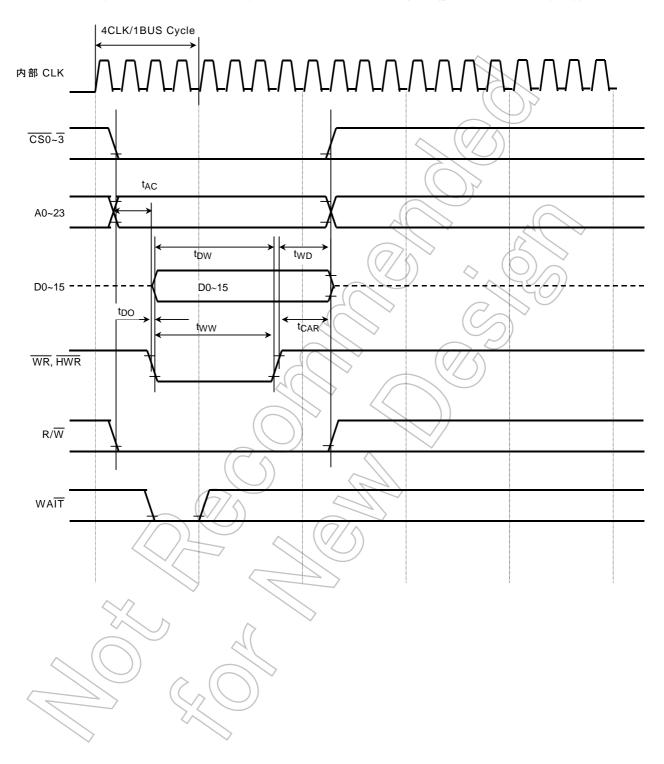

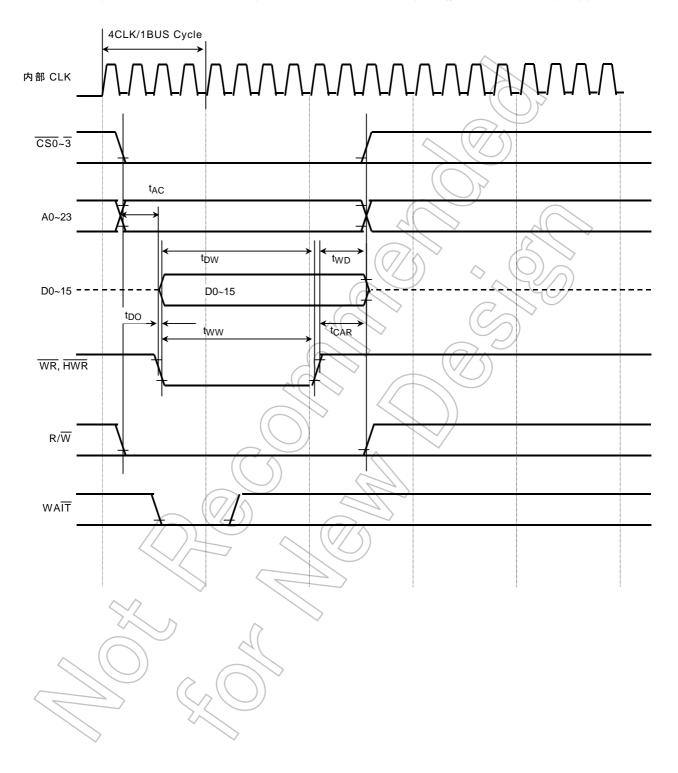

#### (3) 外部メモリ拡張

- 16M バイト(プログラム/データ共通)まで拡張可能

- 外部データバス:

セパレートバス/マルチプレクスバス チップセレクト/ウェイトコントロ<del>/</del>ラ

: 8/16 ビット幅共存可能

: 4チャネル/

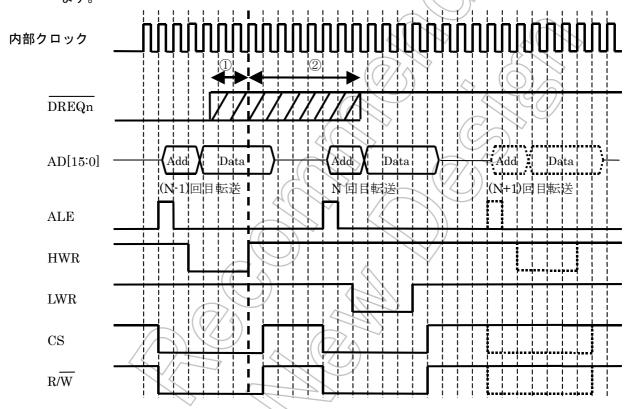

(4) DMA コントローラ

· 8 チャネル(割り込みは2要因)

- 割り込みもしくはソフトウェアにて起動

- 転送対象は内蔵メモリ、内蔵 1/0、外部メモリ及び外部 1/0

(5) 16 ビットタイマ

16 チャネル

- 16 ビットインターバルタイマモード

- 16 ビットイベントカウンタモード

- 16 ビット PPG 出力 (4ch 毎, 同期出力可能)

- インプットキャプチャ機能

- 二相パルス入力カウンタ機能(専用4チャネル):4 逓倍モード

#### (6) 32 ビットタイマ

• 32 ビットインプットキャプチャレジスタ : 4 チャネル

• 32 ビットコンペアレジスタ : 8 チャネル

• 32 ビットタイムベースタイマ : 1 チャネル

(7) 時計用タイマ : 1 チャネル

(8) 汎用シリアル・インタフェース : 3 チャネル

◆ UART/同期式モード選択可能

(9) 高速シリアル・インタフェース : 3 チャネル

■ UART/高速同期式モード(Max:10Mbps fsys=40MHz 時)選択可能

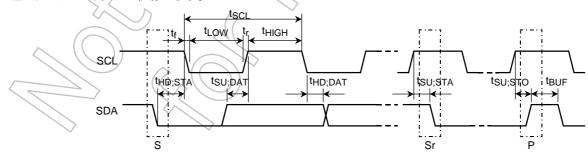

(10) シリアルバスインタフェース : 1 チャネル

I<sup>2</sup>C バスモード/クロック同期式モード選択可能

(11) 10 ビット A/D コンバータ (S/H 有) : 16 チャネル

外部トリガスタート可能、内部タイマトリガ起動

- チャネル固定/スキャンモード

- シングル/リピートモード

- 最優先変換モード

- タイマ監視機能

- 変換時間 1.15 μ sec (fsys=40MHz 時)

(12) 8 ビット D/A コンバータ : 2 チャネル(13) ウォッチドックタイマ : 1 チャネル

(14)割り込み機能

● CPU 2本 ····ソフトウエア割り込み命令

内部 46 本 ・・・・ 7 レベルの優先順位設定可能 (ウォッチドッグタイマ割り込みを除く)

● 外部 48 本 ···· 7 レベルの優先順位設定可能

32 本は KWUP であり、割込み要因としては 1 本 (15) 入出カポート ・・・・ 143 端子

(16) スタンバイ機能

• 3種類のスタンバイモード (IDLE, SLEEP、STOP)

(17) クロックジェネレータ

● PLL 内蔵 (4 逓倍)

• クロックギア機能: 高速クロックを 3/4, 1/2, 1/4, 1/8 に分周

サブクロック: SLOW/SLEEP モード(32.768kHz)

(18) エンディアン ・・・・ バイエンディアン (ビッグエンディアン/リトルエンディアン)

(19) 最大動作周波数

• 40MHz (PLL4 逓倍)

(20)動作電圧範囲

コア 1.35V~1.65V

• 1/0, ADC 2.7V~3.6V

DAC

2. 3V~2. 7V

(21) パッケージ

TFBGA193-P-1212-0.65A4 (12mm×12mm, 0.65mm ピッチ) LQFP176-P-2424-0.5 (24mm×24mm, 0.5mm ピッチ)

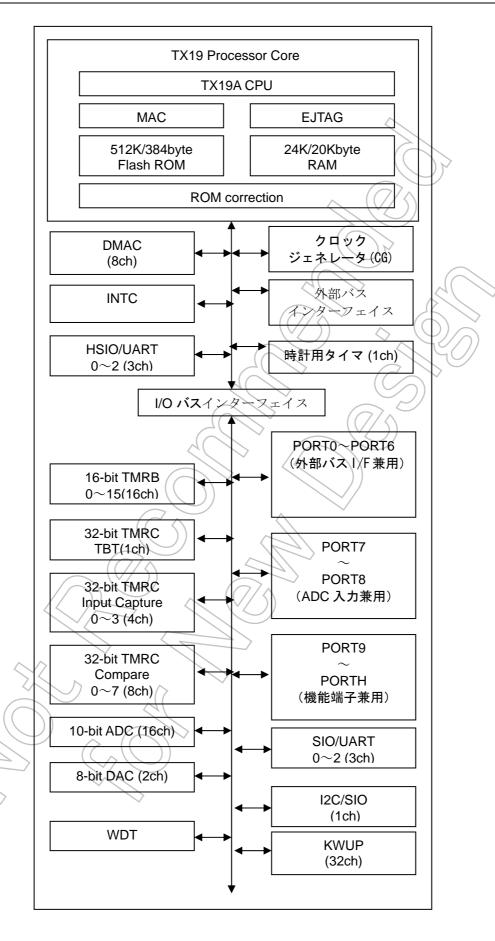

図 1-1TMP19A43 ブロック図

#### Flash 動作説明 2.

Flash 機能について、ハードウエアの構成およびその動作を説明します。本デバイスは TMP19A43CDXBG の内蔵 ROM を内蔵フラッシュメモリに置き換えたものです。その他の構成および機能 は TMP19A43CDXBG と同一です。ここに記載されていない機能については IMP19A43CDXBG のデータシー トを参照してください。

#### 2.1 フラッシュメモリ

#### 2.1.1 特長

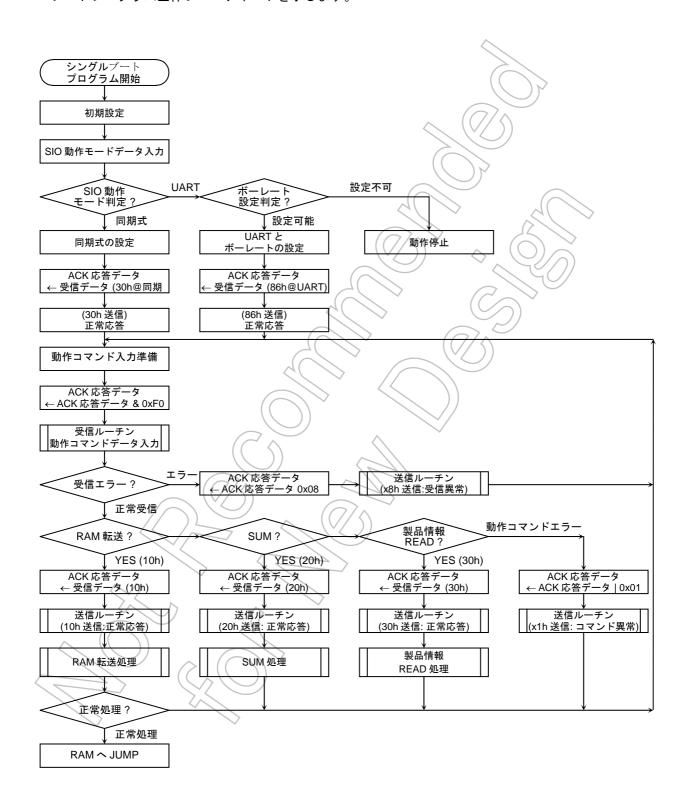

1) メモリ容量

TMP19A43FDXBG はフラッシュメモリ 4M ビット (512K バイト) を搭載しています。構成は 4 ブロック (128K バイト × 4) になっており、各ブロック個別に書き込みをおこなうこと ができます。CPU から内蔵フラッシュメモリをアクセスする場合、データバス幅は 32 ビッ トとなります。

- 2) フラッシュメモリアクセス 本デバイスではインタリーブアクセスです。

- 3) 書き込み/消去時間

書き込み時間: 2sec/Chip (Typ) へ 0.5sec/128Kbyte(Typ.)

消去: 0.4sec/Chip (Typ) 100msec/128Kbyte(Typ.)

- (注) 上記値は理論時間を表しており、データ転送時間などは含まれていません。 チップ当たりの時間はユーザーの書き替え方法により異なります。

- 4) プログラミング方法

ユーザーのボード上で書き替えが可能なオンボードプログラミングモードがあります。

・オンボードプログラミングモード

4-1) ユーザーブートモード

ユーザー独自の書き替え方法をサポート

4-2) シングルブートモード

シリアル転送(当社オリジナル)での書き替え方法をサポート

#### 書き替え方式

本デバイス内蔵のフラッシュメモリは、一部の機能を除き JEDEC 標準機能に準拠していま す。このため、外部メモリとしてフラッシュメモリをご使用になられている場合でも、本LSI への移行が容易です。また、フラッシュメモリ内に書き込み、チップ消去など自動で行う回路 を内蔵していますので、書き込み、消去動作自身に係わる複雑なフローをユーザーがプログラ ムで組む必要がありません。

本デバイスでは、ライタでのフラッシュデータの読み出しを禁止する、プロテクト機能を追 加しています。一方、書き替え禁止を設定するプロテクトは、コマンド(ソフトウエア)によ る対応のみで 12/火電圧を印加して設定する方式(ハードウエア)には対応できません。前記 プロテクト機能は4エリア全てにプロテクトを掛けると自動的に有効になり、プロテクトの解 除を行うと内部データが自動的に消去され、その後に全てのプロテクトが解除されます。

| JEDEC 準拠の機能       | 変更、追加、削除した機能                     |

|-------------------|----------------------------------|

| • 自動プログラム         |                                  |

| ● 自動チップ消去         | 〈変更〉ブロックプロテクト(ソフトウエアプロテクトのみサポート) |

| ● 自動ブロック消去        | 〈削除〉消去レジューム/サスペンド機能              |

| • データポーリング/トグルビット | 自動マルチブロック消去(チップ単位までサポート)         |

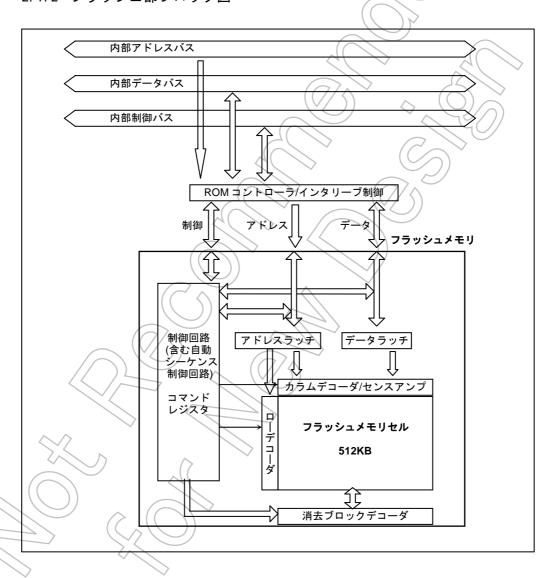

## 2.1.2 フラッシュ部ブロック図

図 2-1 フラッシュ部ブロック図

## 2.2 動作モード

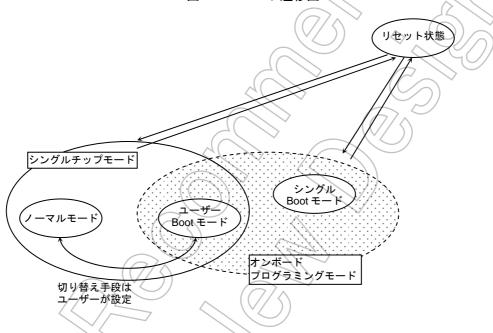

本デバイスは内蔵フラッシュメモリを使用しない場合を含めて、3 通りの動作状態 (モード) が存在します。

表 2-1 動作モード説明

| 動作モード名     | 動作の内容                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| シングルチップモード | リセット解除後、内蔵のフラッシュメモリから起動します。                                                                                                                                                       |

| ノーマルモード    | -<br>本動作モードの中で、ユーザーのアプリケーションプロダラムを実行するモードと、ユーザーのセット                                                                                                                               |

| , ,,, = 1  | 上でフラッシュメモリの書き替えを実行するモードとに分けて定義します。前者を「ノーマルモード」、<br>後者を「ユーザーブートモード」と呼びます。                                                                                                          |

| ユーザーブートモード | この両者の切り替えはユーザーが独自に設定できます。<br>例えばポート 00 が '1' のときノーマルモード、'0' のときにユーザーブートモードというように自由に<br>設計することが可能です。                                                                               |

|            | ユーザーはアプリケーションプログラムの一部に切り替えを判定するためのルーチンを準備してください。                                                                                                                                  |

| シングルブートモード | リセット解除後、内蔵する Boot ROM (Mask ROM) から起動します。Boot ROM には、本デバイスのシリアルポートを経由してユーザーのセット上で書き替えを行うことができるアルゴリズムがプログラムされています。 シリアルポートにより外部ホストと接続し、規定されたプロトコルでデータの転送を行うことで内蔵フラッシュの書き替えが実行できます。 |

上記表でプログラムが可能なフラッシュメモリの動作モードは ユーザーブートモード、シングルブートモードの2つです。ユーザーのセット上で内蔵フラッシュメモリの書き替えが可能なモードは、ユーザーブートモードとシングルブートモードで、この2つをオンボードプログラミングモードと定義します。

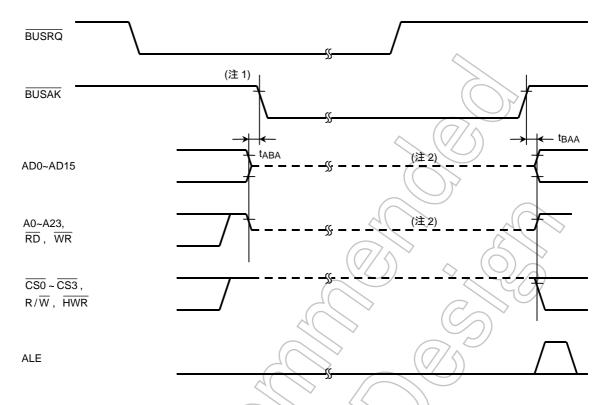

シングルチップ、シングルブートの各動作モードは、リセット状態で入力端子 $\overline{\mathrm{BOOT}}$  のレベルを外部で設定することにより決定されます。

CPU は状態設定後リセットを解除することにより各動作モードで動作を開始します。BOOT 端子については、それぞれモード設定後は動作中にレベルの変更がないように

してください。以下に動作モードの設定方法とモード遷移図を示します。

表 2-2 動作モード設定表

| 動作モード      | 入力端子       |  |  |  |  |

|------------|------------|--|--|--|--|

| 201F = 1   | RESET BOOT |  |  |  |  |

| シングルチップモード | 0 → 1      |  |  |  |  |

| シングルブートモード | 0 -1 0     |  |  |  |  |

図 2-2 モード遷移図

## 2.2.1 リセット動作

本デバイスにリセットをかけるには、電源電圧が動作電圧範囲内で、かつ内部発振器の発振が安定した状態で、少なくとも 12 システムクロック間(40MHz 動作で 2.4  $\mu$ s (リセット後は、クロックギア 1/8 モード)) RESET 入力を "0" にしてください。

- (注1) 電源投入後は、電源電圧および発振が安定した状態から 500 μ s 以上経過してからリセット解除させてください。

- (注 2) 内蔵フラッシュの消去、プログラム中は、システムクロックによらず 0.5 μ s 以上のリセット期間が必要となります。

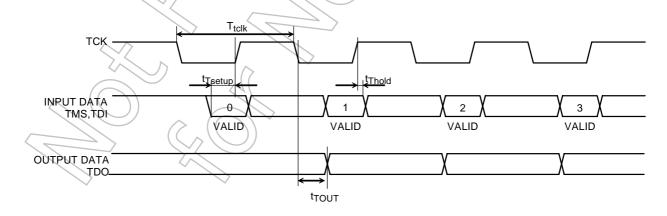

#### 2.2.2 DSU(EJTAG)-PROBE インタフェース

DSU-PROBE を利用してデバッグするときに使用します。DSU-PROBE と接続される専用 I/F です。DSU-PROBE を利用したデバッグの詳細に関しては、ご使用の DSU-PROBE の取扱説明書を参照してください。ここでは、DSU(EJTAG)モードでの DSU-PROBE 使用許可/禁止について説明します。

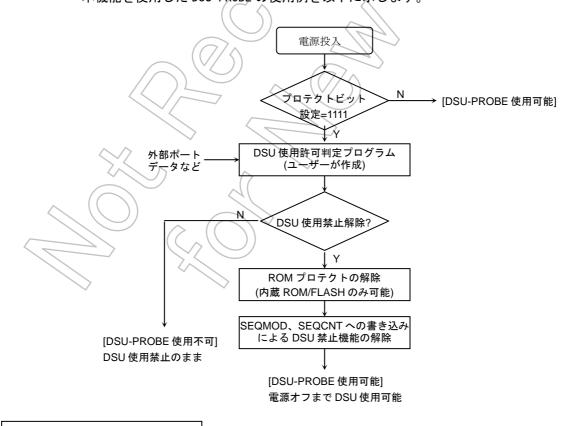

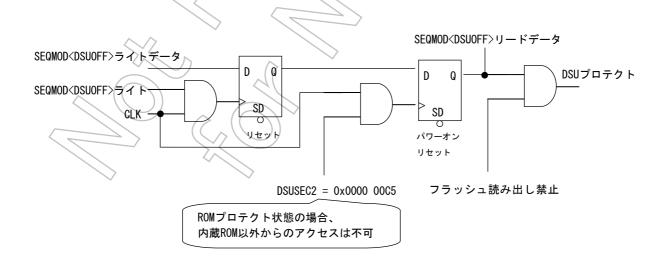

#### 1) プロテクト機能

本デバイスは、オンボード上で DSU-PROBE を使用してデバッグが可能です。このため、ユーザー以外の第三者が容易に内蔵フラッシュのデータを読み出させないようにするプロテクト機能をもっています。プロテクト機能を有効にすることにより、DSU-probe を使用して内蔵フラッシュの内容を読み出すことは不可能になります。後述のフラッシュプロテクト機能とあわせてご使用願います。

#### 2) DSU-PROBE 使用許可/禁止機能

本デバイスは、オンボード上で DSU-PROBE を使用してデバッグが可能です。このため、ユーザー以外の第三者が容易に内蔵フラッシュのデータを読み出させないようにする DSU-PROBE 使用禁止機能(以下、**DSU プロテクト**)をもっています。DSU 禁止機能を有効にすることにより、DSU-PROBE を使用することが不可能になります。

## 3) DSU 使用許可 (DSU-PROBE を利用してのデバッグを有効)

DSU プロテクトを解除する方法は、暴走などによる偶発解除を防ぐために二重構造になっており、DSU プロテクトモードレジスタ SEQMOD<DSUOFF〉 =  $_{0}$ " にし、プロテクトコード " $0x0000\_0005$ " を DSU プロテクト制御レジスタ SEQCNT に書き込みます。この後、DSU-PROBE を使用したデバッグが有効になります。電源をオフしない状態で、SEQMOD<SEQON〉 = "1"にし、SEQCNT レジスタに " $0x0000\_0005$ " を書き込むことにより再びプロテクト機能が有効になります。

表 2-3 DSU プロテクトモードレジスタ

SEQMOD (0xFFFF\_E510)

|   |               | 7  | 6                | 5      | 4      | 3      | 2     | 1  | 0           |

|---|---------------|----|------------------|--------|--------|--------|-------|----|-------------|

|   | Bit Symbol    |    |                  |        |        |        |       |    | DSU0FF      |

|   | Read/Write    |    | <i>)</i>         |        | R      | 7      |       |    | R/W         |

|   | リセット後         |    |                  |        | / (0)  |        |       |    | 1           |

|   | 機能            |    | j                | ノードする。 | と常に"0" | が読めます  | t     |    | 1: DSU 使用不可 |

|   |               |    |                  |        |        |        |       | _  | 0: DSU 使用許可 |

|   |               | 15 | 14               | 13     | 12     | 11     | 10    | 9  | 8           |

|   | Bit/Symbol    |    |                  |        |        |        |       |    |             |

|   | Read/Write    |    | _                |        |        | R      |       |    |             |

|   | リセット後         |    | 0                |        |        |        |       |    |             |

|   | 機能            |    | ///              | IJ     | ードすると  | 常に"0": | が読めます | _  |             |

| / | $\mathcal{D}$ | 23 | 22               | 21     | 20     | 19     | 18    | 17 | 16          |

| / | Bit Symbol    | 11 |                  |        |        |        |       |    |             |

| _ | Read/Write    |    |                  |        |        | R      |       |    |             |

|   | リセット後         |    |                  |        |        | 0      |       |    |             |

| > | 機能            |    | 7                |        |        |        |       | _  |             |

|   |               | 31 | 30               | 29     | 28     | 27     | 26    | 25 | 24          |

|   | Bit Symbol    |    |                  |        |        |        |       |    |             |

|   | Read/Write    |    |                  |        |        | R      |       |    |             |

|   | リセット後         |    |                  |        |        | 0      |       |    |             |

|   | 機能            |    | リードすると常に"0"が読めます |        |        |        |       |    |             |

#### (注) 本レジスタは32ビットのアクセスで行ってください。

(注) 本レジスタはパワーオンリセットのみで初期化されます。通常リセットでは初期化されません。(FLASH版)

表 2-4 DSU プロテクト制御レジスタ

SEQCNT (0xFFFF\_E514)

|            |    | 1  | 1       |           |        | 1     | 1    |    |

|------------|----|----|---------|-----------|--------|-------|------|----|

|            | 7  | 6  | 5       | 4         | 3      | 2     | 1    | 0  |

| Bit Symbol |    |    |         |           |        |       |      |    |

| Read/Write |    |    |         | V         | ٧      |       |      |    |

| リセット後      |    |    |         |           |        |       |      |    |

| 機能         |    |    | "0x0000 | )_00C5"をラ | ライトしてく | ください。 |      |    |

|            | 15 | 14 | 13      | 12        | 11     | 10    | 9    | 8  |

| Bit Symbol |    |    |         |           |        |       |      |    |

| Read/Write |    | •  | •       | V         | V      |       |      |    |

| リセット後      |    |    |         |           | _ (    | 7/4   |      |    |

| 機能         |    |    | "0x000  | 00_00C5"を | ライトして  | ください  |      |    |

|            | 23 | 22 | 21      | 20        | 19     | 18    | 17   | 16 |

| Bit Symbol |    |    |         |           |        |       |      |    |

| Read/Write |    |    |         | у         |        |       |      |    |

| リセット後      |    |    |         | 7         |        |       |      |    |

| 機能         |    |    | "0x000  | 00_00C5"を | ライトして  | ください  |      | ,  |

|            | 31 | 30 | 29      | 28        | 27     | 26    | 25   | 24 |

| Bit Symbol |    |    |         |           | ))     | 0     |      |    |

| Read/Write |    | •  |         |           | ν'     |       | 27)) |    |

| リセット後      |    |    |         |           |        |       |      |    |

| 機能         |    |    | "02000  | 00_00C5"を | ライトして  | 1/2/1 | ~    |    |

## (注) 本レジスタは32ビットのアクセスで行ってください。

## 4) ユーザー使用例

本機能を使用した DSU-PROBE の使用例を以下に示します。

図 2-3 DSU 禁止機能の使用例

### 2.2.3 ユーザーブートモード (シングルチップモード)

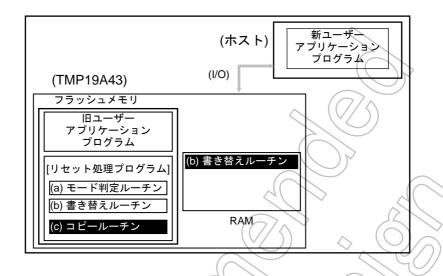

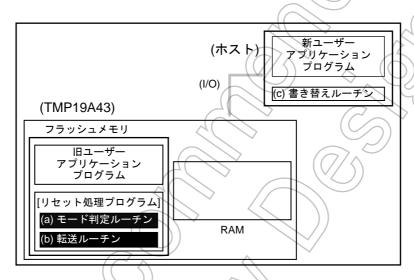

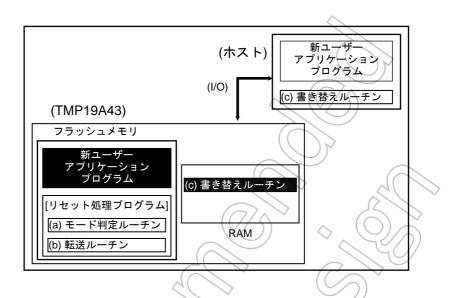

ユーザーブートモードは、ユーザー独自のフラッシュメモリ書き替えルーチンを使う方法です。ユーザーアプリケーション上で用意されているフラッシュメモリ書き替え用のプログラムで用いる、データ転送バスがシリアル I/O と異なる場合に使用します。 動作はシングルチップモード上で行います。このため、シングルチップモードにおいて通常のユーザーアプリケーションプログラムが動作しているノーマルモードから、フラッシュを書き替えるためのユーザーブートモードに移行する必要があります。したがって、条件判定を行うプログラムをユーザーアプリケーションの中で、リセット処理プログラムの中に組み込んでください。

このモード切り替えの条件設定は、本デバイスの I/O を使用してユーザーのシステムセット条件 に合わせて独自に構築してください。また、ユーザーブートモード移行後に使用するユーザー独自のフラッシュメモリ書き替えルーチンも同様にユーザーアプリケーションの中にあらかじめ組み込んでおき、ユーザーブートモード移行後にこれらのルーチンを使用して書き替えを行ってください。なお、内蔵フラッシュメモリは消去/書き込み動作モード中はフラッシュのデータを読み出せません。このため、書き替えルーチンはフラッシュメモリエリア外に格納して実行させる必要があります。また、シングルチップモード(通常動作モード)中に誤ってフラッシュの内容を書き替えないよう、書き替え処理が完了した後、必要なブロックにプロテクトをかけておくことを推奨します。あわせて、ユーザーブートモード中は、ノンマスカブルを含めたすべての割り込み発生を禁止してください。

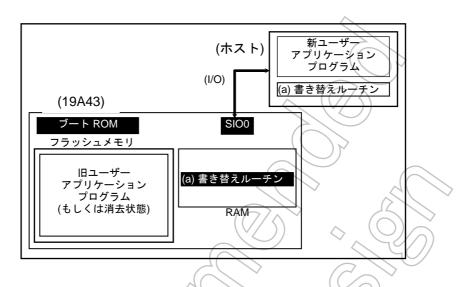

書き替えルーチンを内蔵フラッシュメモリに置く場合と、外部から転送する場合の2ケースを例に、以下(1-A)、(1-B)にその手順を説明します。フラッシュメモリへの書き込み/消去方法の詳細は、「3.4 オンボードプログラミングでのフラッシュメモリ書き込み/消去」を参照してください。

#### ユーザーブートモード

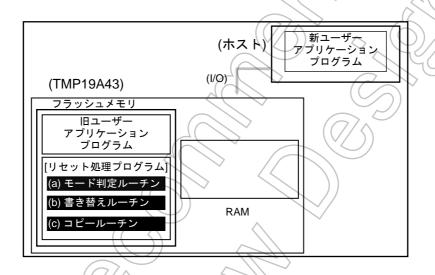

(1-A) 書き替えルーチンをフラッシュメモリに内蔵する場合の手順例

#### (Step-1)

ユーザーは、あらかじめ どのような条件(例えば端子状態)に設定されたらユーザーブートモード に移行するか、どの I/O バスを使用してデータ転送を行うかを決め、それに合った回路の設計、プログラムの作成を行います。ユーザーは本デバイスをボードに組み込む前に、あらかじめフラッシュメモリ上の任意のブロックにライタなどを使用して以下に示す 3 つのプログラムを書き込んでおきます。

(a) モード判定ルーチン: 書き替え動作に移るためのプログラム

(b) フラッシュ書き換えルーチン: 書き替えデータを外部から取り込み、フラッシュメモリを書

き替えるためのプログラム

(c) コピールーチン: 上記 (b) を内蔵 RAM または外部メモリにコピーするための プログラム

### (Step-2)

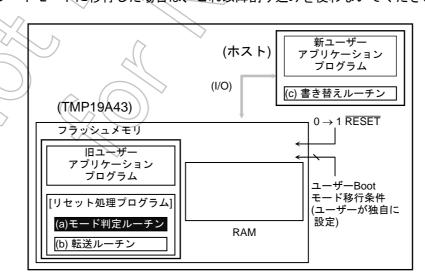

以下リセット処理プログラム内にこれらのルーチンを組み込んだ場合について説明します。まず、リセット解除後のリセット処理プログラムにおいてユーザーブートモードへの移行を判定します。このとき、移行条件が整っていれば、プログラムは書き替えのためのユーザーブートモードに移ります。(ユーザーブートモードに移行した場合は、これ以降割り込みを使わないでください。)

#### (Step-3)

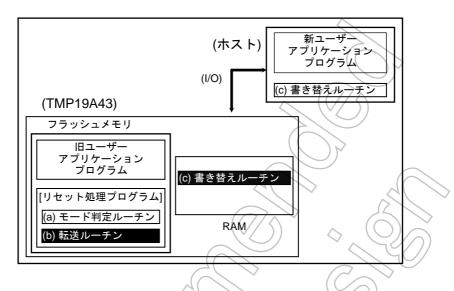

ユーザーブートモードに移ると、(c) コピールーチンを使用して、(b) 書き替えルーチンを内部 RAM もしくは外部メモリにコピーします。(下図は内部 RAM ヘコピーした場合を示します。)

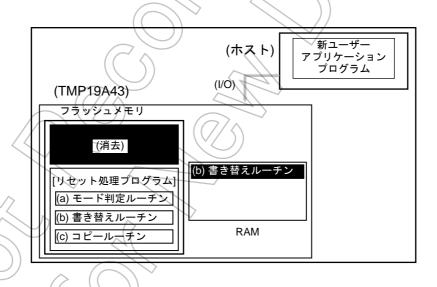

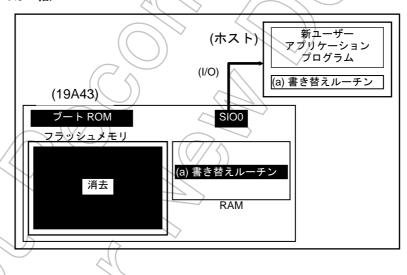

## (Step-4)

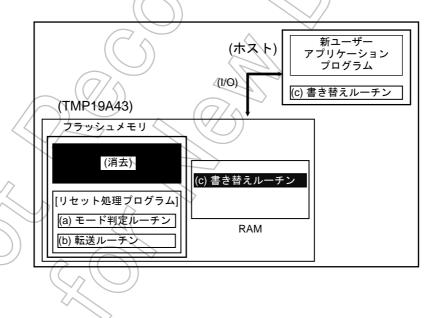

RAM 上の書き替えルーチンへジャンプレ、旧ユーザープログラムエリアのライトプロテクトを解除して、消去(ブロック単位)を行います。

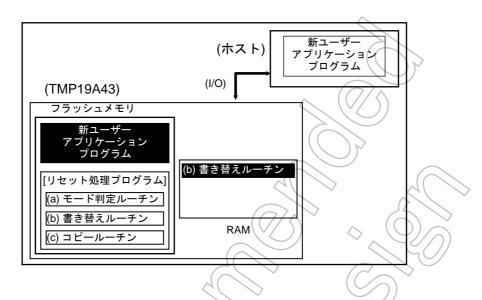

#### (Step-5)

さらに、RAM 上の書き替えルーチンを実行して、転送元(ホスト)より新ユーザーアプリケーションプログラムのデータをロードし、フラッシュメモリの消去したエリアに書き込みを行います。書き込みが完了したら、ユーザープログラムエリアのライトプロテクトをオンにします。

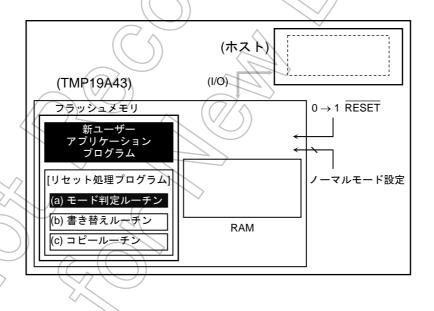

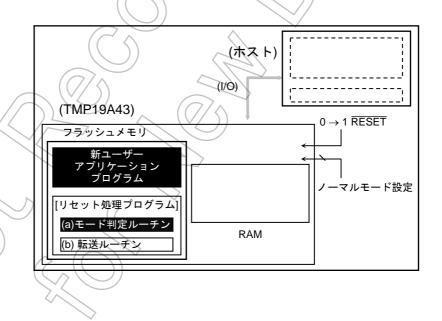

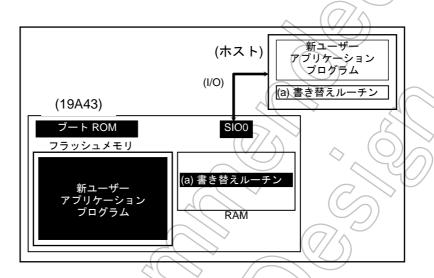

## (Step-6)

$\overline{\text{RESET}}$ 入力端子を "0" にしてリセットを行い、設定条件をメーマルモードの設定にします。リセット解除後、新ユーザーアプリケーションプログラムで動作を開始します。

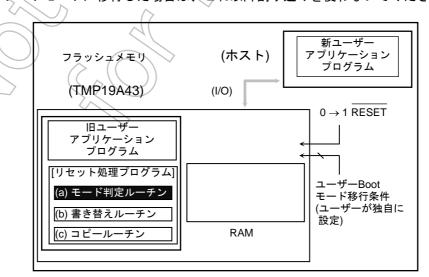

#### (1-B) 書き替えルーチンを外部から転送する手順例

#### (Step-1)

ユーザーは、あらかじめ どのような条件(例えば端子状態)に設定されたらユーザーブートモード に移行するか、どの I/O バスを使用してデータ転送を行うかを決め、それに合った回路の設計、プログラムの作成を行います。ユーザーは本デバイスをボードに組み込む前に、あらかじめフラッシュメモリ上の任意のブロックにライタなどを使用して以下に示す 2 つのプログラムを書き込んでおきます。

(a) モード判定ルーチン: 書き替え動作に移るためのプログラム

(b) 転送ルーチン: 書き替えプログラムを外部から取り込むためのプログラム

また、下記に示すプログラムはホスト上に用意します。

(c) 書き替えルーチン: 書き替えを行うためのプログラム

#### (Step-2)

以下リセット処理プログラム内にこれらのルーチンを組み込んだ場合について説明します。まず、リセット解除後のリセット処理プログラムにおいてユーザーブートモードへの移行を判定します。このとき、移行条件が整っていれば、プログラムは書き替えのためのユーザーブートモードに移ります。(ユーザーブートモードに移行した場合は、これ以降割り込みを使わないでください。)

#### (Step-3)

ユーザーブートモードに移ると、(b) 転送ルーチンを使用して、転送元(ホスト) より(c) 書き替えルーチンを内部 RAM もしくは外部メモリにロードします。(下図は内部 RAM ヘコピーした場合を示します。)

## (Step-4)

RAM 上の書き替えルーチンへジャンプし、旧ユーザープログラムエリアのライトプロテクトを解除して、消去(ブロック単位)を行います。

#### (Step-5)

さらに、RAM 上の (c) 書き替えルーチンを実行して、転送元 (ホスト) より新ユーザーアプリケーシションプログラムのデータをロードし、消去したエリアに書き込みを行います。書き込みが完了したら、ユーザープログラムエリアのライトプロテクトをオンにします。

## (Step-6)

$\overline{\text{RESET}}$ 入力端子を "0" にしてリセットを行い、設定条件をメーマルモードに設定します。リセット解除後、新ユーザーアプリケーションプログラムで動作を開始します。

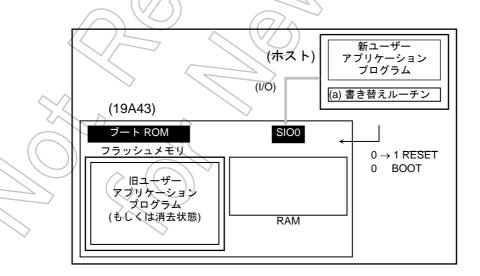

## 2.2.4 シングルブートモード

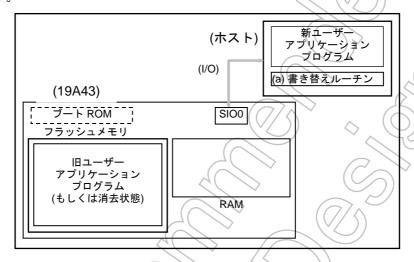

内蔵ブート ROM(マスク ROM)を起動して、ブート ROM のプログラムを利用してフラッシュメモリを書き替える方法です。このモードでは、内蔵ブート ROM が割り込みベクタテーブルを含む領域にマッピングされ、ブート ROM プログラムが実行されます。また、フラッシュメモリはブート ROM 領域とは別のアドレス空間にマッピングされます。

ブートモードでは、コマンドおよびデータをシリアル転送してフラッシュメモリの書き替えを行います。本デバイスの SIO(SIOO)と外部ホストを接続し、外部ホスト側から本デバイスの内蔵 RAM に書き替えプログラムをコピーし、RAM 上の書き替えルーチンを実行してフラッシュメモリの書き替えを行います。書き替えルーチンは、ホスト側からコマンドおよび書き替えデータを送出することにより実行します。ホスト側との通信の詳細は後述のプロトコルに従ってください。RAM へのプログラム転送は、ユーザーの ROM データ、セキュリティ確保のため、実行に先立ちユーザーパスワードの照合を行います。パスワードが一致しない場合は、RAM 転送そのものが実行されません。なお、シングルブートモードでもユーザーブートモードと同様、割り込み禁止状態で行います。シングルボートモード時、ブート ROM プログラムは NORMAL モードで動作します。

シングルチップモード(通常動作モード)中に誤ってフラッシュメモリの内容を書き替えないよう、書き替え処理が完了したら必要なブロックにプロテクトをかけておくことを推奨します。

#### シングルブートモード

(2-A) 内蔵ブート ROM の書き替えアルゴリズムを利用する場合

#### (Step-1)

フラッシュメモリの状態は旧バージョンのユーザープログラムが書かれた状態でも、消去されている状態でも構いません。書き替えルーチン、書き替えデータなどの転送は SIO (ch0) を経由して行いますので、ボード上で本デバイスの SIOO (ch0) と外部ホストとをつなげます。書き替えを行うための (a) 書き替えルーチンはホスト上に用意します。

#### (Step-2)

ブートモードの端子条件設定でリセットを解除し、ブート ROM で起動します。ブートモードの手順に従い、SIO を経由して転送元(ホスト)より(a) 書き替えルーチンの転送を行いますが、最初にユーザーアプリケーションプログラム上に記録されているパスワードとの照合を行います。(フラッシュメモリが消去されている状態でも、消去データ(FFH)をパスワードとして照合を行います。)

#### (Step-3)

パスワードの照合が終了すると、転送元(ホスト)から(a)書き替えルーチンを転送します。ブート ROM はそのルーチンを内部 RAM にロードします。ただし、RAM 上のアドレス  $0xFFFF\_8000\sim0xFFFF\_CFFF$  の範囲に格納してください。

## (Step-4)

RAM 上の (a) 書き替えルーチンへジャンプし、旧ユーザーアプリケーションプログラムエリアの消去を行います。(ブロック単位もしくは一括)

#### (Step-5)

さらに、RAM 上の(a) 書き替えルーチンを実行して、転送元(ホスト)より新ユーザーアプリケーシションプログラムのデータをロードし、フラッシュメモリの消去したエリアに書き込みを行います。書き込みが完了したら、ユーザープログラムエリアのライトプロテクトをオンにします。

下の例の場合、書き替えルーチンを転送したときと同じホストおよび SIO 経由で書き替えデータも転送されていますが、RAM 上で動作を開始した以降では、ユーザー独自にデータバスおよび転送元を設定することもできます。方法に応じて、ボードのハードおよび書き替えルーチンを組み立ててください。

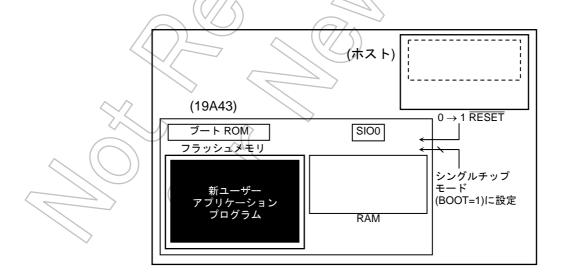

#### (Step-6)

書き込みが完了したら、一度ボードの電源を落とし、ホストと接続していたケーブルをはずします。この後、再度電源を入れ直し、シングルチップモード(ノーマルモード)起動し、新しいユーザーアプリケーションプログラムを実行します。

#### (1)モード設定

オンボードプログラミングを実行するためには、本デバイスをシングルブートモードで立ち上げます。シングルブートモードで立ち上がるための設定を以下に示します。

$\overline{\text{BOOT}} = 0$   $\overline{\text{RESET}} = 0 \to 1$

RESET 入力端子を "0" の状態にして、BOOT の各端子をあらかじめ上記条件に設定します。その後 RESET 解除を行うとシングルブートモードで起動します。

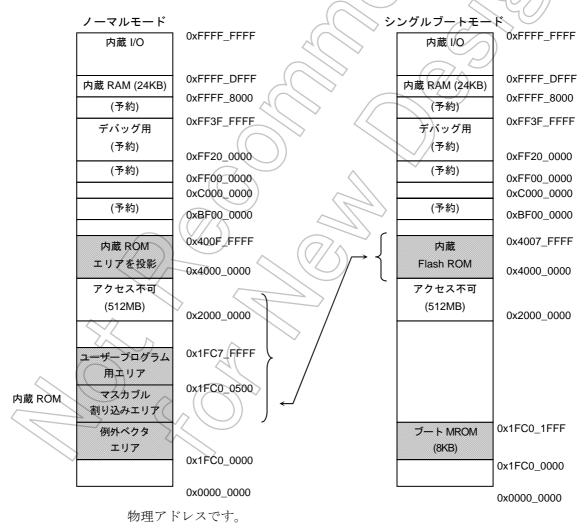

#### (2) メモリマップ

図 2--3 にシングルチップモードとシングルブートモードのメモリマップの比較を示します。図のように、シングルブートモードでは、内蔵フラッシュメモリは物理アドレス (0x4000\_0000~0x4007\_FFFF 番地)、仮想アドレス (0x0000\_0000~0x0007\_FFFF 番地) にマッピングされます。また、0x1FC0\_0000 番地から 0x1FC0\_1FFF 番地にはブート ROM (マスク ROM) がマッピングされます。

図 2-3 メモリマップの比較

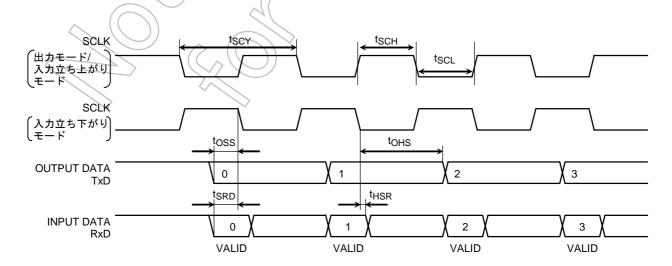

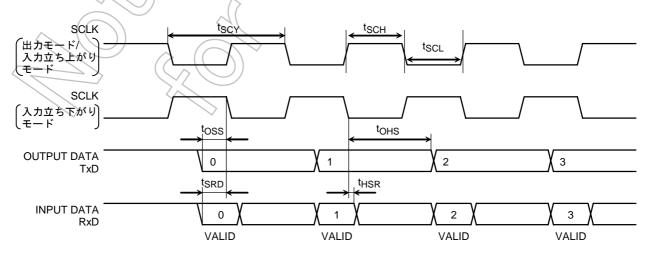

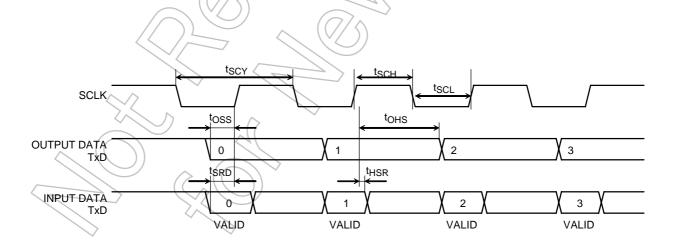

#### (3) インタフェース仕様

シングルブートモードでの SIO 通信フォーマットを以下に示します。シリアル動作のモードは、UART(非同期通信)と I/O インタフェースモード両方に対応しています。オンボードプログラミングを実行するためには、書き込みコントローラ側の通信フォーマットも同様に設定する必要があります。

UART で通信する場合

通信チャネル : SIO チャネル 0

シリアル転送モード: UART (非同期通信) モード、全二重通信、LSB ファスト

データ長: 8 ビットパリティビット: なしSTOP ビット: 1 ビット

ボーレート: 任意のボーレート

▶ I/O インタフェースモードで通信する場合

通信チャネル : SIO チャネル 0

シリアル転送モード : I/O インタフェースモード、半二重通信、LSB ファスト

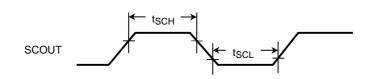

同期信号 (SCLK0) : 入力

ハンドシェイク端子: 出力ポード P67ボーレート: 任意のボーレート

表.5 端子の接続

| עֿ      | 湍 子    |       | インタフェース        |  |  |  |

|---------|--------|-------|----------------|--|--|--|

|         |        | ⊎ART  | 1/0 インタフェースモード |  |  |  |

| 電源系端子   | DVCC15 |       | 0              |  |  |  |

|         | DVSS   | 0     | 0              |  |  |  |

| モード設定端子 | BOOT   | 0     | 0              |  |  |  |

| リセット端子  | RESET  | 0     | 0              |  |  |  |

| 通信端子    | TXD0   |       | 0              |  |  |  |

|         | RXD0   | 0     | 0              |  |  |  |

|         | SCLK0  | ×     | ○ (入力モード)      |  |  |  |

|         | P67    | (7×\) | 〇 (出力ポート)      |  |  |  |

#### (4) データ転送フォーマット

動作コマンド、および各動作モード時のデータ転送フォーマットをそれぞれ表.6 ~ 表.10に示します。後述の「ブートプログラム動作説明」とあわせてお読みください。

表.6 動作コマンドデータ

| 動作コマンドデータ | 動作モード        |  |  |

|-----------|--------------|--|--|

| () (OH)   | RAM 転送       |  |  |

| 20H       | フラッシュメモリ SUM |  |  |

| 30H       | 製品情報読み出し     |  |  |

## 表.7 シングルブートプログラムの転送フォーマット [RAM 転送の場合]

|          | 転送バイト数       | コントローラ→本デバイスへの<br>転送データ           | ボーレート                           | 本デバイス→コントローラへの<br>転送データ            |

|----------|--------------|-----------------------------------|---------------------------------|------------------------------------|

| ブート ROM  | 1 バイト目       | シリアル動作モード&ボーレート設定                 | 指定された                           |                                    |

| J I KOWI | 17511 1      | UART の場合 86H                      | ボーレート *1                        | _                                  |

|          |              | I/O インタフェースの場合 30H                |                                 |                                    |

|          | 2 バイト目       | _                                 |                                 | シリアル動作モードに対する ACK 応答<br>UART の場合   |

|          |              |                                   |                                 | 正常(設定可能)の場合 86H (ボーレートの設定が不可能と判断した |

|          |              |                                   | ^                               | 場合は動作停止)<br>I/O インタフェースの場合         |

|          |              |                                   |                                 | 正常の場合 30H                          |

|          | 3 バイト目       | 動作コマンドデータ (10H)                   | (                               | _                                  |

|          | 4 バイト目       | _                                 | \                               | 動作コマンドに対する ACK 応答 *2               |

|          |              |                                   |                                 | 正常の場合 30H<br>異常の場合 × 1H            |

|          |              |                                   | 4                               | 通信異常の場合 × 8H                       |

|          | 5 バイト目       | PASS WORD データ (12 バイト)            |                                 |                                    |

|          | ~<br>16 バイト目 | (0x0000_0474~0x0000_047F)         | $( \langle \langle \rangle ) )$ | $\diamond$ (O)                     |

|          | 17 バイト目      | 5 ~ 16 バイト目の CHECK SUM 値          |                                 | ~~~                                |

|          | 18 バイト目      |                                   |                                 | CHECK SUM 値に対する ACK 応答 *2          |

|          |              | $\langle \langle \rangle \rangle$ | , ,                             | 正常の場合 10H                          |

|          |              |                                   |                                 | 異常の場合 x1H<br>通信異常の場合 x8H           |

|          | 19 バイト目      | RAM 格納開始アドレス 31 ~ 24              | $\triangleright$                | 世間共市の場合 XON                        |

|          | 20 バイト目      | RAM 格納開始アドレス 23 ~ 16              |                                 |                                    |

|          | 21 バイト目      | RAM 格納開始アドレス 15~8                 |                                 | _                                  |

|          | 22 バイト目      | RAM 格納開始アドレス 7 ~ 0                |                                 | _                                  |

|          | 23 バイト目      | RAM 格納バイト数 15~8                   |                                 |                                    |

|          | 24 バイト目      | RAM 格納バイト数 7~0                    |                                 | // –                               |

|          | 25 バイト目      | 19~24 バイト目の CHECK SUM 値           |                                 |                                    |

|          | 26 バイト目      |                                   |                                 | CHECK SUM 値に対する ACK 応答 *2          |

|          |              |                                   | 165                             | 正常の場合 10H<br>異常の場合 x1H             |

|          |              | (0)                               |                                 | 通信異常の場合 x8H                        |

|          | 27 バイト目      | RAM 格納データ                         |                                 | _                                  |

|          | ~<br>m バイト目  |                                   |                                 |                                    |

|          | m + 1 バイト目   | 27~m バイト目の CHECK SUM 値            |                                 | _                                  |

|          | m + 2 バイト目   |                                   |                                 | CHECK SUM 値に対する ACK 応答 *2          |

|          |              |                                   |                                 | 正常の場合 10H                          |

|          | \$2          |                                   |                                 | 異常の場合 x1H<br>通信異常の場合 x8H           |

| RAM      | m + 3 バイト目   | ) ( <del>\</del>                  | 1                               | JUMP RAM 格納開始アドレス                  |

- \*1: J/O インタフェースモードの場合、1 バイト目と2 バイト目のボーレートは、指定されたボーレート ÷ 16 で行ってください。

- \*2: 異常応答後は、動作コマンド (3 バイト目) 待ちになります。I/O インタフェースモードの場合は、通信異常の場合は発生しません。

- \*3: 19 バイト目~25 バイト目のデータは、RAM 上のアドレス 0xFFFF\_8000~0xFFFF\_CFFF の領域内に納まるようにプログラムしてください。

表.8 ブートプログラムの転送フォーマット [フラッシュメモリ SUM の場合]

|         | 転送バイト数 | コントローラ→本デバイスへの<br>転送データ | ボーレート    | 本デバイス→コントローラへの<br>転送データ |

|---------|--------|-------------------------|----------|-------------------------|

|         |        | 転送ナータ                   |          | 転送ナータ                   |

| ブート ROM | 1 バイト目 | シリアル動作モード&ボーレート設定       | 指定された    | _                       |

|         |        | UART の場合 86H            | ボーレート *1 | ^                       |

|         |        | I/O インタフェースの場合 30H      |          |                         |

|         | 2 バイト目 | _                       |          | シリアル動作モードに対する ACK 応答    |

|         |        |                         |          | UART の場合                |

|         |        |                         |          | 正常(設定可能)の場合 86H         |

|         |        |                         |          | (ボーレートの設定が不可能と判断した      |

|         |        |                         |          | 場合は動作停止)                |

|         |        |                         |          | I/O インタフェースの場合          |

|         |        |                         | (        | 正常の場合 30H               |

|         | 3 バイト目 | 動作コマンドデータ (20H)         |          |                         |

|         | 4 バイト目 | _                       |          | 動作コマンドに対する ACK 応答 *2    |

|         |        |                         | 4(       | 正常の場合 30H               |

|         |        |                         |          | 異常の場合 x1H               |

|         |        |                         | (0)      | 通信異常の場合 x8H             |

|         | 5 バイト目 | _                       |          | SUM (上位)                |

|         | 6 バイト目 | _ (                     |          | SUM (下位)                |

|         | 7 バイト目 | _                       |          | 5~6 バイト目の CHECK SUM 値   |

|         | 8 バイト目 | (次の動作コマンドデータ待ち)         |          |                         |

\*1: I/O インタフェースモードの場合、1 バイト目と2 バイト目のボーレートは、指定されたボーレート ÷ 16 で行ってください。

\*2: 異常応答後は、動作コマンド(3 バイト目)待ちになります。I/O インタフェースモードの場合は、通信異常の場合は発生しません。

## 表.9 ブートプログラムの転送フォーマット [デバイス情報読み出しの場合] (1/2)

|         | 転送バイト数             | コントローラ→本デバイスへの<br>転送データ | ボーレート                                    | 本デバイス→コントローラへの<br>転送データ              |

|---------|--------------------|-------------------------|------------------------------------------|--------------------------------------|

| ブート ROM | 1 バイト目             | シリアル動作モード&ボーレート設定       | 指定された                                    | +4,62.7 7                            |

| J-F ROM | 17/17日             | UART の場合 86H            | ガルシャル *1                                 | _                                    |

|         |                    | I/O インタフェースの場合30H       | /\ \ \ \   \   \   \   \   \     \     \ | ^                                    |

| ŀ       | 2 バイト目             |                         |                                          | シリアル動作モードに対する ACK 応答                 |

|         | 27311 日            |                         |                                          | UARTの場合                              |

|         |                    |                         |                                          | 正常(設定可能)の場合 86H                      |

|         |                    |                         |                                          | (ボーレートの設定が不可能と判断した                   |

|         |                    |                         |                                          | 場合は、動作停止)                            |

|         |                    |                         |                                          | I/O インタフェースの場合                       |

|         |                    |                         |                                          | 正常の場合 30H                            |

|         | 3 バイト目             | 動作コマンドデータ (30H)         |                                          | _                                    |

|         | 4 バイト目             | _                       |                                          | 動作コマンドに対する ACK 応答 *2                 |

|         |                    |                         |                                          | 正常の場合 10H                            |

|         |                    |                         | $\sim$ (                                 | 異常の場合 × 1H                           |

|         | - % =              |                         |                                          | 通信異常の場合 ×8H                          |

|         | 5 バイト目             | _                       |                                          | フラッシュメモリデータ(0×4000_0470 番地)          |

|         | 6 バイト目             | _                       |                                          | フラッシュメモリデータ(0x4000_0471 番地)          |

|         | 7 バイト目             | _                       |                                          | フラッシュメモリデータ(0×4000_0472 番地)          |

|         | 8 バイト目             | _                       |                                          | フラッシュメモリデータ(0×4000_0473 番地)          |

|         | 9 バイト目             | _                       | 2( >>                                    | 製品名(アスキーコート、12 バイト)                  |

|         | ~<br>20 バイト目       | 4                       |                                          | 9 バイト自から 'TX1943FD '                 |

| •       | 21 バイト目            | _                       | ·                                        | Password 比較開始アドレス (4 バイト)            |

|         | ~                  |                         |                                          | 21 バイト目から 74H, 04H, 00H, 00H         |

|         | 24 バイト目            |                         | $\rightarrow$                            | 217(1) [13] 5 7411, 6411, 6611, 6611 |

|         | 25 バイト目            | - 4()                   |                                          | RAM 開始アドレス (4 バイト)                   |

|         | ~                  |                         |                                          | 25 バイト目から 00H,80H, FFH, FFH          |

|         | 28 バイト目            |                         |                                          |                                      |

|         | 29 バイト目            | - (( ))                 |                                          | ダミーデータ(4 バイト)                        |

|         | ~<br>32 バイト目       |                         | ^                                        | 29 バイト目から FFH, 8FH, FFH, FFH         |

| •       | 33 バイト目            |                         |                                          | RAM 終了アドレス (4 バイト)                   |

|         | ~                  |                         | (6)                                      | 33 バイト目から FFH, DFH, FFH, FFH         |

|         | 36 バイト目            |                         |                                          | 3111,311,111,111                     |

|         | 37 バイト目            |                         |                                          | ダミーデータ(4 バイト)                        |

|         | ~                  |                         | 7                                        | 37 バイト目から 00H, 90H, FFH, FFH         |

|         | 40 バイト目            |                         | ( ) )                                    |                                      |

|         | 41 バイト目            |                         |                                          | ダミーデータ(4 バイト)                        |

|         | ~<br>44 バイト目       |                         | >                                        | 41 バイト目から FFH, CFH, FFH, FFH         |

| •       | 45 バイト目            |                         |                                          | FUSE 情報 (2 バイト)                      |

|         | ~                  | _                       |                                          | 45 バイト目から 00H, 00H                   |

|         | 46 バイト目            |                         |                                          | le variable de la confessione        |

|         | 47 バイト目            | (                       |                                          | フラッシュメモリ開始アドレス (4 バイト)               |

|         | ~ ( )              |                         |                                          | 47 バイト目から 00H, 00H, 00H, 00H         |

| 1       | 50 バイト目            |                         |                                          |                                      |

|         | 51 バイト目            |                         |                                          | フラッシュメモリ終了アドレス (4 バイト)               |

| < 4     | ~<br>54 バイト日       |                         |                                          | 51 バイト目から FFH, FFH, 07H, 00H         |

|         | 54 バイト目<br>55 バイト目 |                         |                                          | フラッシュメモリブロック分割数情報                    |

|         | ~                  |                         |                                          | (2 バイト)                              |

|         | ~<br>56 バイト目       | ~                       |                                          | 55 バイト目から 04H, 00H                   |

|         | 57 バイト目            | _                       |                                          | フラッシュメモリ同一ブロックサイズの                   |

|         | ~                  |                         |                                          | 開始アドレス (4 バイト)                       |

|         | 60 バイト目            |                         |                                          | 57 バイト目から 00H, 00H, 00H              |

|         |                    | l                       |                                          | от тапа у обт, обт, обт, обт         |

|         | 転送バイト数       | コントローラ→本デバイスへの<br>転送データ | ボーレート | 本デバイス→コントローラへの<br>転送データ                      |

|---------|--------------|-------------------------|-------|----------------------------------------------|

| ブート ROM | 61 バイト目<br>~ | _                       |       | フラッシュメモリ同一ブロックサイズの<br>サイズ (ハーフワード表現) (4 バイト) |

|         | 64 バイト目      |                         |       | 61 バイト目から 00H, 00H, 01H, 00H                 |

|         | 65 バイト目      | _                       |       | フラッシュメモリ同一ブロックサイズの<br>個数 (1 バイト) 04H         |

|         | 66 バイト目      | _                       |       | 5~65 バイト目の CHECK SUM 値                       |

|         | 67 バイト日      | (次の動作コマンドデータ待ち)         |       | $(\Omega/\Lambda)$                           |

表.10 ブートプログラムの転送フォーマット [デバイス情報読み出しの場合] (2/2)

- \*1: I/O インタフェースモードの場合、1 バイト目と2 バイト目のボーレートは、指定されたボーレート÷16 で行ってください。

- \*2: 異常応答後は、動作コマンド(3 バイト目)待ちになります。I/O インタフェースモードの場合は、通信異常の場合は発生しません。

#### (5) ブートプログラム

シングルブートモードで立ち上げるとブートプログラムが起動し、以下の機能を提供します。 詳細は、1) RAM 転送コマンド ~ 3) 製品情報読み出しコマンドに記載してありますので、参 照してください。

以下、特にことわりのない限りアドレスは仮想アドレスで表記します。

#### 1. RAM 転送コマンド

RAM 転送は、コントローラから送られてくるデータを内蔵 RAM へ格納します。転送が正常に終了するとユーザープログラムの実行を開始します。ユーザープログラムのサイズは、最大 36K バイト、実行開始アドレスは、RAM 格納開始アドレスになります。

この RAM 転送機能により、ユーザー独自のオンボートプログラミング制御を行うことができます。ユーザープログラムでオンボードプログラミングを実行するためには、後章 3.5 で説明するフラッシュメモリコマンドシーケンスを使う必要があります。RAM 転送コマンドは、実行に先立ちパスワードの照合結果をチェックします。パスワードが一致していない場合、実行されません。

## 2. クラッシュメモリ SUM コマンド

フラッシュメモリ 512k バイトの SUM を計算しその結果を返します。ブートプログラムではフラッシュメモリの全エリアのデータを読み出す動作コマンドはサポートしていません。その代わりに、このフラッシュメモリ SUM コマンドがあります。SUM を読み出すことで、アプリケーションプログラムのレビジョンを管理することができます。

#### 製品情報読み出しコマンド

本デバイスの製品名やメモリ情報などを返します。デバイス情報読み出しコマンドでは、フラッシュメモリの一部エリア(0x0000\_0470~0x0000\_0473 番地)のデータを返します。フラッシュメモリ SUM コマンド以外に、このデータを用いることで、アプリケーションプログラムのレビジョンを管理することができます。

- 1) RAM 転送コマンド(表. 7参照)

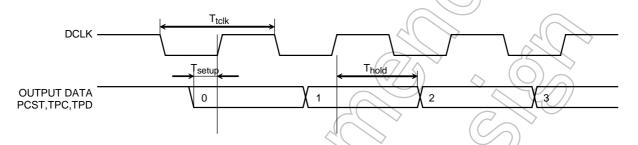

- 1. 1バイト目のデータは、シリアル動作モードを判定するデータになります。シリアルの動作モードを認める方法は、後述の「シリアル動作モード判定」を参照してください。シリアルの動作モードで UART と判定した場合は、ボーレートの設定が可能かどうかを判定します。1バイト目のデータは、受信を禁止した状態(SCOMOD<RXE> = 0)にしています。

- UART で通信を行いたい場合

UART と判定された場合

コントローラからターゲットボードへは、UART の設定で、所望のボーレートでデータを 86H にして送信してください。シリアルの動作モードの判定で UART と判定した場合、ボーレートの設定が可能かどうかを判定します。設定が不可能と判断した場合は動作を停止するため、通信が行えなくなります。ボーレートの設定が可能かどうかを判定する方法については、後述の「ボーレートの設定方法」を参照してください。

I/0 インタフェースで通信を行いたい場合

コントローラからターゲットボードへは、同期式の設定で、所望のボーレート÷

16 でデータを 30H にして送信してください。2 バイト目も同様に、所望のボーレート÷ 16 にしてください。所望のボーレートで転送するのは、3 バイト目(動作コマンドデータ)からにしてください。

I/0 インタフェースの場合、CPU が受信端子を入力ポートとして見ており、その入力ポートのレベルの変化をモニタしています。したがって、ボーレートが早い場合や動作周波数が多い場合は、CPU はレベルの変化を判別できないことがあります。これを防ぐために I/0 インタフェースの場合、ボーレートは所望のボーレート  $\div$  16 で指定します。 I/0 インタフェースと判定した場合、SCLK 入力モードになります。コントローラは、AC タイミングを満足するボーレートで送信を行ってください。 I/0 インタフェースの場合、受信エラーフラグのチェックは行いません。したがって、ACK 応答データの通信異常 ACK (bit 3) (x8H) はありません。

- 2. 2 バイト目の送信データは、1 バイト目のシリアル動作モード設定データに対する ACK 応答データになります。1 バイト目のデータが、UART と判定されボーレートの設定が可能な場合 86H を、1/0 インタフェースと判定された場合 30H を送信します。

- ボーレートの設定が可能かどうかを判定します。設定が可能と判定した場合、BROCR の値を書き替え、86H を送信し、設定が不可能と判定した場合、動作を停止するため何も送信しません。コントローラは、1 バイト目のデータの送信が終了した後、タイムアウト時間(5秒)を設けます。タイムアウト時間内に、データ(86H)を正常受信できなければ、通信不能と判断してください。受信を許可

- すした後、タイムアワト時間(5 秒)を設けます。タイムアワト時間内に、テータ(86H)を正常受信できなければ、通信不能と判断してください。受信を許可(SCOMOD〈RXE〉= 1)するタイミングは、送信バッファにデータ(86H)を書き込む前に行っています。

- I/O インタフェースと判定された場合

I/O インタフェースの設定になるように SCOMOD、SCOCR の値を書き替え、SCOBUF に 30H を書き込み、SCLKO クロックを待ちます。コントローラは、1 バイト目のデータ送信が終了した後、アイドル時間(数m秒)後、SCLK クロックを出力してください。このときのボーレートは、所望のボーレート÷16で行い、受信デ

ータが 30H なら、通信可能と判断してください。3 バイト目からは所望のボーレートで行ってください。受信を許可 (SCOMOD<RXE>= 1) するタイミングは、送信バッファにデータ (30H) を書き込む前に行っています。

- 3. 3 バイト目の受信データは、動作コマンドデータになります。この場合は、RAM 転送 コマンドデータ (10H) になります。

- 4. 4 バイト目の送信データは、3 バイト目の動作コマンドデータに対する ACK 応答データになります。最初に、3 バイト目の受信データに受信エラーがあるかをチェックします。受信エラーがある場合、通信異常の ACK 応答データ (bit 3) x8H を送信して、次の動作コマンド(3 バイト目) データ待ちになります。送信データの上位 4 ビットは、不定値になります。(直前の動作コマンドデータの上位 4 ビットになります。) なお、1/0 インタフェースの場合、受信エラーのチェックは行いません。

次に、3 バイト目の受信データが、表.6の動作コマンドデータのいずれかに該当する場合は、受信データをエコーバック送信(正常 ACK 応答データ)します。この場合、10H をエコーバック送信して RAM 転送処理ルーチンに分岐します。このルーチンに分岐後、パスワードエリアのデータをチェックします。パスワードエリアのデータのチェック方法は、後述の「パスワードについて」を参照してください。該当しない場合は、動作コマンドエラーの ACK 応答データ(bit 0)xiH を送信して、次の動作コマンド(3 バイト目)データ待ちになります。送信データの上位 4 ビットは、不定値になります。(直前の動作コマンドデータの上位 4 ビットになります。)

- 5. 5 バイト目 ~ 16 バイト目の受信データは、パスワードデータ (12 バイト) になります。5 バイト目の受信データはフラッシュメモリの 0x0000\_0474 番地のデータと照合し、6 バイト目の受信データはフラッシュメモリの 0x0000\_0475 番地のデータと照合します。同様に 16 バイト目の受信データはフラッシュメモリの 0x0000\_047F 番地のデータと照合します。一致していない場合、パスワードエラーフラグをセットします。

- 6. 17 バイト目の受信データは、CHECK SUM データになります。5 バイト目から 16 バイト目の送信データを符号なしの 8 ビット加算 (オーバフローを無視) して得られた下位 8 ビット値の 2 の補数をコントローラから送信してください。CHECK SUM データの計算方法は、後述の「CHECK SUM の計算方法」を参照してください。

- 18 バイト目の送信データは、5 バイト目 ~ 17 バイト目のデータに対する ACK 応答データ (CHECK SUM 値に対する ACK 応答) になります。最初に、5 バイト目 ~ 17 バイト目の受信データに受信エラーがあるかをチェックします。受信エラーがある場合、通信異常の ACK 応答データ (bit 3) 18H を送信して、次の動作コマンド (3 バイト目) データ待ちになります。送信データの上位 4 ビットは、直前の動作コマンドデータの上位 4 ビットになるので、"1" になります。なお、1/0 インタフェースの場合、受信エラーのチェックは行いません。

次に、17 バイト目の CHECK SUM データをチェックします。CHECK SUM データのチェック方法は、5 バイト目  $\sim$  17 バイト目までの受信データを符号なし 8 ビット加算(オーバフローを無視)して得られた値の下位 8 ビットが、00H かどうかをチェックしています。00H 以外の場合、CHECK SUM エラーの ACK 応答データ(bit0)11H を送信して、次の動作コマンド(3 バイト目)データ待ちになります。

最後に、パスワードの照合結果をチェックします。次の場合、パスワードエラーのACK 応答データ(bit 0)11H を送信して、次の動作コマンド(3 バイト目)データ待

ちになります。

- 5 バイト目~16 バイト目のパスワードデータの照合結果に関わらず、パスワードエリアの12 バイトのデータが、FFH 以外の同一データの場合。

- 5バイト目~16バイト目のパスワードデータの照合がすべてが一致しない場合。

上記のチェックを終えて、すべて正常なら、正常 ACK 応答データ 10H を送信します。

- 8. 19 バイト目 ~ 22 バイト目までの受信データは、ブロック転送における格納先の RAM の開始アドレスを表します。19 バイト目がアドレスの 31 ビット ~ 24 ビットに対応し、22 バイト目が 7 ビット ~ 0 ビットに対応します。

- 9. 23 バイト目、24 バイト目の受信データは、ブロック転送するバイト数を表します。 23 バイト目が転送バイト数の 15 ビット ~ 8 ビット目に対応し、24 バイト目が 7 ビット ~ 0 ビット目に対応します。

- 10. 25 バイト目の受信データは、CHECK SUM データになります。19 バイト目から 24 バイト目の送信データを符号なし 8 ビット加算 (オーバフローを無視) して得られた下位 8 ビット値の 2 の補数値をコントローラから送信してください。CHECK SUM データ計算方法は、後述の「CHECK SUM の計算方法」を参照してください。

- 11. 26 バイト目の送信データは、19 バイト目 ~ 25 バイト目のデータに対する ACK 応答 データ (CHECK SUM 値に対する ACK 応答) になります。最初に、19 バイト目 ~ 25 バイト目の受信データに受信エラーがあるかどうかをチェックします。受信エラーがある場合、通信異常の ACK 応答データ (bit 3) 18H を送信して、次の動作コマンド (3 バイト目) データ待ちになります。送信データの上位 4 ビットは、直前の動作コマンドデータの上位 4 ビットになるので "1" になります。なお、1/0 インタフェースの場合、受信エラーのチェックは行いません。

次に、25 バイト目の CHECK SUM データをチェックします。CHECK SUM データのチェック方法は、19 バイト目 ~ 25 バイト目までの受信データを符号なし 8 ビット加算(オーバフローを無視)して得られた値の下位 8 ビットが、00H かどうかをチェックしています。00H 以外の場合、CHECK SUM エラーの ACK 応答データ(bit 0)11H を送信して、次の動作コマンド(3 バイト目)データ待ちになります。

19 バイト目~25 バイト目のデータは RAM 上のアドレス 0xFFFD\_8000~0xFFFD\_EFFF の領域に納まるようにプログラムしてください。

上記のチェックを終えてすべて正常なら、正常 ACK 応答データ 10H を送信します。

- 12. 27 バイト目 ~ m バイト目の受信データは、RAM へ格納するデータになります。RAM に格納するデータを、19 バイト目から 22 バイト目で指定されたアドレスから書き込み、23 バイト目から 24 バイト目に指定されたバイト数分だけ書き込みます。

- 13. m + 1 バイト目の受信データは、CHECK SUM データになります。27 バイト目 ~ m バイト目の送信データを符号なし 8 ビット加算 (オーバフローを無視) して得られた下位 8 ビット値の 2 の補数をコントローラから送信してください。CHECK SUM データの計算方法は、後述の「CHECK SUM の計算方法」を参照してください。

- 14. m + 2 バイト目の送信データは、27 バイト目~1 バイト目のデータに対する ACK 応答データ (CHECK SUM に対する ACK 応答) になります。最初に 27 バイト目~ m + 1 バイト目の受信データに受信エラーがあるかどうかをチェックします。受信エラーがある場合、通信異常の ACK 応答データ (bit 3) 18H を送信して、次の動作コマンド (3 バイト目) データ待ちになります。送信データの上位 4 ビットは、直前の動作コマンドデータの上位 4 ビットになるので "1" になります。なお、1/0 インタフェースの場合、受信エラーのチェックは行いません。

次に、m+1 バイト目の CHECK SUM データをチェックします。CHECK SUM データのチェック方法は、27 バイト目  $\sim m+1$  バイト目までの受信データを符号なし 8 ビット加算(オーバフローを無視)して得られた値の下位 8 ビットが、00H かどうかをチェックしています。00H 以外の場合、CHECK SUM エラーの ACK 応答データ(bit 0) 11H を送信して、次の動作コマンド(3 バイト目)データ待ちになります。上記のチェックを終えてすべて正常なら、正常 ACK 応答データ 10H を送信します。

15. m + 2 バイト目の ACK 応答データが正常 ACK 応答データの場合、正常 ACK 応答データ 10H を送信後、19 バイト目 ~ 22 バイト目で指定されたアドレスに分岐(32 ISA)します。

- 2) フラッシュメモリ SUM コマンド (表. 8参照)

- 1. 1 バイト目  $\sim 2$  バイト目までの送受信データは RAM 転送コマンドの場合と同一になります。

- 2. 3 バイト目の受信データは動作コマンドデータになります。この場合は、フラッシュメモリ SUM コマンドデータ (20 H) になります。

- 3. 4 バイト目の送信データは、3 バイト目の動作コマンドデータに対する ACK 応答データになります。最初に、3 バイト目の受信データに受信エラーがあるかをチェックします。受信エラーがある場合、通信異常の ACK 応答データ (bit 3) x8H を送信して、次の動作コマンド (3 バイト目) データ待ちになります。送信データの上位 4 ビットは不定値になります。(直前の動作コマンドデータの上位 4 ビットになります。) なお、1/0 インタフェースの場合、受信エラーのチェックは行いません。

次に、3 バイト目の受信データが、表 6の動作コマンドデータのいずれかに該当する場合は、受信データをエコーバック送信(正常 ACK 応答データ) します。この場合、20H をエコーバック送信して、フラッシュメモリ SUM 処理ルーチンに分岐します。該当しない場合は、動作コマンドエラーの ACK 応答データ (bit 0) x1H を送信して、次の動作コマンド (3 バイト目) データ待ちになります。送信データ上位 4 ビットは不定値になります。(直前の動作コマンドデータの上位 4 ビットになります。)

- 4. 5 バイト目の送信データは SUM 値の上位データ、6 バイト目の送信データは SUM 値の下位データになります。SUM の計算方法は、後述の「SUM の計算方法」を参照してください。

- 5. 7 バイト目の送信データは、CHECK SUM データになります。5 バイト目から 6 バイト目の送信データを符号なし 8 ビット加算 (オーバフローを無視) を行い、得られた下位 8 ビット値の 2 の補数を送信します。

- 6. 8 バイト目の受信データは、次の動作コマンドデータになります。

- 3) 製品情報読み出しコマンド(参照)

- 1. 1 バイト目~2 バイト目までの送受信データは RAM 転送コマンドの場合と同一になります。

- 2. 3 バイト目の受信データは、動作コマンドデータになります。この場合は、製品情報 読み出しコマンドデータ (30H) になります。

- 3. 4 バイト目の送信データは、3 バイト目の動作コマンドデータに対する ACK 応答データになります。最初に、3 バイト目の受信データに受信エラーがあるかどうかをチェックします。受信エラーがある場合、通信異常の ACK 応答データ (bit 3) x8H を送信して、次の動作コマンド(3 バイト目) データ待ちになります。送信データの上位4 ビットは不定値になります。(直前の動作コマンドデータの上位4 ビットになります。) なお、1/0 インタフェースの場合、受信エラーのチェックは行いません。

次に、3 バイト目の受信データが、表 6の動作コマンドデータのいずれかに該当する場合は、受信データをエコーバック送信(正常 ACK 応答データ)します。この場合、30H をエコーバック送信して、製品情報読み出し処理ルーチンに分岐します。該当しない場合は、動作コマンドエラーの ACK 応答データ (bit 0) x1H を送信して、次の動作コマンド(3 バイト目)データ待ちになります。送信データの上位 4 ビットは不定値になります。(直前の動作コマンドデータの上位 4 ビットになります。)

- 4. 5 バイト目 ~ 8 バイト目の送信データは、フラッシュメモリのデータ (0x0000\_0470 番地~0x0000\_03F3 番地のデータ) になります。この番地にソフトなどの ID 情報を書き込んでおくことにより、書き込んだソフトのバージョン管理をすることができます。

- 5. 9 バイト目 ~ 20 バイト目の送信データは製品名になります。9 バイト目から、アスキーコードで、 'TX1943FD\_ \_ \_' を送信します。

- 6. 21 バイト目 ~ 24 バイト目の送信データはパスワード比較開始アドレスになります。 21 バイト目から、F4H、03H、00H、00H を送信します。

- 7. 25 バイト目 ~ 28 バイト目の送信データは RAM 開始アドレスになります。25 バイト 目から、00H、80H、FDH、FFH を送信します。

- 8. 29 バイト目 ~ 32 バイト目の送信データはダミーデータになります。29 バイト目から、FFH、8FH、FDH、FFH を送信します。

- 9. 33 バイト目 ~ 36 バイト目の送信データは RAM 終了アドレスになります。33 バイト 目から、FFH、FFH、FDH、FFH を送信します。

- 37 バイト目 ~ 40 バイト目の送信データは、00H、90H、FDH、FFH になります。

41 バイト目 ~ 44 バイト目の送信データは、FFH、EFH、FDH、FFH になります。

- 11. 45 バイト目~46 バイト目の送信データは、セキュリティビットやプロテクトビットの有無やフラッシュメモリがブロック分割されているかどうかを各ビットに割り付けたデータにります。0 ビット目は、セキュリティビットの有無を示します。 "0" はセキュリティビットがあることを、"1" はセキュリティビットがないことを示します。1 ビット目は、プロテクトビットの有無を示します。 "0" はプロテクトビット

があることを、"1" はプロテクトビットがないことを示します。2 ビット目は、フラッシュメモリがブロック分割されているかどうかを示します。"0" は分割されていることを、"1" は分割されていないことを示します。3 ビット目  $\sim$  15 ビット目は未定義です。45 バイト目から、01H、00H を送信します。

- 12. 47 バイト目~50 バイト目の送信データは、フラッシュメモリ開始アドレスになります。47 バイト目から、00H、00H、00H、00Hを送信します。

- 13. 51 バイト目~54 バイト目の送信データは、フラッシュメモリ終了アドレスになります。51 バイト目から、FFH、FFH、07H、00H を送信します。

- 14. 55 バイト目  $\sim 56$  バイト目の送信データは、フラッシュメモリのブロック分割数になります。55 バイト目から、04H、00H を送信します。

- 15. 57 バイト目~92 バイト目の送信データは、フラッシュメモリのブロック情報になります。ブロック情報は、フラッシュメモリ開始アドレスから見たとき、同一ブロックサイズが何ブロック続いているかを一単位とし、同一ブロックサイズの先頭の開始アドレスとブロックサイズ(ハーフワード単位) およびブロックの個数で表します。

57 バイト目~65 バイト目の送信データは、128k バイトのブロック (Block0~Block3) を を表します。送信データについては、を参照してください。

- 16. 66 バイト目の送信データは、CHECK SUM データになります。5 バイト目から 65 バイト目の送信データを符号なし 8 ビット加算 (オーバフローを無視) して、得られた下位 8 ビット値の 2 の補数を送信します。

- 17. 67 バイト目の受信データは、次の動作コマンドデータになります。

#### 4) ACK 応答データ

ブートプログラムは処理状況を各種コードによってコントローラに送信します。表 11から表 13に各受信データに対する ACK 応答データを示します。ACK 応答データの上位 4 ビットは、動作コマンドデータの上位 4 ビットになります。また 3 ビット目は受信エラーを表し、0 ビット目は動作コマンドエラー、CHECK SUM エラー、パスワードエラーの状態を表します。1 ビット目と 2 ビット目は常に 0 になります。なお、I/O インタフェースの場合、受信エラーのチェックは行いません。

表11 シリアル動作判定データに対する ACK 応答データ

| 送信データ | 送信データの意味                 |

|-------|--------------------------|

| 0x86  | UART での通信が可能と判定した。 *1    |

| 0x30  | I/O インタフェースでの通信が可能と判定した。 |

\*1: UART の場合、ボーレートの設定が不可能と判定したら、何も送信しないで動作を停止します。

表12 動作コマンドデータに対する ACK 応答データ

| 送信データ   | 送信データの意味                |

|---------|-------------------------|

| 0x?8 *1 | 動作コマンドデータに受信エラーが発生した。   |

| 0x?1 *1 | 未定義の動作コマンドデータを正常受信した。   |

| 0x10    | RAM 転送コマンドと判定した。        |

| 0x20    | フラッシュメモリ SUM コマンドと判定した。 |

| 0x30    | 製品情報読み出しコマンドと判定した。      |

\*1: 上位 4 ビットは、直前の動作コマンドデータの上位 4 ビットになります

表 13 CHECK SUM データに対する ACK 応答データ

| 送信データ   | 送信データの意味                               |

|---------|----------------------------------------|

| 0xN8 *2 | 受信エラーが発生していた。                          |

| 0xN1 *2 | CHECK SUM エラーが発生した。あるいは、パスワードエラーが発生した。 |

| 0xN0 *2 | CHECK SUM 値は正常な値と判定した。                 |

\*2: 上位 4ビットは動作コマンドデータの上位 4ビットになります。例えば、パスワードエラ一発生時は 1( N=RAM 転送コマンドデータ[7:4] )となります。

#### 5) シリアル動作モード判定

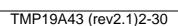

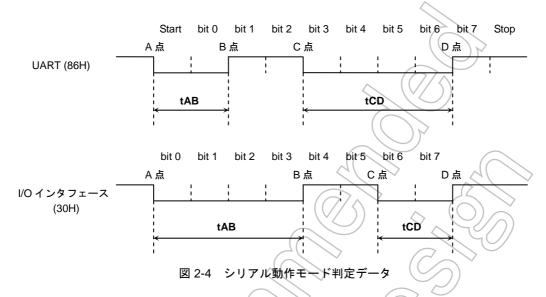

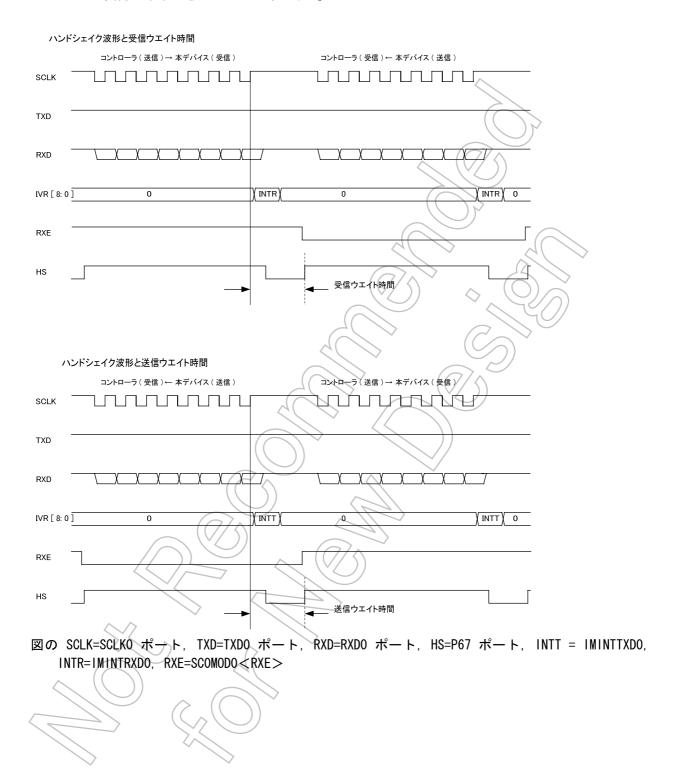

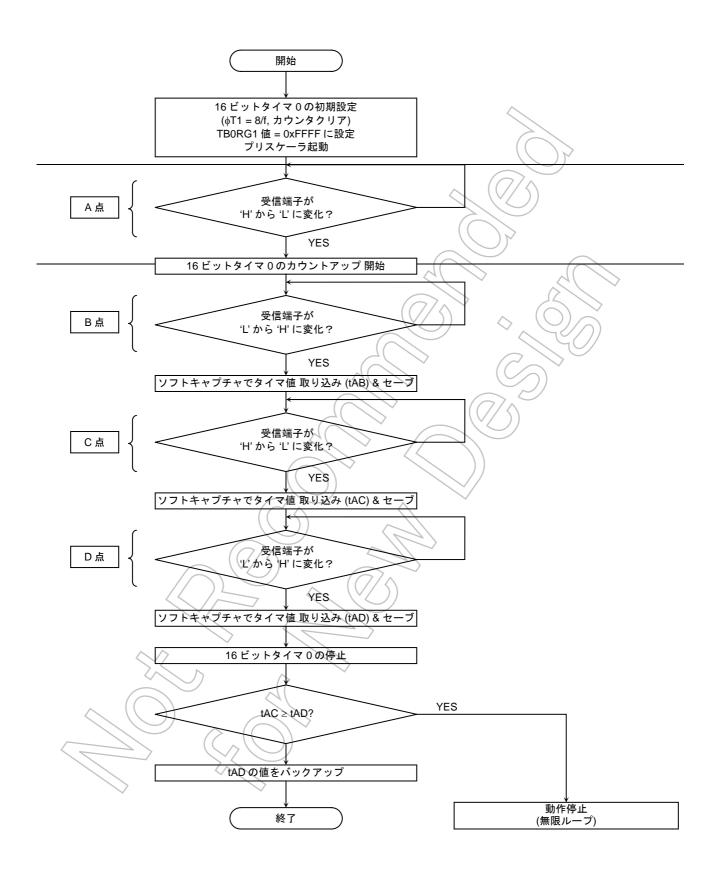

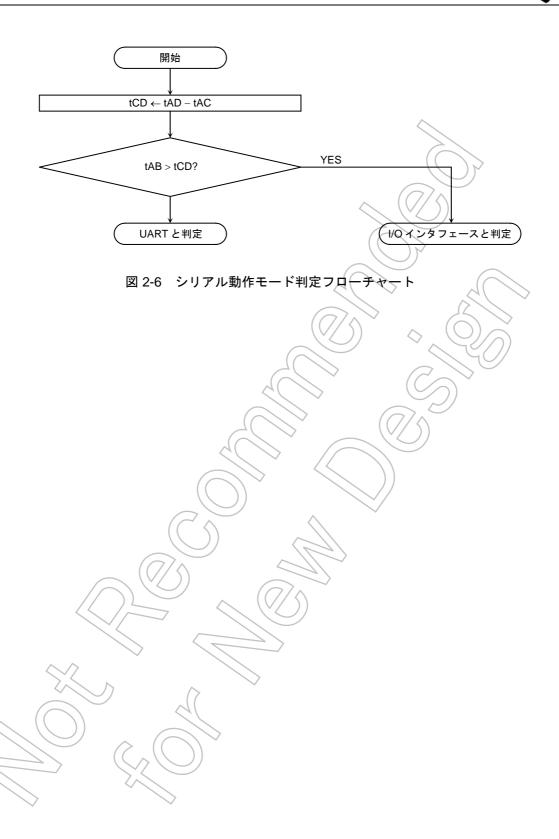

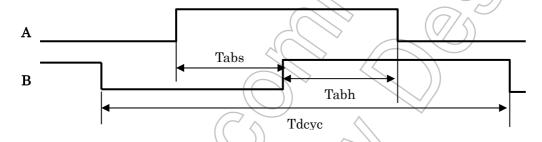

コントローラは、UART で通信したい場合、所望のボーレートで 1 バイト目を 86H にし、I/O インタフェースで 通信したい場合、所望のボーレート ÷ 16 で 1 バイト目を 30H にして送信してください。図 **2-4**にそれぞれの場合の波形を示します。

ブードプログラムは、リセット解除後の 1 バイト目のシリアル動作モード判定データ (86H、30H) を受信禁止状態にして、図 2-5 に示すフローチャートで、図 2-4の tAB、tAC と、tAD の時間を求めています。図 2-5 のフローチャートに示すように、CPU が受信端子のレベルをモニタしてレベルの変化があると、そのときのタイマ値を取り込みます。このため、tAB、tAC と、tAD のタイマ値には誤差が生じます。また、ボーレートが速いときには、CPU は受信端子のレベルの変化を判断できない場合がありますので注意してください。特に、I/O インタフェースは UART に比べボーレートが速いため、このような場合が発生しやすくなります。このようなことが起こらないようにするために、I/O インタフェースの場合、コントローラのボーレートは所望ボーレート ÷ 16 にして送信してください。

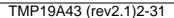

同期式通信を行う場合、1 バイト目の通信波形は tAB > tCD を満足していれば、30H である必要はありません。ただし、1 バイト目は SIO(ch0) 機能を使用していないため、シリアルクロック (SCLKO) を認識しません。 A 点立下りを確実に認識させるために RESET 後すぐに"1"を RXDO 端子に入力してください。同期式通信が選択された場合、2 バイト目の通信データは、1 バイト目のデータによらず 30H となります。下図例で同期式が選択された場合、1 バイトデータの通信中でも D 点立ち上がり以降にハンドシェーク端子が"H"出力され、2 バイト目のシリアルクロックを待ちます。このため 1 バイト目にシリアルクロックを入力する場合は、2 バイト目のシリアルクロックと判定しないようなデータ (波形) として入力する必要があります。

1バイト目の送信データ= 0x30

図の RXD=RXD0 ポート, HS=P67 ポート

図 2-5 のフローチャートに示すように、シルアル動作モードの判定は、受信端子が "L" レベルのときの時間幅の大小関係で判定しています。tAB < tCD の場合 UART と判定し、ボーレートの自動設定が可能かどうかを tAD の時間から判定します。tAB > tCD の場合、I/O インタフェースと判定します。なお、先に述べたように、tAB、tAC、tAD のタイマ値には誤差が生じているため、ボーレートが速く、動作周波数が遅い場合、各タイマ値が小さくなり、意図しない判断を行うことがありますので注意してください。

例えば、コントローラは UART で通信したいのに、I/O インタフェースと判定してしまうことがあります。このようなことを考慮して、コントローラは UART で通信したい場合、1 バイト目のデータを送信後、タイムアウト時間内にデータ 86H を正常受信できなければ通信不可能と判断してください。また、I/O インタフェースで通信したい場合 1 バイト目のデータを送信後、アイドル時間後に SCLK クロックを出力してデータを受信し、受信データが 30H でなければ通信不可能と判断してください。

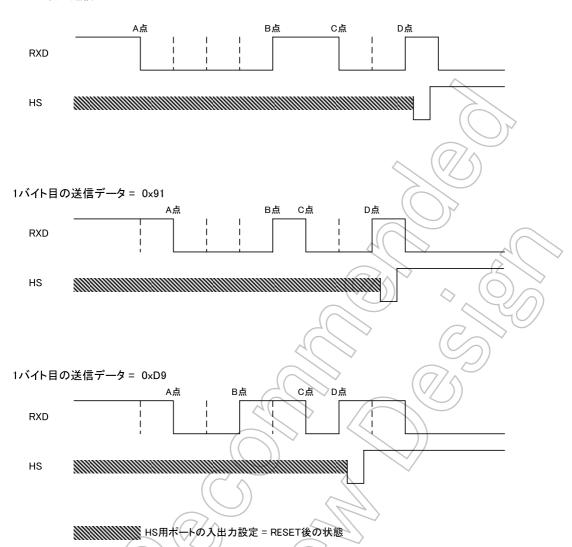

同期式通信時のハンドシェーク端子の出力値が"L"のときは通信後のデータ処理中です(送信ウエイト時間/受信ウエイト時間)。この期間にシリアルクロックを入力しても正常応答動作しません。通信可能になった場合ハンドシェーク端子を"H"出力に変えます。下図の送受信ウエイト時間は、動作周波数やボーレートによって異なります。通信後のデータ処理内容によって送受信ウエイト時間が変わります。コントローラはデータ送受信後にハンドシェーク端子が"L"出力、つい

で"H"出力になるのをモニタしてください。

図 2-5 シリアル動作モード受信フローチャート

#### 6) パスワードについて

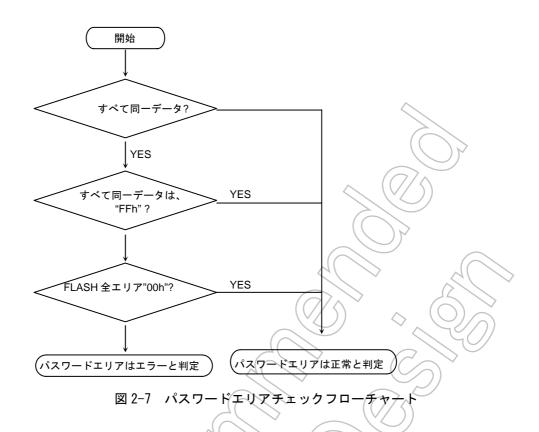

動作コマンドデータが RAM 転送コマンド (10H) の場合、パスワードのチェックを行います。まず、動作コマンドデータをエコーバック送信 (10H) 後、パスワードエリア (0x0000\_0474 番地~0x0000\_047F 番地) のデータ (12 バイト) をチェックします。

図 2-に示すようにパスワードエリアのデータが、FFH 以外の同一データになっていた場合、パスワードエリアエラーと判定します。パスワードエリアエラーと判定された場合、パスワードデータの照合結果に関わらず、17 バイト目の CHECK SUM 値に対する ACK 対応は 11H を送信します。

次に、5 バイト目 ~ 16 バイト目の受信データ (パスワードデータ) の照合を行います。表 14に対応表を示します。12 バイト分すべてが一致しないと、パスワードエラーになります。パスワードエラーと判定された場合、17 バイト目の CHECK SUM 値に対する ACK 応答は、パスワードエラーとなります。

図 2-7 に示すようにパスワードエリアのデータが、0xFF 以外の同一データになっていた場合、パスワードエリアエラーと判定します。パスワードエリアエラーと判定された場合、パスワードデータの照合結果に関わらず、 17 バイト目の CHECK SUM 値に対する ACK 対応は 0x11 を送信します

ROM セキュリティ状態では、実際のパスワードデータではなくマスクされたアドレスのデータをパスワードとして扱います。パスワードエリアのデータを使用する場合はあらかじめ ROM セキュリティ機能を解除しておきます。

表14 受信データと照合するデータの対応

|         | 照合す                | <sup>ト</sup> るデータ  |

|---------|--------------------|--------------------|

| 受信データ   | ROM プロテクト OFF      | ROM プロテクト ON       |

| 5 バイト目  | 0x0000_0474 番地のデータ | 0x0000_0004 番地のデータ |

| 6 バイト目  | 0x0000_0475 番地のデータ | 0x0000_0005 番地のデータ |

| 7 バイト目  | 0x0000_0476 番地のデータ | 0x0000_0006 番地のデータ |

| 8 バイト自  | 0x0000_0477 番地のデータ | 0x0000_0007 番地のデータ |

| 9 バイト目  | 0x0000_0478 番地のデータ | 0x0000_0000 番地のデータ |

| 10 バイト目 | 0x0000_0479 番地のデータ | 0x0000_0001 番地のデータ |

| 11 バイト目 | 0x0000_047A 番地のデータ | 0x0000_0002 番地のデータ |

| 12 バイト目 | 0x0000_047B 番地のデータ | 0x0000_0003 番地のデータ |

| 13/5イト目 | 0x0000_047C 番地のデータ | 0x0000_0004 番地のデータ |

| 14バイト目  | 0x0000_047D 番地のデータ | 0x0000_0005 番地のデータ |

| 15 バイト目 | 0x0000_047E 番地のデータ | 0x0000_0006 番地のデータ |

| 16バイト目  | 0x0000_047F 番地のデータ | 0x0000_0007 番地のデータ |

#### 7) SUM の計算方法

例)

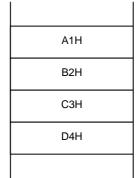

左記 4 バイトが計算対象データの場合、SUM の値は、 A1H + B2H + C3H + D4H = 02EAH

となるので、

SUM の上位のデータは、02H、

SUM の下位のデータは、EAH になります。

したがって、コントローラには 02H、EAH の順番で送信します。

## 8) CHECK SUM の計算方法

CHECK SUM の計算方法は、送信データを符号なし8ビット加算(オーバフローを無視)して得られた下位8ビット値の2の補数値を求めています。フラッシュメモリ SUM コマンド、製品情報読み出しコマンドを実行したときに返される CHECK SUM は、本計算方法を使用しています。また、コントローラは CHECK SUM 値を送信するときは、本計算方法を使用してください。

例) フラッシュメモリ SUM コマンドのときを例に説明します。

SUM の上位8ビットデータが E5H、下位8ビットデータが F6H の場合の CHECK SUM 値を求めます。

まず、符号なし8ビット加算して得られた値を求めます。

E5H + F6H = 1DBH

この値の下位 8 ビットに対しての 2 の補数をとると以下のようになり、この値が CHECK SUM 値になります。したがって、コントローラには 25H を送信します。

0 - DBH = 25H

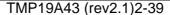

(6) ブートプログラム全体フローチャート

ブートブロクラム全体フローチャートを示します。

図 2-8 ブートプログラム全体フローチャート

## 2.3 オンボードプログラミングでのフラッシュメモリ書き込み/消去

オンボードプログラミングでは、CPUによりソフトウェア的にコマンドを実行することで、フラッシュの書き込み/消去を行います。この書き込み/消去の制御プログラムはユーザーがあらかじめ用意しておきます。フラッシュメモリの書き込み/消去を行っている間は、フラッシュメモリ自身の読み出しはできませんので、ユーザーブートモードに移行後、書き込み/消去制御プログラムは内蔵 RAM もしくは外部メモリ上で実行してください。 この章では特に断りの無い限り、フラッシュメモリを仮想アドレスで表記します。

## 2.3.1 フラッシュメモリ

一部の機能を除き、フラッシュメモリの書き込みおよび消去などは JEDEC 標準コマンドに準拠しています。書き込み、消去を行う場合、CPU の SW 命令を用いてフラッシュメモリへコマンドを入力します。コマンド入力後、書き込みおよび消去は内部で自動的に行われます。

主な機能 説 明

自動ページプログラム データ書き込みを自動で行います。

自動チップ消去 フラッシュメモリ全エリアの一括消去を自動で行います。

自動ブロック消去 ブロック単位での消去を自動で行います。(128K バイト単位)

ライトプロテクト ブロック単位(128K バイト)ごとに書き込みおよび消去を禁止することができます。

全ブロックにプロテクトを掛けると自動的にプロテクト機能が有効になります。

プロテクト機能 4 ビットのプロテクトビット書き込みによってブロックごとに書き込みおよび消去を禁止することができます。

表 2-15 フラッシュメモリの機能

ユーザーブートモードもしくは RAM 転送の詳細な動作説明は後述しますが、CPU とのインターフェースの関係上、動作コマンドのアドレス指定が標準コマンドとは異なります。また、特に断りのない限りフラッシュメモリの書き込みは 32 ビット単位で行います。フラッシュメモリへの書き込みは、32 ビット (ワード) のデータ転送命令を用いてください。

#### (2) 基本動作

このフラッシュメモリには、大きく分けて以下の2種類の動作モードがあります。

- メモリデータを読み出すモード(リードモード)

- ▶ メモリデータを自動的に消去/書き替えるモード(自動動作)

リードモード中にコマンドシーケンスを実行することで、自動動作に移ることができます。自動動作中は、フラッシュメモリデータの読み出しとフラッシュメモリ上の命令の実行ができません。自動動作中はハードウエアリセットを除いて割り込みや例外が発生した場合、リードモードに移りません。自動動作中は DSU-PROBE 接続時のデバッグ例外とリセットを除いて、全ての例外を発生させないでください。ハードウエアリセットを除いて割り込みや例外が発生した場合、リードモードに移行しません。

#### 1) リード

データを読み出す場合、フラッシュメモリをリードモードにします。電源投入直後、CPU リセット解除後および自動動作の正常終了時に、フラッシュメモリばリードモードになります。自動動作の異常終了時や、他のモードからリードモードに復帰させるには、後述する Read/リセットコマンド(ソフトウエアリセット)もしくはハードウエアリセットを用います。フラッシュメモリに書かれた命令を実行する場合もリードモードでなければなりません。

• Read/リセットコマンド 及び Read コマンド(ソフトウエアリセット)

自動動作が異常終了した場合、フラッシュメモリは自動ではリードモードに復帰しません (FLCS\RDY/BSY)="0"となっている状態では、フラッシュメモリの読み出し値は不定)。この場合、Read/リセットコマンドでフラッシュメモリをリードモードに復帰させます。また、途中までコマンドライトしたコマンドをキャンセルする場合も、Read/リセットコマンドでリードモードに復帰させる必要があります。Read コマンドは、フラッシュメモリの任意のアドレスに 0x0000\_00F0 データを SW 命令実行してリードモードに復帰するコマンドです。

- Read/リセットコマンドは第3バスライトサイクル終了後にリードモードになります。

- 2) コマンドライト

このフラッシュメモリは、コマンドコントロール方式を用いています。コマンド実行は、フラッシュメモリに対してコマンドシーケンスを実行することで行います。フラッシュメモリは、入力されたアドレスとデータの組み合わせによって各自動動作コマンドを実行します(コマンドシーケンス参照 )。

コマンドシーケンスの途中でコマンドライトをキャンセルしたい場合や、間違ったコマンドシーケンスを入力した場合は、Read/リセットコマンドを実行します。フラッシュメモリはコマンド実行を中止してリードモードになります。

各コマンドはいくつかのバスサイクルで構成されており、フラッシュメモリに対して SW 命令を実行するものを "バスライトサイクル" と呼びます。各バスライトサイクルには順番があり、フラッシュメモリはバスライトサイクルのアドレスとデータが規定の順番でコマンドライトされた時は自動動作を実施します。規定の順番でコマンドライトされなかったバスライトサイクルがあった場合にフラッシュメモリはコマンドの実行を中止してリードモードになります。各バスライトサイクルのアドレス[31:21]は、コマンドを実施する仮想アドレス[31:21]をコマンドライトします。アドレスの[20:8]に関しては後で説明します。

(注意1)各コマンドシーケンスは、フラッシュメモリ外のエリアから実施します。

- (注意 2) 本デバイスへのバスライトサイクル間隔は 15 システムクロック以上にしてください。 フラッシュメモリのコマンドシーケンサがバスライトサイクルを認識するのに必要な時間があり、この時間内に複数のバスライトサイクルが実施されたときは、正常に動作しません。使用される動作周波数でのソフトウエアタイマ等によるバスライトサイクル間隔の調整は 10) ID-Read を使用して確認してください。

- (注意 3) 各バスライトサイクルの間に、フラッシュメモリに対するロード命令 (LW, LH, LB 命令等)およびフラッシュエリアをソースアドレスに指定 して DMA 転送を実施しないでください。また、フラッシュメモリへの JUMP 命令を実行しないでください。各コマンドシーケンスの実行中にマスカブル割り込みなど、全ての割り込み(DSU-PROBE 接続時は、デバッグ例外を除く)を発生させないでください。

これらの動作により、フラッシュメモリに対して予期せぬリードアクセスが生じることになり、コマンドシーケンサがコマンドを正常に認識できない恐れがあります。各コマンドシーケンスは正常終了しない恐れがあると同時に、誤ったコマンドライトとして認識してしまう可能性が有ります。

- (注意4) 各バスライトサイクルのSW命令直後にSYNC命令を実行してください。

- (注意 5) コマンドシーケンサがコマンドを認識するために、コマンド開始前の状態がリードモードである必要があります。各コマンドシーケンスの第1バスライトサイクル前に FLCS[0]RDY/BSY = 1 であることを確認してください。続いて Read コマンドを実行することを推奨します。

- (注意6) コマンド発行時、誤ったアドレスやデータをライトした場合は、必ずシステムリセットもしくは、リセットコマンドを発行して、一度リードモードに戻して下さい。

- 3) リセット

ハードウエアリセット

本フラッシュメモリはメモリブロックとしてリセット入力を持ち、この入力は CPU のリセット信号とつながっています。このため、本デバイスの RESET 入力端子が V<sub>IL</sub> となるか、ウォッチドッグタイマのオーバフローなどにより CPU のリセットがかかると、フラッシュメモリは自動動作の実行中であってもその動作を中止し、リードモードに戻ります。また、自動動作が異常終了したときや、コマンドを用いてセットしたモードを解除するときも CPU のリセットによりリードモードへ復帰します。なお、自動動作の実行中にハードウエアリセットが入った場合は、データの書き替えが正常に行えませんので注意が必要です。再度、書き替えを行う処置をしてください。

CPUのリセット動作については、「2.2.1リセット動作」を参照してください。所定のリセット入力後、CPUはフラッシュメモリよりリセットベクタデータをリードし、リセット解除後の動作を開始します。

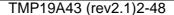

4) 自動ページプログラム

フラッシュメモリへの書き込みは、"1" データセルを "0" データにすることです。 "0" データセルを "1" データにすることはできません。 "0" データセルを "1" データにするには消去動作を行う必要があります。

本デバイスの自動ページプログラムは、128 ワードごとの書き込みとなります。この 128 ワードはアドレス [31:9] が同じで、先頭アドレス [8:0] = 0、最後のアドレス [8:0] = 0x1FF のグループです。以降はページプログラムの単位をページと呼びます。

データセルへの書き込みは、内部シーケンサで自動的に行われ、CPU による外部からの制御を必要としません。自動ページプログラムの状態 (書き込み動作中であるか) はレジスタ FLCS[0] < RDY/BSY> にて確認できます。

また、自動ページプログラム中は、新たにコマンドシーケンスを受け付けません。自動ページプログラム動作を中止したい場合は、ハードウエアリセットを用います。これにより動作を中止させた場合、該当のページに対するデータの書き込みは正常に行われていないため、消去動作後に改めて自動ページプログラムを実行する必要があります。

自動ページプログラムは消去後のページに対して1回のみ可能で、"1" データセルであっても"0" データセルであってもページに対して2回以上の実行はできません。一度書き込み動作を行ったページに対して再度書き込みを行う場合は、自動ブロック消去または自動チップ消去コマンドを行った後に自動ページプログラムを実行しなおす必要がありますのでご注意ください。消去動作を伴わない同一ページへの2回以上ページプログラム実施はデバイス破損の可能性が有ります。

本デバイス内部で自動的なベリファイ動作は行いません。正常に書き込みができたか、実 行後に読み出しをして確認してください。

自動ページプログラムは、コマンドサイクルの第4バスライトサイクル終了から開始します。第5バスライトサイクル以降は、第4バスライトサイクルで指定した次のアドレス(第4バスライトサイクルではページの先頭アドレスをコマンドライトします)から順番に書き込みを行います(データ入力は32ビット単位で行います)。第4バスサイクル以降のコマンドライトは必ずSW命令を使用してください。このときSW命令はワード境界をまたいだ位置へ実施しないでください。第5バスライトサイクル以降は同一ページェリアに対してデータをコマンドライトします。また、ページの一部に書き込みをしたい場合でもページ単位で自動ページプログラムする必要があります。この場合も第4バスライトサイクルのアドレス入力はページの先頭アドレスにしてください。この時"0"データセルにしたくない箇所は入力データを"1"にしてコマンドライトします。例えば、あるページの先頭アドレスの書き込みをしない場合、第4バスライトサイクルのデータ入力を0xFFFFFFFF としてコマンドライトします。

第4バスライトサイクルを実行すると自動プログラム動作中となります。このことはレジスタ FLCS[0] < RDY/BSY > (表 2-16)をモニタすることで確認できます。自動プログラム動作中は、新たなコマンドシーケンスを受け付けません。動作を中止する場合は、ハードウエアリセットを用います。動作を中止させた場合は、データの書き込みは正常に行えませんので注意してください。1 ページのデータをコマンドライト後、ページ自動書き込みが正常終了した時に FLCS[0] < RDY/BSY> = "1"となり、リードモードに復帰します。

複数のページに対してデータの書き込みを行うときは、ページ毎にページプログラムコマンドを実行する必要があります(1回の自動ページプログラムコマンドで書き込めるサイズは1ページです)。ページを跨ったデータ入力の自動ページプログラムは出来ません。

プロテクトされたブロックへの書き込みはできません。自動プログラムが正常終了すると、自動的にリードモードに復帰します。このことは FLCS[0] <RDY/BSY>(表 2-16)をモニタすることで確認できます。自動プログラム動作が不良となった場合は、フラッシュメモリはこのモードのままロックされ、リードモードには復帰しません。リード状態に復帰させるにはリセットコマンドかハードウエアリセットでフラッシュメモリまたはデバイスをリセットする必要があります。この場合、このアドレスへの書き込みが不良になっていますので、デバイスの使用を停止するか、以後このアドレスを含むブロックを使用しないことを推奨します。

注:自動ページプログラム第4バスライトサイクル以降のバスライトサイクルでは、ソフトウエアリセットが無効になります。

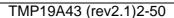

#### 5) 自動チップ消去

自動チップ消去動作は、コマンドサイクルの第6バスライトサイクル終了から開始します。

FLCS[0]<RDY/BSY>(表 2-16)をモニタすることで確認できます。本デバイス内部で自動的なベリファイ動作は行いませんので、正常に消去ができたか、実行後に読み出しをして確認してください。自動チップ消去動作中は、新たなコマンドシーケンスを受け付けません。動作を中止する場合は、ハードウエアリセットを用います。動作を中止した場合、データの消去は正常に行えないので、再度自動チップ消去を行う必要があります。

また、プロテクトされているブロックがある場合、そのブロックの消去は行いません。すべてのブロックがプロテクトされている場合は、自動チップ消去を実行せず、コマンドシーケンスの第6バスライトサイクルの完了後にリードモードになります。自動チップ消去が正常終了すると、自動的にリードモードに復帰します。自動チップ消去動作が不良となった場合は、フラッシュメモリはこのモードのままロックされ、リードモードには復帰しません。

リードモードに復帰させるにはリセットコマンドかハードウェアリセットでフラッシュメモリもしくはデバイスをリセットする必要があります。この場合は、不良が発生したブロックの検知はできません。デバイスの使用を停止するか、ブロック消去機能を利用して不良ブロックを特定し、以降不良ブロックを使用しないことを推奨します。

#### 6) 自動ブロック消去(128KB 単位)

自動ブロック消去は、コマンドサイクルの第 6 バスライトサイクル終了から開始します。 自動ブロック消去動作の状態は、FLCS[0]〈RDY/BSY〉(表 2-16)をモニタすることで確認できます。本デバイス内部で自動的なベリファイ動作は行いませんので、正常に消去ができたか、実行後に読み出しをして確認してください。自動ブロック消去中は新たなコマンドシーケンスを受け付けません。動作を中止する場合は、ハードウエアリセットを用います。この場合、データの消去は正常に行えませんので、再度自動ブロック消去を行う必要があります。

また、プロテクトされているブロックがある場合、そのブロックの消去を行いません。自動 ブロック消去動作が不良になった場合、フラッシュメモリはこのモードのままロックされ、 リードモードには復帰しません。リセットコマンドかハードウエアリセットを用いてフラッ シュメモリまたは、デバイスをリセットしてください。

## 7) 自動プロテクトビットプログラム

本デバイスは4ビットのプロテクトビットを内蔵しています。自動プロテクトビットプログラムは1ビット単位で実行できます。ビットの指定は第7バスライトサイクルで行います。自動プロテクトビットプログラムにより、ブロックごとに書き込みと消去の動作を禁止(プロテクト)することができます。各ブロックのプロテクトの状態は後で説明するFLCS〈BLPRO 3:0〉で確認できます。自動プロテクトビットプログラム動作の状態は、FLCS〈RDY/BSY〉(表 2-16)をモニタすることで確認できます。自動プロテクトビットプログラム動作中は新たなコマンドシーケンスを受け付けません。動作を中止する場合は、ハードウエアリセットを用います。この場合、プロテクトの設定は正常に行えない可能性がありますので、再度ブロックプロテクトの動作をやり直す必要があります。全てのプロテクトビットをプログラムした後は、内蔵RAM等のフラッシュメモリ以外のエリアからフラッ

シュメモリの読み出しを行うことはできません。この時 FLCS $\langle$ BLPRO 3:0 $\rangle$ = 0 x F(表 2-16) になっています(プロテクト状態)。これ以降はコマンドライトも正常に実施できません。

注:自動プロテクトビットプログラム第7バスライトサイクルでは、ソフトウェアリセットが無効になります。FLCS<RDY/BSY> は、第7バスライトサイクル入力後から、FLCS<RDY/BSY> = "0" となります。

#### 8) 自動プロテクトビット消去

プロテクトビットの状態によって、自動プロテクトビット消去コマンドの実行結果が異なります。コマンド実行前に FLCS $\langle$ BLPRO 3:0 $\rangle$  = 0xF か、それ以外の値かで決まります。自動プロテクトビット消去コマンド実施前に必ず FLCS $\langle$ BLPRO 3:0 $\rangle$ 値を確認してください。

•FLCS〈BLPRO 3:0〉 = 0xF (全てのプロテクトビットがプログラムされている)の場合 自動プロテクトビット消去コマンドをコマンドライトすると、自動的に本デバイス内部でフラッシュメモリの初期化を行います。第7バスライトサイクル終了後、フラッシュメモリ全エリアのデータセルの消去を行い、引き続いてプロテクトビットの消去を行います。この動作に関してはFLCS〈RDY/BSY〉をモニタすることで確認できます。自動プロテクトビット消去動作が正常に終了した場合 FLCS=0x01 となります。本デバイス内部で自動的なベリファイ動作は行いませんので、正常に消去ができたか、実行後に読み出しをして確認してください。第7バスサイクル以降の自動動作中にリードモードに復帰させるにはハードウエアリセットでフラッシュメモリもしくはデバイスをリセットする必要があります。この場合リードモードに復帰後、FLCS〈BLPRO 3:0〉にてプロテクトビットの状態を確認して、必要に応じて再度自動プロテクトビット消去または、自動チップ消去或いは自動ブロック消去を実行する必要があります。

・FLCS〈BLPRO  $3:0〉 \neq 0$ xF(全てのプロデクトビットがプログラムされていない)の場合自動プロテクトビット消去により、プロテクトの状態を解除することができます。本デバイスでは、プロテクトビットは 2 ビット単位で消去します。ビットの指定は第 7 バスライトサイクルで行い、ロマンド終了後は 2 ビット消去状態となります。各ブロックのプロテクトの状態は後で説明する FLCS〈BLPRO 3:0〉で確認できます。自動プロテクトビットプログラム動作の状態は、FLCS〈RDY/BSY〉をモニタすることで確認できます。自動プロテクトビット消去動作が正常に終了した場合、FLCS〈BLPRO 3:0〉の消去選択した 2 つのプロテクトビットの値が "0" となります。

いずれの場合も、自動プロテクトビット消去動作中は新たなコマンドシーケンスを受け付けません。動作を中止する場合はハードウエアリセットを用います。自動プロテクトビット消去動作が正常に終了した場合はリードモードに復帰します。

FLCS<RDY/BSY> ビットは自動動作中"0"、自動動作終了後"1"になります。

9) フラッシュコントロール/ステータスレジスタ フラッシュメモリのステータスモニタと、ブロックプロテクト状態を示すレジスタです。

表 2-16フラッシュコントロールレジスタ

FLCS (0xFFFF\_E520)

|            | 7         | 6      | 5            | 4      | 3             | 2            | 1           | 0          |  |

|------------|-----------|--------|--------------|--------|---------------|--------------|-------------|------------|--|

| Bit Symbol | BLPR03    | BLPR02 | BLPR01       | BLPR00 |               | ROMTYPE      |             | RDY/BSY    |  |

| Read/Write |           | F      | ?            | •      | R             | R            | R           | R          |  |

| リセット後      | 0         | 0      | 0            | 0      | 0             | 0            | ) 0         | 1          |  |

| 機能         | プロ        | テクトエリア | '設定 (128KB i | 単位)    | リードす /        | ROM 識別       | リードする       | Ready/Busy |  |

|            | 0000:全    | ブロックプロ | テクトなし        |        | ると" 0"        | ピット)         | と"0"が       | 0: 自動動作    |  |

|            | xxx1:ブロ   | ロック0がプ | ロテクト状態       |        | が読めま          |              | 読めます        | 中          |  |

|            |           |        | ロテクト状態       |        | す(            | 0:Flash      |             | 1: 自動動作    |  |

|            |           |        | ロテクト状態       |        |               | )1:MROM      |             | 終了         |  |

|            | 1xxx : ブロ | ロック3がプ | ロテクト状態       |        |               | /            |             |            |  |

|            | 15        | 14     | 13           | 12 🛆   | ( 1ì)         | 10           | 9           | 8          |  |

| Bit Symbol |           |        |              |        |               | 1            |             |            |  |

| Read/Write |           |        |              | (O)    | R V           |              |             |            |  |

| リセット後      | 0         | 0      | 0            | 0\^<   | <i>))</i> o   | 0            | <b>((0)</b> | 0          |  |

| 機能         |           |        |              |        |               |              | 40//        |            |  |

|            | 23        | 22     | 21           | 20     | 19            | 18           | <u>\</u>    | 16         |  |

| Bit Symbol |           |        | 4            |        |               | (A)          |             |            |  |

| Read/Write |           |        |              | F      | 2             |              |             |            |  |

| リセット後      | 0         | 0      | 0            | 0      | 0((/          | / <b>\</b> 0 | 0           | 0          |  |

| 機能         |           |        |              | V /    |               | <i>))</i>    |             |            |  |

|            | 31        | 30     | 29           | 28//   | 27            | 26           | 25          | 24         |  |

| Bit Symbol |           | 4      | 1            | 1      | $\mathcal{A}$ |              |             |            |  |

| Read/Write |           |        |              |        |               |              |             |            |  |

| リセット後      | 0         | 0      | <u> </u>     | 0      | 0             | 0            | 0           | 0          |  |

| 機能         |           | (()    |              |        |               | •            | •           | •          |  |

図 2-10

## ビット 0: Ready/Busy フラグビット

自動動作の状態を認識する方法として、RDY/BSY 出力を備えています。本ビットはこの機能を CPU からモニタ するための機能ビットです。フラッシュメモリが自動動作中は "0" を出力し、ビジー状態であるとことを 示します。自動動作が終了するとレディ状態となり "1" を出力し、次のコマンドを受け付けます。自動動作の結果が不良であった場合、本ビットは "0" 出力を継続します。ハードウエアリセットにより "1" に 復帰します。

力出来なくなる可能性があります。その際は、システムリセットまたはリセットコマンドで復帰して下さい。

(注) コマンド発行は、必ずレディ状態であることを確認してから発行して下さい。 ビジー中にコマンド発行を行なった場合、正常なコマンドが送られないだけでなく、それ以降のコマンドを入

ビット 2: ROM タイプ識別ビット

リセット後の値でフラッシュ ROM またはマスク ROM タイプの識別を行なうビットです。

フラッシュ ROM: "0" マスク ROM: "1"

ビット[7:4]: プロテクトビット状態ビット(ブロック毎の組み合わせ設定可能)

プロテクトビット(4 ビット)値は各ブロックのプロテクト状態に対応します。該当ビットが"1"の時は対応するブロックがプロテクト状態であることを示します。プロテクト状態のブロックは書き換えはできません。

#### 10) ID-Read

ID-Read コマンドを使用すると、本デバイスに内蔵しているフラッシュメモリのタイプ等の情報を知ることが出来ます。第 4 バスライトサイクル以降でのアドレス[15:14] の値によりロードされるデータが異なります(データ入力値は 0xF 以外の任意のデータ)。第 4 バスライトサイクル以降でのフラッシュへの SW 命令後の LW 命令(任意のフラッシュメモリエリアを読み出します)で、ID の値がロードされます(LW 命令直後に SYNC 命令を実施してください)。ID-Read コマンド第 4 バスライトサイクル以降は自動的にリードモードに復帰しません。第 4 バスライトサイクルと LW +SYNC 命令を繰り返し実行できます。 リードモードへの復帰はシステムリセットもしくは、Read コマンドまたは Read/リセットコマンドで行います。

ID-Read コマンドは、フラッシュメモリ内蔵タイプ製品とマスク ROM 内蔵タイプ製品を同一アプリケーション上で識別する必要があるときに使用できます。マスク ROM には、コマンドシーケンサが無い為、ID-Read コマンドがコマンドライトされても、マスク ROM に対して SW 命令と LW 命令が実施されたと認識する為です。マスク ROM 内蔵タイプで ID-Read コマンドを実行する場合はプロテクト状態を考慮して、通常の LW 命令を実行して得られる rt 値がフラッシュメモリ内蔵タイプの ID-Read コマンド実行結果(ID)とは異なるアドレスを予め抽出しておく必要があります。(FLCS の ROMTYPE ビットでも判断可能です)

(重要)各コマンドシーケンスの "バスライトサイクル間隔" は、使用している動作周波数によらず15システムクロック以上にする必要があります。本デバイスは、フラッシュメモリへの複数のSW命令実行に関して、バスライトサイクル間隔を自動調整する機能を有しません。従ってバスライトサイクル間隔が適正でない場合は所望のフラッシュメモリ書き換えが実行できません。オンボードプログラミングモード実行に先立ち、アプリケーションの動作周波数で、ソフトウエアタイマ等を使用してバスライト間隔を調整し、ID-Readコマンドの正常動作を確認してください。オンボードプログラミングモードでは、ID-Readコマンドが正常に実施できるバスライトサイクル間隔にてコマンドシーケンスを実行し、フラッシュメモリの書き換えをしてください。

#### (3) コマンドシーケンス一覧

表 2-17 内部 CPU によるフラッシュメモリアクセス

|            | 第1バス   | 第2バス   | 第3バス   | 第4バス      | 第5バス   | 第6バス   | 第7バス  |  |  |

|------------|--------|--------|--------|-----------|--------|--------|-------|--|--|

| コマンド       | サイクル   | サイクル   | サイクル   | サイクル      | サイクル   | サイクル   | サイクル  |  |  |

| シーケンス      | Addr.  | Addr.  | Addr.  | Addr.     | Addr.  | Addr.  | Addr. |  |  |

|            | Data   | Data   | Data   | Data      | Data   | Data   | Data  |  |  |

| Read       | 0xXX   |        |        | R         | A (    |        |       |  |  |

|            | 0xF0   |        |        | R         | RD     |        |       |  |  |

| Read/リセット  | 0x55XX | 0xAAXX | 0x55XX |           | (7/B   | RA     |       |  |  |

|            | 0xAA   | 0x55   | 0xF0   | RD        |        |        |       |  |  |

| ID-Read    | 0x55XX | 0xAAXX | 0x55XX | IA 0xXX — |        |        | -     |  |  |

|            | 0xAA   | 0x55   | 0x90   | 0x00      | ( ID   | -      | _     |  |  |

| Auto ページ   | 0x55XX | 0xAAXX | 0x55XX | PA        | PA     | PA     | PA    |  |  |

| プログラム(注)   | 0xAA   | 0x55   | 0xA0   | PD0       | PD1    | PD2    | PD3   |  |  |

| Auto チップ消去 | 0x55XX | 0xAAXX | 0x55XX | 0x55XX    | 0×AAXX | 0x55XX | _     |  |  |

|            | 0xAA   | 0x55   | 0x80   | 0xAA      | 0x55   | 0x10   | _     |  |  |

| Auto       | 0x55XX | 0xAAXX | 0x55XX | 0x55XX    | 0xAAXX | BA     | _     |  |  |

| ブロック消去(注)  | 0xAA   | 0x55   | 0x80   | 0xAA      | 0x55   | 0x30   | _     |  |  |

| プロテクトビット   | 0x55XX | 0×AAXX | 0x55XX | 0x55XX    | 0xAAXX | 0x55XX | PBA   |  |  |

| プログラム      | 0xAA   | 0x55   | 0x9A   | _ OxAA    | 0x55   | 0x9A   | 0x9A  |  |  |

| プロテクトビット   | 0x55XX | 0xAAXX | 0x55XX | 0x55XX    | 0xAAXX | 0x55XX | PBA   |  |  |

| 消去         | 0xAA   | 0x55   | 0x6A   | 0xAA      | 0x55   | Ox6A   | 0x6A  |  |  |

図 2-11

## (4) 補足説明

• RA: リードアドレス

• RD: リードデータ

● IA: IDアドレス

• ID: ID データ

• PA: プログラム ページアドレス

PD: プログラムデータ(32 ビットデータ)

第4バスサイクル以降 1ページ分をアドレス順にデータ入力

• BA: ブロックアドレス

• PBA: プロテクトビットアドレス

- (注1)全パスサイクル、アドレスビット[1:0]へは常に"0"を設定して下さい。(ビット[7:2]への設定値は未定義)

- (注 2) Read コマンドの第 2 パスサイクル、Read/リセットコマンドの第 4 パスサイクル、ID-Read コマンドの第 5 パスサイクル以外は全て"パスライトサイクル"です。 パスライトサイクルは SW 命令で実施します。SW 命令のストアデータには表の"Data"を用います。各パスライトサイクルのアドレス[31:16]はコマンドシーケンス実施対象のフラッシュメモリのアドレス[31:16]を用います。アドレス[15:0]は表の"Addr."を用います。

- (注3) 各パスライトサイクルの間隔を15システムクロック以上あけて実行してください。

- (注 4) 各パスライトサイクル終了直後に"SYNC 命令"を実行してください。

- (注 5) ID-Read コマンド第 4 パスライトサイクル後の "LW 命令"直後に"SYNC 命令"を実施してください。

# (5) バスライトサイクル時のアドレスビット構成 表 2.17.2 バスライトサイクル時のアドレスビット構成

| アドレス       | Addr<br>[31:21] | Addr<br>[20] | Addr<br>[19] | Addr<br>[18:17] | Addr<br>[16] | Addr<br>[15]           | Addr<br>[14] | Addr<br>[13] | Addr<br>[12:9] | Addr<br>[8] | Addr<br>[7:0]                      |

|------------|-----------------|--------------|--------------|-----------------|--------------|------------------------|--------------|--------------|----------------|-------------|------------------------------------|

| 12 AL      |                 |              |              | 通               | 常のバ          | <b>ベスライトサイクルアドレス設定</b> |              |              |                |             |                                    |

| 通常<br>コマンド | フラッシュ<br>領域     |              | "0"          | 推奨              |              |                        | コマ           | ンド           |                |             | Addr [1:0]= "0" 固定、<br>他ビットは"0" 推奨 |

| ブロック                      |                                                 | BA:ブロッ     | ックアドレ      | ス(フ   | ブロック消去の第                                                           | 6 バスライ | (トサイクルアドレ        | ス設定)                         |  |  |  |

|---------------------------|-------------------------------------------------|------------|------------|-------|--------------------------------------------------------------------|--------|------------------|------------------------------|--|--|--|

| 消去                        | フラッシュ<br>領域                                     | "0" 推奨     | ブロック<br>選択 |       | Addr [1:0]="0"固定、他ビットは"0"推奨                                        |        |                  |                              |  |  |  |

| Auto                      | PA: プログラムページアドレス (ページプログラムの第 4 バスライトサイクルアドレス設定) |            |            |       |                                                                    |        |                  |                              |  |  |  |

| ページプ<br>ログラム              | フラッシュ<br>領域                                     | "0" 推奨     | ブロック<br>選択 |       | ~-                                                                 | -ジ選択   | > /              | Addr [1:0]= "0"固定、他ビットは"0"推奨 |  |  |  |

| 10.0510                   |                                                 | IA:        | ID アドレ     | ス (ID | )–READ の第 4 バス                                                     | ライトサ   | イクルアドレス設定        |                              |  |  |  |

| ID-READ                   | フラッシュ<br>領域                                     | "0"        | 推奨         |       | IDFFD                                                              | Z      | Addr [1:0]= "0"  | 固定、他ビットは"0"推奨                |  |  |  |

|                           | PBA:                                            | プロテクトビッ    | トアドレス      | ス (プ  | ロテクトビットブ                                                           | ゚ログラム( | の第7パスライトも        | トイクルアドレス設定)                  |  |  |  |

| プロテク<br>トビット<br>プログラ<br>ム | フラッシュ<br>領域                                     | "0"        | 推奨         |       | プロテヴトビット<br>"00": ブロック<br>"01": ブロック<br>"10": ブロック:<br>"11": ブロック: | 1 2    | Addr[1:0]= "0"   | )<br>固定、他ビットは"O"推奨           |  |  |  |

|                           | PE                                              | BA: プロテクトビ | ットアド       | シス    | (プロテクトビッ                                                           | ト消去の第  | 57 バスライトサイ       | クルアドレス設定)                    |  |  |  |

| プロテク<br>トビット<br>消去        | フラッシュ<br>領域                                     | "0"        | 推奨         |       | プロテクト消去<br>0: ブロック 0, 1<br>1: ブロック 2, 3                            |        | Addr[1:0]= "0"固定 | 、他ビットは"0"推奨                  |  |  |  |

- (注) 表 20.5.1.2 内部 CPU によるフラッシュメモリアクセス」と併せてご使用願います。

- (注) 第 1 バスサイクルから「通常のバスライトサイクルアドレス設定」に従い、アドレス設定を行なって下さい。

- (注) 「"0" 推奨」は適宜変更可能です。

表 2-18 ブロック消去アドレス表

|        | アドレ                     | ス範囲                     |            |

|--------|-------------------------|-------------------------|------------|

| BA     | フラッシュメモリ                | 投影エリアに対して               | サイズ        |

|        | アドレス                    | 実施する場合                  |            |

| ブロック 0 | 0xBFC0_0000~0xBFC1_FFFF | 0x0000_0000~0x0001_FFFF | 128 K バイト  |

| ブロック 1 | 0xBFC2_0000~0xBFC3_FFFF | 0x0002_0000~0x0003_FFFF | 128 K バイト  |

| ブロック 2 | 0xBFC4_0000~0xBFC5_FFFF | 0x0004_0000~0x0005_FFFF | 128 Kバイト   |

| ブロック 3 | 0xBFC6_0000~0xBFC7_FFFF | 0x0006_0000~0x0007_FFFF | 】128 K バイト |

例: BAO を選択する場合、0xBFC0\_0000~0xBFC1\_FFFF で任意の1アドレスを入力します。

第1バスサイクルから第6バスサイクルまで上位側のアドレスは消去するブロックの アドレスを指定してください。

表 2-19 プロテクトビットプログラムアドレス表

| OPBA   | 第 7 バスライトサイクルのアドレス[15:14] |

|--------|---------------------------|

| OFDA   | アドレス[15] アドレス[14]         |

| ブロック 0 | 0                         |

| ブロック 1 |                           |

| ブロック 2 | 1 (\( \sqrt{0} \)         |

| ブロック 3 | 1                         |

表 2-20 プロテクトビットプ消去アドレス表

| OPBA    | 第1バスライトサイク | ルのアドレス[15:14] |

|---------|------------|---------------|

| UPDA    | アドレス[15]   | アドレス[14]      |

| ブロック 0/ | 0          | Х             |

| ブロック/1/ |            | Х             |

| ブロック 2  | 1          | Х             |

| ブロック 3  | 1          | Х             |

プロテクトビット消去コマンドは ビット0とビット1を まとめて消去します。 同様にビット2と ビット3は まとめて消去します。

表 2-21 ID-Read コマンド第 4 バスライトサイクルの ID アドレス(IA) と その後の LW 命令で読み出せるデータ(ID)

| IA [15:14] | ID [7: 0 ] | Code    |

|------------|------------|---------|

| 00b        | 0x98       | メーカーコード |

| 01b        | 0x5A       | デバイスコード |

| 10b        | Reserved   |         |

| 11b        | 0x05       | マクロコード  |

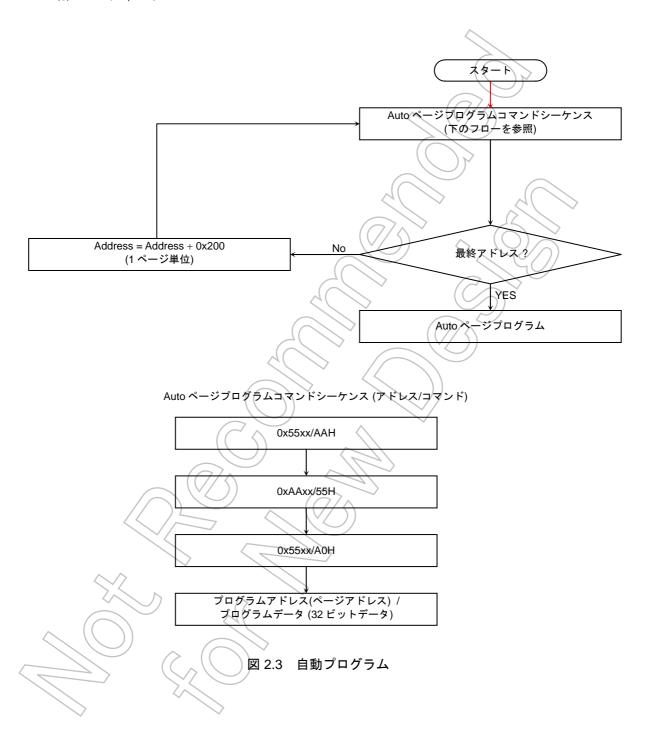

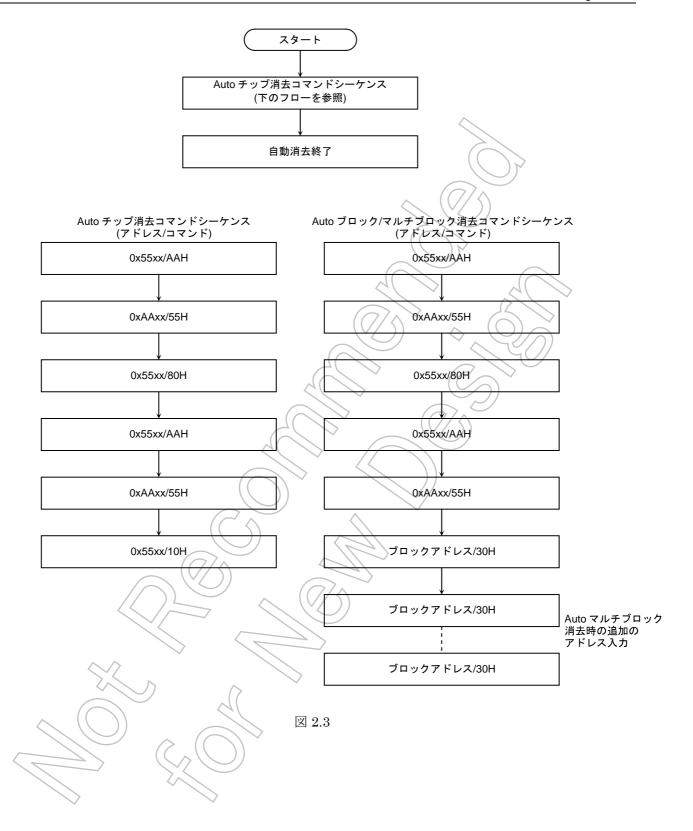

## (6) フロチャート

## 3. 各種プロテクト機能

## 3.1 概 要

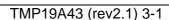

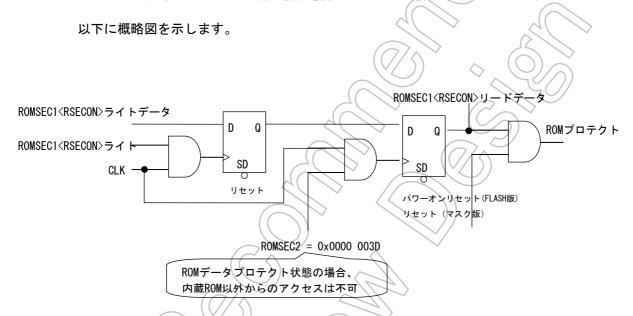

本製品は内蔵 ROM(Flash) 領域を読み出し禁止に設定できる ROM プロテクト及び DSU (DSU-Probe) の使用を禁止する DSU プロテクト機能などを内蔵しています。読み出し禁止機能として、次3つの機能をもっています。

- フラッシュプロテクト

- ROM データプロテクト

- DSU プロテクト

## 3.2 特 長

## 3.2.1 フラッシュプロテクト機能

#### <フラッシュ版>

内蔵フラッシュは、128K バイト単位のブロックごとに書き込みと消去の動作を禁止することができます。 この機能をブロックプロテクトと呼びます。

ブロックプロテクト機能を有効にするためには、プロテクトをかけたいブロックに対応するプロテクトビットを"1"にします。プロテクトビットを"0"にすることによりブロックプロテクトを解除することができます。(プログラム方法については、Flash 動作説明の章をご覧ください。)

プロテクトビットは、FLCS レジスタ〈BLPRO3:0〉ビットでモニタすることができます。

すべてのブロックにプロテクトをかけた状態を FLASH プロテクトと呼びます。一度 FLASH プロテクト状態 にしたあとプロテクト解除動作(プロテクトビットを"O"にする動作)を行うと、自動的にフラッシュの全データを消去した後、すべてのプロテクトビットが"O"になりますので注意が必要です。

#### <マスク版>

マスク版では常時 FLASH プロテクト状態となっており、FLASH プロテクトを解除することはできません。マスク版ではこの機能は通常の動作には影響しません。

<フラッシュ版、マスク版共通▶

これから説明する「ROM データプロテクト」、「DSU プロテクト」を有効にするためには、FLASH プロテクト 状態であることが必要です。

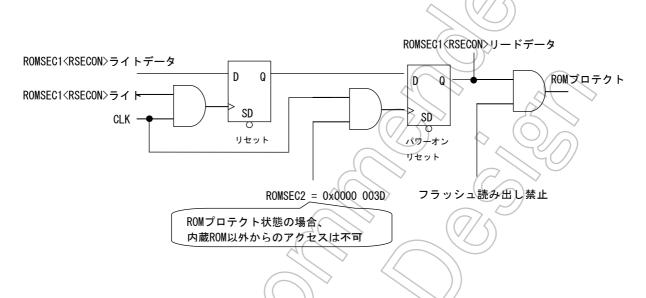

## 3.2.2 ROM データプロテクト

ROM データプロテクトは、内蔵 FLASH/ROM に対してデータの読み出しを制限する機能ですまた、フラッシュ版ではフラッシュに対するコマンドの実行も禁止されます。

ROM データプロテクトは、FLASH プロテクト状態で ROM プロテクトレジスタ ROMSEC1<RSECON>ビットが"1"のときに有効になります。

RSECON ビットはフラッシュ版、マスク版とも初期状態は"1"となっています。マスク版では FLASH プロテクトが常時有効ですので、ユーザプログラムで RSECON ビットを"O"に設定しない限り ROM データプロテクト状態となります。

フラッシュ版では FLASH の全ブロックにプロテクトをかけていなければ ROM データプロテクト状態にはなりません。FLASH の全ブロックにプロテクトをかけて FLASH プロテクト状態となっているときはマスク版と同様に初期状態が ROM データプロテクト状態となります。

(注)

ROM データプロテクト状態では RSECON ビットのアクセスは内蔵 ROM に置かれた命令からしかできません。プロテクト解除のプログラムは内蔵 ROM におく必要がありますので注意が必要です。

ROM correction 機能で ROM 領域の命令と置き換えられた RAM 上の命令の PC はフラッシュ ROM の領域を示しますが。実際には RAM 領域にあるため、ROM プロテクト状態でのデータの読み出しを行うことは出来ません。置き換えた RAM 上の命令でデータを読み出す場合は ROM 領域のプログラムでそのデータ値を RAM にライトする等の対策を行う必要があります。

ROM 領域に ROM プロテクトが掛かると以下の動作が出来なくなります。

- ROM 領域以外に置かれた命令からの ROM 領域のデータのロード及びストア

- DMAC レジスタへのストア (バスエラーによる NMI が発生します)

- EJTAG による ROM 領域のデータのロード及びストア

- BOOT-ROM による ROM 領域のデータのロード及びストア(FLASH 品のみ該当)

- フラッシュライタによる ROM 領域のデータのロード及びストア(FLASH 品のみ該当)

- ROM 領域以外に置かれた命令からの ROM 領域のプロテクト関連レジスタ(ROMSEC1、 ROMSEC2)へのアクセス

- ◆ ライタモードでの自動ブロックプロテクト解除コマンド、自動ブロックプロテクト解除コマンド以外のフラッシュコマンドシーケンス実行及びシングルモード、ブートモードでの ROM 領域のアドレスを指定したフラッシュコマンドシーケンス(FLASH 品のみ該当)

また、ROM 領域に ROM プロテクトが掛かった状態でも、以下の動作は実行出来ます。

- ROM 領域に置かれた命令から ROM 領域のデータのロード

- すべての領域に置かれている命令から ROM 領域以外のデータのロード

- すべての領域に置かれている命令から ROM 領域への命令分岐

- EJTAG による ROM 領域の PC トレース(制限あり)、ブレーク

- DMAC による ROM 領域のデータ転送

## 注) Mask 品は、ROM プロテクトが掛かった状態が初期値となります。

FLASH 品ではプロテクトビット設定 FLCS SLPRO 3:0> =1111 とする事で Mask 品同様に ROM プロテクトを掛けることが出来ます。Mask 品、FLASH 品で動作が

異なるため注意が必要です。

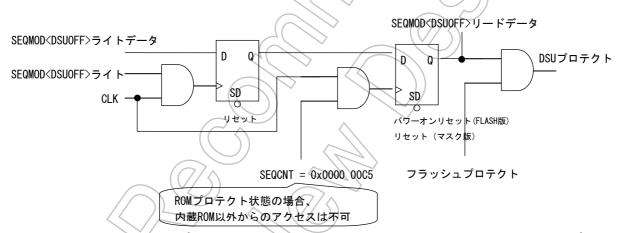

## 3.2.3 DSU プロテクト

DSU プロテクト機能は、DSU-probe の接続を無効にすることによりユーザー以外の第三者に容易に内蔵フラッシュのデータを読み出せないようにする機能です。

DSU プロテクトは、FLASH プロテクト状態で SEQMOD レジスタ〈DSUOFF〉ビットが、1 "のときに有効になります。

DSUOFF ビットはフラッシュ版、マスク版とも初期状態は"1"となっています。マスク版では FLASH プロテクトが常時有効ですので、ユーザプログラムで DSUOFF ビットを"O"に設定しない限り DSU プロテクト状態となります。

フラッシュ版では FLASH の全ブロックにプロテクトをかけていなければ DSU プロテクト状態にはなりません。FLASH の全ブロックにプロテクトをかけて FLASH プロテクト状態となっているときはマスク版と同様に初期状態が DSU プロテクト状態となります。

(注) ROM データプロテクト状態では DSUOFF ビットのアクセスは内蔵 ROM に置かれた命令からしかできません。DSU プロテクト解除のプログラムは内蔵 ROM におく必要がありますので注意が必要です。

## 3.3 プロテクト概略図および対応表

表 3-1各モードの各種プロテクト状態

|          | FLASH プロテクト状態                  |      | ()) c | N    |      | 0FF  |

|----------|--------------------------------|------|-------|------|------|------|

|          | ROM データプロテクト状態                 | 0    |       | 0    | FF   | 0FF  |