# 32 ビット TX System RISC TX19 ファミリー TMP1962F10AXBG

REV1.5 2006年2月21日

#### 当社半導体製品取り扱い上のお願い

030519TBP

- マイコン製品の信頼性予測については、「品質保証と信頼性/取り扱い上のご注意とお願い」の 1.3 項に記載されておりますので必ずお読みください。

- 当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり故障することがあります。当社半導体製品をご使用いただく場合は、半導体製品の誤作動や故障により、生命・身体・財産が侵害されることのないように、購入者側の責任において、機器の安全設計を行うことをお願いします。なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用いただくと共に、考慮されるべき注意事項や条件について「東芝半導体製品の取り扱い上のご注意とお願い」、「半導体信頼性ハンドブック」などでご確認ください。

- 本資料に掲載されている製品は、一般的電子機器 (コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電機器など) に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や誤作動が直接人命を脅かしたり人体に危害を及ぼす恐れのある機器(原子力制御機器、航空宇宙機器、輸送機器、交通信号機器、燃焼制御、医療機器、各種安全装置など) にこれらの製品を使用すること (以下"特定用途"という) は意図もされていませんし、また保証もされていません。本資料に掲載されている製品を当該特定用途に使用することは、お客様の責任でなされることとなります。

- ◆ 本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されている ものです。

- 本資料に掲載されている技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社および第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 本資料に掲載されている製品を、国内外の法令、規則および命令により製造、販売を禁止されている応用製品に 使用することはできません。

- 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

# 目 次

# TMP1962F10AXBG 製品別マニュアル

# 32 ビット RISC マイクロプロセッサ TX19 ファミリー TMP1962F10AXBG

# 1. 概要と特長

TX19 ファミリーは、米国 MIPS グループの RISC マイクロプロセッサである R3000A™をベースにして 当社が開発した TX39 プロセッサに、高コード効率の拡張命令セットである MIPS16™ASE (Application Specific Extension)を追加して、当社で独自開発した高性能な 32 ビット RISC プロッセサファミリーです。

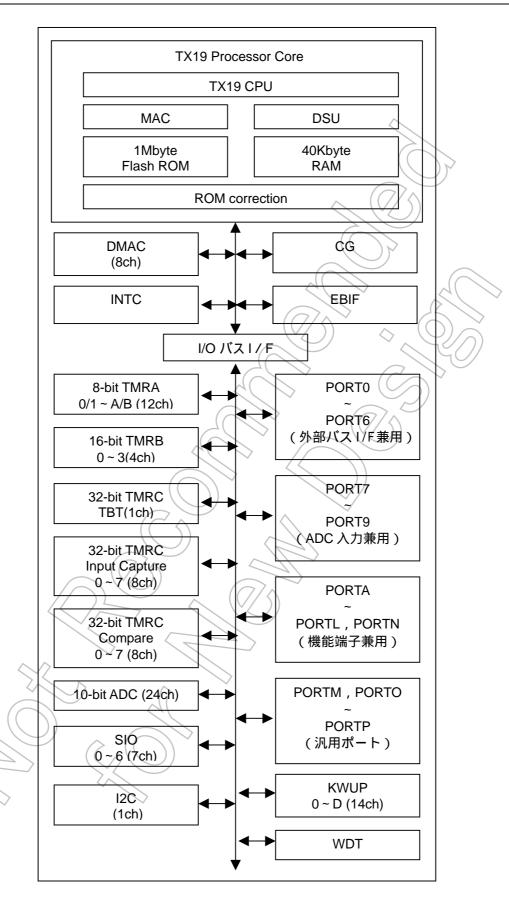

TMP1962 は、TX19 プロセッサコアをベースに各種周辺機能を内蔵した低電圧/低消費電力動作が可能な 32 ビット RISC マイクロプロセッサです。

TMP1962 の特長は次のとおりです。

## (1) TX19 プロセッサコア

16 ビットと 32 ビットの 2 つの ISA (Instruction Set Architecture) モードで、コード効率と演算性能の向上を実現

16 ビット ISA モードの命令は、コード効率の優れた MIPS16™ASE とオブジェクトレベルで互換 32 ビット ISA モードの命令は、演算性能の優れた TX39 とオブジェクトレベルで互換

高性能化と低消費電力化を同時に実現

#### 高性能化

ほとんどの命令を1クロックで実行 3オペランドの演算命令により高性能を実現 5段パイプライン

高速メモリを内蔵

DSP 機能: 32 ビット積和演算を 1 クロックで実行

#### 低消費電力化

低消費電力ライブラリを使用した最適化設計 プロセッサコアの動作を停止させるスタンバイ機能 リアルタイム制御に向いた高速割り込み応答 エントリーアドレスを独立化

割り込みマスクレベルを自動更新

要因別のベクタアドレスを自動生成

#### (2) 内蔵プログラムメモリ / データメモリ

| 製品名            | 内蔵 ROM        | 内蔵 RAM  |

|----------------|---------------|---------|

| TMP1962C10BXBG | 1Mbyte        | 40Kbyte |

| TMP1962F10AXBG | 1Mbyte(Flash) | 40Kbyte |

ROM コレクション機能(8ワード×8ブロック)

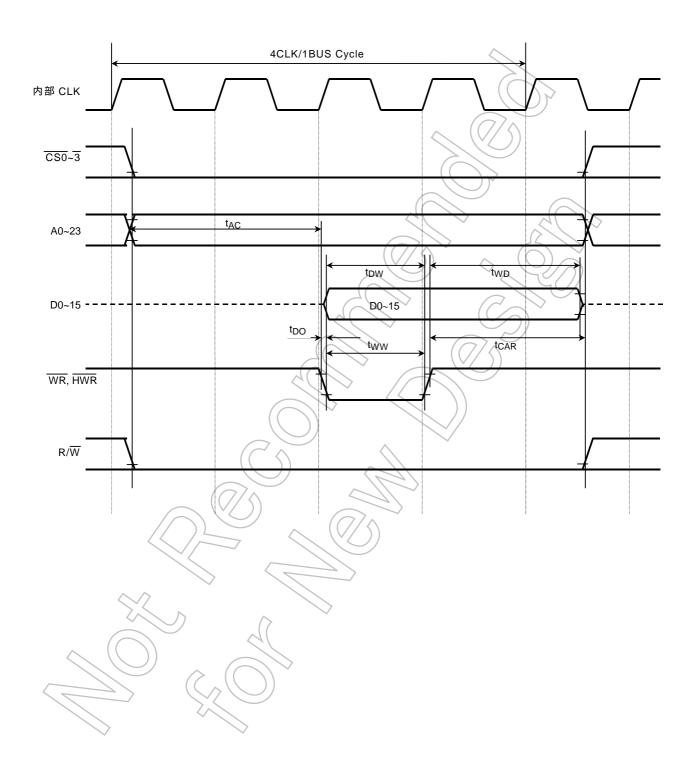

(3)外部メモリ拡張

16M バイト(プログラム/データ共通)まで拡張可能 外部データバス

セパレートバス / マルチプレクスバス : 8/16 ビット幅共存可能

4チャネル

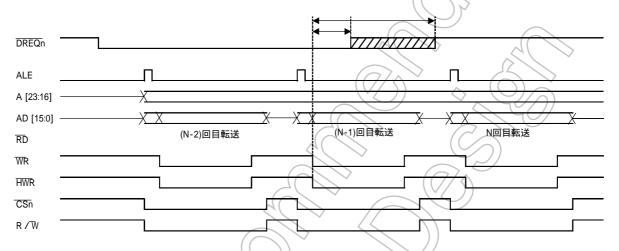

(4) DMA コントローラ : 8 チャネル

割り込みもしくはソフトウエアにて起動

転送対象は内蔵メモリ、内蔵 1/0、外部メモリ及び外部 1/0

(5) 8 ビットタイマ ( ... 12 チャネル

8/16/24/32 ビットインターバルタイマモード

8ビットPWMモード

8ビットPPGモード

(6)16 ビットタイマ

16 ビットインターバルタイマモード

16 ビットイベントカウンタモード

16 ビット PPG 出力

インプットキャプチャ機能

二相パルス入力カウンタ機能(2チャネル)

(7)32 ビットインプットキャプチャ

32 ビットインプットキャプチャレジスタ 8 チャネル

32 ビットコンペアレジスタ (7/ヘ: 8チャネル

32 ビットタイムベースタイマ : 1チャネル

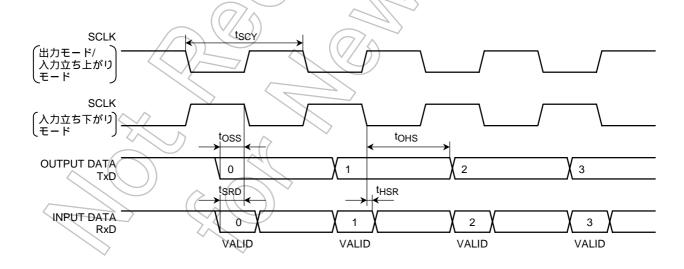

(8) 汎用シリアル・インタフェース : 7チャネル

UART/同期式モード選択可能

(9) シリアルバスインタフェース : 1チャネル

I<sup>2</sup>C バスモード/クロック同期式モード選択可能

(10) 10 ビット A/D コンバータ (S/H 有) : 24 チャネル

外部トリガスタート可能

チャネル固定/スキャンモード

シングル/リピートモード

タイマ監視機能

(11) ウォッチドックタイマ : 1チャネル

(12) チップセレクト/ウェイトコントローラ : 4 チャネル

#### (13)割り込み機能

CPU 4本 ····ソフトウエア割り込み命令

内部 55 本 ・・・・ 7 レベルの優先順位設定可能

(ウォッチドッグタイマ割り込みを除く)

外部 25 本 ···· 7 レベルの優先順位設定可能 (NMI 割り込みを除く)

またこの内、14本は KWUP であり割込み要因としては1本

(14) 入出力ポート ・・・・ 202 端子

(15)スタンバイ機能

2種類のスタンバイモード (IDLE, STOP)

(16) クロックジェネレータ

PLL 内蔵 (3 逓倍)

クロックギア機能: 高速クロックを 1/2, 1/4, 1/8 に分周

(17)エンディアン ・・・・ バイエンディアン

#### ビッグエンディアンの場合

| _,,_,,   |       |       | ( ∨ /  | )) / | \ \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

|----------|-------|-------|--------|------|----------------------------------------|

| 上位アドレス   | 31 24 | 23 16 | 3 15 8 | 1/ c | ^ ワードアビレス)                             |

| <b>↑</b> | 8     | 9     | 10     | 11   | 8                                      |

|          | 4     | 5     | 6      | 7 /  | 4>                                     |

|          | 0     | 1 <   | 2      | 3    | 0 ) 0                                  |

|          |       |       |        |      |                                        |

下位アドレス

バイト 0 が最上位バイト (ビット 31-24) です。

ワードのアドレスは、最上位バイト (バイト 0) のアドレスで指定します。

#### リトルエンディアンの場合

| 上位アドレス        | 31 | 24   | 23         | 16 15 | 8  | 7 | 0 | ワードアドレス |

|---------------|----|------|------------|-------|----|---|---|---------|

| <b>↑</b>      | ,  | 11   | 7 10       |       | 9/ | 8 |   | 8       |

|               |    | 7 (( | 6          |       | 5  | 4 |   | 4       |

|               |    | 3    | $-$ / $_2$ |       | 1  | 0 |   | 0       |

| <b>ナムコル・コ</b> |    |      |            |       |    | 7 |   |         |

下位アドレス

バイト 0 が最下位バイト (ビット 7-0) です。

ワードのアドレスは、最下位バイト (バイトの)のアドレスで指定します。

#### (18)動作周波数

40.5MHz ( $Vcc = 2.2V \sim 2.7V$ )

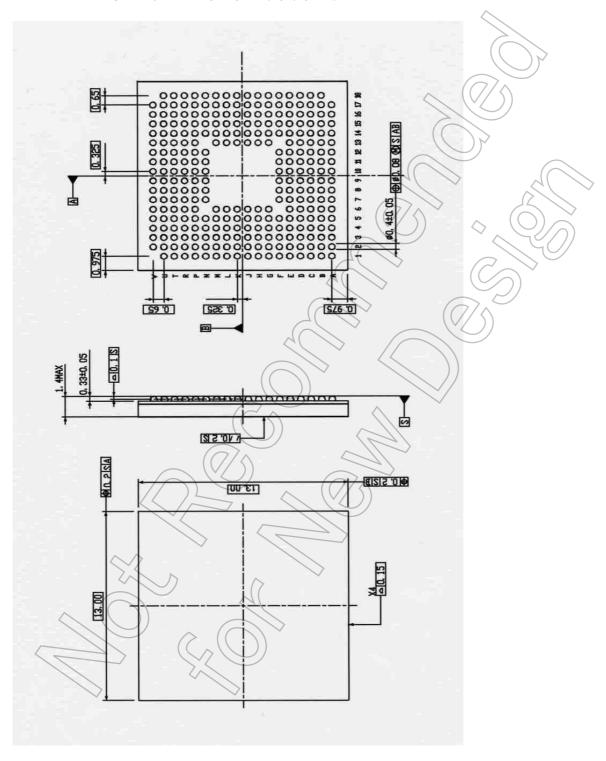

# (19)パッケージ

P-FBGA281 (13mm×13mm, 0.65mm ピッチ)

図 1.1 TMP1962F10AXBG ブロック図

# 2. ピン配置とピン機能

TMP1962 のピン配置図および入出力ピンの名称と概略機能を示します。

# 2.1 ピン配置図 (Top view)

TMP1962 のピン配置図は、図 2.1.1 のとおりです。

|    |    |    |    |    |    |                |                 |    |     |      |      |     |      |             |      |      | -    |

|----|----|----|----|----|----|----------------|-----------------|----|-----|------|------|-----|------|-------------|------|------|------|

| A1 | A2 | А3 | A4 | A5 | A6 | A7             | A8              | A9 | A10 | A11  | A12  | A13 | A14  | A15         | A16  | A17  |      |

| B1 | B2 | В3 | B4 | B5 | В6 | В7             | B8              | В9 | B10 | B11  | B12  | B13 | B14  | B15         | B16  | B17  | B18  |

| C1 | C2 | C3 | C4 | C5 | C6 | C7             | C8              | C9 | C10 | C11  | C12  | C13 | C14  | C15         | C16  | C17  | C18  |

| D1 | D2 | D3 | D4 | D5 | D6 | D7             | D8              | D9 | D10 | D11  | D12  | D13 | D14  | <b>D</b> 15 | D16  | D17  | D18  |

| E1 | E2 | E3 | E4 | E5 | E6 | E7             | E8              | E9 | E10 | E11  | E12  | £13 | E14  | E15         | E16  | E17  | E18  |

| F1 | F2 | F3 | F4 | F5 |    | F7             | F8              | F9 | F10 | F11  | F12  |     | F14  | F15         | F16< | F17  | F18  |

| G1 | G2 | G3 | G4 | G5 | G6 |                |                 |    |     |      |      | G13 | G14  | G15         | G16  | G17  | G18  |

| H1 | H2 | НЗ | H4 | H5 | Н6 |                |                 |    |     |      | V    | H13 | H14  | H15         | H16  | H17) | )H18 |

| J1 | J2 | J3 | J4 | J5 | J6 |                |                 |    |     | 1    |      | J13 | J14  | J15         | J16  | J17  | J18  |

| K1 | K2 | K3 | K4 | K5 | K6 |                |                 |    | 2   |      |      | K13 | K14  | K15         | K16  | K17  | K18  |

| L1 | L2 | L3 | L4 | L5 | L6 |                |                 |    |     |      |      | L13 | (14) | L45         | L16  | L17  | L18  |

| M1 | M2 | M3 | M4 | M5 | M6 |                |                 |    |     |      |      | M13 | M14  | M15         | M16  | M17  | M18  |

| N1 | N2 | N3 | N4 | N5 |    | N7             | N8              | N9 | N10 | N11  | N12  |     | N14  | N15         | N16  | N17  | N18  |

| P1 | P2 | P3 | P4 | P5 | P6 | P7             | P8 (            | P9 | P10 | P11  | P12  | P13 | P14  | P15         | P16  | P17  | P18  |

| R1 | R2 | R3 | R4 | R5 | R6 | R7             | R8              | R9 | R10 | R11  | .R12 | R13 | R14  | R15         | R16  | R17  | R18  |

| T1 | T2 | Т3 | T4 | T5 | Т6 | T7(            | T8              | Т9 | T10 | T11  | T12  | T13 | T14  | T15         | T16  | T17  | T18  |

| U1 | U2 | U3 | U4 | U5 | U6 | <del>[</del> 7 | )               | U9 | U10 | U11  | U12  | U13 | U14  | U15         | U16  | U17  | U18  |

|    | V2 | V3 | V4 | V5 | V6 | V7             | ) <sub>V8</sub> | V9 | V10 | /\11 | V12  | V13 | V14  | V15         | V16  | V17  |      |

図 2.1.1 ピン配置図 (P-FBGA281)

TMP1962 のピン番号とピン名称との関係はは、表 2.1.1 のとおりです。

表 2.1.1 ピン番号とピン名称 (1/2)

| ピン番<br>号 <i>(</i> | ピン名称      | ピン番<br>号 | ピン名称      | ピン番<br>号 | ピン名称        | ピン番<br>号 | ピン名称        | ピン番<br>号 | ピン名称           |

|-------------------|-----------|----------|-----------|----------|-------------|----------|-------------|----------|----------------|

| A1                | NC        | A13      | PK1/KEY1  | B8       | P75/AIN5    | C2       | PCST3 (DSU) | C14      | PK6/KEY6       |

| A2                | VREFL     | A14      | PI1/INT1  | B9       | PL0/TA4IN   | C3       | P92/AIN18   | C15      | PI5/INT9       |

| A3                | P90/AIN16 | A15      | PI3/INT3  | B10      | PL3/TAAIN   | C4       | P95/AIN21   | C16      | TCK (JTAG)     |

| A4                | P93/AIN19 | A16      | PI6/INTA  | B11      | PM1         | C5       | P82/AIN10   | C17      | CVCC2          |

| A5                | P80/AIN8  | A17      | X2        | B12      | PM4         | C6       | P85/AIN13   | C18      | XT2            |

| A6                | P83/AIN11 | B1       | AVCC31    | B13      | PK2/KEY2    | C7       | P72/AIN2    | D1       | SDAO/TPC (DSU) |

| A7                | P70/AIN0  | B2       | VREFH     | B14      | PI2/INT2    | C8       | AVSS        | D2       | PCST2 (DSU)    |

| A8                | P74/AIN4  | В3       | P91/AIN17 | B15      | PI4/INT4    | C9       | PL1/TA6IN   | D3       | SDI/DINT (DSU) |

| A9                | NC        | B4       | P94/AIN20 | B16      | PI7         | C10      | PL4/TB0IN0  | D4       | DVCC2          |

| A10               | PL2/TA8IN | B5       | P81/AIN9  | B17      | CVSS        | C11      | PM2         | D5       | P96/AIN22      |

| A11               | PM0       | B6       | P84/AIN12 | B18      | X1          | C12      | PM5         | D6       | P86/AIN14      |

| A12               | PK0/KEY0  | В7       | P71/AIN1  | C1       | PCST0 (DSU) | C13      | PK3/KEY3    | D7       | P73/AIN3       |

表 2.1.2 ピン番号とピン名称 (2/2)

| ピン番<br>号 | ピン名称             | ピン番<br>号 | ピン名称           | ピン番<br>号 | ピン名称            | ピン番<br>号 | ピン名称            | ピン番<br>号 | ピン名称           |

|----------|------------------|----------|----------------|----------|-----------------|----------|-----------------|----------|----------------|

| D8       | DVCC2            | F18      | P44/SCOUT      | K14      | P12/D10/AD10    | N18      | DVSS            | T8       | PD4/TXD4       |

| D9       | DVSS             | G1       | RESET          | K15      | P13/D11/AD11    | P1       | PP0             | T9       | PC0/TXD0       |

| D10      | PL5/TB0IN1       | G2       | TEST5          | K16      | P14/D12/AD12    | P2       | PB2/TB2IN0/INT5 | T10      | PC3/TXD1       |

| D11      | PM3              | G3       | FVCC2          | K17      | DVCC33          | P3       | PB3/TB2IN1/INT6 | T11      | PH4/TCOUT4     |

| D12      | PM6              | G4       | FVSS           | K18      | P15/D13/AD13    | P4       | PB4/TB2OUT      | T12      | PE2/SCLK5/CTS5 |

| D13      | PK4/KEY4         | G5       | PJ0/INT0       | L1       | FVCC3           | P5       | PB5/TB3IN0/INT7 | T13      | PE5/KEYB       |

| D14      | PK7/KEY7         | G6       | BW0            | L2       | PO1             | P6       | PG5/TC5IN       | T14      | P53/A3         |

| D15      | DVCC34           | G13      | TRST           | L3       | PO2             | P7       | PG7/TC7IN       | T15      | P56/A6         |

| D16      | TDI (JTAG)       | G14      | CAP1           | L4       | PO3             | P8       | PD6/SCLK4/CTS4  | T16      | P62/A10        |

| D17      | TDO (JTAG)       | G15      | P41/CS1        | L5       | PO4             | P9 (     | PC2/SCLK0/CTS0  | T17      | P65/A13        |

| D18      | XT1              | G16      | P37/ALE        | L6       | P07             | P10      | PC5/SCLK1/CTS1  | T18      | P20/A16/A0     |

| E1       | DCLK (DSU)       | G17      | P35/BUSAK      | L13      | TEST3           | P11      | PH6/TCOUT6      | U1       | PA0/TA0IN      |

| E2       | PCST1 (DSU)      | G18      | FVCC2          | L14      | P06/D6/AD6 <    | R12      | → NC △          | (U2      | PA3/TA3OUT     |

| E3       | DBGE             | H1       | NMI            | L15      | FVCC2           | P13      | P50/A0          | U3       | PA6/TA9OUT     |

| E4       | PJ3/INTLV        | H2       | DVCC31         | L16      | P07/D7/AD7      | ₽14      | P51/A1          | U4       | PF1/SI/SCL     |

| E5       | PJ4/ENDIAN       | НЗ       | PN7            | L17      | P10/D8/AD8      | P15      | P54/A4          | U5       | PF5/DREQ3      |

| E6       | P97/AIN23        | H4       | BW1            | L18      | P11/D9/AD9      | P16      | P23/A19/A3      | 1 U6/    | PG2/TC2IN      |

| E7       | P87/AIN15        | H5       | PLLOFF         | M1       | P00             | P17      | P24/A20/A4      | U7       | PD2/RXD3       |

| E8       | P76/AIN6         | H6       | TEST1          | M2       | PP5             | P18      | P25/A21/A5      | U8       | DVCC32         |

| E9       | <u>P7</u> 7/AIN7 | H13      | TEST2          | М3       | PP6             | R1       | PB0/TB00UT      | U9       | PC7/RXD2       |

| E10      | PL6/TB1IN0       | H14      | P31/WR         | M4       | PP7             | R2       | PB1/TB1OUT      | U10      | PH1/TCOUT1     |

| E11      | PL7/TB1IN1       | H15      | P32/HWR        | M5       | PB7/TB3OUT      | R3       | PF3/DREQ2       | U11      | PH3/TCOUT3     |

| E12      | PM7              | H16      | P33/WAIT/RDY   | M6       | DVCC32          | R4       | PF4/DACK2       | U12      | PE1/RXD5       |

| E13      | PK5/KEY5         | H17      | P30/RD         | M13      | TEST4           | R5       | PF7/TBTIN       | U13      | PE4/KEYA       |

| E14      | NC               | H18      | P40/CS0 (      | M14      | P02/D2/AD2      | R6       | // PG4/TC4IN    | U14      | DVCC32         |

| E15      | TMS (JTAG)       | J1       | PN2/SCLK6/CTS6 | M15      | FVSS            | R7       | PG6/TC6IN       | U15      | P57/A7         |

| E16      | CVCCH            | J2       | PN3            | M16      | P03/D3/AD3      | R8       | PD5/RXD4        | U16      | P63/A11        |

| E17      | NC               | J3       | PN4            | M17      | P04/D4/AD4      | R9       | PC1/RXD0        | U17      | P66/A14        |

| E18      | DVCC2            | J4       | PN5            | M18      | P05/D5/AD5      | , R10    | PC4/RXD1        | U18      | DVCC33         |

| F1       | DVSS             | J5       | PN6            | N1       | PP1             | R11      | PH5/TCOUT5      | V2       | PA2/TA2IN      |

| F2       | DRESET           | J6       | DVCC2          | N2       | PP2             | R12      | PH7/TCOUT7      | V3       | PA5/TA7OUT     |

| F3       | SYSRDY           | J13      | FVSS           | N3       | (/PP3)          | R13      | PE6/KEYC        | V4       | PF0/SO/SDA     |

| F4       | PJ1/BUSMD        | J14      | P16/D14/AD14   | N4       | PP4             | R14      | P52/A2          | V5       | PG0/TC0IN      |

| F5       | PJ2/BOOT         | J15      | DVSS           | N5       | PB6/TB3IN1/INT8 | R15      | P55/A5          | V6       | PG1/TC1IN      |

| F7       | AVSS             | J16      | P17/D15/AD15   | N7       | DVSS            | R16      | P61/A9          | V7       | PD1/TXD3       |

| F8       | AVSS             | J17      | P36/ R/W       | N8       | PD7/KEY8        | R17      | P21/A17/A1      | V8       | PD0/SCLK2/CTS2 |

| F9       | AVCC32           | J18      | P34/BUSRQ      | N9       | DVCC2           | R18      | P22/A18/A2      | V9       | PC6/TXD2       |

| F10      | DVCC34           | ¥        | PN0/TXD6       | N10      | DVSS            | T1       | PA1/TA1OUT      | V10      | PH0/TCOUT0     |

| F11      | PI0/ADTRG        | ∖ K2     | PN1/RXD6       | N11      | RSTPUP          | T2       | PA4/TA5OUT      | V11      | PH2/TCOUT2     |

| F12      | DVSS             | /кз      | PO5            | N12      | DVSS            | T3       | PA7/TABOUT      | V12      | PE0/TXD5       |

| F14      | CAP2             | K4       | P06            | N14      | P26/A22/A6      | T4       | PF2/SCK         | V13      | PE3/KEY9       |

| F15      | P42/CS2          | K5       | FVSS           | N15      | P27/A23/A7      | T5       | PF6/DACK3       | V14      | PE7/KEYD       |

| F16      | P43/CS3          | K6       | DVSS           | N16      | P00/D0/AD0      | T6       | PG3/TC3IN       | V15      | P60/A8         |

| F17      | DVCC33           | K13      | TEST0          | N17      | P01/D1/AD1      | T7       | PD3/SCLK3/CTS3  | V16      | P64/A12        |

|          |                  |          |                |          |                 |          |                 | V17      | P67/A15        |

# 2.2 ピン名称と機能

入出力ピンの名称と機能は、表 2.2.1 のとおりです。

表 2.2.1 ピン名称と機能 (1/6)

| ピン名称             | ピン数     | 入出力       | 機能                                                               |

|------------------|---------|-----------|------------------------------------------------------------------|

| P00~P07          | 8       | 入出力       | ポート 0: ビット単位で入出力の設定ができる入出力ポート                                    |

| D0~D7            |         | 入出力       | データ (下位) : データバス 0~7(セパレートバスモード)                                 |

| AD0~D7           |         | 入出力       | アドレスデータ (下位) : アドレス・データバス 0~7 (マルチプレクスバスモード)                     |

| P10~P17          | 8       | 入出力       | ポート 1: ビット単位で入出力の設定ができる入出力ポート                                    |

| D8~D15           |         | 入出力       | データ (上位): データバス 8~15: (セパレートバスモード)                               |

| AD8~AD15         |         | 入出力       | アドレスデータ (上位): アドレス・データパス 8~15 ( マルチプレクスバスモード )                   |

| A8~A15           |         | 出力        | アドレス: アドレスバス 8~15(マルチプレクスバスモード)                                  |

| P20~P27          | 8       | 入出力<br>出力 | ポート 2: ビット単位で入出力の設定ができる入出力ポート<br>アドレス: アドレスバス 15~23(セパレートバスモード)  |

| A16~A23<br>A0~A7 |         | 出力        | アドレス: アドレスバス 15~23(セパレードバスモード)<br>アドレス: アドレスバス 0~7(マルチプレクスバスモード) |

| A16~A23          |         | 出力        | アドレス: アドレスバス 0~7(マルチプレクスバスモード)                                   |

| P30              | 1       | 出力        | ポート 30: 出力専用ポート                                                  |

| RD               |         | 出力        | リード: 外部メモリをリードするためのストローブ信号                                       |

| P31              | 1       | 出力        | ポート 31: 出力専用ポート                                                  |

| $\overline{WR}$  |         | 出力        | ライト: D0~7 端子のデータをライトするためのストローブ信号                                 |

| P32              | 1       | 入出力       | ポート 32: 入出力ポート (ブルアップ付)                                          |

| HWR              |         | 出力        | 上位ライト: D8~15 端子のデータをライトするためのストローブ信号                              |

| P33              | 1       | 入出力       | ポート 33: 入出力ポート (プルアップ付)                                          |

| WAIT             |         | 入力        | ウェイト: CPU へのバスウェイト要求端子                                           |

| RDY              |         | 入力        | レディ: CPU へのバスレディ通知端子                                             |

| P34              | 1       | 入出力       | ポート 34: 入出力ポート (プルアップ付)                                          |

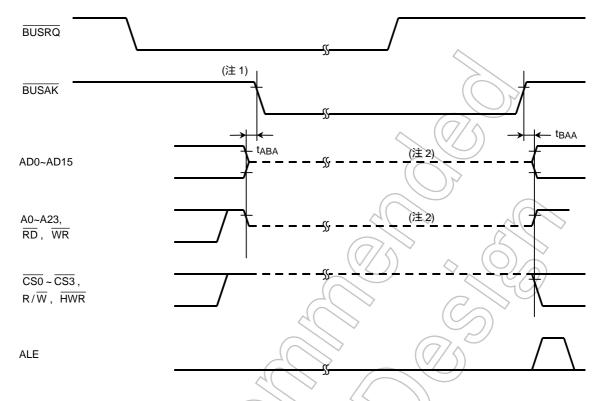

| BUSRQ            |         | 入力        | バスリクエスト: 外部マスタがバス制御権を CPU に要求する信号                                |

| P35              | 1       | 入出力       | ポート 35: 入出力ポート (プルアップ付)                                          |

| BUSAK            |         | 出力        | バスアクノリッジ: BUSRQ を受け CPU がバス制御権を解放しているのを通知する信号                    |

| P36              | 1       | 入出力       | ポート 36: 入出力ポート (プルアップ付)                                          |

| $R/\overline{W}$ |         | 出力        | リード/ライト: "1" でリードサイグルまたはダミーサイクルを "0" でライトサイクルを                   |

|                  |         |           | 示します。                                                            |

| P37              | 1 //    | 入出力       | ポート 37: 入出力ポート                                                   |

| ALE              |         | 出力        | アドレスラッチイネーブル(外部メモリアクセス時のみイネーブル)                                  |

| P40              | 1       | 入出力       | ポート 40: 入出力ポート (プルアップ付)                                          |

| CS0              |         | 出力        | チップセレクト 0: アドレスが指定したアドレス領域内なら "0" を出力                            |

| P41              | _ 1     | 入出力       | ポート 41: 入出力ポート (プルアップ付)                                          |

| CS1              | ><      | 出力        | チップセレクト 1: アドレスが指定したアドレス領域内なら "0" を出力                            |

| P42              | 4       | 入出力       | ポート 42: 入出力ポート (プルアップ付)                                          |

| CS2              |         | 出力        | チップセレクト 2: アドレスが指定したアドレス領域内なら "0" を出力                            |

| P43              | 1))     | 入出力       | ポート 43: 入出力ポート (プルアップ付)                                          |

| CS3              |         | 出力〉((     | チップセレクト 3: アドレスが指定したアドレス領域内なら "0" を出力                            |

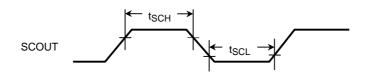

| P44              | <u></u> | 入出力/〉     | ポート 44: 入出力ポート                                                   |

| SCOUT            |         | 出力        | システムクロック出力: CPU と同じ高速クロック、またはその 1/2、または低速クロックを出力                 |

| P50~P57          | 8       | 入出力       | クを出力<br>ポート 5: ビット単位で入出力の設定ができる入出力ポート                            |

| A0~A7            | 0       | 出力        | アドレス: アドレスバス 0~7(セパレートバスモード)                                     |

| P60~P67          | 8       | 入出力       | ポート 6: ビット単位で入出力の設定ができる入出力ポート                                    |

| A8~A15           | U       | 出力        | アドレス: アドレスバス 8~15 (セパレートバスモード)                                   |

| 710-7110         |         | ш/)       | ZIVAZIVANA O (CAV INAC I)                                        |

# 表 2.2.2 ピン名称と機能(2/6)

| ピン名称       | ピン数  | 入出力                                                                                                                                                        | 機能                                                        |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| P70~P77    | 8    | 入力                                                                                                                                                         | ポート 7: 入力専用ポート                                            |

| AN0~AN7    |      | 入力                                                                                                                                                         | アナログ入力: A/D コンバータの入力                                      |

| P80~P87    | 8    | 入力                                                                                                                                                         | ポート 8: 入力専用ポート                                            |

| AN8~AN15   |      | 入力                                                                                                                                                         | アナログ入力: A/D コンバータの入力                                      |

| P90~P97    | 8    | 入力                                                                                                                                                         | ポート 9: 入力専用ポート                                            |

| AN16~AN23  |      | 入力                                                                                                                                                         | アナログ入力: A/D コンバータの入力                                      |

| PI0        | 1    | 入出力                                                                                                                                                        | ポート 10: 入出力ポート                                            |

| ADTRG      |      | 入力                                                                                                                                                         | A/D トリガ: A/D コンバータの外部スタート要求端子                             |

|            |      |                                                                                                                                                            | シュミット付き入力端子                                               |

| PI1        | 1    | 入出力                                                                                                                                                        | ポート I1: 入出力ポート                                            |

| INT1       |      | 入力                                                                                                                                                         | 割込み要求端子1:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能<br>シュミット付き入力端子 |

| PI2        | 1    | 入出力                                                                                                                                                        | ポート 12: 入出力ポート                                            |

| INT2       |      | 入力                                                                                                                                                         | 割込み要求端子 2:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能               |

|            |      |                                                                                                                                                            | シュミット付き入力端子                                               |

| PI3        | 1    | 入出力                                                                                                                                                        | ポート 13: 入出力ポート                                            |

| INT3       |      | 入力                                                                                                                                                         | 割込み要求端子 3:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能               |

|            |      |                                                                                                                                                            | シュミット付き入力端子                                               |

| PI4        | 1    | 入出力                                                                                                                                                        | ポート 14: 入出力ポート                                            |

| INT4       |      | 入力                                                                                                                                                         | 割込み要求端子 4:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能               |

|            |      |                                                                                                                                                            | シュミット付き入力端子                                               |

| PI5        | 1    | 入出力                                                                                                                                                        | ポート 15: 入出力ポート                                            |

| INT9       |      | 入力                                                                                                                                                         | 割込み要求端子 9:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能               |

|            |      |                                                                                                                                                            | シュミット付き入力端子                                               |

| PI6        | 1    | 入出力                                                                                                                                                        | ポート 16: 入出力ポート                                            |

| INTA       |      | 入力                                                                                                                                                         | 割込み要求端子 A:"H" レベル/"L" レベル/立ち上がり/下がりエッジ選択可能                |

| DIZ        | 4    | 入出力                                                                                                                                                        | シュミット付き入力端子<br>ポート (7: 入出力ポート                             |

| PI7<br>PA0 | 1    | 入出力                                                                                                                                                        | ポート 40: 人出力ポート                                            |

| TAOIN      | '    | 入山力                                                                                                                                                        | ルード AU. 八山ガルード<br>8bit タイマ 0 入力: 8bit タイマ 0 の入力端子。        |

| PA1        | 1    | 入出力                                                                                                                                                        | ポート A1: 入出力ポート                                            |

| TA1OUT     | '    | 出力                                                                                                                                                         | 8bit タイマ 01 出力: 8bit タイマ 0 または 1 の出力端子。                   |

| PA2        | 1    | 入出力(7)                                                                                                                                                     | ポート A2: 入出力ポート                                            |

| TA2IN      | '    | $\lambda \lambda $ | 8bit タイマ 2 入力: 8bit タイマ 2 の入力端子。                          |

| PA3        | 1 // | 入出力                                                                                                                                                        | ボート A3: 入出力ボート                                            |

| TA3OUT     | . << | 出力                                                                                                                                                         | 8bit タイマ 23 出力: 8bit タイマ 2 または 3 の出力端子。                   |

| PA4        | 1    | 入出力                                                                                                                                                        | ポート A4: 入出力ポート                                            |

| TA5OUT     | ·    | 出力                                                                                                                                                         | 8bit タイマ 45 出力: 8bit タイマ 4 または 5 の出力端子。                   |

| PA5        | 1,   | 入出力                                                                                                                                                        | ポート A5: 入出力ポート                                            |

| TA7OUT     | ~/?  | 出力                                                                                                                                                         | 8bit タイマ 67 出力: 8bit タイマ 6 または 7 の出力端子。                   |

| PA6        | (1)  | 入出力                                                                                                                                                        | ポート A6: 入出力ポート                                            |

| TA9OUT     |      | 入力                                                                                                                                                         | 8bit タイマ 89 出力: 8bit タイマ 8 または 9 の出力端子。                   |

| PA7 \ (    | 1))  | 入出力                                                                                                                                                        | ポートA7: 入出力ポート                                             |

| TABOUT     |      | 出力                                                                                                                                                         | 8bit タイマ AB 出力: 8bit タイマ A または B の出力端子。                   |

| PB0        | 1    | 入出力                                                                                                                                                        | ポート B0: 入出力ポート                                            |

| TB00UT     |      | 出为                                                                                                                                                         | 16bjt タイマ 0 出力: 18bit タイマ 0 の出力端子。                        |

| PB1        | 1    | 入出力                                                                                                                                                        | ポート B1: 入出力ポート                                            |

| TB1OUT     |      | 出力                                                                                                                                                         |                                                           |

| PB2        | 1    | 入出力                                                                                                                                                        | ポート B2: 入出力ポート                                            |

| TB2IN0     |      | 入力                                                                                                                                                         | 16bit タイマ2入力 0: 16bit タイマ2のカウント/キャプチャトリガ入力                |

| INT5       |      | 入力                                                                                                                                                         | 割込み要求端子 5:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能               |

| PB3        | 1    | 入出力                                                                                                                                                        | ポート B3: 入出力ポート                                            |

| TB2IN1     |      | 入力                                                                                                                                                         | 16bit タイマ 2 入力 1: 16bit タイマ 2 キャプチャトリガ入力                  |

| INT6       |      | 入力                                                                                                                                                         | 割込み要求端子 6:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能               |

表 2.2.3 ピン名称と機能(3/6)

| ピン名称   | ピン数      | 入出力   | 機  能                                                |

|--------|----------|-------|-----------------------------------------------------|

| PB4    | 1        | 入出力   | ポート B4: 入出力ポート                                      |

| TB2OUT |          | 出力    | 16bit タイマ 2 出力: 16bit タイマ 2 の出力端子。                  |

| PB5    | 1        | 入出力   | ポート B5: 入出力ポート                                      |

| TB3IN0 |          | 入力    | 16bit タイマ3入力 0: 16bit タイマ3のカウント/キャプチャトリガ入力          |

| INT7   |          | 入力    | 割込み要求端子 7:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能         |

| PB6    | 1        | 入出力   | ポート B6: 入出力ポート                                      |

| TB3IN1 |          | 入力    | 16bit タイマ 3 入力 1: 16bit タイマ 3 キャプチャトリガ入力            |

| INT8   |          | 入力    | 割込み要求端子8:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能          |

| PB7    | 1        | 入出力   | ポート B7: 入出力ポート                                      |

| TB3OUT |          | 出力    | 16bit タイマ 3 出力: 16bit タイマ 3 の出力端子。                  |

| PC0    | 1        | 入出力   | ポート C0: 入出力ポート                                      |

| TXD0   |          | 出力    | シリアル送信データ 0:プログラムによりオープンドレイン出力端子                    |

| PC1    | 1        | 入出力   | ポート C1: 入出力ポート                                      |

| RXD0   |          | 入力    | シリアル受信データ 0                                         |

| PC2    | 1        | 入出力   | ポート C2: 入出力ポート                                      |

| SCLK0  |          | 入力    | シリアルクロック入出力 0                                       |

| CTS0   |          | 入力    | シリアルデータ送信可能 0 (Clear To Send) :                     |

|        |          |       | プログラムによりオープンドレイン出力端子                                |

| PC3    | 1        | 入出力   | ポート C3: 入出力ポート                                      |

| TXD1   |          | 出力    | シリアル送信データ 1:プログラムによりオープンドレイン出力端子                    |

| PC4    | 1        | 入出力   | ポート C4: 入出力ポート                                      |

| RXD1   |          | 入力    | シリアル受信データ1                                          |

| PC5    | 1        | 入出力   | ポート C5: 入出力ポート                                      |

| SCLK1  |          | 入力    | シリアルクロック入出力1                                        |

| CTS1   |          | 入力    | シリアルデータ送信可能 1 (Clear To Send):                      |

|        |          |       | プログラムによりオープンドレイン出力端子                                |

| PC6    | 1        | 入出力   | ポート C6: 入出力ポート                                      |

| TXD2   |          | 出力    | シリアル送信データ 2:プログラムによりオープンドレイン出力端子                    |

| PC7    | 1        | 入出力   | ポート C7: 入出力ポート                                      |

| RXD2   |          | 入力    | シリアル受信データ2                                          |

| PD0    | 1        | 入出力   | ポート 00: 入出力ポート                                      |

| SCLK2  |          | 入力    | シリアルクロック入出力 2                                       |

| CTS2   |          | 入力(() | シリアルデータ送信可能 2 (Clear To Send):                      |

|        |          |       | プログラムによりオープンドレイン出力端子                                |

| PD1    | 1 //     | 入出力   | ポート D1: 入出力ポート                                      |

| TXD3   |          | 出为    | シリアル送信データ 3:プログラムによりオープンドレイン出力端子                    |

| PD2    | 1        | 入出力   | ポート D2: 入出力ポート                                      |

| RXD3   |          | 入力    | シリアル受信データ3                                          |

| PD3    | 1,       | 入出力   | ポート D3: 入出力ポート                                      |

| SCLK3  | 5.4      | 入力    | シリアルクロック入出力 3                                       |

| CTS3   |          | 入力    | シリアルデータ送信可能 3 (Clear To Send) :                     |

|        |          |       | プログラムによりオープンドレイン出力端子                                |

| PD4 (( | 1))      | 入出力   | ポート D4: 入出力ポート                                      |

| TXD4   |          | 出力    | シリアル送信データ 4:プログラムによりオープンドレイン出力端子                    |

| PD5    | 1        | 入出力   | ポート D5: 入出力ポート                                      |

| RXD4   | >        | 入为    | シリアル受信データ 4                                         |

| PD6    | 1        | 入出力   | ポート D6: 入出力ポート                                      |

| SCLK4  |          | 入力    | シリアルクロック入出力4                                        |

| CTS4   |          | 入力    | シリアルデータ送信可能 4 (Clear To Send) :                     |

|        | <u> </u> |       | プログラムによりオープンドレイン出力端子                                |

| PD7    | 1        | 入出力   | ポート D7: 入出力ポート                                      |

| KEY8   |          | 入力    | KEY on wake up 入力 8:(Dynamic pull up 選択可能)(プルアップ付き) |

|        |          |       | シュミット付き入力                                           |

表 2.2.4 ピン名称と機能(4/6)

| ピン名称            | ピン数          | 入出力       | 機能                                                                       |

|-----------------|--------------|-----------|--------------------------------------------------------------------------|

| PE0             | 1            | 入出力       | ポート E0: 入出力ポート                                                           |

| TXD5            |              | 出力        | シリアル送信データ 5:プログラムによりオープンドレイン出力端子                                         |

| PE1             | 1            | 入出力       | ポート E1: 入出力ポート                                                           |

| RXD5            |              | 入力        | シリアル受信データ 5                                                              |

| PE2             | 1            | 入出力       | ポート E2: 入出力ポート                                                           |

| SCLK5           |              | 入力        | シリアルクロック入出力 5                                                            |

| CTS5            |              | 入力        | シリアルデータ送信可能 5 (Clear To Send):                                           |

|                 |              | N . I . I | プログラムによりオープンドレイン出力端子                                                     |

| PE3             | 1            | 入出力       | ポート E3: 入出力ポート                                                           |

| KEY9            |              | 入力        | KEY on wake up 入力 9:(Dynamic pull up 選択可能)(プルアップ付き)                      |

| DE 4            |              | 入出力       | シュミット付き入力<br>ポート E4: 入出力ポート                                              |

| PE4             | 1            | 入山刀入力     | バート E4: 八田川ホート<br>  KEY on wake up 入力 A:(Dynamic pull up 選択可能)(プルアップ付き)  |

| KEYA            |              | 八刀        | RET OIT WARE UP 入力 A. ( Dyriatriic puit up 選款可能 ) ( フルア シンドさ ) シュミット付き入力 |

| PE5             | 1            | 入出力       | ポート E5: 入出力ポート                                                           |

| KEYB            | ı            | 入山力       | ホード E.S. 八田ガホード<br>KEY on wake up 入力 B:(Dynamic pull up 選択可能)(プルアップ付き)   |

| KEID            |              | 7(7)      | シュミット付き入力                                                                |

| PE6             | 1            | 入出力       | ポート E6: 入出力ポート                                                           |

| KEYC            |              | 入力        | KEY on wake up 入力 C: ( Dynamic pull up 選択可能 ) (プルアップ付き)                  |

|                 |              |           | シュミット付き入力                                                                |

| PE7             | 1            | 入出力       | ポート C7: 入出力ポート                                                           |

| KEYD            |              | 入力        | KEY on wake up 入力 D:(Dynamic pull up 選択可能)(プルアップ付き)                      |

|                 |              |           | シュミット付き入力                                                                |

| PF0             | 1            | 入出力       | ポート F0: 入出力ポート                                                           |

| SO              |              | 出力        | シリアルバスインタフェースの SIO モード時のデータ送信端子                                          |

| SDA             |              | 入出力       | シリアルバスインタフェースの I2C モード時のデータ送受信端子                                         |

|                 |              |           | プログラムによりオープンドレイン出力端子                                                     |

|                 |              |           | シュミット付き入力                                                                |

| PF1             | 1            | 入出力       | ポート F1: 入出力ポート                                                           |

| SI              |              | 入力        | シリアルバスインタフェースの SIO モード時のデータ受信端子                                          |

| SCL             |              | 入出力       | シリアルバスインタフェースの I2C モード時のクロック入出力端子<br>プログラムによりオープンドレイン出力端子                |

|                 |              |           | / シュミット付き入力                                                              |

| PF2             | 1            | 入出力       | ポート F2: 入出力ポート                                                           |

| SCK             | '//          | 入出力       | シリアルバスインタフェースの SIO モード時のクロック入出力端子                                        |

| PF3             | 4<           | 入出力       | ポート F3: 入出力ポート                                                           |

| DREQ2           |              | 入力        | DMA リクエスト信号 2:外部 I/O デバイスから DMAC2 への DMA 転送要求入力                          |

| PF4             | 1            | 入出力       | ポート F4: 入出力ポート                                                           |

| DACK2           |              | 出力        | DMA アクノリッジ信号 2:DREQ2 による DMA 転送要求に対するアクノリッジ信号                            |

| PF5             | <u>/</u> /)1 | 入出力       | ポート F5: 入出力ポート                                                           |

| DREQ3           | N            | 入力        | DMA リクエスト信号 3:外部 I/O デバイスから DMAC3 への DMA 転送要求入力                          |

| PF6             | $\sqrt{1}$   | 入出力       | ポート F6: 入出力ポート                                                           |

| DACK3           |              | 出力        | DMA アクノリッジ信号 3:DREQ3 による DMA 転送要求に対するアクノリッジ信号                            |

| PF7             | リナー          | 入出力       | ポート F7: 入出力ポート                                                           |

| TBTIN           | _            | 入力 ((     | 32bit タイムベースタイマ入力: 32bit タイムベースタイマのカウント入力                                |

| PG0~PG7         | 8            | 入出力       | ポート G: ビット単位で入出力の設定ができる入出力ポート                                            |

| TC0IN ~ TC7IN   |              | 入力        | 32bit タイマキャプチャトリガ入力                                                      |

| PH0 ~ PH7       | 8            | 入出力       | ポート H: ビット単位で入出力の設定ができる入出力ポート                                            |

| TCOUT0 ~ TCOUT7 |              | 出力        | 32bit タイマコンペア一致出力                                                        |

| PJ0             | 1            | 入出力       | ポート JO: 入出力ポート                                                           |

| INT0            |              | 入力        | 割込み要求端子 0:"H" レベル/ "L" レベル/立ち上がり/下がりエッジ選択可能                              |

|                 |              |           | シュミット付き入力端子                                                              |

# 表 2.2.5 ピン名称と機能(5/6)

| ピン名称          | ピン数 | 入出力       | 機能                                                                                    |

|---------------|-----|-----------|---------------------------------------------------------------------------------------|

| PJ1           | 1   | 入出力       | ポート J1: 入出力ポート                                                                        |

| BUSMD         |     | 入力        | 外部バスモード設定端子: リセット信号の立ち上がりで"H ( DVCC21 ) レベル"をサン                                       |

|               |     |           | プリングしてマルチプレクスバスとして、リセット信号の立ち上がりで"L"をサンプリ                                              |

|               |     |           | ングしてセパレートバスとして動作します。使用するバスモードに従ってリセット時                                                |

|               |     |           | にプルアップまたはプルダウンしてください。                                                                 |

| PJ2           | 1   | 入出力       | ポート J2: 入出力ポート                                                                        |

| BOOT          |     | 入力        | シングルブートモード設定端子:リセット信号の立ち上がりで"L"をサンプリングして                                              |

|               |     |           | シングルブートモードになります。内蔵フラッシュメモリの書き換え時に使用します。                                               |

|               |     |           | リセット信号の立ち上がりで"H(DVCC21)レベル"をサンプリングしてノーマル動作<br>(通常動作)します。通常使用時はリセット時にこの端子をプルアップしてください。 |

| PJ3           | 1   | 入出力       | (週帯動作) ひより。 週帯使用時はりとりで時にとめ端子をフルアップしてください。<br>ポート J3: 入出力ポート                           |

| INTLV         | '   | 入山力       | ハード 33. 八山/ハルード<br>  インターリーブモード設定端子:リセット信号の立ち上がりで"H(DVCC21)レベル"                       |

| IINILV        |     | 7(7)      | をサンプリングします。この端子はリセット時にプルアップしてください。                                                    |

| PJ4           | 1   | 入出力       | ポート J4: 入出力ポート                                                                        |

| ENDIAN        | '   | 入力        | この端子はモード設定に使用されます。リセット信号の立ち上がりで"H(DVCC21)                                             |

| 21401/114     |     | 7 (7 )    | レベル"をサンプリングしてビッグエンディアンの動作を、リセット信号の立ち上がり                                               |

|               |     |           | で"L"をサンプリングしてリトルエンディアンの動作をします。使用するエンディアン                                              |

|               |     |           | に従ってリセット時にプルアップまたはプルダウンしてください。                                                        |

| PK0 ~ PK7     | 8   | 入出力       | ポート K: ビット単位で入出力の設定ができる入出力ポート                                                         |

| KEY0 ~ KEY7   |     | 入力        | KEY on wake up 入力 0~7:(Dynamic pull up 選択可能)(プルアップ付き)                                 |

|               |     |           | シュミット付き入力                                                                             |

| PL0           | 1   | 入出力       | ポート LO: 入出力ポート                                                                        |

| TA4IN         |     | 入力        | 8bit タイマ 4 入力: 8bit タイマ 4 の入力端子。                                                      |

| PL1           | 1   | 入出力       | ポート L1: 入出力ポート                                                                        |

| TA6IN         |     | 入力        | 8bit タイマ 6 入力: 8bit タイマ 6 の入力端子。                                                      |

| PL2           | 1   | 入出力       | ポート L2: 入出力ポート                                                                        |

| TA8IN         |     | 入力        | 8bit タイマ 8 入力: 8bit タイマ 8 の入力端子。                                                      |

| PL3           | 1   | 入出力       | ポート L3: 入出力ポート                                                                        |

| TAAIN         |     | 入力        | 8bit タイマ A 入力: 8bit タイマ A の入力端子。                                                      |

| PL4           | 1   | 入出力       | ポートレ4: 入出力ポート                                                                         |

| TB0IN0        | 4   | 入力        | 16bit タイマ 0 入力 0: 16bit タイマ 0 のカウント/キャプチャトリガ入力                                        |

| PL5<br>TB0IN1 | 1   | 入出力入力     | ポート L5: 入出力ポート<br>/16bit タイマ 0 入力 1: 16bit タイマ 0 キャプチャトリガ入力                           |

| PL6           |     | 入出力       | ポート L6: 入出力ポート                                                                        |

| TB1IN0        | 1 / | 入力        | がート L6. 八四月が一下<br>16bit タイマ 1 入力 0:/16bit タイマ 1 のカウント/キャプチャトリガ入力                      |

| PL7           | 1 ( | 入出力       | ポートレス入出力ポート                                                                           |

| TB1IN1        | ' \ | XX        | 16bit タイマ 1 入力 1: 16bit タイマ 1 キャプチャトリガ入力                                              |

| PM0 ~ PM7     | 8   | 入出力       | ポート M: ビット単位で入出力の設定ができる入出力ポート                                                         |

| PN0           | 1.  | 入出力       | ポート N0: 入出力ポート                                                                        |

| TXD6          |     | 出力        | シリアル送信データ 6:プログラムによりオープンドレイン出力端子                                                      |

| PN1           | 1   | 入出力       | ポート N1: 入出力ポート                                                                        |

| RXD6          |     | <b>人力</b> | シリアル受信データ 6                                                                           |

| PN2 \ ((      | 1   | 入出力       | ポート N2: 入出力ポート                                                                        |

| SCLK6         |     | 入力        | シリアルクロック入出力 6                                                                         |

| CTS6          |     | 入ガ〉 ((    | シリアルデータ送信可能 6 (Clear To Send) :                                                       |

|               | >   |           | プログラムによりオープンドレイン出力端子                                                                  |

| PN3~PN7       | 5   | 入出力       | ボート N3~N7: ビット単位で入出力の設定ができる入出力ポート                                                     |

| P00 ~ P07     | 8   | 入出力       | ポート O: ビット単位で入出力の設定ができる入出力ポート                                                         |

| PP0 ~ PP7     | 8   | 入出力       | ポート P: ビット単位で入出力の設定ができる入出力ポート                                                         |

11

表 2.2.6 ピン名称と機能(6/6)

| ピン名称        | ピン数            | 入出力                                    | 機 能                                                                          |

|-------------|----------------|----------------------------------------|------------------------------------------------------------------------------|

| NMI         | 1              | 入力                                     | ノンマスカブル割り込み要求端子: 立ち下がりエッジの割り込み要求端子<br>シュミット付き入力                              |

| PLLOFF      | 1              | 入力                                     | PLL 逓倍クロックを使用する場合は"H ( DVCC21 ) "レベルに、使用しない場合は "L" レベルに固定してください。 (シュミット付き入力) |

| RSTPUP      | 1              | 入力                                     | リセット時"H(DVCC32)"でポート 3、4PullUp イネーブル、"L"でディゼーブル<br>シュミット付き入力                 |

| RESET       | 1              | 入力                                     | リセット: LSI を初期化 (プルアップ付)<br>シュミット付き入力                                         |

| X1/X2       | 2              | 入出力                                    | 高速発振子接続端子                                                                    |

| XT1/XT2     | 2              | 入出力                                    | オープンにしてください                                                                  |

| DRESET      | 1              | 入力                                     | デバッグリセット:DSU-ICE 用信号(シュミット付き入力、プルアップ付き)                                      |

| DCLK        | 1              | 出力                                     | デバッグクロック:DSU-ICE 用信号                                                         |

| DBGE        | 1              | 入力                                     | デバッガイネーブル:DSU-ICE 用信号(シュミット付き入力、プルアップ付き)                                     |

| PCST3~0     | 4              | 出力                                     | PC トレースステータス:DSU-ICE 用信号                                                     |

| SDI/DINT    | 1              | 入力                                     | シリアルデータインプット/デバッグインタラプト:DSU-ICE 用信号                                          |

| SDAO/TPC    | 1              | 出力                                     | (シュミット付き入力、プルアップ付き)<br>シリアルデータ・アドレスアウトプット/ターゲット PC:DSU-ICE 用信号               |

| TCK         | 1              | 入力                                     | テストクロック入力:JTAG テスト用信号(シュミット付き入力、プルアップ付き)                                     |

| TMS         | 1              | 入力                                     | テストモードセレクト入力: JTAG テスト用信号(シュミット付き入力、プルアップ付き)                                 |

| TDI         | 1              | 入力                                     | テストデータ入力:JTAG テスト用信号(シュミット付き入力、プルアップ付き)                                      |

| TDO         | 1              | 出力                                     | テストデータ出力:JTAG テスト用信号                                                         |

| TRST        | 1              | 入力                                     | テストリセット入力:JTAG テスト用信号(シュミット付き入力、プルダウン付き)                                     |

| BW0~1       | 2              | 入力                                     | BW0="H(DVCC21)"、BW1="H(DVCC21)" に固定してください。<br>(シュミット付き入力)                    |

| VREFH       | 1              | 入力                                     | A/D コンバータ用基準電源入力端子 (H)<br>A/D コンバータを使用しないときは AVCC に接続してください                  |

| VREFL       | 1              | 入力                                     | A/D コンバータ用基準電源入力端子 (L)<br>A/D コンバータを使用しないときは AVSS に接続してください                  |

| AVCC31 ~ 32 | 2 /            | $\rightarrow //$                       | A/D コンバータ電源端子。A/D コンバータを使用しない場合も電源に接続してください。                                 |

| AVSS        | 3 //           |                                        | A/D コンバータ GND 端子 (0V)。A/D コンバータを使用しない場合も GND に接続してください。                      |

| TEST0       | 1              | \\-\-\-\-\-\-\-\-\-\-\-\-\-\-\-\-\-\-\ | TEST 用端子:オープンまたは GND に固定してください                                               |

| TEST1       | 1              | 入力                                     | TEST 用端子 GND に固定してください                                                       |

| TEST2       | . 1            | -                                      | TEST 用端子:オープンまたは GND に固定してください                                               |

| TEST3       | <b>\</b> 1     | -                                      | TEST 用端子:オープンまたは GND に固定してください                                               |

| TEST4       |                | 刀 -                                    | TEST 用端子:オープンまたは GND に固定してください                                               |

| TEST5       | 1              | 入力                                     | TEST 用端子:GND に固定してください                                                       |

| SYSRDY      | 1))            | 出力                                     | Flash メモリへのアクセス許可信号                                                          |

| CVCC2       |                | $\triangle$                            | 発振器用電源端:2.5V 系電源                                                             |

| CVSS        | 1              | (- ^                                   | 発振器用 GND 端子(0V)                                                              |

| CVCCH       | <del>-</del> 1 | 77                                     | オープンにしてください                                                                  |

| CAP1        | 1              | <u>-</u>                               | オープンにしてください                                                                  |

| CAP2        | 1              | -                                      | オープンにしてください                                                                  |

| FVCC2       | 3              | -                                      | Flash 用電源端子: 2.5V 系電源                                                        |

| FVCC3       | 1              | -                                      | Flash 用電源端子: 3V 系電源                                                          |

| FVSS        | 4              | -                                      | Flash 用 GND 端子 (0V)                                                          |

| DVCC21 ~ 22 | 5              | -                                      | 電源端子: 2.5V 系電源                                                               |

| DVCC31 ~ 34 | 9              | -                                      | 電源端子: 3V 系電源                                                                 |

| DVSS        | 9              | -                                      | GND 端子 (0V)                                                                  |

- (注 1) PJ1, PJ2, PJ3, PJ4 に関して、リセット信号の立ち上がり前後 1 システムクロック分、各端子の説明通りの状態("H (DVCC21)"レベルまたは"L"レベル)を保持してください。ただし、リセット端子は"L"レベル、"H"レベルともに安定した状態であることが必要です。

- (注 2) フラッシュ内蔵タイプ (TMP1962F10AXBG) では DSU プローブを接続してのデバッグが可能です。マスク ROM 内蔵タイプ (TMP1962C10BXBG) では DSU プローブを接続できますが、内蔵 ROM の読み出し、プロセッサコア以外のレジスタ / 内蔵メモリ / 外部への書き込みはできません。

ピン名称と電源供給端子の関係は、表 2.2.2 のとおりです。

表 2.2.2 ピン名称と電源

|        | 電源                     |          |                                        | 電源      |        |  |  |

|--------|------------------------|----------|----------------------------------------|---------|--------|--|--|

| ピン名称   | マスク品                   | フラッシュ品   | ピン名称                                   | マスク品    | フラッシュ品 |  |  |

| P0     | P0 DVCC33 DVCC33       |          | PO _                                   | DVCC31  | DVCC31 |  |  |

| P1     | DVCC33                 | DVCC33   | PP( (//                                | DVCC31  | DVCC31 |  |  |

| P2     | DVCC33                 | DVCC33   | X1                                     | CVCC15  | CVCC2  |  |  |

| P3     | DVCC33                 | DVCC33   | X2                                     | CVCC15  | CVCC2  |  |  |

| P4     | DVCC33                 | DVCC33   | RESET                                  | DVCC2(( | DVCC21 |  |  |

| P5     | DVCC33                 | DVCC33   | NMI                                    | DVCC2   | DVCC21 |  |  |

| P6     | DVCC33                 | DVCC33   | PLLOFF                                 | DVCC2   | DVCC21 |  |  |

| P7     | AVCC32                 | AVCC32   | DRESET                                 | DVCC2   | DVCC21 |  |  |

| P8     | AVCC32                 | AVCC32   | DCLK                                   | DVCC2   | DVCC21 |  |  |

| P9     | P9 AVCC31              |          | DBGE                                   | DVCC2   | DVCC21 |  |  |

| PA     | DVCC32                 | DVCC32   | PCST3~0                                | DVCC2   | DVCC21 |  |  |

| PB     | PB DVCC32              |          | SDI/DINT                               | DVCC2   | DVCC21 |  |  |

| PC     | DVCC32                 | DVCC32   | SDAO/TPC<br>TCK                        | DVCC2   | DVCC21 |  |  |

| PD     | DVCC32                 | DVCC32   |                                        | DVCC34  | DVCC34 |  |  |

| PE /   | DVCC32                 | DVCC32 / | TMS                                    | DVCC34  | DVCC34 |  |  |

| PF <<  | DVCC32                 | DVCC32   | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | DVCC34  | DVCC34 |  |  |

| PG     | DVCC32                 | DVCC32   | TDO                                    | DVCC34  | DVCC34 |  |  |

| PH     | DVCC32                 | DVCC32   | TRST                                   | DVCC34  | DVCC34 |  |  |

| <\PI\^ | DVCC34                 | DVCC34   | BW1 ~ 0                                | DVCC2   | DVCC21 |  |  |

| PJ     | DVCC2                  | /DVCC21  | RSTPUP                                 | DVCC32  | DVCC32 |  |  |

| PK     | DVCC34                 | DVCC34   |                                        |         |        |  |  |

| PL     | PL DVCC34<br>PM DVCC34 |          |                                        |         |        |  |  |

| PM     |                        |          |                                        |         |        |  |  |

| ÝΝ     | DVCC31                 | DVCC31   |                                        |         |        |  |  |

電源供給端子の動作電圧範囲を、表2.2.3に示します。

表 2.2.3 電源供給端子の動作電圧範囲

| 電源供給端子      | 動作電圧範囲        | 対応関係    |

|-------------|---------------|---------|

| DVCC15      | 1.35V ~ 1.65V | (       |

| CVCC15      | 1.35V ~ 1.65V | マスク品    |

| DVCC2       | 2.3V ~ 3.3V   |         |

| DVCC21      | 2.2V ~ 2.7V   |         |

| DVCC22      | 2.2V ~ 2.7V   |         |

| CVCC2       | 2.2V ~ 2.7V   | フラッシュ品  |

| FVCC2       | 2.2V ~ 2.7V   |         |

| FVCC3       | 2.9V ~ 3.6V   |         |

| DVCC31 ~ 34 | 1.65V ~ 3.3V  | マネケ /   |

| AVCC31 ~ 32 | 2.7V ~ 3.3V   | フラッシュ共通 |

# (注1) AVCC32 AVCC31

- · P7~P9をAD入力として使用する場合は、2.7V // AVCC3\*

- P9 (AVCC31 系)を AD 入力として使用、P7、P8 (AVCC32 系)をポートとして使用する場合は

2.7V AVCC31 3.3V 1.65V AVCC32 AVCC31

・ P7 (AVCC32 系) を AD 入力として使用、P8 (AVCC32 系) P9 (AVCC31 系)をポートとして使用する場合は

2.7V AVCC32 AVCC31 3.3V

として使用してください。

(注2) TMP1962 は CPU、内部ロジック用電源(マスク品: DVCC15 / DVCC2 / CVCC15 / 、Flash 品: DVCC21 / DVCC22 / CVCC2 / FVCC3 ) が印加された状態で、他の I/O (ポート) 用電源を遮断することが可能です。但し、フラッシュ品 TMP1962F10A ではアナログ用電源 AVCC31 を遮断すると OV に安定するまでの過渡期に貫通電流が発生します。AVCC31 電源を遮断する前に変換結果 OV の AD 変換を行うことにより貫通電流を抑制することが可能ですが、応用機器での対応をお願い致します。

# 3. 動作説明

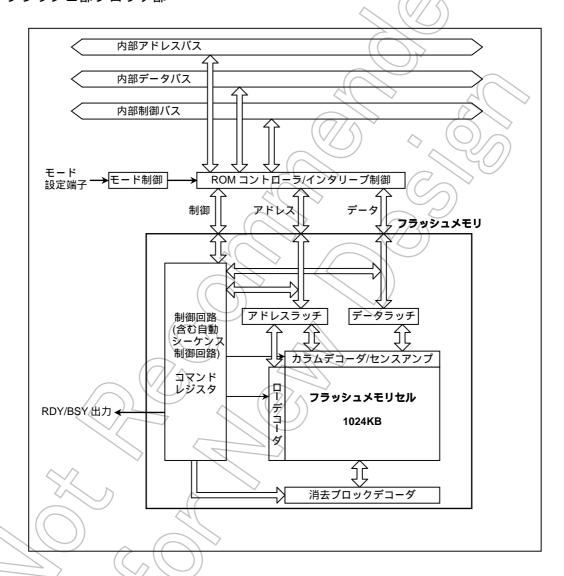

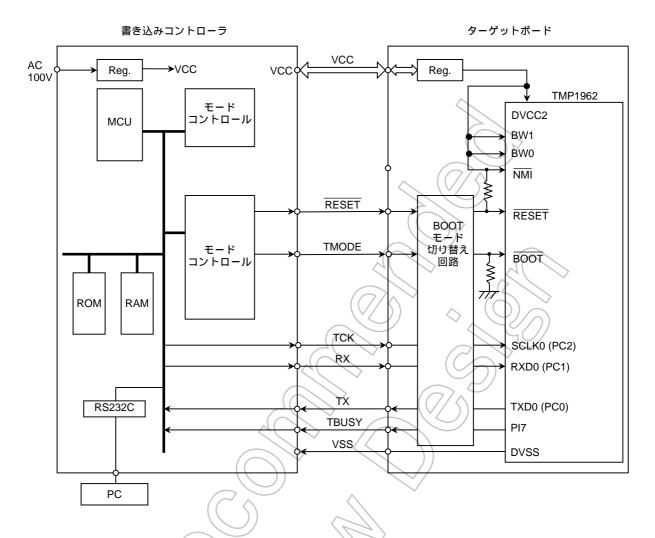

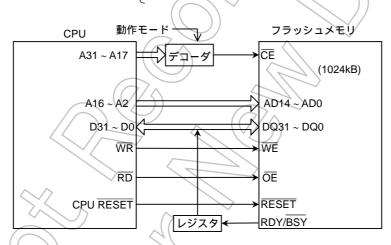

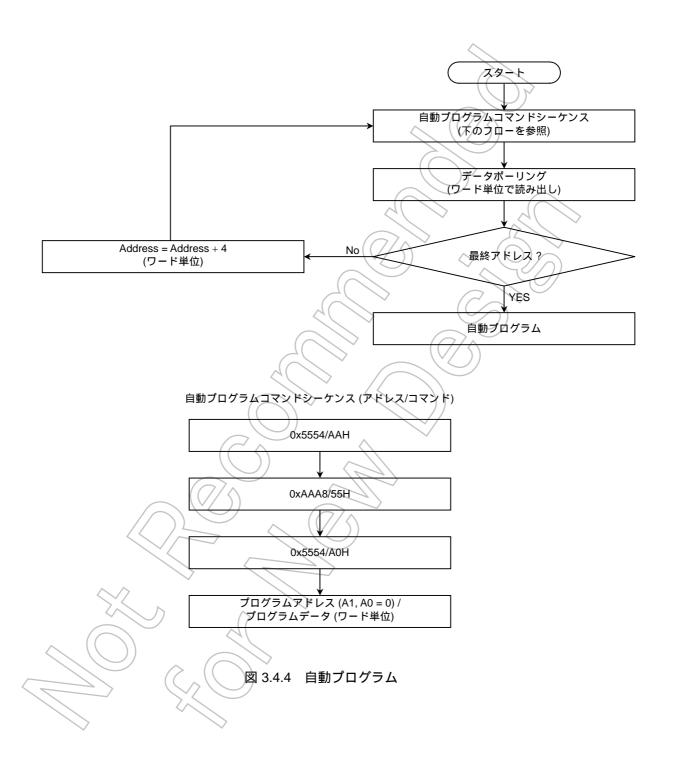

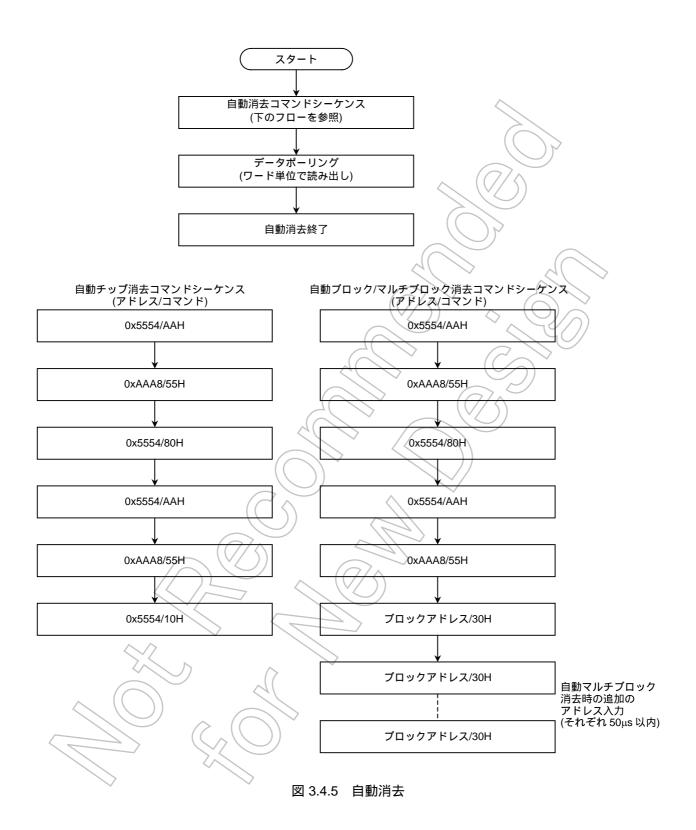

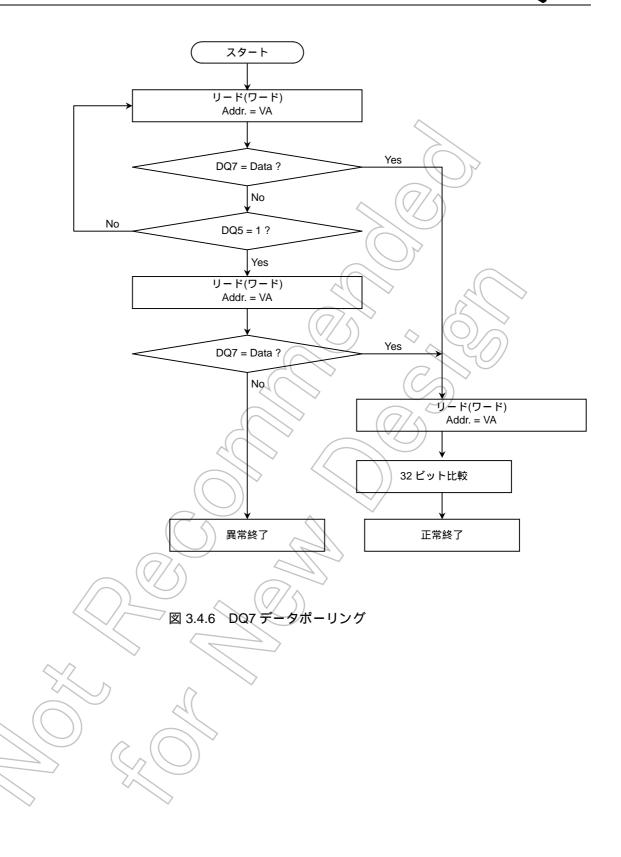

Flash 機能について、ハードウエアの構成およびその動作を説明します。本デバイスは TMP1962C10BXBG の内蔵 ROM を内蔵フラッシュメモリに置き換えたものです。その他の構成および機能は TMP1962C10BXBG と同一です。ここに記載されていない機能については TMP1962C10BXBG のデータシートを参照してください。

# 3.1 フラッシュメモリ

#### 3.1.1 特長

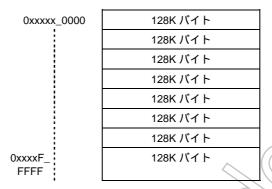

1) メモリ容量

TMP1962 はフラッシュメモリ 8 Mビット (1024K バイト) を搭載しています。構成は 8 ブロック (128K バイト  $\times$  8) になっており、各ブロック個別に書き込み/消去を禁止することができます。 CPU から内蔵フラッシュメモリをアクセスする場合、データバス幅は 32 ビットとなります。ライタにより書き替えを行う場合 (ライタモード) は 16 ビット幅のアクセスとなります。

- フラッシュメモリアクセス 本デバイスではインタリーブアクセスです。

- 3) 書き込み/消去時間

書き込み時間 (Verify 含む): 15 秒/Chip (Typ)

消去 (Verify 含む): 40 秒/Chip (Typ)

(注)上記値は理論時間を表しており、データ転送時間などは含まれていません。 Chip 当たりの時間はユーザーの書き替え方法により異なります。

4) プログラミング方法

ユーザーのボード上で書き替えが可能なオンボードプログラミングモードと、EPROM ライタで書き替えを行うライタモードがあります。

• オンボードプログラムモード 一

- 1) ユーザーブートモード

ユーザー独自の書き替え方法をサポート

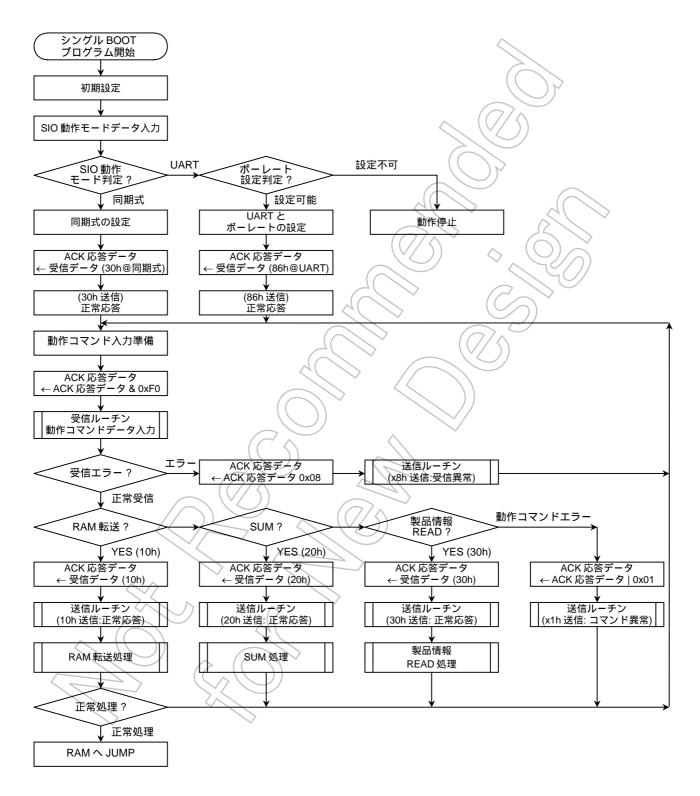

2) シングルブートモード

シリアル転送 (当社オリジナル) での書き 替え方法をサポート

ライタモード

汎用 EPROM ライタでの書き替えをサポート。

#### 5) 書き替え方式

本デバイス内蔵のフラッシュメモリは、一部の機能を除き JEDEC 標準機能に準拠しています。このため、外部メモリとしてフラッシュメモリをご使用になられている場合でも、本 LSI への移行が容易です。また、フラッシュメモリ内に書き込み、チップ消去など自動で行う回路を内蔵していますので、書き込み、消去動作自身に係わる複雑なフローをユーザーがプログラムで組む必要がありません。

本デバイスでは、ライタでのフラッシュデータの読み出しを禁止する、セキュリティ機能を追加しています。一方、書き替え禁止を設定するプロックプロテクトは、コマンド (ソフトウエア) による対応のみで 12 V 電圧を印加して設定する方式 (ハードウエア) には対応できません。前記セキュリテイ機能は全8BLOCK全てにブロックプロテクトを掛けると自動的に有効になり、ブロックプロテクトの解除を行うと内部データが自動的に消去され、その後にブロックプロテクトが解除されます。

| JEDEC 準拠の機能 | 変更、追加、削除した機能                                            |

|-------------|---------------------------------------------------------|

|             | <変更> ブロックプロテクト (ソフトウエアプロテクトのみサポート) <削除> 消去レジューム/サスペンド機能 |

# 3.1.2 フラッシュ部ブロック部

図 3.1.1 フラッシュ部ブロック図

# 3.2 動作モード

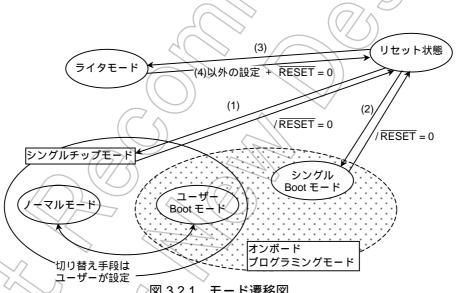

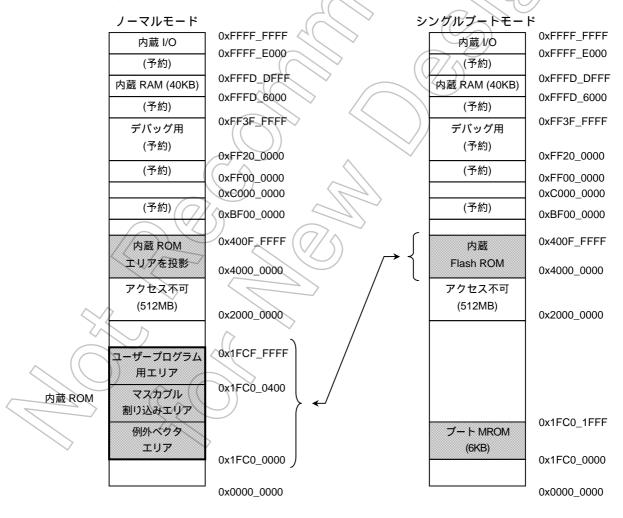

本デバイスは内蔵フラッシュメモリを使用しない場合を含めて、5 通りの動作状態 (モード) が存在します。

表 3.2.1 動作モード説明

| 動作モード名     | 動作の内容                                                        |

|------------|--------------------------------------------------------------|

| 動作で一下名     | 動IFの内台                                                       |

| シングルチップモード | リセット解除後、内蔵のフラッシュメモリから起動します。                                  |

|            | リセット立ち上がり時には INTLV 端子の"H"レベルの状態にしてください。                      |

|            | $\langle \langle \langle \langle \rangle \rangle \rangle$    |

|            | 本動作モードの中で、ユーザーのアプリケーションプログラムを実行するモードと、ユーザーのセット               |

| ノーマルモード    | 上でフラッシュメモリの書き替えを実行するモードとに分けて定義します。前者を「ノーマルモード」、              |

|            | 後者を「ユーザーブートモード」と呼びます。                                        |

|            |                                                              |

|            | この両者の切り替えはユーザーが独自に設定できます。                                    |

| ユーザーブートモード | 例えばポート 00 が '1' のときノーマルモード、'0' のときにユーザーブートモードというように自由に       |

|            | 設計することが可能です。                                                 |

|            | ユーザーはアプリケーションプログラムの一部に切り替えを判定するためのルーチンを準備してくだ                |

|            | til.                                                         |

| シングルブートモード | リセット解除後、内蔵する Boot ROM (Mask ROM) から起動します。Boot ROM には、本デバイスのシ |

|            | リアルポートを経由してユーザーのセット上で書き替えを行うことができるアルゴリズムがプログラ                |

|            | ムされています。シリアルポートにより外部ホストと接続し、規定されたプロトコルでデータの転送を               |

|            | 行うことで内蔵フラッシュの書き替えが実行できます。                                    |

| ライタモード     | 汎用の EPROM ライタで内蔵フラッッシュメモリを書き替えるためのモードです。規定のプログラムア            |

|            | ダプタと、推奨するライタをご使用ください。                                        |

上記表において、プログラムが可能なフラッシュメモリの動作モードは ユーザーブートモード、シングルブートモード、ライタモードの3つです。このうち、ユーザーのセット上で内蔵フラッシュメモリの書き替えが可能なモードは、ユーザーブートモードとシングルブートモードで、この2つを総称してオンボードプログラミングモードと定義します。

シングルチップ、シングルブートおよびライタの各動作モードは、リセット状態で入力端子 BW0、 BW1、 $\overline{\mathrm{BOOT}}$ 、 $\overline{\mathrm{INTLV}}$ のレベルを外部で設定することにより決定されます。 $\overline{\mathrm{PJ2}}(\overline{\mathrm{BOOT}})$ および PA 2 ( $\overline{\mathrm{INTLV}}$ )はリセット解除後には汎用ポートとして使用できます。

CPU はライタモードを除き、状態設定後リセットを解除することにより各動作モードで動作を開始します。ライタモードはRESET = "0" のまま使用します。それぞれモード設定後は動作中にレベルの変更がないようにしてください。以下に各動作モードの設定方法とモード遷移図を示します。

|     | F1         |                          |

|-----|------------|--------------------------|

|     | 動作モード      | 入力端子                     |

|     | ±311 C 1   | RESET BWO BW1 BOOT INTLY |

| (1) | シングルチップモード | 0 1 1 1 1                |

| (2) | シングルブートモード | 0 1 1 1 0 *1             |

| (3) | ライタモード     | 0 0 1 *1 *1              |

表 3.2.2 動作モード設定表

\*1 Don't Care。 ただし、0 もしくは 1 に固定。

図 3.2.1 モード遷移図

()数字は上表の対応するモードの入力端子状態に設定することを意味します。

# 3.2.1 リセット動作

本デバイスにリセットをかけるには、電源電圧が動作電圧範囲内で、かつ内部発振器の発振が安定した状態で、少なくとも 12 システムクロック間 (40.5 MHz 動作で PLL 使用時は 2.37 (40.5 RESET) 入力を "0" にしてください。

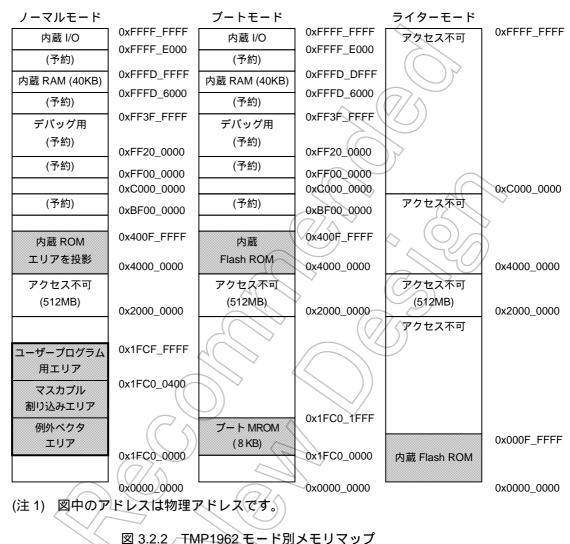

#### 3.2.2 モード別メモリマップ

本製品では動作モードごとにメモリマップが変わります。以下に、各動作モードごとのメモ リマップを示します。

128KB Block-0 128KB Block-1 Block-2 128KB Block-3 128KB Block-4 128KB Block-5 128KB

Block-6 128KB Block-7 128KB 1024KB

図 3.2.3 ブロック分割

| 表 3.2.3 モード | 別ブトック | フアドレス | 節用表 |

|-------------|-------|-------|-----|

|-------------|-------|-------|-----|

|         | ユーザ Boot モード                                                  | Boot モード                  | ライタモード                    |

|---------|---------------------------------------------------------------|---------------------------|---------------------------|

| Block-0 | 0x1FC0_0000 ~ 0x1FC 1_FFFF<br>(または 0x4000_0000 ~ 0x4001_FFFF) | 0x1FC0_0000~0x1FC1_FFFF   | 0x0000_0000 ~ 0x0001_FFFF |

| Block-1 | 0x1FC2_0000 ~ 0x1FC3_FFFF<br>(または 0x4002_0000 ~ 0x4003_FFFF)  | 0x1FC2_0000 ~ 0x1FC3_FFFF | 0x0000_8000 ~ 0x0003_FFFF |

| Block-2 | 0x1FC4_0000 ~ 0x1FC5_FFFF<br>(または 0x40040000 ~ 0x4005_FFFF)   | 0x1FC4_0000 ~ 0x1FC5_FFFF | 0x0001_0000 ~ 0x0005_FFFF |

| Block-3 | 0x1FC6_0000 ~ 0x1FC7_FFFF<br>(または 0x4006_0000 ~ 0x4007_FFFF)  | 0x1FC6_0000 ~ 0x1FC7_FFFF | 0x0001_8000 ~ 0x0007_FFFF |

| Block-4 | 0x1FC8_0000 ~ 0x1FC9_FFFF<br>(または0x4008_0000 ~ 0x4009_FFFF)   | 0x1FC8_0000 ~ 0x1FC9_FFFF | 0x0002_0000 ~ 0x0009_FFFF |

| Block-5 | 0x1FCA_0000 ~ 0x1FCB_FFFF<br>(または 0x400A_0000 ~ 0x400B_FFFF)  | 0x1FCA_0000 ~ 0x1FCB_FFFF | 0x0002_8000 ~ 0x000A_FFFF |

| Block-6 | 0x1FCC_0000 ~ 0x1FCD_FFFF<br>(または 0x400C_0000 ~ 0x400D_FFFF)  | 0x1FCC_0000 ~ 0x1FCD_FFFF | 0x0003_0000 ~ 0x000B_FFFF |

| Block-7 | 0x1FCE_0000 ~ 0x1FCF_FFFF<br>(または 0x400E_0000 ~ 0x400F_FFFF)  | 0x1FCE_0000 ~ 0x1FCF_FFFF | 0x0003_8000 ~ 0x000C_FFFF |

## 3.2.3 インターリーブ

リセット信号の立ち上がりでポート J3(PJ3)の "H" レベルをサンプリングしてインターリーブモードになります。本デバイスでは PJ3 を "H" レベルに設定してください。

# 3.2.4 ブロックプロテクト

ブロック分割されたそれぞれのブロック(128KB×8)は、独立したプロテクトビットを有し、ブロックプロテクトコマンドを使用することによりプログラム/消去を無効にする(ロックする)ことが可能です。チップ消去、もしくはプロテクトされたブロックを含むマルチブロック消去を行った場合は、プロテクトされたブロックのみ消去されずにほかのブロックは消去されます。ブロックプロテクトはフラッシュメモリセルで操作するために電源オフしてもプロテクト情報は保持されます。また、全 Blaock にプロテクトを掛けると、後述のライターモードでの読み出し動作も禁止されて、セキュリテイ機能を実現できます。

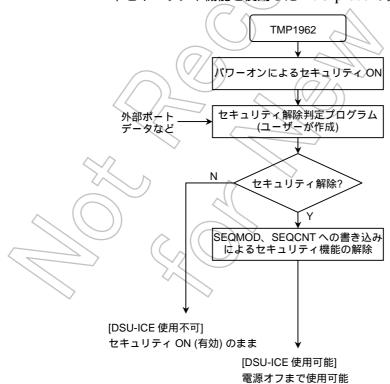

#### 3.2.5 DSU-probe インタフェース

DSU-probe を利用してデバッグするときに使用します。DSU-probe と接続される専用 I/Fです。DSU-probe を利用したデバッグの詳細に関しては、ご使用の DSU-probe の取扱説明書を参照してください。ここでは、DSU モードに関するセキュリティ機能について説明します。

#### (1) セキュリティ機能

本デバイスは、オンボード上で DSU-probe を使用してデバッグが可能です。このため、ユーザー以外の第三者が容易に内蔵フラッシュのデータを読み出させないようにするセキュリティ機能をもっています。セキュリティ機能を有効にすることにより、DSU-probeを使用して内蔵フラッシュの内容を読み出すことは不可能になります。後述の内蔵フラッシュ本体へのセキュリティ機能とあわせてご使用願います。

(2) セキュリティオン (DSU-probe を使用してのデバッグを無効)

ユーザーはプログラムデバッグ完了時に、ブラッシュの全8ブロック全でに後述のプロテクトコマンドを発行してプロテクトをかける事により、フラッシュ本体に対してセキュリティ機能を有効にします。この状態ではライタを使用してリードを行っても内蔵フラッシュのデータはリードできません。電源オフ後、次のパワーオン時にセキュリティ機能がセットされ、セキュリティが解除されるまで DSU-probe を使用してのデバッグは不可能となります。

(3) セキュリティオフ (DSU-probe を利用してのデバッグを有効)

セキュリティを解除する方法は、暴走などによる偶発解除を防ぐために二重構造になっており、セキュリティモードレジスタ SEQMOD<SEQON> = "0" にし、セキュリティコード "0x0000\_00C5" をセキュリティ制御レジスタ SEQCNT に書き込みます。この後、DSU-probe を使用したデバッグが有効になります。電源をオフしない状態で、SEQMOD<SEQON> = "1"にし、SEQCNTに "0x0000\_00C5" を書き込むことにより再びセキュリティ機能が有効になります。

SEQMOD (0xFFFF\_E510)

|   |            |          |          |     | 100       |      |    |    |           |

|---|------------|----------|----------|-----|-----------|------|----|----|-----------|

|   |            | 31       | 30       | 29  | 28        | → 27 | 26 | 25 | 24        |

|   | bit Symbol |          |          |     | 7         |      |    |    |           |

|   | Read/Write |          | )        | -(O | $/\wedge$ |      |    |    |           |

|   | リセット後      |          |          |     |           |      |    |    |           |

|   | 機能         |          |          |     |           |      |    |    |           |

|   |            | 23       | 22 —     | 21  | 20        | 19   | 18 | 17 | 16        |

|   | bit Symbol | <b>\</b> |          |     |           |      |    |    |           |

| 4 | Read/Write |          |          |     |           |      |    |    |           |

|   | リセット後      |          | $\wedge$ |     |           |      |    |    |           |

|   | 機能         |          | AI.      |     |           |      |    |    |           |

|   | <b>***</b> | 15       | 14       | 13  | 12        | 11   | 10 | 9  | 8         |

|   | bit Symbol | > ((     |          |     |           |      |    |    |           |

| / | Read/Write |          | $\cup$ ) |     |           |      |    |    |           |

|   | リセット後      |          | )        |     |           |      |    |    |           |

|   | 機能         | , ///    |          |     |           |      |    |    |           |

|   |            | 7        | 6        | 5   | 4         | 3    | 2  | 1  | 0         |

|   | bit Symbol |          |          |     |           |      |    |    | SEQON     |

|   | Read/Write |          |          |     |           |      |    |    | R/W       |

|   | リセット後      |          |          |     |           |      |    |    | 1         |

|   | 機能         |          |          |     |           |      |    |    | 1: セキュリティ |

|   |            |          |          |     |           |      |    |    | オン        |

|   |            |          |          |     |           |      |    |    | 0: セキュリティ |

|   |            |          |          |     |           |      |    |    | オフ        |

(注) 本レジスタは32 ビットのアクセスになり、ビット1 からビット31 はリードすると0 になります。

SEQCNT (0xFFFF\_E514)

|            | 31                                | 30 | 29      | 28        | 27     | 26   | 25   | 24 |  |

|------------|-----------------------------------|----|---------|-----------|--------|------|------|----|--|

| bit Symbol |                                   |    |         |           |        |      |      |    |  |

| Read/Write | W                                 |    |         |           |        |      |      |    |  |

| リセット後      |                                   |    |         |           |        |      |      |    |  |

| 機能         |                                   |    | "0x0000 | _00C5" をラ | イトしてく  | ださい。 |      |    |  |

|            | 23                                | 22 | 21      | 20        | 19     | 18   | 17   | 16 |  |

| bit Symbol |                                   |    |         |           |        |      |      |    |  |

| Read/Write |                                   |    |         | V         | ٧      |      |      |    |  |

| リセット後      |                                   |    |         |           |        |      |      |    |  |

| 機能         | "0x0000_00C5" をライトして <i>くだ</i> さい |    |         |           |        |      |      |    |  |

|            | 15                                | 14 | 13      | 12        | 11     | (10) | 9    | 8  |  |

| bit Symbol |                                   |    |         |           |        |      |      |    |  |

| Read/Write |                                   |    |         | V         | v ((   | 15   |      |    |  |

| リセット後      |                                   |    |         |           |        | 7)   |      |    |  |

| 機能         |                                   |    | "0x000  | 0_00C5"を  | ライトしてく | ください |      |    |  |

|            | 7                                 | 6  | 5       | 4         | 3      | 2    | d(1) | 0  |  |

| bit Symbol |                                   |    |         |           |        |      |      |    |  |

| Read/Write |                                   |    |         | . ((//v   | v\     | , (( | 7)   |    |  |

| リセット後      |                                   |    |         |           |        | 0,6  |      |    |  |

| 機能         | "0x0000_00C5" をライトしてください          |    |         |           |        |      |      |    |  |

- (注1) 本レジスタは32ピットのアクセスになります。

- (注 2) 本セキュリティ機能は保証できるものではなく、内蔵 ROM の守秘が第一の場合には、マスク ROM 内蔵タイプの使用をお願い致します。

- (4) ユーザー使用例

本セキュリティ機能を使用した DSU-probe の使用例を以下に示します。

図 3.2.4 セキュリティ機能の使用例

#### 3.3 オンボードプログラミングモード

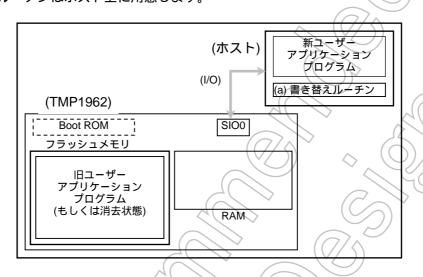

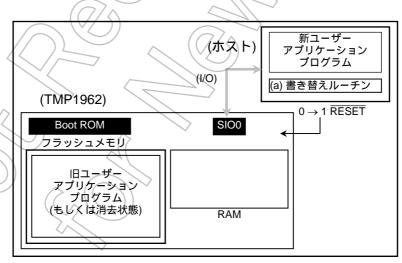

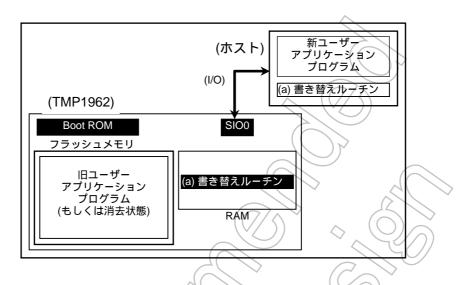

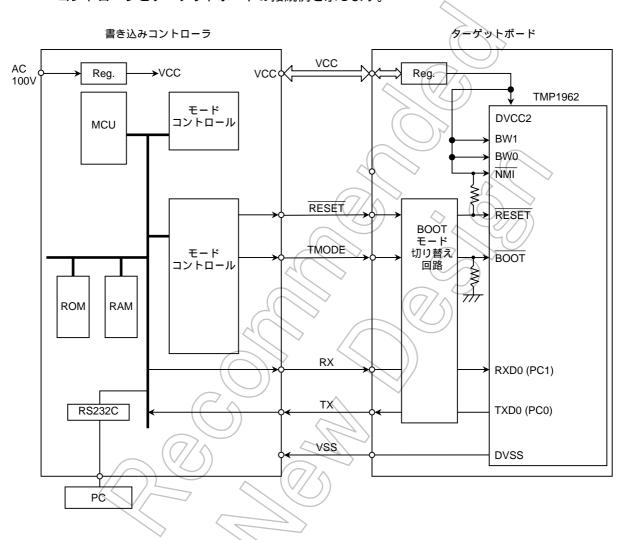

ユーザーのシステムセット上で書き替えができるオンボードプログラミングモードは、シリアル I/O を利用した当社独自の書き替え方式をサポートするシングルブートモード、シングルチップモード内においてユーザーが独自に書き替え方式を構築できるユーザーブートモードがあります。

また、本デバイスはライタモード中に、ROM データの読み出しを禁止する「セキュリティ機能」を持っています。オンボードプログラミング完了時にセキュリティ機能をオンにしておくことで、第三者への ROM データ流出を最小限にすることができます。

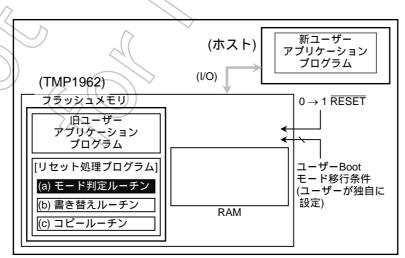

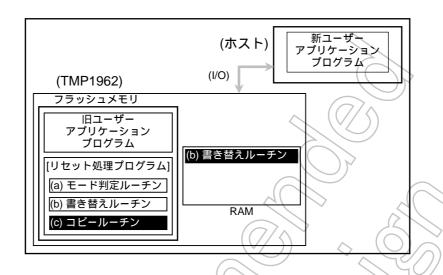

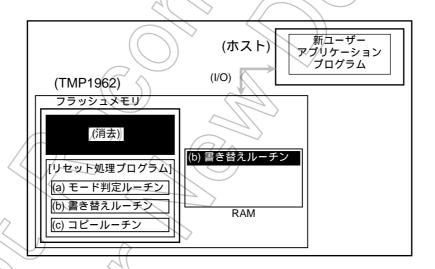

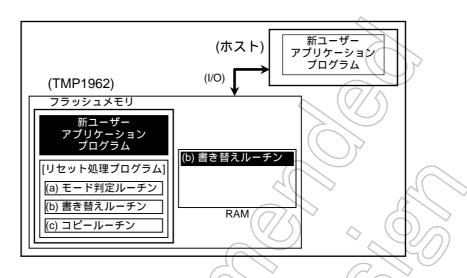

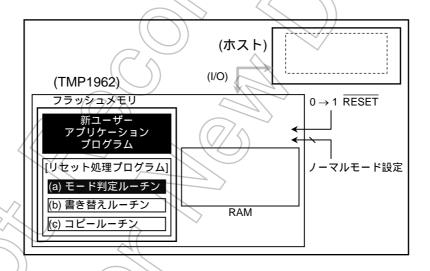

## 3.3.1 ユーザーブートモード (シングルチップモード)

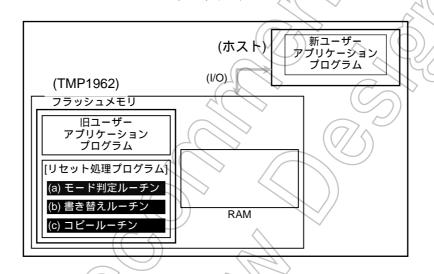

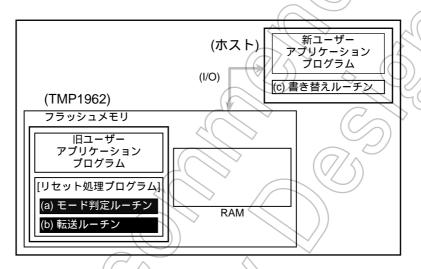

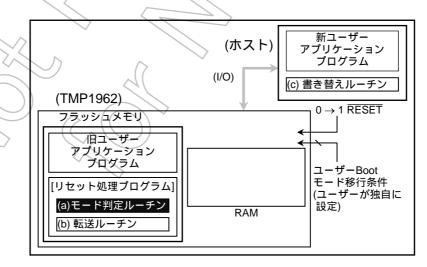

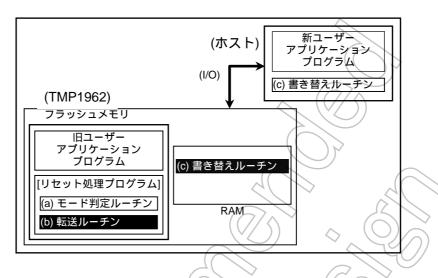

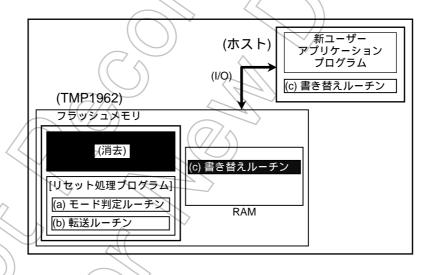

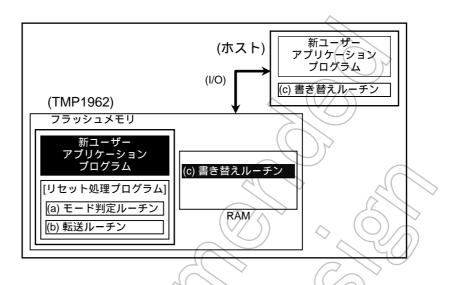

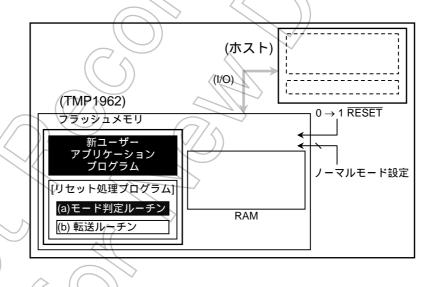

ユーザーブートモードは、ユーザー独自のフラッシュメモリ書き替えルーチンを使う方法です。ユーザーアプリケーション上で用意されているフラッシュメモリ書き替え用のプログラムで用いる、データ転送バスがシリアル I/O と異なる場合に使用します。動作はシングルチップモード上で行います。このため、シングルチップモードにおいて通常のユーザーアプリケーションプログラムが動作しているノーマルモードから、フラッシュを書き替えるためのユーザーブートモードに移行する必要があります。したがって、条件判定を行うプログラムをユーザーアプリケーションの中で、リセット処理プログラムの中に組み込んでください。

このモード切り替えの条件設定は、本デバイスの I/O を使用してユーザーのシステムセット条件に合わせて独自に構築してください。また、ユーザーブートモード移行後に使用するユーザー独自のフラッシュメモリ書き替えルーチンも同様にユーザーアプリケーションの中にあらかじめ組み込んでおき、ユーザーブートモード移行後にこれらのルーチンを使用して書き替えを行ってください。なお、内蔵フラッシュメモリは消去/書き込み動作モード中はフラッシュのデータを読み出せません。このため、書き替えルーチンはフラッシュメモリエリア外に格納して実行させる必要があります。また、シングルチップモード(通常動作モード)中に誤ってフラッシュの内容を書き替えないよう、書き替え処理が完了した後、必要なブロックにプロテクトをかけておくことを推奨します。あわせて、ユーザーブートモード中は、ノンマスカブルを含めたすべての割り込み発生を禁止してください。

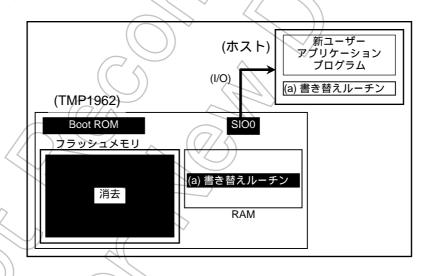

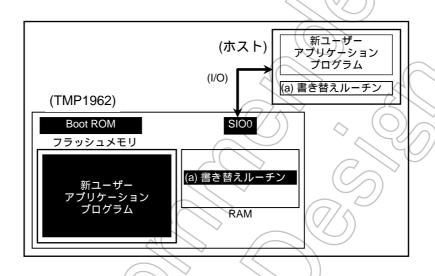

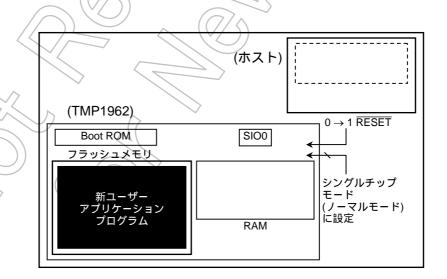

書き替えルーチンを内蔵フラッシュメモリに置く場合と、外部から転送する場合の 2 ケースを例に、以下 (1-A)、(1-B) にその手順を説明します。フラッシュメモリへの書き込み/消去 方法の詳細は、「3.4 オンボードプログラミングでのフラッシュメモリ書き込み/消去」を参照してください。

#### ユーザーブートモード

(1-A) 書き替えルーチンをフラッシュメモリに内蔵する場合の手順例

#### (Step-1)

ユーザーは、あらかじめ どのような条件 (例えば端子状態) に設定されたらユーザーブートモードに移行するか、どの I/O バスを使用してデータ転送を行うかを決め、それに合った回路の設計、プログラムの作成を行います。ユーザーは本デバイスをボードに組み込む前に、あらかじめフラッシュメモリ上の任意のブロックにライタなどを使用して以下に示す3つのプログラムを書き込んでおきます。

(a) モード判定ルーチン: 書き替え動作に移るためのプログラム

(b) フラッシュ書き換えルーチン: 書き替えデータを外部から取り込み、フラッシュメモリを書

き替えるためのプログラム

(c) コピールーチン: 上記 (b) を内蔵 RAM または外部メモリにコピーするための プログラム

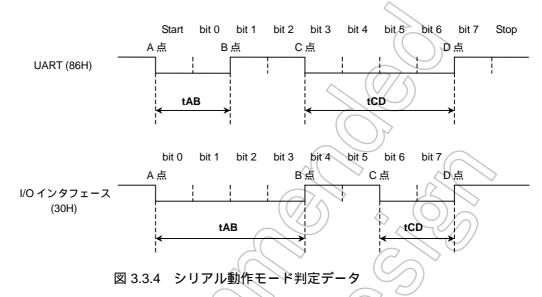

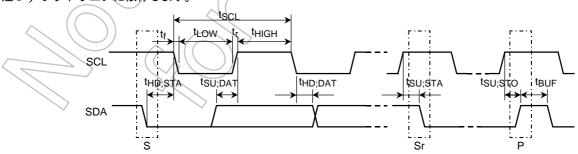

#### (Step-2)