# **TOSHIBA**

株式会社 東芝 セミコンダクター社

● 当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり 故障することがあります。当社半導体製品をご使用いただく場合は、半導体製品の 誤作動や故障により、生命・身体・財産が侵害されることのないように、購入者側の責 任において、機器の安全設計を行うことをお願いします。 なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用い ただくと共に、考慮されるべき注意事項や条件について「東芝半導体製品の取り扱 い上のご注意とお願い」、「半導体信頼性ハンドブック」などでご確認ください。

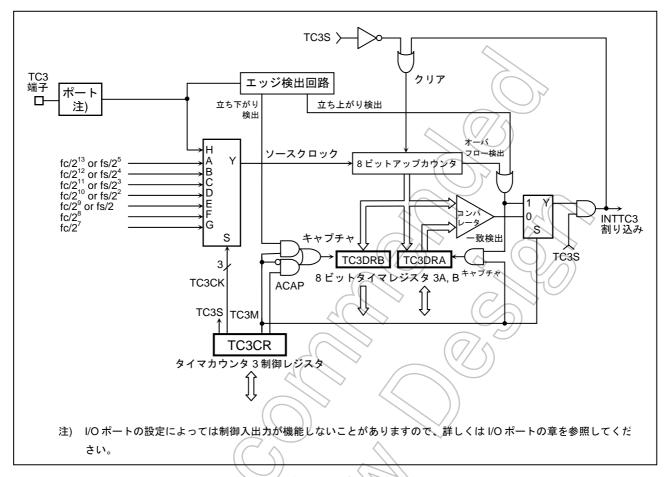

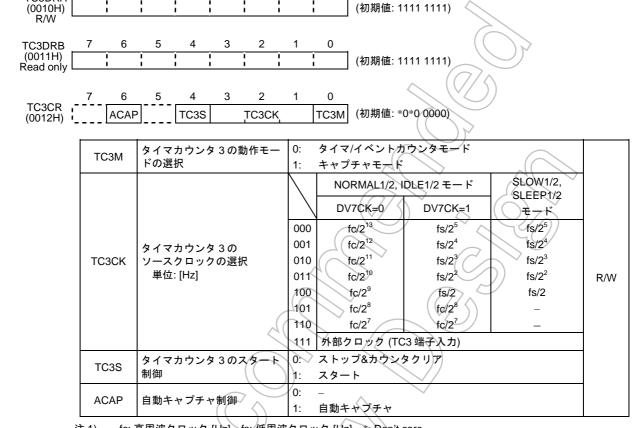

021023\_A

● 本資料に掲載されている製品は、一般的電子機器 (コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電機器など)に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や誤作動が直接人命を脅かしたり人体に危害を及ぼす恐れのある機器 (原子力制御機器、航空宇宙機器、輸送機器、交通信号機器、燃焼制御、医療機器、各種安全装置など)にこれらの製品を使用すること(以下"特定用途"という)は意図もされていませんし、また保証もされていません。本資料に掲載されている製品を当該特定用途に使用することは、お客様の責任でなされることとなります。021023\_B

- 本資料に掲載されている製品を、国内外の法令、規則及び命令により製造、使用、 販売を禁止されている応用製品に使用することはできません。060106\_Q

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、 その使用に際して当社および第三者の知的財産権その他の権利に対する保証または 実施権の許諾を行うものではありません。021023\_C

- 本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されているものです。021023\_E

- 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。021023\_D

- マイコン製品の信頼性予測については、「品質保証と信頼性/取り扱い上のご注意とお願い」の 1.3 項に記載されておりますのでかならずお読みください。030519\_S

# 改訂履歴

| 日付        | 版 | 改訂理由          |

|-----------|---|---------------|

| 2007/8/24 | 1 | First Release |

| 2008/8/29 | 2 | 内容改訂          |

# UART ノイズ除去時間設定における注意事項

本製品に搭載されている UART を使用する場合、転送クロック選択 (BRG) により、ノイズ除去時間設定(RXDNC設定)には以下の制約があります。"〇"の箇所にて使用し、"一"の箇所は設定しないでください。

なお、転送クロックとしてタイマカウンタ割り込みを使用する場合、転送クロックはタイマカウンタソースクロック [Hz] ÷ TTREG 設定値で計算されます。

|                            |             |                 | <u> </u>                      | $\langle ( / ) \rangle$       |                                   |

|----------------------------|-------------|-----------------|-------------------------------|-------------------------------|-----------------------------------|

|                            |             |                 | RXDN                          | C設定                           |                                   |

| BRG 設定                     | 転送クロック [Hz] | 00<br>(ノイズ除去なし) | 01<br>(31/fc[s] 未満の<br>パルス除去) | 10<br>(63/fc[s] 未満の<br>パルス除去) | 11<br>(127/fc[s] 未満の<br>パルス除去)    |

| 000                        | fc/13       | 0               | 000                           | <b>&gt;</b> 0                 | $\langle \langle \rangle \rangle$ |

| 110                        | fc/8        | 0               |                               | > - 52                        |                                   |

| (タイマカウンタ割り込<br>みでの転送クロックが右 | fc/16       | 0               | (Ø/ Ś)                        | <u>~</u> (€                   | ))~-                              |

| 記となる場合)                    | fc/32       | 0               | 0                             | 0                             | S())-                             |

| 上記以                        | .外          | 0               | 7                             | 0                             | 0                                 |

|                            |             |                 |                               |                               |                                   |

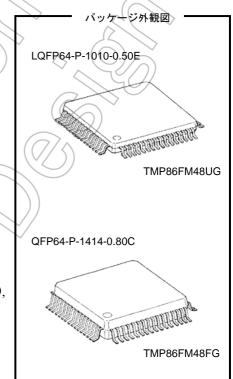

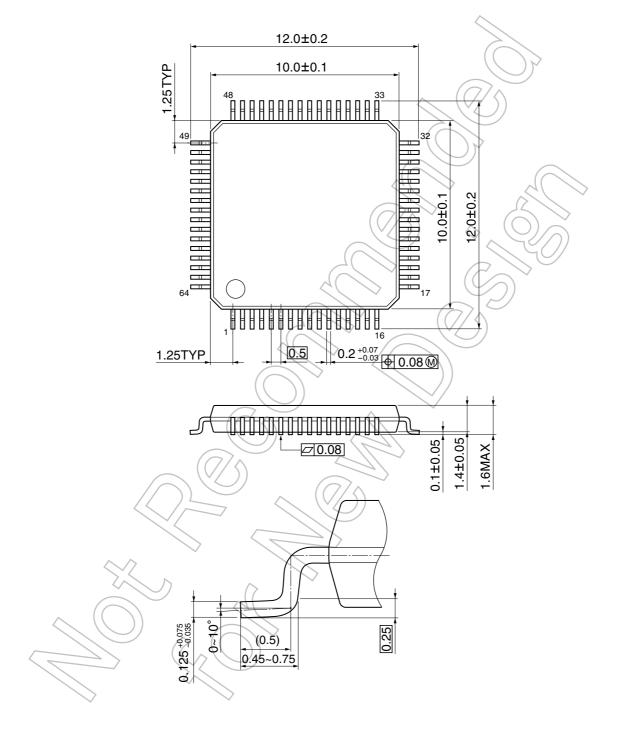

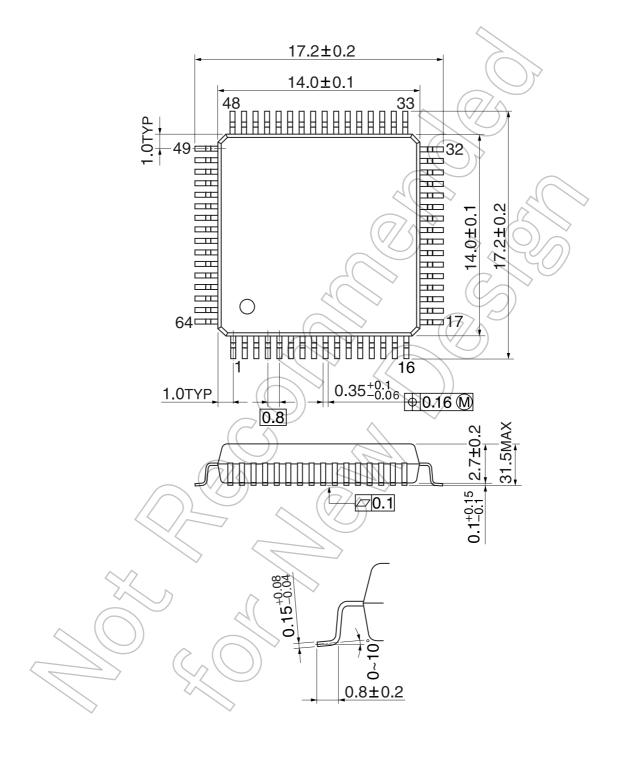

# CMOS 8 ビット マイクロコントローラ TMP86FM48UG/FG

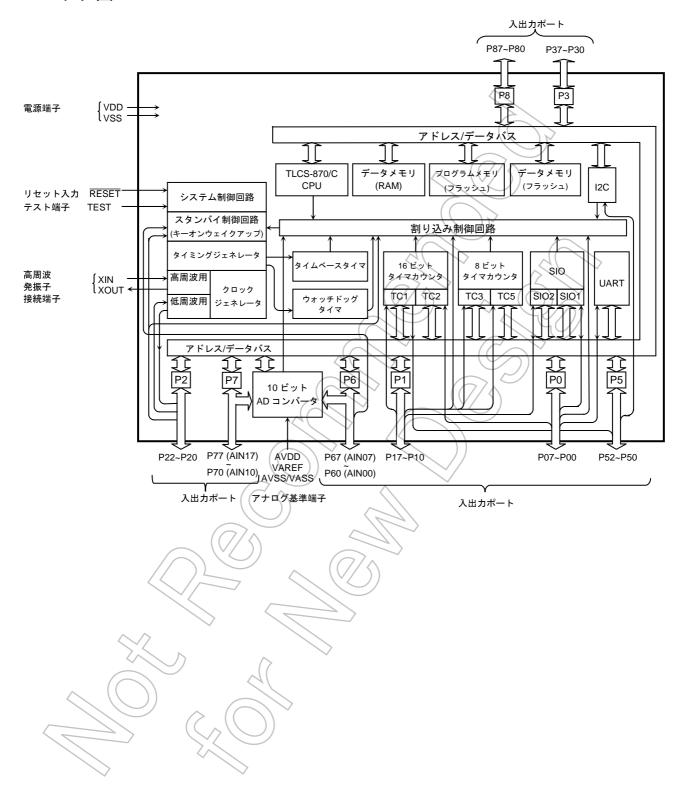

TMP86FM48 はTLCS-870/C シリーズコアに 3Tr NAND 型フラッシュ EEPROM (以下フラッシュ と称す), RAM, 多機能タイマカウンタ, 非同期型シリアルインタフェース (UART), 同期型シリアル インタフェース(SIO,  $I^2C$ ), 10 ビット AD コンバータおよび 2 系統の発振回路などを内蔵した高速, 高 機能8ビットシングルチップマイクロコンピュータです。

| 製品形名        | フラッシュメモリ<br>(Program area) | フラッシュメモリ<br>(Data area) | RAM            | パッケージ               | エミュレーション<br>チップ |

|-------------|----------------------------|-------------------------|----------------|---------------------|-----------------|

| TMP86FM48UG | 32256×8ビット                 | 512×8 ビット               | 2048×8ビット      | LQFP64-P-1010-0.50E | TMP86C948XB     |

| TMP86FM48FG | 32230 × 6 L 7 F            | 312 × 0 € 9 1           | 2040 × 0 € 9 1 | QFP64-P-1414-0.80C  | TWI GOC 940 AB  |

# 特長

- 8 ビットシングルチップマイクロコンピュータ TLCS-870/C シリーズ

- 最小実行時間: 0.25 μs (16 MHz 動作時) 122 μs (32.768 kHz 動作時)

- 基本機械命令: 132 種類 731 命令

- 割り込み要因 20 要因 (外部: 5. 内部: 15)

- 入出力ポート (54 端子)

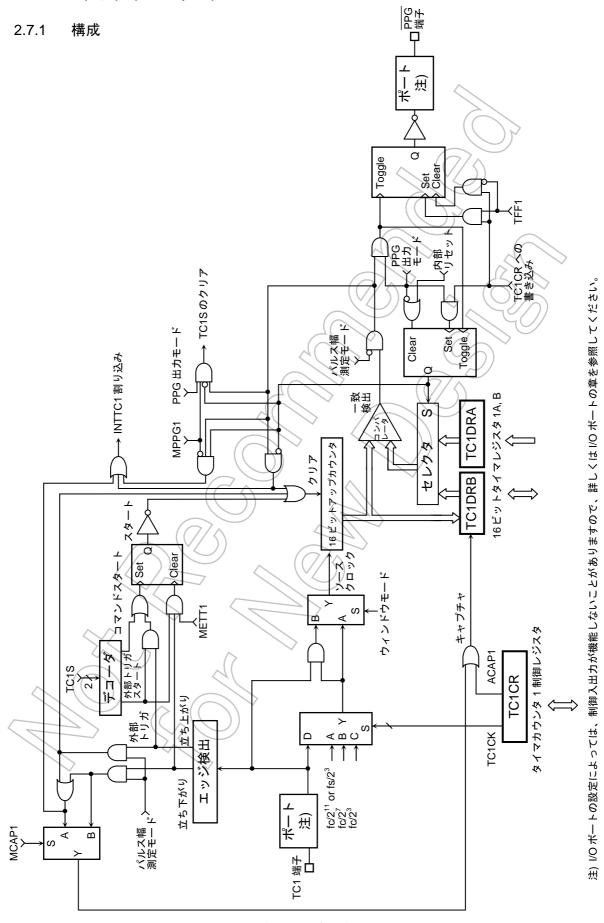

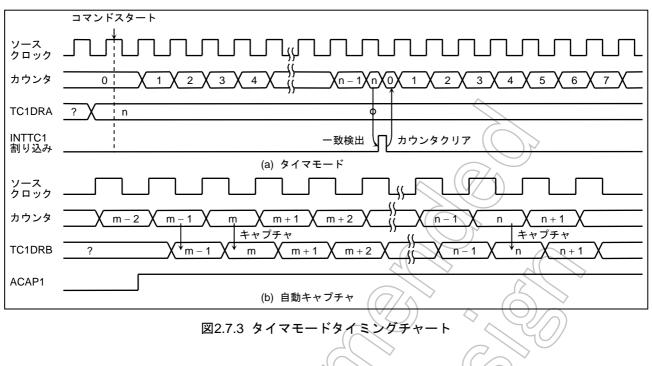

- 16 ビットタイマカウンタ: 2 チャネル

- タイマ, イベントカウンタ, パルス幅測定, 外部トリガタイマ、ウィンドウ、PPG 出力モード

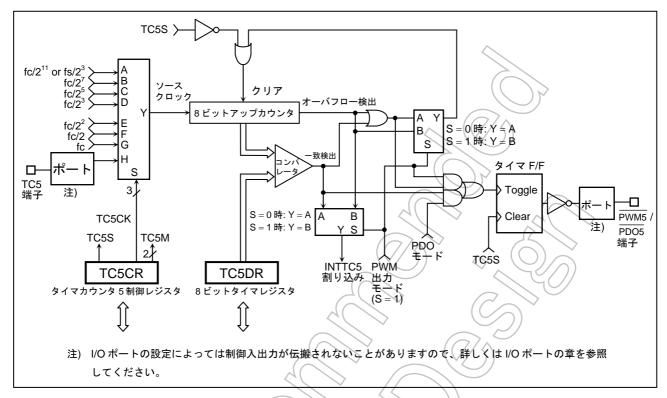

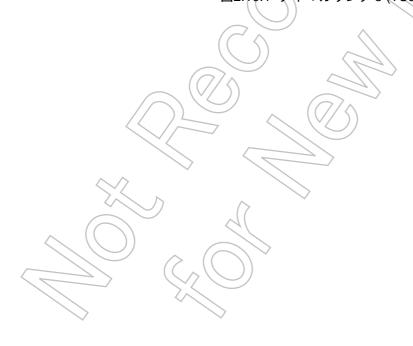

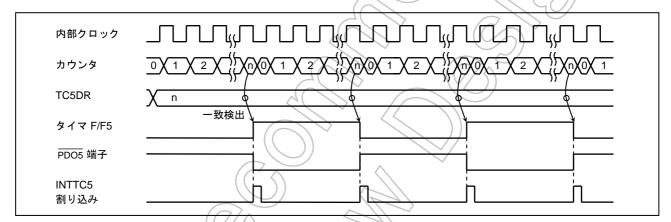

- 8ビットタイマカウンタ:2チャネル

- タイマ, イベントカウンタ, PWM (パルス幅変調出力), PDO (Programmable Divider Output), キャプチャモード

- タイムベースタイマ

- デバイダ出力機能

- ウォッチドッグタイマ

- 割り込み/リセット発生の選択 (プログラマブル)

- 当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり故障することがあります。当社半導体製品をご使用いただく場合は、半導体製品の誤作動や故障により、生命・身体・財産が侵害されることのないように、購入者側の責任において、機器の安全設計を行うことをお願いします。

なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用いただくと共に、考慮されるべき注意事項や条件について「東芝半導体製品の取り扱い上のご注意とお願い」、「半導体信頼性ハンドブック」などでご確認ください。 021023\_A

本資料に掲載されている製品は、一般的電子機器(コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電機器など)に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や誤作動が直接人命を脅かしたり人体に危害を及ぼす恐れのある機器(原子力制御機器、航空宇宙機器、輸送機器、交通信号機器、燃焼制御、医療機器、各種安全装置など)にこれらの製品を使用すること(以下 "特定用途"という)は意図もされていませんし、また保証もされていません。本資料に掲載されている製品を当該特定用途に使用することは、お客様の責任でなされることとなります。 021023\_B

本資料に掲載されている製品を、国内外の法会、相則および命会により製造、使用、販売を禁止されている原理製品に使用するこ

- 本資料に掲載されている製品を、国内外の法令、規則および命令により製造、使用、販売を禁止されている応用製品に使用するこ とはできません。 060106\_Q

- ◆本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社および第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。 021023\_C

- 本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されているものです。 021023 E

- ◆本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。 021023\_D

- マイコン製品の信頼性予測については、「品質保証と信頼性/取り扱い上のご注意とお願い」の 1.3 項に記載されておりますので必ずお読みください。 030519\_S

2007-08-24 86FM48-1

- ◆ シリアルインタフェース

- UART/SIO: 1 チャネル

- SIO: 1 チャネル

- I<sup>2</sup>C-bus: 1 チャネル

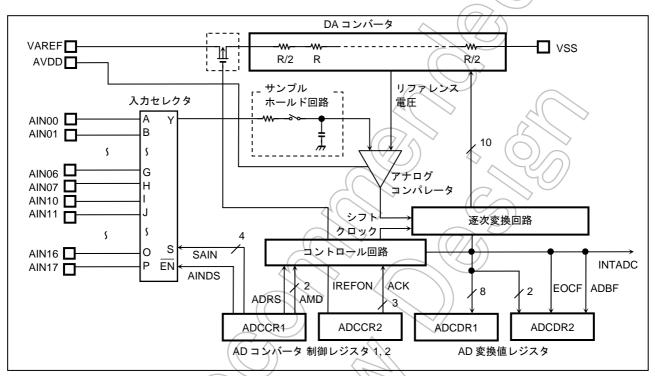

- ◆ 10 ビット逐次比較方式 AD コンバータ

- アナログ入力: 16 チャネル

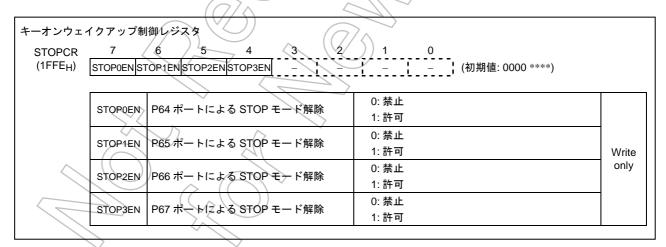

- ◆ キーオンウェイクアップ:4チャネル

- ◆ クロック発振回路: 2回路

- シングル/デュアルクロックモードの選択

- ◆ 低消費電力動作(9モード)

- STOPモード: 発振停止 (バッテリーコンデンサバッタアップ)

- SLOW1 モード: 低周波クロックによる低周波動作(高周波停止)

- SLOW2 モード: 低周波クロックによる低周波動作(高周波発振)

- IDLE0 モード: CPU 停止。周辺ハードウエアのうち、TBT のみ動作(高周波クロック)継続し、TBT 設定の基準時間経過により解除。

- IDLE1 モード: CPU 停止。周辺ハードウエアのみ動作(高周波クロック)継続し、割り込みで解除(CPU 再起動)

- IDLE2 モード: CPU 停止。周辺ハードウエアのみ動作 (高周波/低周波クロック) 継続し、 割り込みで解除

- SLEEP0 モード: CPU 停止。周辺ハードウエアのうち、TBT のみ動作(低周波クロック)継続し、TBT 設定の基準時間経過により解除。

- SLEEP1 モード: CPU 停止。周辺ハードウエアのみ動作(低周波クロック)継続し、割り込みで解除。

- SLEEP2 モード: CPU 停止。周辺ハードウエアのみ動作(高周波/低周波クロック)継続し、 割り込みで解除。

- ◆ 動作電圧: 1.8~3.6 V @ 8 MHz/32.768 kHz 2.7~3.6 V @ 16 MHz/32.768 kHz

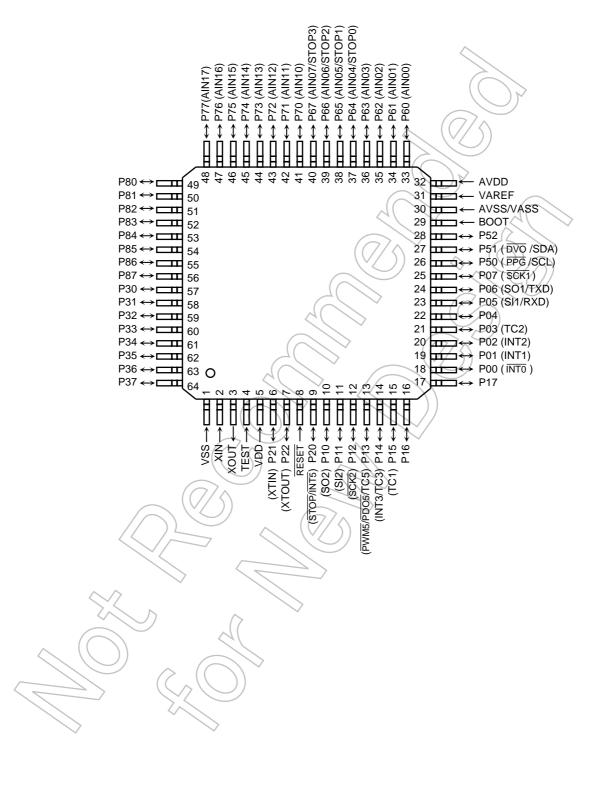

# ピン配置図 (上面図)

LQFP64-P-1010-0.50E QFP64-P-1414-0.80C

86FM48-3 2007-08-24

# ブロック図

86FM48-4 2007-08-24

# 端子機能 (1/2)

| 端子名                      | 入出力              |                                                                                                      | 機能                                      |               |  |

|--------------------------|------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------|--|

| P07 ( SCK1 )             | 入出力 (入出力)        | 8 ビットの入出力ポートです。                                                                                      | シリアルクロック入出力 1                           |               |  |

| P06 (TXD, SO1)           | 入出力 (出力)         | シリアルインタフェース出力、UART                                                                                   | UART データ出力, シリア                         | ルデータ出力 1      |  |

| P05 (RXD, SI1)           | 入出力 (入力)         | 出力として使用する場合は、出力ラッ                                                                                    | UART データ入力,シリアルデータ入力 1                  |               |  |

| P04                      | 入出力              | チ (PODR) を "1" に設定してくださ<br>い。                                                                        |                                         |               |  |

| P03 (TC2)                | 入出力 (入力)         | 入力ポート、シリアルインタフェース                                                                                    | タイマカウンタ 2 入力                            |               |  |

| P02 (INT2)               | 入出力 (入力)         | 入力、UART 入力、タイマカウンタ入力、                                                                                | 外部割り込み2入力                               |               |  |

| P01 (INT1)               | 入出力 (入力)         | 外部割り込み入力として使用する場合<br>は、PODR を "1" に設定した後、出力                                                          | 外部割り込み1入力                               |               |  |

| P00 ( INTO )             | 入出力 (入力)         | 回路制御 (POOUTCR) を "0" に設定<br>してください。                                                                  | 外部割り込み 0 入力                             |               |  |

| P17                      | 入出力              | 8 ビットの入出力ポートです。                                                                                      |                                         |               |  |

| P16                      | 入出力              | タイマカウンタ出力、シリアルインタ                                                                                    | ( ) ) '                                 |               |  |

| P15 (TC1)                | 入出力 (入力)         | フェース出力として使用する場合は、<br>出カラッチ (P1DR) を "1" に設定し                                                         | タイマカウンタ 1 入力                            |               |  |

| P14 (TC3, INT3)          | 入出力 (入力)         | てください。入力ポート、タイマカウ<br>」ンタ入力、外部割り込み入力、シリア                                                              | タイマカウンタ3入力,<br>外部割り込み3入力                |               |  |

| P13 ( PWM5 , PDO5 , TC5) | 入出力 (入出力)        | ルインタフェース入力として使用する                                                                                    | タイマカウンタ 5 入出力                           | $\rightarrow$ |  |

| P12 ( SCK2 )             | 入出力 (入出力)        | 場合は、P1DR を "1" に設定した後、<br>出力回路制御 (P1OUTCR) を "0" に                                                   | シリアルクロック入出力 2                           |               |  |

| P11 (SI2)                | 入出力 (入力)         | 設定してください。                                                                                            | シリアルデータ入力2                              |               |  |

| P10 (SO2)                | 入出力 (出力)         |                                                                                                      | シリアルデータ出力 2                             |               |  |

| P22 (XTOUT)              | 入出力 (出力)         | 3 ビットの入出カポートです。<br>入力ポート、外部割り込み入力として                                                                 | <br> 低周波発振子接続端子 (32<br> 外部クロック入力の場合、    |               |  |

| P21 (XTIN)               | 入出力 (入力)         | 使用する場合は、出カラッチ (P2DR)<br>を "1" に設定した後、出カ回路制御                                                          | XTOUTは開放します。                            |               |  |

| P20 ( INT5 ), ( STOP )   | 入出力 (入力)         | (P2OUTCR) を "0" に設定してくださ<br>い。                                                                       | 外部割り込み 5 入力, STO                        | Pモード解除入力      |  |

| P37~P30                  | 入出力              | 8 ビットの入出カポートです (N-ch 大電流)。入カポートとして使用する場合は、出カラッチ (P3DR) を "1" に設定した後、出カ回路制御 (P3OUTCR) を "0"に設定してください。 |                                         |               |  |

| P52                      | 入出力              | 3 ビットの入出カポートです (N-ch 大<br>電流)。<br>入カポート、I <sup>2</sup> C-bus インタフェース入                                |                                         |               |  |

| P51 ( DVO , SDA)         | 入出力<br>(出力, 入出力) | 出力として使用する場合は、出力ラッチ (P5DR) を "1" に設定した後、出力<br>回路制御 (P5OUTCR) を "0" に設定                                | デバイダ出力, I <sup>2</sup> C-bus シリ         | アルデータ入出力      |  |

| P50 ( PPG , SCL)         | 入出力<br>(出力,入出力)  | してください。タイマカウンタ1出力、<br>デバイダ出力として使用する場合は、<br>P5DR を "1" に設定してください。                                     | タイマカウンタ 1 出力, l <sup>2</sup> C<br>ック入出力 | -bus シリアルクロ   |  |

| P67 (AIN07, STOP3)       | 入出力 (入力)         | 8 ビットのプログラマブル入出力ポートです (トライステート)。1 ビット単位                                                              | STOP 3 入力                               |               |  |

| P66 (AIN06, STOP2)       | 入出力 (入力)         | で入力/出力の設定ができます。                                                                                      | STOP 2 入力                               | ]             |  |

| P65 (AIN05, STOP1)       | 入出力 (入力)         | 入力ポートとして使用する場合は、入<br>力制御 (P6CR2) を"1"に設定した                                                           | STOP 1 入力                               |               |  |

| P64 (AIN04, STOP0)       | 入出力 (入力)         | 後、入出力制御 (P6CR1) を "0" に設<br>定してください。                                                                 | STOP 0 入力                               | AD コンバータ      |  |

| P63 (AIN03)              | 入出力 (入力)         | アナログ入力、キーオンウェイクアッ                                                                                    |                                         | アナログ入力        |  |

| P62 (AIN02)              | 入出力 (入力)         | プ入力として使用する場合は、P6CR2<br>を "0" に設定した後、P6CR1 を "0" に                                                    |                                         |               |  |

| P61 (AIN01)              | 入出力 (入力)         | 設定してください。また、キーオンウェイクアップを使用する場合は、                                                                     |                                         |               |  |

| P60 (AIN00)              | 入出力 (入力)         | STOPCR <stopien>を "1" に設定してください。(i = 0~3)</stopien>                                                  |                                         |               |  |

86FM48-5 2007-08-24

# 端子機能 (2/2)

| P77 (AIN17) | 入出力 (入力) | 8 ビットのプログラマブル入出力ポー                                                                                                   |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------|

| P76 (AIN16) | 入出力 (入力) | トです (トライステート)。1 ビット単位                                                                                                |

| P75 (AIN15) | 入出力 (入力) | 】で入力/出力の設定ができます。<br>■ 入力ポートとして使用する場合は、入                                                                              |

| P74 (AIN14) | 入出力 (入力) | カガルードとして使用する場合は、ス<br>カ制御 (P7CR2) を "1" に設定した AD コンバータアナログ入力                                                          |

| P73 (AIN13) | 入出力 (入力) | 後、人出力制御 (P/CR1) を "0" に設                                                                                             |

| P72 (AIN12) | 入出力 (入力) | 定してください。<br>  アナログ入力として使用する場合は、                                                                                      |

| P71 (AIN11) | 入出力 (入力) | P7CR2 を "0" に設定した後、P7CR1                                                                                             |

| P70 (AIN10) | 入出力 (入力) | を"0"に設定してください。                                                                                                       |

| P87~P80     | 入出力      | 8 ビットの入出カポートです (N-ch 大<br>電流)。入カポートとして使用する場合<br>は、出カラッチ (P8DR) を "1" に設定<br>した後、出カ回路制御 (P8OUTCR) を<br>"0" に設定してください。 |

| XIN, XOUT   | 入力, 出力   | 高周波発振子接続端子。<br>外部クロックを入力する場合は、XIN 端子へ入力し、XOUT は開放してください。                                                             |

| RESET       | 入力       | リセット信号入力                                                                                                             |

| TEST        | 入力       | 出荷試験用端子。"L"レベルに固定してください。                                                                                             |

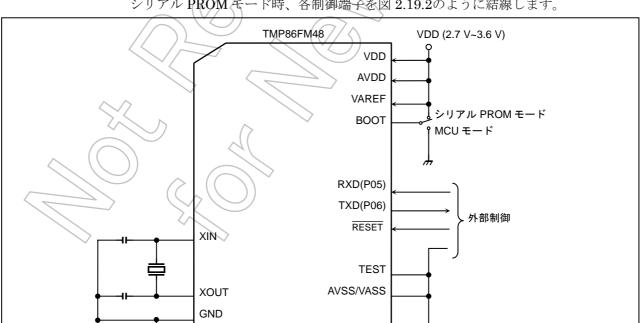

| воот        | 入力       | シリアル PROM モード制御入力端子。<br>シリアル PROM モードを起動する場合、BOOT 端子は"1"に設定してください。<br>MCU モードを起動する場合、BOOT 端子は"0"に設定してください。           |

| VDD, VSS    |          | 電源端子                                                                                                                 |

| VAREF       | 電源       | AD コンバータ用アナログ基準端子                                                                                                    |

| AVDD        | 电源       | AD コンバータ用電源端子                                                                                                        |

| AVSS/VASS   |          | AD コンバータ用電源端子/AD コンバータ用アナログ基準端子                                                                                      |

86FM48-6 2007-08-24

# 動作説明

# 1. CPUコア機能

CPU コアは、CPU, システムクロック制御回路, 割り込み制御回路およびウォッチドッグタイマから構成されています。

本章では、CPU コア、プログラムメモリ、データメモリ、およびリセット回路について説明します。

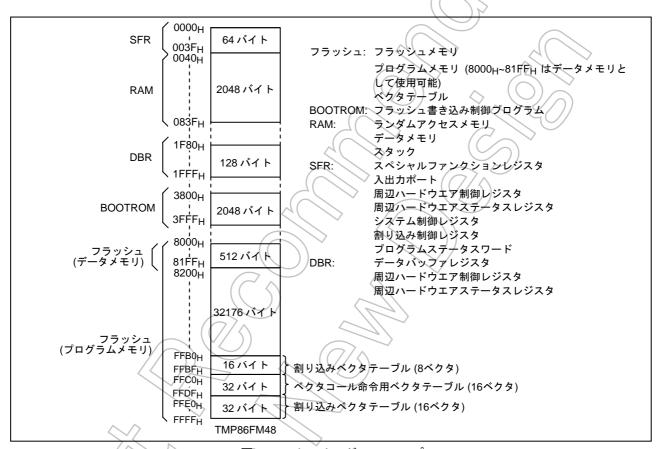

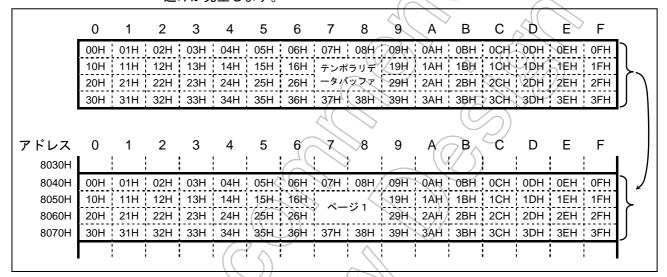

# 1.1 メモリアドレスマップ

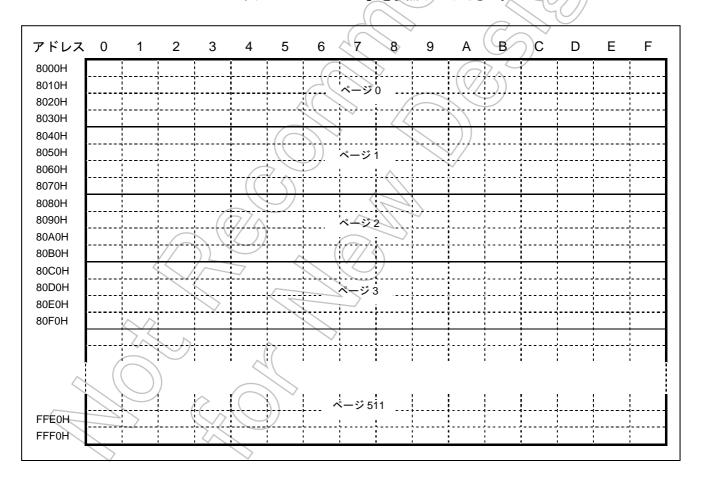

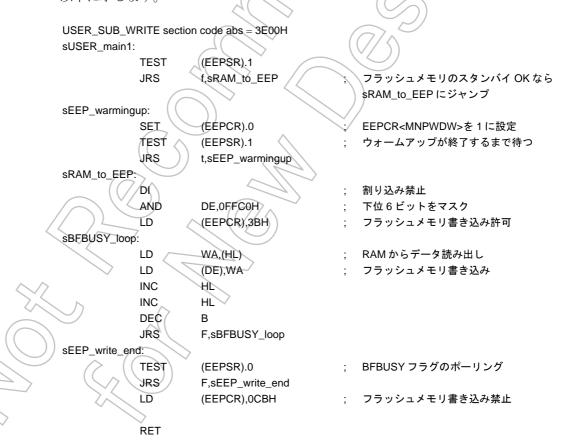

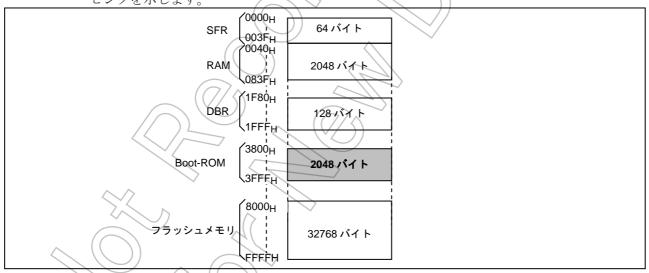

TMP86FM48 のメモリは、フラッシュ、BOOT、RAM、SFR (スペシャルファンクションレジスタ)、DBR (データバッファレジスタ) の 5 つのブロックで構成され、それらは 1 つの 64 K バイトアドレス空間上にマッピングされています。図 1.1.1に TMP86FM48のメモリアドレスマップを示します。

図1.1.1 メモリアドレスマップ

# 1.2 プログラムメモリ (フラッシュ)

TMP86FM48 は 32 K ベイト (アドレス  $8000_{H}$ ~FFFF<sub>H</sub>)のプログラムメモリ (フラッシュ) を内蔵しています。プログラムメモリ中のアドレス  $8000_{H}$ ~81FF<sub>H</sub> は、512 バイトのデータメモリとして使用することができます。

86FM48-7 2007-08-24

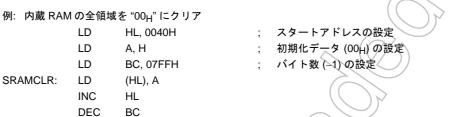

# 1.3 データメモリ (RAM)

JRS

F, SRAMCLR

TMP86FM48 は、2 K バイト (アドレス  $0040\sim083$  FH) の RAM を内蔵しています。内蔵 RAM の 領域中、アドレス  $(0040_{H}\sim00$  FFH) はダイレクト領域となっており、この領域に対しては実行時間 を短縮した命令による処理が可能です

<u>データメモリの内容は、電源投入時不定になりますので、イニシャライズルーチンで初期設定を</u> <u>行ってください。</u>

86FM48-8 2007-08-24

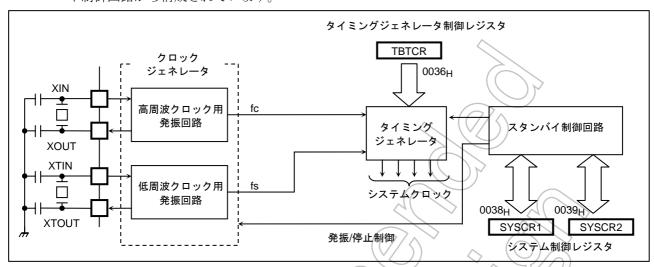

## 1.4 システムクロック制御回路

システムクロック制御回路は、クロックジェネレータ、タイミングジェネレータおよびスタンバイ制御回路から構成されています。

図1.4.1 システムクロック制御回路

#### 1.4.1 クロックジェネレータ

クロックジェネレータは、CPU コアおよび周辺ハードウエアに供給されるシステムクロックの基準となる基本クロックを発生する回路です。高周波クロック用と低周波クロック用の2つの発振回路を内蔵しており、スタンバイ制御回路で低周波クロックによる低速動作に切り替えて消費電力の低減を図ることもできます。

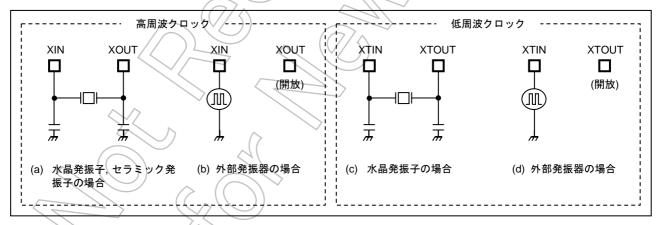

高周波クロック (周波数 fc)、低周波クロック (周波数 fs) は、それぞれ XIN, XOUT 端子, XTIN, XTOUT 端子に発振子を接続することにより容易に得られます。また、外部発振器からのクロックを入力することもできます。この場合、XIN, XTIN 端子からクロックを入力し、XOUT, XTOUT 端子は開放しておきます。

図1.4.2 発振子の接続例

注) 基本クロックを外部にて直接モニタする機能はハードウエア的には用意されていませんが、割り 込み禁止状態,ウォッチドッグタイマのディセーブル状態でプログラムによってポートに一定周 波数のパルス (例えばクロック出力) を出力させ、これをモニタすることにより調節を行うことが できます。発振周波数の調整が必要なシステムでは、あらかじめ調整用プログラムを作成してお く必要があります。

86FM48-9 2007-08-24

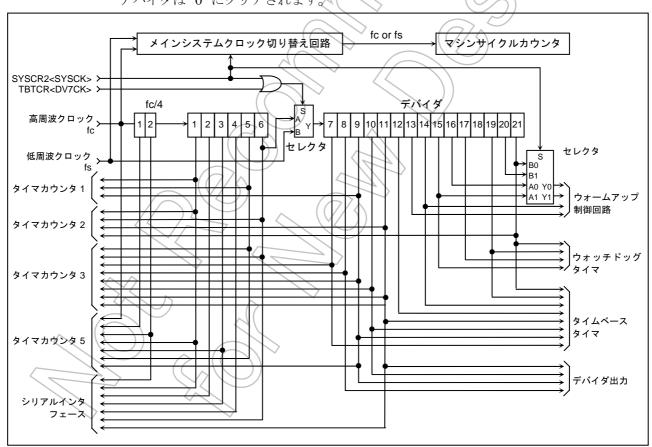

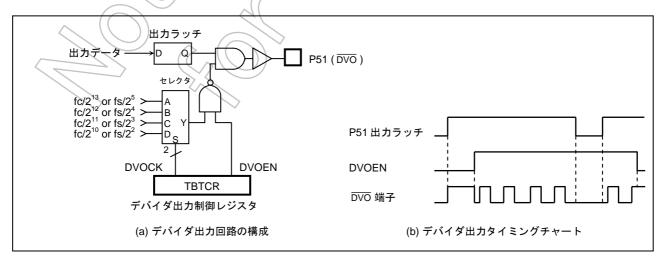

## 1.4.2 タイミングジェネレータ

タイミングジェネレータは、基本クロック (fc または fs) から CPU コアおよび 周辺ハードウエアに供給する各種システムクロックを発生する回路です。タイミングジェネレータの機能は、次のとおりです。

- a. メインシステムクロックの生成

- b. デバイダ出力 (**DVO**) パルス生成

- c. タイムベースタイマのソースクロック生成

- d. ウォッチドッグタイマのソースクロック生成

- e. タイマカウンタなどの内部ソースクロック生成

- f. STOPモード解除時のウォームアップクロック生成

### (1) タイミングジェネレータの構成

タイミングジェネレータは、2段のプリスケーラ、21段のデバイダ、メインシステムクロック切り替え回路およびマシンサイクルカウンタから構成されています。

デバイダの7段目への入力クロックは動作モード、TBTCR<DV7CK>により図1.4.4のようになります。なお、リセット時およびSTOPモード起動/解除時プリスケーラおよびデバイダは"0"にクリアされます。

図1.4.3 タイミングジェネレータの構成

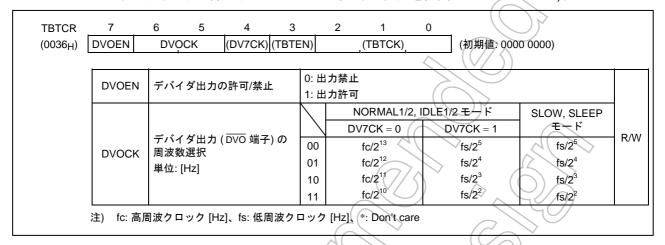

| TBTCR                | 7 6 5 4 3 2 1 0                                                  |     |

|----------------------|------------------------------------------------------------------|-----|

| (0036 <sub>H</sub> ) | (DVOEN) (DVOCK) DV7CK (TBTEN) (TBTCK) (初期值: 0000 0000)           |     |

|                      | デバイダの 7 段目への 0: fc/2 <sup>8</sup> [Hz]                           |     |

|                      | DV7CK 入力クロックの選択 1: fs R                                          | /W  |

|                      | 注 1) シングルクロックモード時は、DV7CK を "1" セットしないでください。                      |     |

|                      | 注 2) 低周波クロックの発振安定前に DV7CK を "1" にセットしないでください。                    |     |

|                      | 注 3) fc: 高周波クロック [Hz]、fc: 低周波クロック [Hz]、*: Don't care             |     |

|                      | 注 4) SLOW1/2, SLEEP1/2 モード時は、DV7CKの設定にかかわらず、デバイダ7段目には fs が入力されます | - 0 |

|                      | 注 5) NORMAL1/2 モードから STOP モードを起動した場合、STOP モード解除後のウォームアップ中は DV7   | CK  |

|                      | の設定にかかわらず、デバイダ7段目にはデバイダ6段目の出力が入力されます。                            |     |

図1.4.4 タイミングジェネレータ制御レジスタ

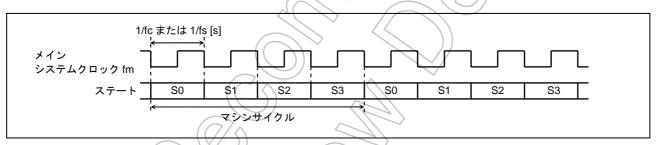

# (2) マシンサイクル

命令の実行および内蔵ハードウエアの動作は、システムクロックに同期して行われます。 命令実行の最小単位を、『マシンサイクル』と呼びます。TLCS-870/C シリーズの命令 には、1 マシンサイクルで実行される 1 サイクル命令から最長 10 マンンサイクルを要す る 10 サイクル命令までの 10 種類があります。

マシンサイクルは、4 ステート(S0~S3)で構成され、各スデートは1メインシステムクロックで構成されます。

図1.4.5 マシンサイクル

### 1.4.3 動作モード制御回路

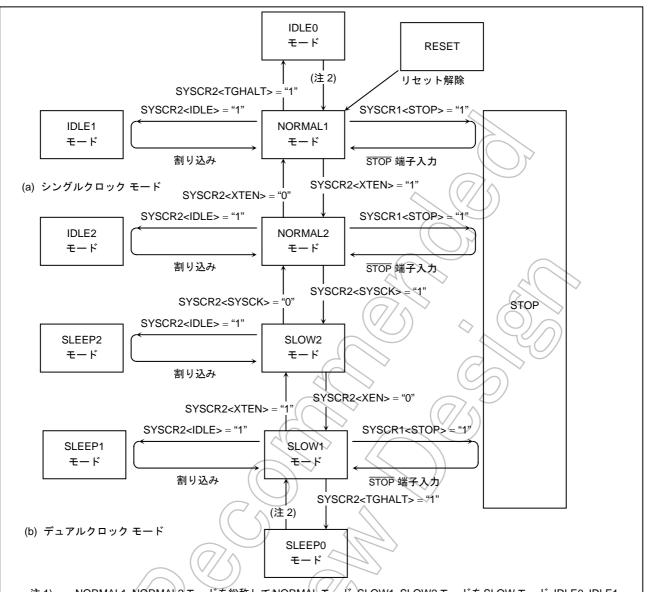

動作モード制御回路は、高周波クロック用,低周波クロック用の各発振回路の発振/停止およびメインシステムクロックの切り替えを行います。動作モードは、シングルクロックモードとデュアルクロックモードに大別され、各動作モードの制御はシステム制御レジスタ (SYSCR1, SYSCR2) で行います。

図 1.4.6に動作モード遷移図を、図 1.4.7に制御レジスタを示します。

#### (1) シングルクロックモード

高周波クロック用発振回路のみ使用し、P21 (XTIN), P22 (XTOUT) は、通常の入出力ポートとなります。メインシステムクロックは、高周波クロックから生成されますので、シングルクロックモードにおけるマシンサイクルタイムは 4ffc [s] となります。

#### a. NORMAL1モード

CPU コアおよび周辺ハードウエアを高周波クロックで動作させるモードです。リセット解除後は、NORMAL1モードになります。

## b. IDLE1モード

CPU およびウォッチドッグタイマを停止し、周辺ハードウェアを高周波クロックで動作させるモードです。IDLE1 モードの起動は、システム制御レジスタ 2 (SYSCR2) の IDLE を "1" にセットすることで行います。周辺ハードウエアからの割り込みまたは外部割り込みにより解除され、NORMAL1 モードに復帰します。IMF (割り込みマスタ許可フラグ)が "1" (割り込み許可状態) のときは、割り込み処理が行われたあと、通常の動作に戻ります。IMF が "0" (割り込み禁止状態) のときは、IDLE1 モードを起動した命令の次の命令から実行再開します。

#### c. IDLE0モード

発振回路とTBTを除き、コアおよび周辺回路を停止させるモードです。NORMAL1 モード時にシステム制御レジスタ SYSCR2 の TGHALT ビットに "1"をセットすることにより起動します。IDLE0 モードを起動すると、CPU が停止しタイミングジェネレータは TBT 以外の周辺回路へのクロック供給を停止します。その後、TBTCR<TBTCK>によって設定されたソースクロックの立ち下がりエッジを検出するとタイミングジェネレータは全周辺回路へのクロック供給を開始します。

IDLEO モードを解除すると、CPU は動作を再開し、NORMAL1 モードに復帰します。

なお、IDLE0 モードは、TBTCR<TBTEN>の設定に関係なく起動/復帰し IMF="1", EF7 (TBT の割り込み個別許可フラグ)="1", TBTCR<TBTEN>="1"のときは割り込み処理が行われます。

TBTCR<TBTEN> = "1" の状態で IDLE0 モードを起動すると、NORMAL モードに復帰後、INTTBT割り込みラッチがセットされます。

## (2) デュアルクロックモード

高周波,低周波用の 2 つの発振回路を使用する動作モードで、P21 (XTIN), P22 (XTOUT) は入出力ポートとして使用することはできません。メインシステムクロックは、NORMAL2, IDLE2 モード時、高周波クロックから生成され、SLOW1, 2, SLEEP1, 2 モード時、低周波クロックから生成されています。従って、マシンサイクルタイムは、NORMAL2, IDLE2 モード時 4/fc [s], SLOW, SLEEPモード時 4/fs [s] (122  $\mu$ s @fs = 32.768 kHz) となります。

TLCS-870/C シリーズは、リセット中シングルクロックモードとなります。デュアルクロックモードで使用する場合は、プログラムの先頭で低周波クロックを発振させてください。

#### a. NORMAL2モード

CPU コアを高周波クロックで動作させるモードで、周辺ハードウエアは高周波/低周波の両クロックで動作します。

#### b. SLOW2モード

高周波クロックの発振を動作させながら、CPU コアを低周波クロックで動作させるモードです。NORMAL2 から SLOW2 への切り替え、SLOW2 から NORMAL2 への切り替えは、システム制御レジスタ 2 (SYSCR) の SYSCK ビットで行います。SLOW2 モード時、XTEN を "0" にクリアしないでください。

#### c. SLOW1モード

高周波クロックの発振を停止させ、CPUコア、周辺ハードウエアを低周波クロックで動作させるモードで消費電力を低減できます。

SLOW1 モードと SLOW2 モードの間の変換はシステム制御レジスタ 2 (SYSCR2) の XEN ビットで行います。SLOW1, SLEEP1 モード時、デバイダの初段から 6 段目までの出力は停止します。

#### d. IDLE2モード

CPU およびウォッチドッグタイマを停止し、周辺ハードウエアを高周波/低周波の両クロックで動作させるモードです。IDLE2 モードの起動/解除方法は、IDLE1 モードと同じです。解除後、NORMAL2 モードに戻ります。

### e. SLEEP1モード

CPU およびウォッチドッグタイマを停止し、周辺ハードウエアを低周波クロックで動作させるモードです。SLEEP1モードの起動/解除方法は、IDLE1モードと同じです。解除後、SLOW1モードに戻ります。なお、高周波クロックは発振しておりません。SLOW1、SLEEP1時、デバイダの初段から6段目までの出力は停止します。

#### f. SLEEP2 モード

SLOW2 モードに対応する IDLE モードです。高周波クロックが動作することを除き、SLEEP1 モードと同一の状態です。

### g. SLEEPO F-F

発振回路と TBT を除き、コアおよび周辺回路を停止させるモードです。SLOW1 モード時にシステム制御レジスタ SYSCR2の TGHALT ビットに "1"をセットすることにより起動します。SLEEP0モードを起動すると、CPU が停止しタイミングジェネレータは TBT 以外へのクロック供給を停止します。その後、TBTCR<TBTCK>によって設定されたソースクロックの立ち下がりエッジを検出すると、タイミングジェネレータは全周辺回路へのクロック供給を開始します。

SLEEP0 モードを解除すると、CPU は動作を再開し、SLOW1 モードに復帰します。

なお、SLEEPO モードは、TBTCR<TBTEN>の設定に関係なく起動/復帰し、IMF = "1"、EF7 (TBT の割り込み許可フラグ) = "1"、TBTCR<TBTEN> = "1" のときは割り込み処理が行われます。

TBTCR<TBTEN> = "1" の状態で SLEEP0 モードを起動すると、SLOW1 モード に復帰後、INTTBT 割り込みラッチがセットされます。

(3) STOP モード

シングルクロックモード、デュアルクロックモードを問わず、発振回路を含めシステム の動作をすべて停止し、停止直前の内部状態を低消費電力で保持するモードです。

STOP モードの起動は、システム制御レジスタ1で行います。解除は、 $\overline{STOP}$ 端子入力(レベル/エッジの選択可能)で行い、ウォームアップ時間経過後、 $\overline{STOP}$ モード起動時のモードに戻り、 $\overline{STOP}$ モードを起動した命令の次の命令から実行再開します。

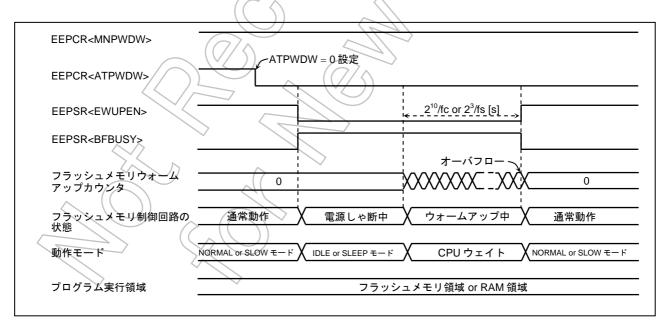

注 1) EEPCR<ATPWDW>が "0" のときに IDLE0/1/2, SLEEP0/1/2 モードを起動すると、これらのモードを解除した後にフラッシュ制御回路の電源が安定するまでの期間、CPU ウェイトが行われます。

注 2) EEPCR<MNPWDW>が "1" のときに STOP モードを起動すると、STOP モードの 解除後、STOP のウォームアップに続きフラッシュ制御回路の電源が安定するまでの期間 CPU ウェイトが行われます。

- 注 1) NORMAL1, NORMAL2モードを総称してNORMALモード、SLOW1, SLOW2モードをSLOWモード, IDLE0, IDLE1, IDLE2モードをIDLEモード、SLEEP0, SLEEP1, SLEEP2モードをSLEEPモードと呼びます。

- 注 2) TBTCR<TBTCK>によって選択されたソースクロックの立ち下がりエッジによって解除。

|      | 動作モード            | 発振<br>高周波 | 回路<br>低周波 | CPUコア | TBT  | その他<br>周辺回路 | マシンサイクル<br>タイム |  |

|------|------------------|-----------|-----------|-------|------|-------------|----------------|--|

| シ    | RESET            |           |           | リセット  | リセット | リセット        |                |  |

| ングルク | NORMAL1<br>IDLE1 | 発振        | 停止        | 動作    | 動作   | 動作          | 4/fc [s]       |  |

|      | IDLE0            |           |           | 停止    |      | 停止          |                |  |

| Ź    | STOP             | 停止        |           |       | 停止   | 15年         | =              |  |

|      | NORMAL2          |           |           | 高周波動作 |      |             | 4/fc [s]       |  |

| デ    | IDLE2            | 発振        |           | 停止    |      |             | 4/10 [5]       |  |

| ュ    | SLOW2            | 光派        |           | 低周波動作 |      | 動作          |                |  |

| アル   | SLEEP2           |           | 発振        | 停止    | 動作   | 到TF         | 4/fs [s]       |  |

| クロ   | SLOW1            |           |           | 低周波動作 |      |             | 4/15 [5]       |  |

| ッ    | SLEEP1           | 停止        |           |       |      |             |                |  |

| ク    | SLEEP0           | 沙兀        |           | 停止    |      | 停止          |                |  |

|      | STOP             |           | 停止        |       | 停止   | 1字址         | =              |  |

図1.4.6 動作モード状態遷移図

システム制御レジスタ1

SYSCR1 (0038<sub>H</sub>)

| . 7  | 6    | 5    | 4     | 3  | 2  | 1 | 0 |                  |

|------|------|------|-------|----|----|---|---|------------------|

| STOP | RELM | RETM | OUTEN | WĻ | JT | T |   | (初期値: 0000 00**) |

| STOP   | STOP モードの起動    | 0: CPU コア, 周辺ハードウエア 動作                                                                             |  |  |  |

|--------|----------------|----------------------------------------------------------------------------------------------------|--|--|--|

| 3101   |                | 1: CPU コア, 周辺ハードウエア 停止 (STOP モード起動)                                                                |  |  |  |

| RELM   | STOP 端子の解除方法の  | O: STOP 端子入力の立ち上がりエッジで解除                                                                           |  |  |  |

| KELIVI | 選択             | 1: STOP 端子入力の "H" レベルで解除                                                                           |  |  |  |

| RETM   | STOP モード解除後の動作 | 0: NORMAL1/2 モードへ戻る                                                                                |  |  |  |

| KETW   | モードの選択         | 1: SLOW1 モードへ戻る                                                                                    |  |  |  |

| OUTEN  | STOP モード時の     | 0: ハイインピーダンス                                                                                       |  |  |  |

| OUTEN  | ポート出力状態の選択     | 1: 出力保持                                                                                            |  |  |  |

|        |                | NORMAL1/2 ŧ-F SLOW1 ŧ-F                                                                            |  |  |  |

|        | STOP モード解除時の   | へ戻る場合 へ戻る場合                                                                                        |  |  |  |

| WUT    | ウォームアップ時間      | 00 $3 \times 2^{16}$ /fc + $(2^{10}$ /fc) $3 \times 2^{13}$ /fs + $(2^{3}$ /fs)                    |  |  |  |

| WUI    | 単位: [s]        | 01 $2^{16}/\text{fc} + (2^{10}/\text{fc})$ $2^{13}/\text{fs} + (2^{3}/\text{fs})$                  |  |  |  |

|        | (注 8)          | 10 $3 \times 2^{14}/\text{fc} + (2^{10}/\text{fc})$ $3 \times 2^{6}/\text{fs} + (2^{3}/\text{fs})$ |  |  |  |

|        |                | 11 $2^{14}/\text{fc} + (2^{10}/\text{fc})$ $2^{6}/\text{fs} + (2^{3}/\text{fs})$                   |  |  |  |

- 注 1) NORMAL モードから STOP モードを起動する場合、RETM は "0" に設定してください。 SLOW モードから STOP モードを起動する場合、RETM は "1" に設定してください。

- 注 2) STOP モードを RESET 端子入力で解除した場合は、RETM の値にかかわらず NORMAL1 モードに戻ります。

- 注 3) fc: 高周波クロック [Hz]、fs: 低周波クロック [Hz]、\*: Don't care

- 注 4) SYSCR1 のビット 1,0 は、リードすると不定値が読み出されます。

- 注 5) OUTEN = "0" のときに STOP モードを起動すると、ポートの内部入力は "0" に固定されますので、外部割り 込み端子の状態によっては立ち下がりエッジの割り込みがセットされる恐れがあります。

- 注 6) キーオンウェイクアップ入力を使用する場合は、RELM を "1" に設定してください。

- 注 7) P20端子は STOP 端子と兼用のため、STOP モードを起動すると OUTENの状態にかかわらず、出力は High-Z 状態となります。

- 注 8) EEPCR<MNPWDW>が"1"のときにSTOPモードを起動すると、STOPモードの解除後、STOPのウォームアップに続きフラッシュ制御回路の電源が安定するまでの期間 CPU ウェイトが行われます。

(CPU ウェイト時間を括弧内に示します)

#### システム制御レジスタ2

SYSCR2 (0039<sub>H</sub>) 7 6 5 4 3 2 1 0 XEN XTEN SYSCK IDLE TGHALT (初期值: 1000 \*0\*\*)

| XEN    | 高周波発振器の制御                              | 0: 発振停止<br>1: 発振継続 または 発振開始                                                        |     |

|--------|----------------------------------------|------------------------------------------------------------------------------------|-----|

| XTEN   | 低周波発振器の制御                              | 0: 発振停止<br>1: 発振継続 または 発振開始                                                        |     |

| SYSCK  | システムクロックの<br>選択 (Write)/モニタ (Read)     | 0: 高周波クロック (NORMAL1/NORMAL2/IDLE1/IDLE2)<br>1: 低周波クロック (SLOW/ SLEEP)               | R/W |

| IDLE   | CPU, WDT 制御<br>(IDLE1/2, SLEEP1/2 モード) | 0: CPU, WDT 動作<br>1: CPU, WDT 停止 (IDLE1/2, SLEEP1/2 モード起動)                         |     |

| TGHALT | TG 制御<br>(IDLE0, SLEEP0 モード)           | 0: TG から全周辺回路へのクロック供給動作<br>1: TG から TBT を除く周辺回路へのクロック供給停止<br>(IDLE0, SLEEP0 モード起動) |     |

- 注 1) XEN, XTEN をともに"0" にクリアした場合、SYSCK = "0" で XEN を "0" にクリアした場合、および SYSCK = "1" で XTEN を "0" にクリアした場合、リセットがかかります。

- 注 2) WDT: ウォッチドッグタイマ, TG: タイミングジェネレータ、\*: Don't care

- 注 3) SYSCR2 のビット 3, 1, 0 は、リードすると不定値が読み出されます。

- 注 4) IDLE と TGHALT は、同時に "1" に設定しないでください。

- 注 5) IDLE0/SLEEP0 モードは、TBTCR<TBTCK>によって選択された非同期の内部ソースクロックによって NORMAL1/SLOW1 モードに復帰しますので、モード起動から復帰までの時間は、TBTCR<TBTCK>の時間 よりも短くなります

- 注 6) IDLE1/2, SLEEP1/2 モード解除時、IDLE は自動的に "0" にクリアされます。

- 注 7) IDLE0, SLEEP0 モード解除時、TGHALT は自動的に "0" にクリアされます。

- 注 8) TGHALT を "1" に設定するときは、事前に周辺機能の動作を停止してから行ってください。周辺機能の動作が停止されない場合、IDLE0 または SLEEPO モードから復帰した直後に周辺機能の割り込みラッチがセットされることがあります。

図1.4.7 システム制御レジスタ 1,2

### 1.4.4 動作モードの制御

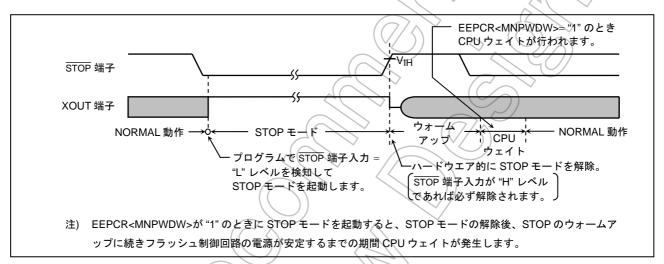

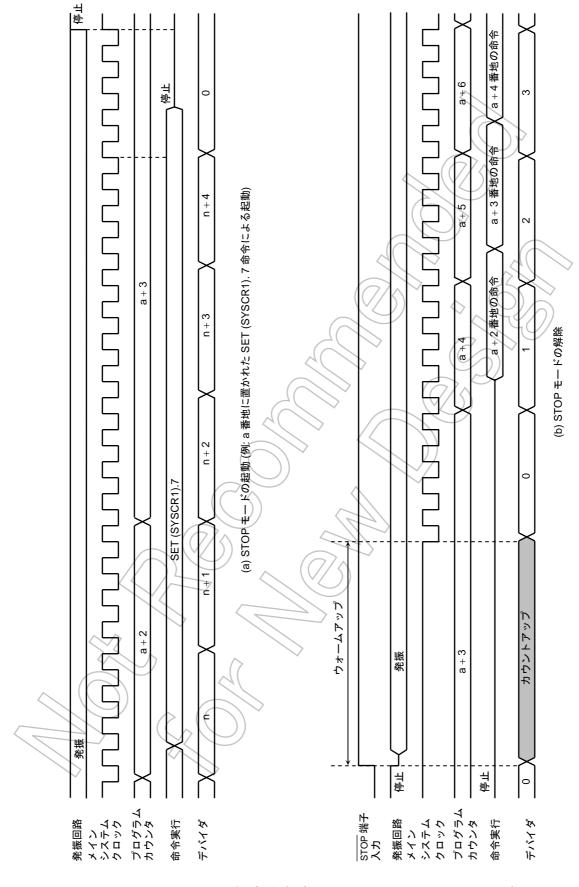

(1) STOP モード

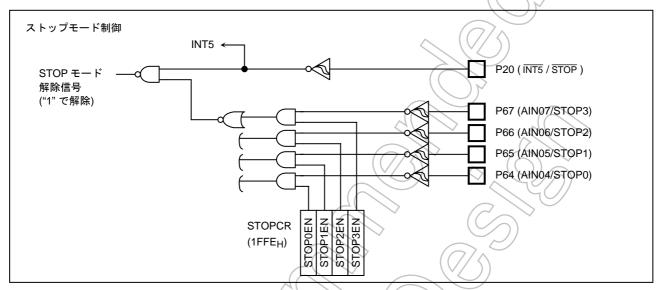

STOP モードは、システム制御レジスタ 1 (SYSCR1) と  $\overline{STOP}$  端子入力およびキーオンウェイクアップ入力端子 (STOP0~STOP3) によって制御されます。  $\overline{STOP}$  端子は、P20ポートならびに  $\overline{INT5}$  (外部割り込み入力 5) 端子と兼用です。 STOP モードは、SYSCR1<STOP> を"1"にセットすることにより起動され、STOP モード中、次の状態を保持しています。

- a. 高周波, 低周波とも発振を停止し、内部の動作をすべて停止します。

- b. データメモリ,レジスタ,プログラムステータスワード,ポートの出力ラッチなどは STOP モードに入る直前の状態を保持します。

- c. タイミングジェネレータのプリスケーラおよびデバイダを "0" にクリアします。

- d. プログラムカウンタは、STOP モードを起動する命令 (SET (SYSCR1). 7 など) の 2 つ先の命令のアドレスを保持します。

STOP モードの解除には、レベル解除モードとエッジ解除モードがあり、システム制御レジスタ 1 の SYSCR1<RELM>で選択します。エッジ解除モードの場合には、STOP0~STOP3 を使用禁止に設定してください。

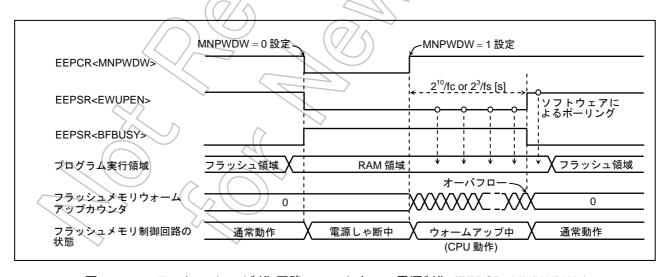

EEPCR<MNPWDW>が"1"のときにSTOPモードを起動すると、STOPモードの解除後、STOPのウォームアップに続きフラッシュ制御回路の電源が安定するまでの期間CPUウェイトが発生します。

- 注 1) STOP モードは、STOP 端子とキーオンウェイクアップ入力端子(STOP0~STOP3) のいずれかの端子によって解除することが可能ですが、STOP 端子はキーオンウェイクアップ入力端子とは異なり入力を禁止する機能がありませんので、必ずSTOPモード解除用の端子として使用してください。

- 注 2) STOP 期間中 (STOP モード起動からウォームアップ終了までの期間)、外部割り込み端子の信号の変化により割り込みラッチが "1" にセットされ、STOP モード解除後、直ちに割り込みを受け付ける場合があります。従って、STOP モードの起動は、割り込みを禁止してから行ってください。また STOP モード解除後に割り込みを許可する場合、あらかじめ不要な割り込みラッチをクリアしてください。

## a. レベル解除モード (RELM = "1" のとき)

STOP 端子への"H"レベル入力またはSTOP0~STOP3 (STOPCR でビットごとに設定可能)端子への"L"レベル入力によりSTOPモードを解除するモードで、メイン電源しゃ断時のコンデンサバックアップや長時間のバッテリーバックアップなどに使用します。

$\overline{STOP}$ 端子入力が"H"レベルまたは STOP0~STOP3端子が"L"レベルの状態で STOPモードを起動する命令を実行した場合、STOPモードは起動されず、直ちに解除シーケンス(ウォームアップ)が行われます。従って、レベル解除モードで STOPモードを起動する場合、 $\overline{STOP}$ 端子入力が"L"レベルであり、また STOP0~STOP3端子入力が"H"レベルになっていることをプログラム上で認識する必要があります。この認識を行うには、次の方法があります。

- 1. ポートの状態をテストする方法

- 2. **INT5** 割り込みによる方法 (<del>INT5</del> 端子入力の立ち下がりエッジで割り込みを 発生します)

例 1: P20 ポートをテストして NORMAL モードから STOP モードを起動

LD (SYSCR1), 01010000B ; レベル解除モードにセット

アップ

SSTOPH: TEST (P2PRD). 0 ; STOP 端子入力が "L" レベルになるまで

ウェイト

JRS F, SSTOPH ; システムクロック f<sub>SYS</sub> を fc/2 へ切り替え

SET (SYSCR1).7 ; STOPモードを起動

例 2: INT5 割り込みにより、NORMAL モードから STOP モードを起動

PINT5: TEST (P2PRD). 0 ; ノイズ除去のため P20 ポート入力が "H"

レベルなら STOP モードを起動しない。

JRS F. SINT5

LD (SYSCR1), 01010000B ; レベル解除モードにセット

アップ

SET (SYSCR1). 7 ; STOPモードを起動

SINT5: RETI

### 図1.4.8 レベル解除モード

86FM48-18

- 注 1) ウォームアップ開始後、再び STOP 端子入力が "L" レベルまたは、 STOP0~STOP3 端子が "H" レベルになっても STOP モードには戻りません。

- 注 2) エッジ解除モードにセットアップ後にレベル解除モードに戻した場合は、 STOP 端子入力の立ち上がりエッジが検出されるまではモードは切り替わり ません。

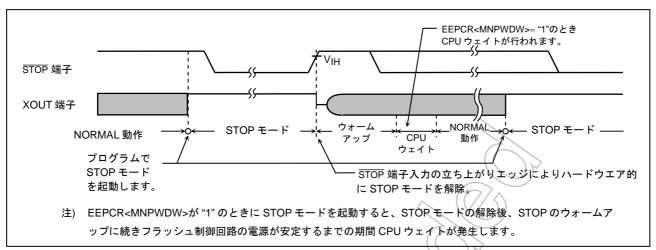

- b. エッジ解除モード (RELM = "0" のとき)

$\overline{STOP}$  端子入力の立ち上がりエッジで STOP モードを解除するモードです。比較的 短時間のプログラム処理を一定周期で繰り返す応用などに使用し、この一定周期の信号、例えば、低消費電力の発振源からのクロックを  $\overline{STOP}$  端子に入力します。エッジ 解除モードの場合、 $\overline{STOP}$  端子入力が "H" レベルの状態でも STOP モードが起動されます。なお、STOP0~STOP3 端子入力は、キーオンウェイクアップ制御レジスタ (STOPCR) によってすべて禁止に設定してください。

例: NORMAL モードから STOP モードを起動

LD (SYSCR1), 10010000B ; エッジ解除で STOP モードを起動

図1.4.9 エッジ解除モード

STOPモードの解除は、次のシーケンスで行われます。

- 1. 発振が開始されます。デュアルクロックモードの場合、NORMAL2 へ戻るときは、高周波/低周波発振器の両方が発振し、SLOW1 に戻るときは低周波発振器のみ発振します。シングルクロックモードの場合は、高周波発振器のみ発振します。

- 2. 発振が安定するのに必要な時間の確保のため、ウォームアップを行います。 ウォームアップ中、内部動作は停止したままです。ウォームアップ時間は、 発振器の特性に合わせて SYSCR1<WUT> で4種類選択できます。

- 3. EEPCR<MNPWDW>が"1"の場合、フラッシュ制御回路の電源が安定するまでの期間 CPU ウェイトが行われます。CPU ウェイトが開始すると、CPU は動作停止状態となりますが、周辺機能およびタイミングジェネレータは動作を再開します。CPU ウェイトが終了した後、STOP モードを起動する命令の次の命令から通常の動作が再開されます。

- 4. EEPCR<MNPWDW>が"0"の場合、ウォームアップが終了した後、STOPモードを起動する命令の次の命令から通常の動作が再開されます。

- 注 1) STOP モードを解除すると、タイミングジェネレータのプリスケーラおよびデバイダは"0" にクリアされた状態から始まります。

- 注 2) STOP モードは、RESET端子を "L" レベルにすることによっても解除され、 直ちに通常のリセット動作を行います。

- 注3) 低い保持電圧で STOP モードの解除を行う場合には、次の注意が必要です。 STOP モードの解除に先立ち、電源電圧を動作電圧に上げる必要があります。その際、RESET 端子も "H" レベルにあり、電源電圧とともに上昇します。この場合、外部に時定数回路などが付加されているときには、RESET 端子入力の電圧上昇は電源電圧の上昇よりも立ち上がりが遅くなります。 このとき、RESET 端子の入力電圧レベルが、RESET 端子入力(ヒステリシス入力)の非反転高レベル入力電圧を切るとリセット動作を行う恐れがあります。

86FM48-19 2007-08-24

表1.4.1 ウォームアップ時間 (例: fc = 16.0 MHz, fs = 32.768 kHz 時)

| WUT  | ウォームアップ時間 [ms] (注 2) |                |  |  |  |  |

|------|----------------------|----------------|--|--|--|--|

| VVOI | NORMAL モードへ戻る場合      | SLOW モードに戻る場合  |  |  |  |  |

| 00   | 12.288 + (0.064)     | 750 + (0.244)  |  |  |  |  |

| 01   | 4.096 + (0.064)      | 250 + (0.244)  |  |  |  |  |

| 10   | 3.072 + (0.064)      | 5.85 + (0.244) |  |  |  |  |

| 11   | 1.024 + (0.064)      | 1.95 + (0.244) |  |  |  |  |

注 1) ウォームアップ時間は、基本クロックをデバイダにて分周して得ていますので、 STOPモードの解除時に発振周波数にゆらぎがある場合は、ウォームアップ時間 は誤差を含むことになります。従って、ウォームアップ時間は、概略値としてと らえる必要があります。

86FM48-20 2007-08-24

図1.4.10 STOP モードの起動/解除 (EEPCR<MNPWDW> = "0" のとき)

86FM48-21 2007-08-24

図1.4.11 STOP モードの起動/解除 (EEPCR<MNPWDW> = "1" のとき)

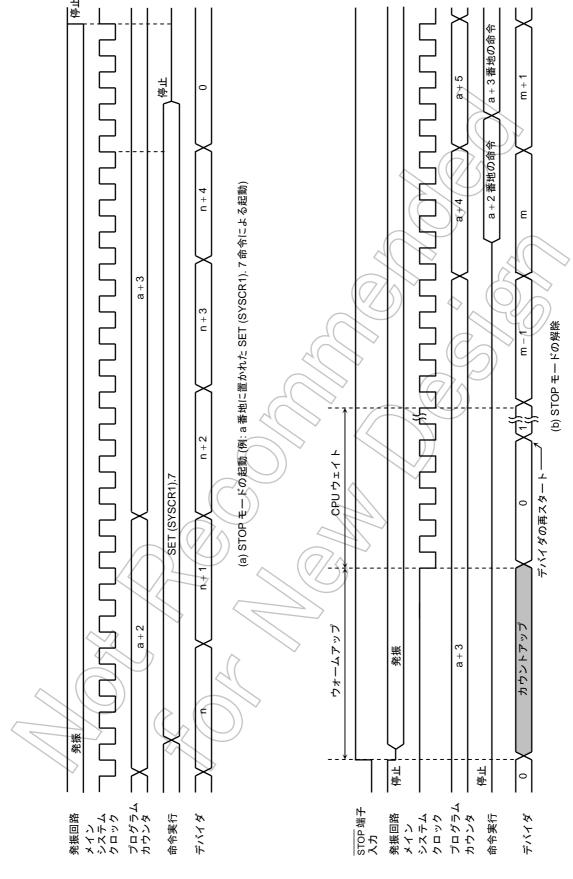

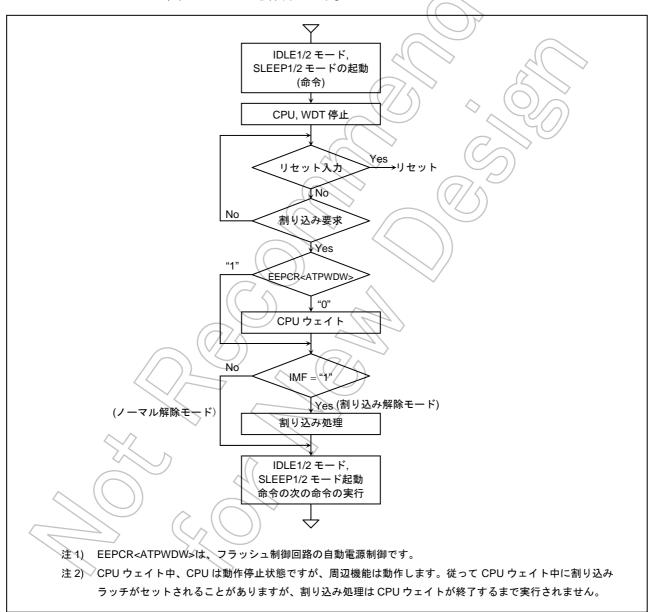

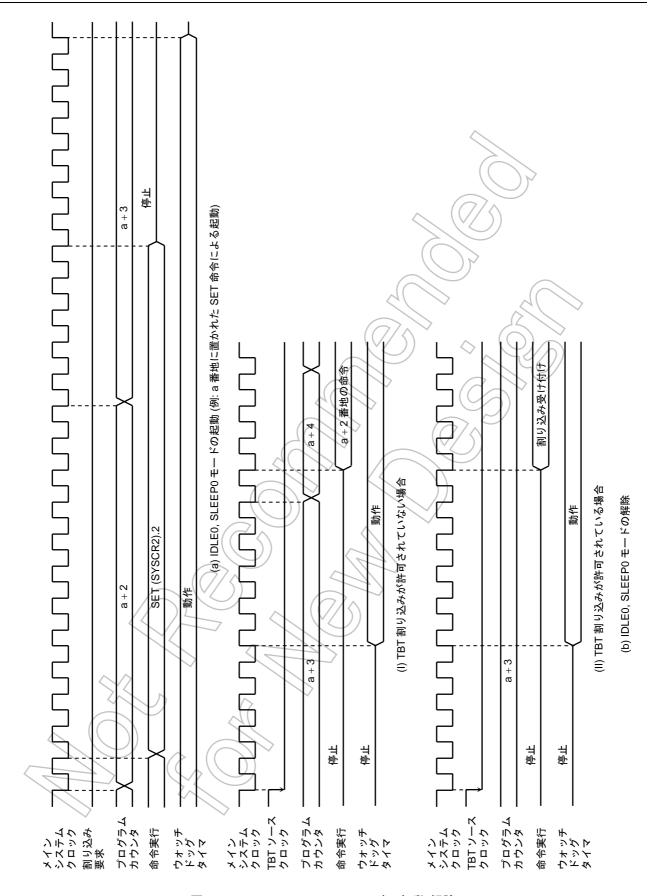

## (2) IDLE1/2 モード, SLEEP1/2 モード

IDLE1/2 モード、SLEEP1/2 モードは、システム制御レジスタ 2 (SYSCR2) とマスカブル割り込みによって制御されます。IDLE1/2 モード、SLEEP1/2 モード中、次の状態を保持しています。

- a. CPU およびウォッチドッグタイマは動作を停止します。周辺ハードウエアは動作を 継続します。

- b. データメモリ、レジスタ、プログラムステータスワード、ポートの出力ラッチなどは IDLE1/2 モード、SLEEP1/2 モードに入る直前の状態を保持します。

- c. プログラムカウンタは、IDLE1/2 モード、SLEEP1/2 モードを起動する命令の 2 つ先 の命令のアドレスを保持します。

図1.4.12 IDLE1/2 モード, SLEEP1/2 モード

86FM48-23 2007-08-24

• IDLE1/2, SLEEP1/2 モードの起動

IDLE1/2, SLEEP1/2 モードを起動するには、SYSCR2<IDLE>を"1"に設定します。

• IDLE1/2, SLEEP1/2 モードの解除

IDLE1/2, SLEEP1/2 モードには、ノーマル解除モードと割り込み解除モードがあり、それぞれの選択は割り込みマスタ許可フラグ (IMF) によって行います。IDLE1/2, SLEEP1/2 モードが解除されると、SYSCR2<IDLE>は自動的に"0"にクリアされ、起動したモードに復帰します。

EEPCR<ATPWDW>が "0" のときに IDLE1/2, SLEEP1/2 モードを起動すると、起動したモードに復帰する前にフラッシュ制御回路の電源が安定するまでの期間 CPU ウェイトが行われます。 CPU ウェイト時間は、IDLE1/2 モード時  $2^{10}$ /fc [s]、SLEEP1/2 モード時  $2^{3}$ /fs [s]となります。

なお、IDLE1/2, SLEEP1/2 モードは $\overline{RESET}$  端子を "L" レベルにすることによっても解除されます。この場合、リセット解除後は NORMAL1 モードが起動します。

- 注) CPU ウェイト中、CPU は動作停止状態ですが、周辺機能は動作します。従って CPU ウェイト中に割り込みラッチがセットされることがありますが、割り込み処理は CPU ウェイトが終了するまで実行されません。

- (I) ノーマル解除モード (IMF = "0" のとき)

割り込み個別許可プラグ (EF) で許可された割り込み要因により、IDLE1/2, SLEEP1/2 モードが解除され、IDLE1/2, SLEEP1/2 モードを起動した命令の次の命令から実行を再開します。通常、解除に使用した割り込み要因の割り込みラッチ (IL) はロード命令で "0" にクリアする必要があります

(II) 割り込み解除モード (IMF = "1" のとき)

割り込み個別許可フラグ (EF) で許可された割り込み要因により IDLE1/2, SLEEP1/2 モードが解除され、割り込み処理に入ります。割り込み処理後、IDLE1/2, SLEEP1/2 モードを起動した命令の次の命令に戻ります。

注) IDLE1/2, SLEEP1/2 モード起動直前にウォッチドッグタイマ割り込みが発生した 場合、IDLE1/2, SLEEP1/2 モードは起動されずウォッチドッグタイマ割り込み処 理が行われます。

図1.4.13 IDLE1/2, SLEEP1/2 モードの起動/解除

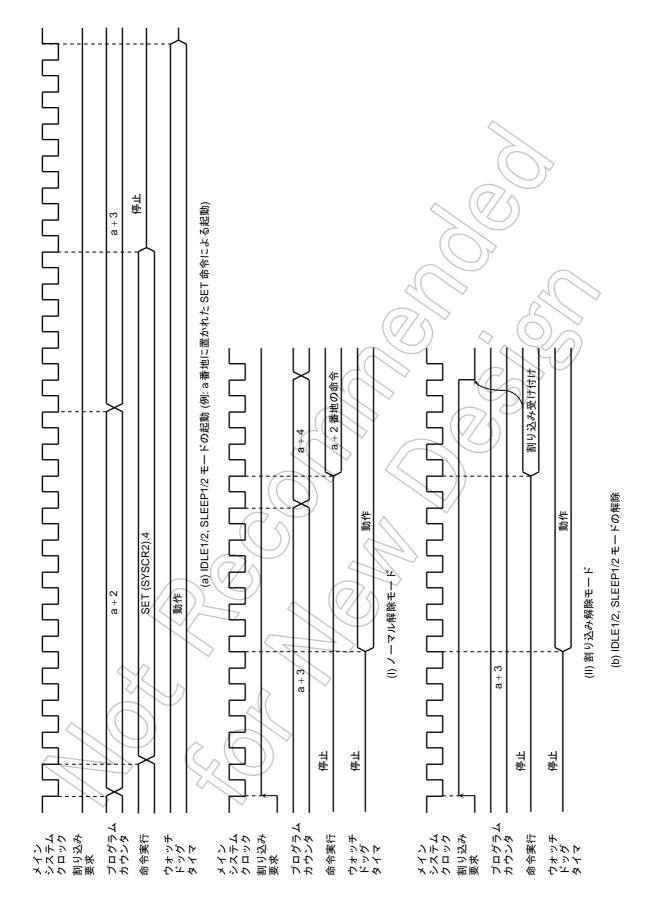

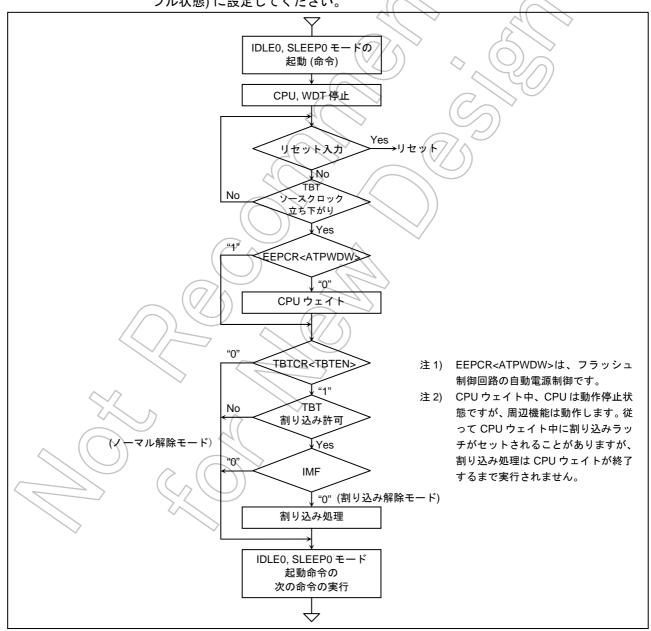

#### (3) IDLEO, SLEEPO ₹- F

IDLE0, SLEEP0 モードは、システム制御レジスタ 2 (SYSCR2) とタイムベースタイマ制御レジスタ (TBTCR) によって制御されます。IDLE0, SLEEP0 モード中、次の状態を保持しています。

- a. タイミングジェネレータは、タイムベースタイマを除く周辺回路へのクロック供給を 停止します。

- b. データメモリ、レジスタ、プログラムステータスワード、ポートの出力ラッチなどは IDLE0、SLEEPO モードに入る直前の状態を保持します。

- c. プログラムカウンタは、IDLEO, SLEEPO モードを起動する命令の 2 つ先の命令のアドレスを保持します。

注) IDLE0, SLEEP0 モードを起動する場合は、事前に周辺機能を停止状態 (ディセーブル状態) に設定してください。

図1.4.14 IDLE0, SLEEP0 モード

86FM48-26 2007-08-24

• IDLE0, SLEEP0 モードの起動 IDLE0, SLEEP0 モードを起動するには、SYSCR2<TGHALT>を"1"に設定します。

• IDLE0, SLEEP0 モードの解除

IDLEO、SLEEPO モードには、ノーマル解除モードと割り込み解除モードがあり、それぞれの選択は割り込みマスタ許可フラグ (IMF)、タイムベースタイマ割り込み個別許可フラグ (EF7)、TBTCR<TBTEN>によって行います。IDLEO、SLEEPO モードが解除されると、SYSCR2<TGHALT>は自動的に"0"にクリアされ、起動したモードに復帰します。またこのとき TBTCR<TBTEN>が"1"にセットされているとINTTBT の割り込みラッチがセットされます。

EEPCR<ATPWDW>が "0" のときに IDLE0, SLEEP0 モードを起動すると、これらのモードを解除した後にフラッシュ制御回路の電源が安定するまでの期間、CPU ウェイトが行われます。CPU ウェイト時間は、IDLE1/2 モード時  $2^{10}$ /fc [s]、SLEEP1/2 モード時  $2^{3}$ /fs [s]となります。

なお、IDLE0、SLEEP0 モードは $\overline{\text{RESET}}$ 端子を "L" レベルにすることによっても解除されます。この場合、リセット解除後は $\overline{\text{NORMAL1}}$ モードが起動します。

- 注 1) IDLE0, SLEEP0 モードは、TBTCR<TBTEN>の設定に関係なく起動/復帰します。

- 注 2) CPU ウェイト中、CPU は動作停止状態ですが、周辺機能は動作します。従って CPU ウェイト中に割り込みラッチがセットされることがありますが、割り込み処理は CPU ウェイトが終了するまで実行されません。

- (I) ノーマル解除モード (IMF・EF7・TBTCR<TBTEN> = "0" のとき)

TBTCR<TBTCK>によって設定されたソースクロックの立ち下がりエッジを検出すると、IDLE0、SLEEP0モードは解除されます。IDLE0、SLEEP0モードが解除されると、それらのモードを起動した命令の次の命令から処理を再開します。

(II) 割り込み解除モード (IMF・EF7・TBTCR<TBTEN>="1" のとき)

**TBTCR<TBTCK>**によって設定されたソースクロックの立ち下がりエッジを検出すると、**IDLE**0, **SLEEP**0 モードが解除された後、**INTTBT** の割り込み処理が行われます。

- 注1) IDLE0, SLEEP0 モードは、TBTCR<TBTCK>によって選択された非同期の内部ソースクロックによって NORMAL1, SLOW1 に復帰しますので、モード起動から復帰までの時間は TBTCR<TBTCK>の時間よりも短くなります。

- 注2) IDLEO, SLEEPO モード起動直前にウォッチドッグタイマ割り込みが発生した場合、IDLEO, SLEEPO モードは起動されずウォッチドッグタイマ割り込み処理が行われます。

図1.4.15 IDLE0, SLEEP0 モードの起動/解除

86FM48-28 2007-08-24

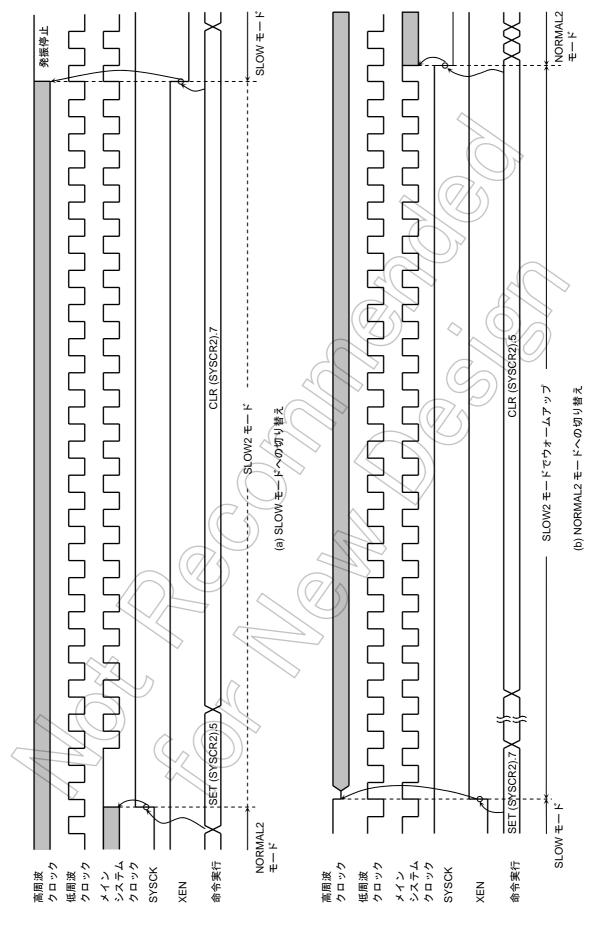

(4) SLOW モード

SLOW モードは、システム制御レジスタ 2 (SYSCR2) よって制御されます。 ここでは、ウォームアップにタイマカウンタ 2 (TC2) を用いた場合を示しています。

a. NORMAL2 モードから SLOW モードへの切り替え

まず、SYSCR2<SYSCK>に"1"を書き込み、システムタロックを低周波クロックに切り替えます。

次に、SYSCR2<XEN>を"0"にクリアして高周波発振器を停止します。

注) NORMAL2 モードへ早く戻るために高周波クロックの発振を継続させることも可能です。

ただし、SLOW モードから STOP モードを起動する場合は、必ず高周波クロックを停止してください。

なお、低周波クロックが安定に発振していない場合は、安定発振するまで待ってから上記操作を行ってください。低周波クロックの安定発振を確認するのに、タイマカウンタ2を使用すると便利です。

例 1: NORMAL2 モードから SLOW1 モードへの切り替え。

DΩ

SET (SYSCR2). 5 ; SYSCR2<SYSCK> $\leftarrow$ 1

(システムクロックを低周波 (SLOW2 モ

ードに) に切り替え) SYSCR2<XEN> ← 0

CLR (\$Y\$CR2). 7 ; \$Y\$CR2<XEN> ← 0 (高周波クロック停止)

例 2: TC2 で低周波クロックの安定発振の確認後、SLOW1 モードへ切り替え。

SET \ (\$YSCR2). 6 \ \ \ SYSCR2<XTEN> ← 1

(低周波クロック発振開始) LD (TC2CR), 14H ; TC2のモードをセット

LDW (TC2DRL), 8000H ウォームアップ時間をセット (発振子の特性で時間を決定します。)

; IMF ← 0

SET (EIRE).4 ; INTTC2割り込み許可

EI ; IMF ← 1 SET (TC2CR).5 ; TC2スタート

PINTTC2: CLR (TC2CR).5 ; TC2ストップ

SET (SYSCR2). 5 ; SYSCR2<SYSCK> $\leftarrow$  1

(システムクロックを低周波に切り替え)

CLR (SYSCR2). 7 ; SYSCR2<XEN> ← 0 (高周波クロック停止)

RET

VINTTC2:, DW PINTTC2 ; INTTC2 ベクタテーブル

86FM48-29 2007-08-24

#### b. SLOW1 モードから NORMAL2 モードへの切り替え

まず、XEN (SYSCR2 のビット 7) を "1" にセットして高周波クロックを発振させ ます。発振の安定時間(ウォームアップ)をタイマカウンタ2によって確保したあと、 SYSCK (SYSCR2 OEV > 5) E''0" EOUP EV

注 1) SYSCK を "0" にクリアした後、低周波クロックと高周波クロックの同期をと っている期間は低周波クロックで命令の実行を継続しています。

高周波クロック wwwwwww 低周波クロック メインシステムクロック

注 2) SLOW モードは、RESET 端子を "L" レベルにすることによっても解除され、 直ちに通常のリセット動作を行います。TMP86FM48 は、リセット解除後 NORMAL1 モードになります。

例: SLOW1 モードから NORMAL2 モードへの切り替え

DI

ΕI

(fc = 16 MHz, ウォームアップ時間 = 4.0 ms)。

(SYSCR2). 7 SYSCR2<XEN> + SET (高周波クロック発振開始)

TC2のモードをセット LD (TC2CR), 10H

ウォームアップ時間をセット (TC2DRH), 0F8H LD

(周波数と発振子の特性で時間を決定しま す。)

IMF ← 0

INTTC2 割り込み許可 (EIRE), 4 SET

/MF ← 1 SET (TC2CR). 5 TC2 スタート

CLR PINTTC2: (TC2CR). 5 TC2 ストップ

> CLR (SYSCR2). 5  ${\sf SYSCR2}{<}{\sf SYSCK}{>} \leftarrow 0$

(システムクロックを高周波に切り替え) RĖTI

VINTTC2: DW PINTTC2 INTTC2 ベクタテーブル

> 2007-08-24 86FM48-30

図1.4.16 SLOW→NORMAL2モード切り替え

86FM48-31 2007-08-24

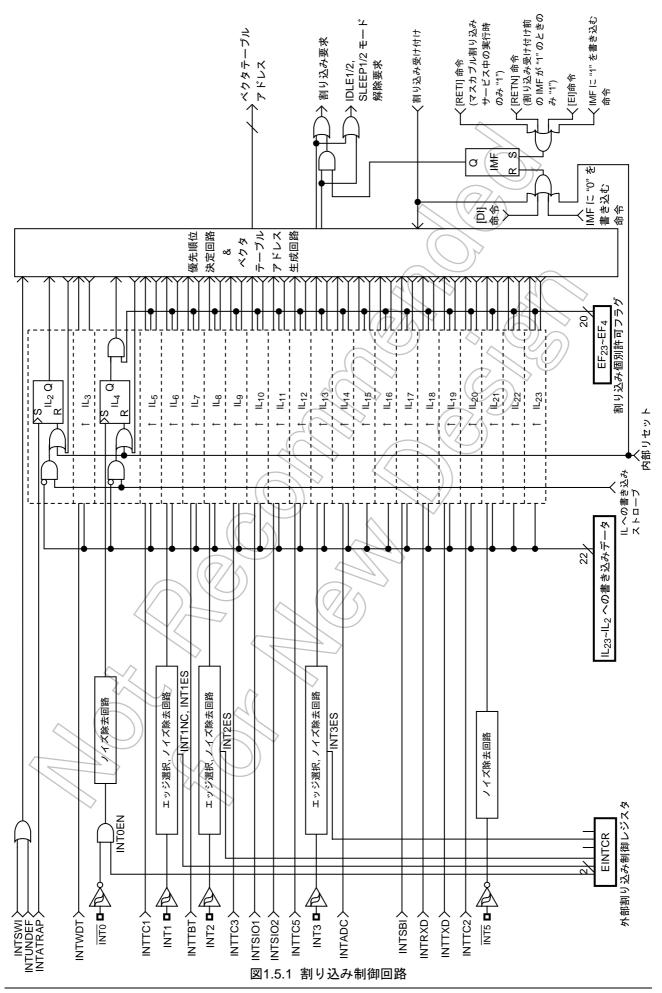

## 1.5 割り込み制御回路

TMP86FM48には、リセットを除き合計 20 種類 (外部: 5 要因、内部: 15 要因) の割り込み要因 があり、優先順位付きの多重割り込みが可能です。内部要因のうち 4 種はノンマスカブル割り込みで、そのほかはすべてマスカブル割り込みです。

割り込み要因には、それぞれ割り込み要求を保持する割り込みラッチ (IL) が用意され、また、独立したベクタになっています。割り込みラッチは、割り込み要求の発生により"1"にセットされ、CPU に割り込みの受け付けを要求します。割り込みの受け付けは、割り込みマスタ許可フラグ (IMF) と各割り込み要因の個別許可フラグ (EF) によって、プログラムで選択し許可/禁止できます。なお、複数の割り込みが同時に発生した場合は、ハードウエアで定められた優先順位の高いものから受け付けられます。ただし、ノンマスカブル割り込みに優先順位はありません。

図 1.5.1に割り込み制御回路を示します。

表1.5.1 割り込み要因

|          | <b>双1.5.1</b>               | リリ込み安囚                     |                     |                      |       |

|----------|-----------------------------|----------------------------|---------------------|----------------------|-------|

|          | 割り込み要因                      | 許可条件                       | 割り込み<br>ラッチ         | ベクタ<br>アドレス          | 優先順位  |

| 内部/外部    | (リセット)                      | ノンマスカブル                    | -                   | FFFEH                | 高位 1  |

| 内 部      | INTSWI (ソフトウエア割り込み)         | ノンマスカブル                    | - \                 | FFFC <sub>H</sub> // | 2     |

| 内 部      | INTUNDEF (未定義命令実行割り込み)      | ノンマスカブル                    | - (7)               | FFFCH                | 2     |

| 内 部      | INTATRAP (アドレストラップ割り込み)     | ノンマスカブル                    | IL <sub>2</sub>     | FFFAH                | 2     |

| 内 部      | INTWDT (ウォッチドッグタイマ割り込み)     | ノンマスカブル                    | IL <sub>3</sub>     | FFF8 <sub>H</sub>    | 2     |

| 外 部      | INTO (外部割り込み 0)             | $IMF \cdot EF_4 = 1$       | (JLA)               | FFF6 <sub>H</sub>    | 5     |

| 内 部      | INTTC1 (タイマカウンタ 1割り込み)      | IMF·EF <sub>5</sub> = 1    | (V <sub>L</sub> 5)) | FFF4 <sub>H</sub>    | 6     |

| 外 部      | INT1 (外部割り込み 1)             | $IMF \cdot EF_6 = 1$       | IL6                 | FFF2 <sub>H</sub>    | 7     |

| 内 部      | INTTBT (タイムベースタイマ割り込み)      | IMF·EF <sub>7</sub> € 1    | IL <sub>7</sub>     | FFF0 <sub>H</sub>    | 8     |

| 外 部      | INT2 (外部割り込み 2)             | IMF·EF <sub>8</sub> = 1    | // IL <sub>8</sub>  | FFEE <sub>H</sub>    | 9     |

| 内 部      | INTTC3 (タイマカウンタ 3割り込み)      | IMF·EF <sub>9</sub> = 1    | // IL <sub>9</sub>  | FFECH                | 10    |

| 内 部      | INTSIO1 (シリアルインタフェース 1割り込み) | IMF · EF <sub>10</sub> = 1 | IL <sub>10</sub>    | FFEA <sub>H</sub>    | 11    |

| 内 部      | INTSIO2 (シリアルインタフェース 2割り込み) | IMF · EF <sub>11</sub> = 1 | IL <sub>11</sub>    | FFE8 <sub>H</sub>    | 12    |

| 内 部      | INTTC5 (タイマカウンタ 5割り込み)      | IMF·EF <sub>12</sub> =1    | IL <sub>12</sub>    | FFE6 <sub>H</sub>    | 13    |

| 外 部      | INT3 (外部割り込み 3)             | IMF · EF <sub>13</sub> = 1 | IL <sub>13</sub>    | FFE4 <sub>H</sub>    | 14    |

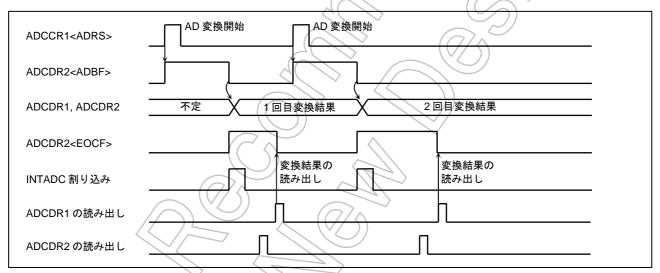

| 内 部      | INTADC (AD変換終了割り込み)         | IMF: EF <sub>14</sub> = 1  | IL <sub>14</sub>    | FFE2 <sub>H</sub>    | 15    |

|          | Reserved                    | IMF · EF <sub>15</sub> = 1 | IL <sub>15</sub>    | FFE0 <sub>H</sub>    | 16    |

|          | Reserved                    | IMF · EF <sub>16</sub> = 1 | IL <sub>16</sub>    | FFBE <sub>H</sub>    | 17    |

| 内 部      | INTSBI (シリアルバスインタフェース割り込み)  | IMF · EF <sub>17</sub> = 1 | IL <sub>17</sub>    | FFBC <sub>H</sub>    | 18    |

| 内 部      | INTRXD (UART 受信割り込み)        | IMF · EF <sub>18</sub> = 1 | IL <sub>18</sub>    | FFBA <sub>H</sub>    | 19    |

| 内 部      | INTTXD (UART 送信割り込み)        | IMF · EF <sub>19</sub> = 1 | IL <sub>19</sub>    | FFB8 <sub>H</sub>    | 20    |

| 内 部      | INTTC2 (タイマカウンタ 2 割り込み)     | $IMF \cdot EF_{20} = 1$    | IL <sub>20</sub>    | FFB6 <sub>H</sub>    | 21    |

| 外 部      | INT5 (外部割り込み 5)             | $IMF \cdot EF_{21} = 1$    | IL <sub>21</sub>    | FFB4 <sub>H</sub>    | 22    |

| $\wedge$ | Reserved                    | IMF · EF <sub>22</sub> = 1 | IL <sub>22</sub>    | FFB2 <sub>H</sub>    | 23    |

|          | Reserved                    | $IMF \cdot EF_{23} = 1$    | IL <sub>23</sub>    | FFB0 <sub>H</sub>    | 低位 24 |

注 1) ウォッチドッグタイマ割り込み (INTWDT) を使用するためには、WDTCR1<WDTOUT>を "0" に設定してください (リセット解除後は、"リセット要求" に設定されています)。 詳しくは「2.4 ウォッチドッグタイマ」を参照してください。

注 2) アドレストラップ割り込み (INTATRAP) を使用するには、WDTCR1<ATOUT>を "0" に設定してください (リセット解除後は、"リセット要求" に設定されています)。 詳しくは「2.4.5 アドレストラップ」をご参照ください。

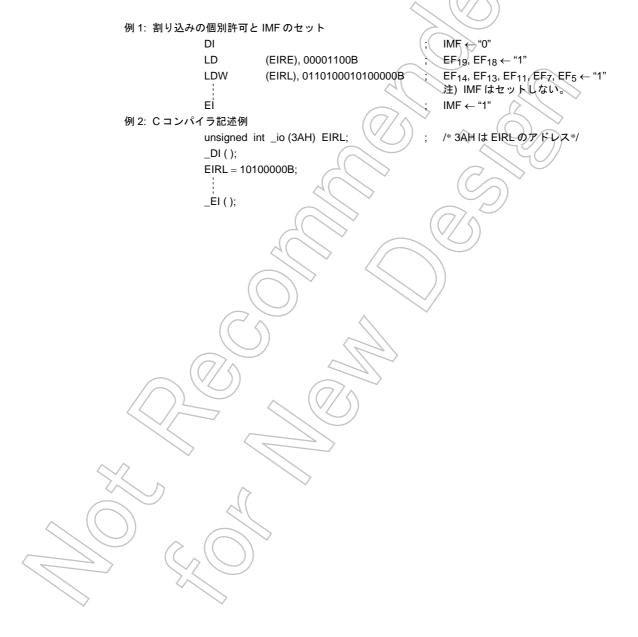

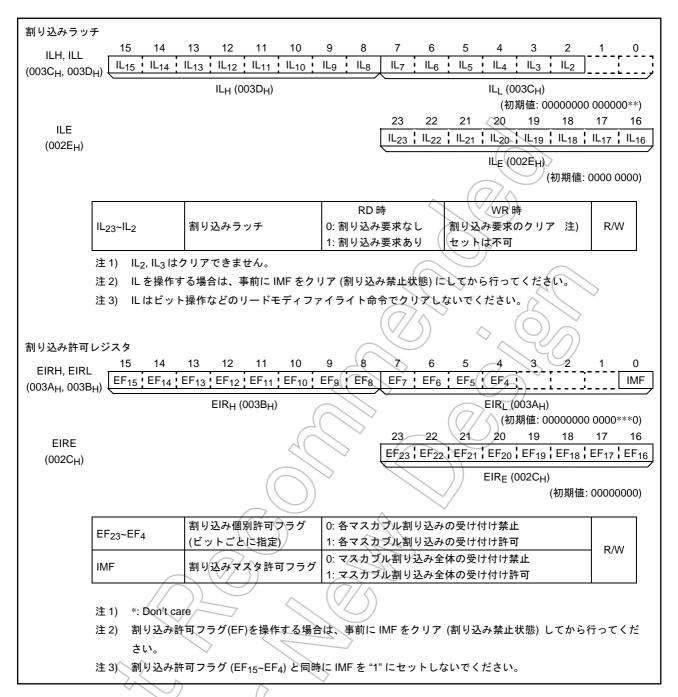

# (1) 割り込みラッチ (IL<sub>24</sub>~IL<sub>2</sub>)

割り込みラッチは、ソフトウエア割り込みを除いて各要因ごとに設けられており、割り込み要求の発生により"1"にセットされます。割り込み受け付けが許可されていると、CPUに割り込みの受け付けを要求します。割り込みが受け付けられた直後に割り込みラッチは"0"にクリアされます。リセット時、割り込みラッチはすべて"0"に初期化されます。

割り込みラッチは、SFR内のアドレス 002EH, 003CH, 003DH に割り付けられており、IL2, IL3 を除いて命令で個別にクリアすることができ(ただし、ビット操作命令や演算命令などのリードモディファイライト命令は使用できません。これは、リードモディファイライト命令実行中に割り込み要求が発生してもクリアされる場合が想定されるためです。)、プログラムで割り込み要求の取り消し/初期化ができます。なお、割り込みラッチを命令で直接セットすることはできません。また、割り込みラッチの内容を読み出すことができますので、割り込み要求のソフトウエアによるテストも可能です。

注) 割り込みラッチ (IL) を操作する場合は、事前にマスタ許可フラグ (IMF) を "0" (割り込み禁止状態) にしてから行ってください。

例 1: 割り込みラッチのクリア

DI

LD (ILE), 11110011B

LDW (ILL), 1110100000111111B

$|L_{12}, L_{10} \sim |L_6 \leftarrow 0|$   $|MF \leftarrow 1|$

$IMF \leftarrow 0$

$IL_{19}$ ,  $IL_{18} \leftarrow 0$

ΕI

例 2: 割り込みラッチの読み出し

LD WA, (HLL)

例 3: 割り込みラッチのテスト TEST (IL).7

R F, SSET

W ← IL<sub>H</sub>, A ← IL<sub>L</sub>

IL<sub>7</sub>=1ならジャンプ

(2) 割り込み許可レジスタ (EIR)

ノンマスカブル割り込み (ソフトウエア割り込み、未定義命令割り込み、アドレストラップ割り込みとウォッチドッグタイマ割り込み) を除く割り込み要因に対して受け付けの許可/禁止を行うレジスタです。メンマスカブル割り込みは、割り込み許可レジスタの内容にかかわらず受け付けられます。

割り込み許可レジスタは、割り込みマスタ許可フラグ (IMF) と割り込み個別許可フラグ (EF) で構成されています。割り込み許可レジスタは、SFR 内のアドレス  $002C_H$ ,  $003A_H$ ,  $003B_H$  に割り付けられており、命令でリード/ライト (ビット操作命令などのリードモディファイライトも含む) できます。

#### a. 割り込みマスタ許可フラグ (IMF)

マスカブル割り込み全体に対して受け付けの許可/禁止の制御を行うフラグです。"0" に クリアされていると、すべてのマスカブル割り込みの受け付けは禁止状態であり、"1" に セットされていると、割り込み個別許可フラグで指定された割り込み受け付けが許可状態です。

割り込みが受け付けられると割り込みマスタ許可フラグはスタックの一時退避された後"0"にクリアされ、そのあとのマスカブル割り込みの受け付けを一時的に禁止します。割り込みサービスプログラムを実行後、マスカブル割り込みリターン命令 [RETI]/[RETN]によりスタックから読み出された値がセットされ割り込み受け付け前の状態に戻ります。

割り込みマスタ許可フラグは、 $EIR_L$  (SFR 内のアドレス  $003A_H$ ) のビット 0 に割り付けられており、命令でリード/ライトできます。通常、割り込みマスタ許可フラグのセット/クリアは、[EI]/[DI]命令で行います。なお、リセット時、割り込みマスタ許可フラグは"0"に初期化されます。

b. 割り込み個別許可フラグ (EF<sub>23</sub>~EF<sub>4</sub>)

各マスカブル割り込み要因に対し、個々に割り込み受け付けの許可/禁止の指定を行うフラグです。割り込み個別許可フラグの該当ビットが"1"なら割り込み受け付けを許可し、"0"なら禁止します。

注) 割り込み個別許可フラグ (EF) を操作する場合は、事前にマスタ許可フラグ (IMF) を "0" にクリア (割り込み禁止状態) にしてから行ってください。通常、割り込みサービスルーチン内では、自動的に IMF = "0" となりますので上記操作は不要ですが、多重割り込みを利用するため割り込みサービスルーチン内で IMF = "1" の操作を行っている場合は、同様な処理を行ってください。

86FM48-35 2007-08-24

図1.5.2 割り込みラッチ (IL), 割り込み許可レジスタ (EIR)

86FM48-36

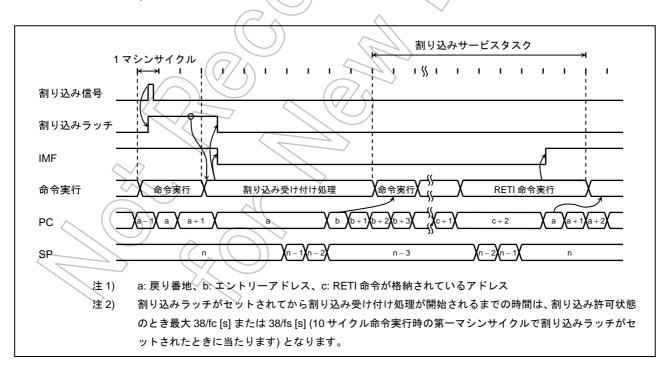

#### 1.5.1 割り込み処理

割り込み要求は、割り込みが受け付けられるか、リセット動作または命令によって、割り込みラッチが"0"にクリアされるまで保持されます。割り込み受け付け処理は、実行中の命令が終了したあと、8マシンサイクル (4  $\mu$ s @ 8.0 MHz) を要して実行されます。割り込みサービスタスクは、割り込みリターン命令 [RETI] (マスカブル割り込みの場合)/[RETN] (ノンマスカブル割り込みの場合)を実行して終了します。図 1.5.3に割り込み受け付け処理タイミングを示します。

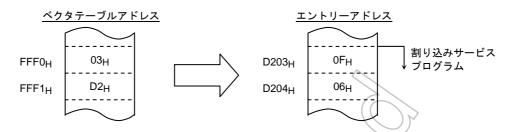

#### (1) 割り込み受け付け処理

割り込み受け付け処理は、次の動作を自動的に行います

- 1. 割り込みマスタ許可フラグ (IMF) を "0" にクリアし、そのあとのマスカブル割り込みの受け付けを一時的に禁止します。

- 2. 受け付けた割り込み要因の割り込みラッチを"0" にクリアします

- 3. プログラムカウンタ (PC) プログラムステータスワード (PSW) および割り込み受け付け前の IMF の内容をスタックに退避します (PSW + IMF, PCH, PCL) の順にプッシュダウンされます)。スタックポインタ (SP) は 3 回デクリメントされます。

- 4. 割り込み要因に応じたベクタテーブルアドレスから割り込みサービスプログラムの エントリーアドレス (割り込みベクタ) を読み出し、プログラムカウンタにセットします。

- 5. 割り込みサービスプログラムのエントリーアドレスに格納されている命令の実行に 移ります。

- 注) PSW の内容がスタックに退避される際、同時に IMF の状態も退避されます。

図1.5.3 割り込み受け付け処理/割り込みリターン命令タイミングチャート

INTTBT の受け付け処理におけるベクタテーブルアドレスと割り込みサービスプ 例: ログラムのエントリーアドレスの対応

割り込みサービス中に、その割り込み要因よりレベルの高いマスカブル割り込みが発生 しても、割り込みマスタ許可フラグが"1"にセットさせるまで受け付けられません。従っ て、多重割り込みを行う場合は、割り込みサービスプログラムの中で、割り込みマスタ許 可フラグを "1" にセットします。その際、割り込み個別許可フラグにより、受け付けて良 い割り込み要因を選択的に許可します。過重なネスティングを防ぐため、現在受け付けて いる割り込みの割り込み個別許可フラグは、割り込みマスタ許可フラグを"1"にセットす る前にクリアしてください。また、ノンマスカブル割り込みは、割り込み要求の間隔より 割り込み処理時間が短くなるようにしてください。

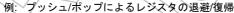

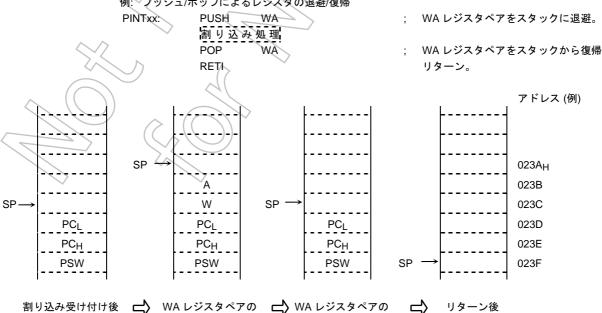

#### (2) 汎用レジスタ退避/復帰処理

割り込み受け付け処理で、プログラムカウンタとプログラムスカータスワードは自動的 にスタックに退避されますが、アキュムレータやそのほかのレジスタは自動的には退避さ れません。これらのレジスタ類の退避処理が必要な場合は、プログラムで行います。また、 多重割り込みを行う場合、退避用のデータメモリ領域が重ならないようにする必要があり ます。

汎用レジスタの退避には、次の2つの方法があります。

# a. プッシュ/ポップ命令による汎用レジスタの退避/復帰

特定のレジスタのみ退避する場合や同一の割り込み要因の多重化の場合には、プッ シュ/ポップ命令により汎用レジスタの退避/復帰を行います。

プッシュ後

ポップ後

#### b. 転送命令による汎用レジスタの退避/復帰

多重割り込みを行わない割り込み処理において、特定のレジスタのみ退避する場合は、データメモリとの転送命令により汎用レジスタの退避/復帰を行います。

#### 例: データメモリとの転送命令によるレジスタの退避/復帰

PINTxx: LD (GSAVA), A ; A レジスタの退避

割り込み処理

LD A, (GSAVA) ; A レジスタの復帰

RETI ; リターン

図1.5.4 割り込み処理における汎用レジスタの退避/復帰処理

#### (3) 割り込みリターン

割り込みリターン命令は、次の動作を行います。

#### [RETII/[RETN] マスカブル割り込みリターン

- 1. プログラムカウンタ、プログラムステータスワードおよび IMFの内容をスタックからそれぞれリストアします。

- 2. スタックポインタを3回インクリメントします。

ただし、アドレストラップ割り込みからのリターンは、割り込み受け付け処理直後にスタックされる PCL、PCH の値を、割り込みサービスプログラムの先頭で、プログラム実行を再開するアドレスに書き替える必要があります。

注) これらを書き替えないままリターン命令 [RETN] を実行した場合、アドレストラップ領域に復帰し、再度アドレストラップ割り込みが発生します。

割り込みリターン後の  $PC_L$ 、 $PC_H$  となる値は、割り込み受け付け処理後はそれぞれ (SP+1)、(SP+2) のアドレスに格納されています。

86FM48-39 2007-08-24

例 1: アドレストラップ割り込みサービスプログラムからのリターン

PINTxx: POP WA ; スタックポインタを 2 つ戻す。

LD WA, ReturnAddress ; WA レジスタに再開アドレスを代入する。

PUSH WA ; スタックにプッシュダウンする。

割り込み処理

RETN ; ノンマスカブル割り込みリターン命令

例 2: リターンしない場合 (割り込み受け付け前の PSW および IMF の値を破棄する場合)

PINTxx: INC SP ; スタックポインタを3つ戻す。

INC SP INC SP 割り込み処理 LD EIRL,

JΡ

EIRL, data RestartAddress IMF を"1" にセット、または "0" にクリア。 復帰アドレスヘジャンプ。

注) アドレストラップ割り込みが発生し、割り込みサービスプログラムでリターン命令 [RETN] を使用しない場合 (例 2 のような場合)、割り込みサービスプログラムで、スタックポインタの値を、アドレストラップ発生時の値にインクリメントすることを推奨します (3 回インクリメントする)。

割り込み要求は、実行中の命令の最終サイクルでサンプリングされます。従って、割り 込みリターン命令の実行直後から次の割り込み処理を行うことができます。

注) 割り込み処理時間が、割り込み要求の発生時間よりも長いと、割り込みサービス タスクの実行のみ行われ、メインタスクの実行が行われなくなります。

## 1.5.2 ソフトウェア割り込み (INTSW)

SWI 命令を実行することにより、ソフトウエア割り込みが発生し直ちに割り込み処理に入ります (最優先割り込み)。

SWI命令は、次に示すアドレスエラー検出またはデバッギング以外には使用しないでください。

#### a. アドレスエラー検出

シングルチップモードのとき、CPU が何らかの原因(ノイズなど)により、メモリの存在しないアドレスから命令フェッチを行った場合、 $FF_H$  が読み込まれます。 コード  $FF_H$  は、SWI 命令ですのでソフトウエア割り込みが発生し、これによりアドレスエラーの検出ができます。また、プログラムメモリの不使用領域をすべて  $FF_H$  で埋めておくことで、アドレスエラー検出範囲がよりいっそう広がります。なお、RAM、SFR 領域に対する命令フェッチのときは、アドレストラップリセット、もしくは設定によりアドレストラップ割り込みがかかります。

# b. デバッギング

SWI 命令をソフトウエアブレークポイント設定アドレスに置くことによって、デバッギング効率を高めることができます。

## 1.5.3 未定義命令割り込み (INTUNDEF)

命令セットで定義されていない命令をフェッチし、実行しようとした場合は、INTUNDEF が発生し、割り込み処理に入ります。INTUNDEF は他のノンマスカブル割り込み処理中でも受け付けられ、現在の処理を中断し、即、INTUNDEF割り込み処理に入ります。

注) 未定義命令割り込み (INTUNDEF) は、ソフトウェア割り込みと同じ割り込みベクタアドレスへジャンプします。

## 1.5.4 アドレストラップ割り込み (INTATRAP)

命令が置かれている以外の領域(アドレストラップ領域)から命令をフェッチした場合、リセット出力または割り込み信号 (INTATRAP) 出力を行います。アドレストラップ割り込みが発生すると、割り込みラッチ (IL2) がセットされ、割り込み処理に入ります。INTATRAP は他のメンマスカブル割り込み処理中でも受け付けられ、現在の処理を中断し、即、INTATRAP 割り込み処理に入ります。

注) アドレストラップ時の動作設定 (リセット出力/割り込み信号出力) は、ウォッチドッグタイマ制御レジスタで設定します。

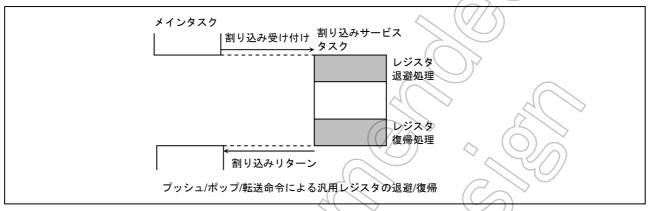

#### 1.5.5 外部割り込み

「TMP86FM48には、5本の外部割り込み入力があり、すべてデジタルノイズ除去回路付き(一定時間未満のパルス入力を、ノイズとして除去します)となっています。

また、INT1~INT3 端子は、エッジ選択が可能です。なお、INTO /P00 端子は、外部割り込み入力端子として使用するか、入出力ポートとして使用するかの選択ができます。リセット時は入力ポートとなります。

エッジの選択、ノイズ除去の制御および INTO /P00 端子の機能選択は、外部割り込み制御レジスタ(EINTCR)で行います。

| 要因   | 端子名  | 兼用端子      | 許可条件                                        | エッジ             | デジタルノイズ除去回路                                                                                                                                           |

|------|------|-----------|---------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT0 | ĪNT0 | P00       | IMF = 1, EF <sub>4</sub> = 1,<br>INT0EN = 1 | 立ち下がりエッジ        | 2/fc [s] 未満のパルスはノイズとして除去されます。7/fc [s] 以上は確実に信号とみなされます。<br>SLOW/SLEEPモード時は、1/fs [s] 未満はノイズとして除去され、3.5/fs [s] 以上は確実に信号とみなされます。                          |

| INT1 | INT1 | P01       | IMF·EF <sub>6</sub> = 1                     | 立ち下がりエッジ<br>または | 15/fc または 63/fc [s] 未満のパルスはノイズとして除去されます。 49/fc または 193/fc [s] 以上は確実に信号とみなされます。<br>SLOW/SLEEP モード時は、1/fs [s] 未満はノイズとして除去され、3.5/fs [s] 以上は確実に信号とみなされます。 |

| INT2 | INT2 | P02       | IMF·EF <sub>8</sub> = 1                     | 立ち上がりエッジ        | 7/fc [s] 未満のパルスはノイズとして除去されます。25/fc [s] 以上は確実に信号とみなされます。<br>SLOW/SLEEP モード時は、1/fs [s] 未満はノイ                                                            |

| INT3 | INT3 | P14/TC3   | IMF·EF <sub>13</sub> = 1                    |                 | 3.5.00W.S.EEF モード時は、1/15 [5] 水洞はアイズとして除去され、3.5/fs [5] 以上は確実に信号とみなされます                                                                                 |

| INT5 | ĪNT5 | P20/ STOP | IMF • EF <sub>21</sub> = 1                  | 立ち下がりエッジ        | 2/fc [s] 未満のパルスはノイズとして除去されます。7/fc [s] 以上は確実に信号とみなされます。<br>SLOW/SLEEP モード時は、1/fs [s] 未満はノイズとして除去され、3.5/fs [s] 以上は確実に信号とみなされます。                         |

表1.5.2 外部割り込み

- 注 1) NORMAL1, NORMAL2 または IDLE1, IDLE2 モード時、ノイズのない信号が外部割り込み端子に 入力された場合、入力信号のエッジから割り込みラッチがセットされるまでの最大時間は次のと おりです。

- 55/fc [s] (INT1NC = "1" のとき), 199/fc [s] (INT1NC = "0" のとき) a. INT1 端子

- b. INT2, INT3 端子 31/fc [s])

- 注 2) INTOEN = "0" のとき、INTO 端子入力の立ち下がりエッジが検出されても割り込みラッチ IL₄ はセ ットされません。

- 注 3) 兼用の端子を出力ポートとして使用し、データが変化したり入出力の切り替えを行った場合、擬 似的に割り込み要求信号が発生しますので、割り込み許可フラグの禁止などの処理が必要です。

- 注 4) INT1NC を切り替えた場合、最大 26/fc の期間ノイズキャンセル時間が切り替わらないことがあり ます。

- 注 1) fc: 高周波クロック [Hz]、\*: Don't care

- 注 2) システムクロックを高周波と低周波の間で切り替えるとき、または外部割り込み制御レジスタ (EINTCR) を 書き替えるときは、切り替えの前後でノイズキャンセラが正常に動作しない場合がありますので、割り込み 許可レジスタ (EIR) によって外部割り込みを禁止しておくことを推奨します。

図1.5.5 外部割り込み制御レジスタ

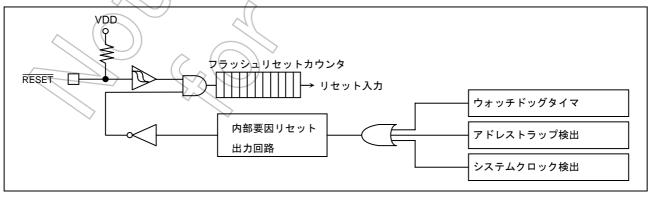

#### 1.6 リセット回路

TMP86FM48 には外部リセット入力, アドレストラップリセット, ウォッチドッグタイマリセット, システムクロックリセットの 4 種類のリセット発生手段があります。

リセット回路は 11 段のフラッシュリセットカウンタを内蔵しており、上記のリセットが発生するとフラッシュ制御回路の電源が安定するまでの間、リセットを発生します。リセット時間は  $2^{10}$ /fc [s] (64  $\mu$ s @ 16MHz) です。

また、電源投入時、内部要因リセット回路 (ウォッチドッグタイマリセット, アドレストラップリセットおよびシステムクロックリセット) は初期化されませんので、最大 24/fc [s] (1.5  $\mu$ s @ 16 MHz) の期間、リセット状態となることがあります。

従ってリセットの最大時間は、24/fc [s] +  $2^{10}/\text{fc}$  [s] (65.5  $\mu$ s @ 16 MHz) となります。表 1.6.1にリセット動作による内蔵ハードウエアの初期化を示します。

| 内蔵ハードウエア                                | 初期値                  | 内蔵ハードウエア                        | 初期値          |

|-----------------------------------------|----------------------|---------------------------------|--------------|

| プログラムカウンタ (PC)                          | (FFFE <sub>H</sub> ) | タイミングジェネレータのプリス                 |              |

| スタックポインタ (SP)                           | 初期化されません             | ダイミングシェイレータのフリス<br>  ケーラおよびデバイダ | 0            |

| 汎用レジスタ (W, A, B, C, D, E, H, L, IX, IY) | 初期化されません             |                                 |              |

| ジャンプステータスフラグ (JF)                       | 初期化されません             | ウォッチドッグタイマ                      | <sub>【</sub> |

| ゼロフラグ (ZF)                              | 初期化されません             |                                 |              |

| キャリーフラグ (CF)                            | 初期化されません             |                                 |              |

| ハーフキャリーフラグ (HF)                         | 初期化されません             | 入出力ポートの出力ラッチ                    | 各入出力ポートの説    |

| サインフラグ (SF)                             | 初期化されません             | 人田ガポートの田ガラッチ                    | 明箇所を参照       |

| オーバフローフラグ (VF)                          | 初期化されません             |                                 |              |

| 割り込みマスク許可フラグ (IMF)                      | 0                    |                                 |              |

| 割り込み個別許可フラグ (EF)                        | 0                    | 制御レジスタ                          | 各制御レジスタの説    |

| 割り込みラッチ (IL)                            | 0                    | 制型レジスタ                          | 明箇所を参照       |

|                                         |                      | RAM                             | 初期化されません     |

表1.6.1 リセット動作による内蔵ハードウエアの初期化

# 1.6.1 外部リセット入力

RESET 端子はプルアップ抵抗付きのセステリシス入力となっており、電源電圧が動作電圧範囲内にあり、発振が安定している条件のもとで最小 3 マシンサイクル (12/fc [s]) 以上の間 RESET 端子を "L" レベルに保つと、リセットがかかり内部状態が初期化されます。

RESET 端子入力が "H" レベルに立ち上がった後、 $2^{10}$ /fc [s] (65.5  $\mu$ s @ 16 MHz) 経過すると、 リセット動作は解除され、アドレス FFFEH~FFFFH に格納されたベクタアドレスからプログラムの実行を開始します。

図1.6.1 リセット回路

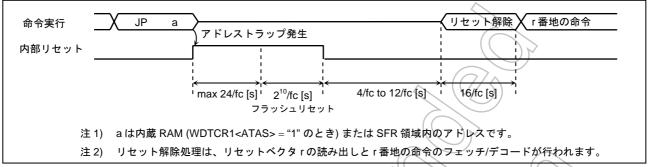

## 1.6.2 アドレストラップリセット

CPU がノイズなどの原因により暴走して内蔵 RAM (WDTCR1<ATAS>= "1" 時), DBR または SFR 領域から命令をフェッチしようとすると内部リセットおよび、フラッシュリセットが発生します。リセット時間は、最大  $24/\text{fc} + 2^{10}/\text{fc}$  [s] (65.5  $\mu$ s @ 16.0 MHz) です。

図1.6.2 アドレストラップリセット

注) アドレストラップはリセットと割り込みの選択が可能です。また、内蔵 RAM はアドレストラップするか否かを WDTCR1<ATAS>によって選択することが可能です。

## 1.6.3 ウォッチドッグタイマリセット

『2.4 ウォッチドッグタイマ』をご参照ください。

# 1.6.4 システムクロックリセット

以下のいずれかの条件が成立した場合、CPU がデッドロック状態に陥るのを防ぐため、自動的にシステムクロックリセットが発生します。(発振は継続します)

- SYSCR2<XEN>, SYSCR2<XTEN> をともに "0" にクリアした場合

- SYSCR2<SYSCK>="0"のとき、SYSCR2<XEN>を"0"にクリアした場合

- SYSCR2<SYSCK>="1"のとき、SYSCR2<XTEN>を"0"にクリアした場合

システムクロックリセットが発生すると、その後フラッシュリセットが発生します。リセット時間は、最大  $24/\text{fc} + 2^{10}/\text{fe}$  [s] (65.5  $\mu$ s @ 16.0 MHz) です。

86FM48-44 2007-08-24

# 2. 周辺ハードウエア機能

## 2.1 スペシャルファンクションレジスタ (SFR)

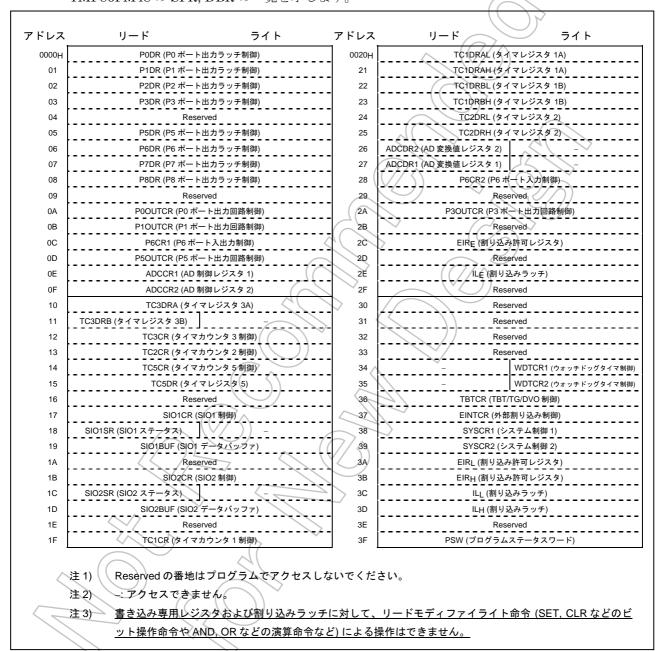

TMP86FM48 は、メモリマップ I/O 方式で、周辺ハードウエアのデータ制御/転送はすべてスペシャルファンクションレジスタ (SFR) またはデータバッファレジスタ (DBR) を通して行われます。 SFR は、 $0000H\sim003FH$  に、DBR は  $1F80H\sim1FFFH$  にマッピングされています。図 2.1.1に TMP86FM48 の SFR, DBR の一覧を示します。

図2.1.1 スペシャルファンクションレジスタ (SFR) (1/2)

|             | アドレス        | リード                    | ライト                  |                                       |

|-------------|-------------|------------------------|----------------------|---------------------------------------|

|             | 1F80H       |                        | erved                | ]                                     |

|             | :           |                        | :                    |                                       |

|             | D8          | Res                    | erved                |                                       |

|             | D9          | -                      | SBICRA (SBI 制御 1)    |                                       |

|             | DA          | SBIDBR (SBI            |                      |                                       |

|             | DB          | -                      | I2CAR (I2C アドレス)     |                                       |

|             | DC          | SBISR (SBI ステータス)      | SBICRB (SBI 制御 2)    | $\langle \langle ( ) \rangle \rangle$ |

|             | DD U        | ARTSR (UART ステータス)     | UARTCR1 (UART 制御 1)  |                                       |

|             | DE          |                        | UARTCR2 (UART 制御 2)  | $V_{\wedge}$                          |

|             | DF          | RDBUF                  | TDBUF                |                                       |

|             | ((          | JART 受信データバッファ)        | (UART 送信データバッファ)     |                                       |

|             | E0          | EEPCR (フラッ             | シュメモリ制御)             |                                       |

|             | E1          | EEPSR                  | _                    |                                       |

|             | (フ          | 'ラッシュメモリステータス)         |                      |                                       |

|             | E2          | EEPEVA (フラッシュメモリ書      | 書き込みエミュレート時間制御)<br>  | $\mathcal{A}(\mathcal{A})$            |

|             | E3          |                        | erved                | 2                                     |

|             | E4          | `                      | 一卜出力回路制御)            |                                       |

|             | E5          |                        | ート入出力制御)             |                                       |

|             | E6          |                        | 《一ト入力制御)<br>         | 901                                   |

|             | E7          |                        | - ト入出力制御)            |                                       |

|             | E8          |                        | erved                |                                       |

|             | E9          |                        | erved                |                                       |

|             | EA          | ++                     | erved                |                                       |

|             | EB          |                        | erved                | )                                     |

|             | EC          |                        | erved                |                                       |

|             | ED          | P0PRD (P0 端子入力)        |                      |                                       |

|             | EE          | P1PRD (P1 端子入力)        |                      |                                       |

|             | EF          | P2PRD (P2 端子入力)        |                      |                                       |

|             | F0<br>F1    | P3PRD (P3 端孑入力)        | J                    |                                       |

|             | F2 -(-(-    | Res<br>P5PRD (P5 端子入力) | erved                |                                       |

|             | F3          | ->                     | erved                |                                       |

|             | F4 //-<     | <i></i>                | erved                |                                       |

|             | F5          | ++                     | erved                |                                       |

|             | F6.         |                        | erved                |                                       |

| <           | F7          | /- / /- /- /-          | erved                |                                       |

|             | F8          |                        | erved                |                                       |

|             | E9          | Res                    | erved                |                                       |

| $\wedge$    | FA          | Res                    |                      |                                       |

|             | FB          | Res                    | erved                |                                       |

|             | FC FC       | Res                    | erved                |                                       |

|             | FD C        | Res                    | erved                |                                       |

|             | FE          | -                      | STOPCR               |                                       |

|             | $\Diamond$  |                        | (キーオンウェイクアップ制御)      |                                       |

|             | (FF)        |                        | erved                |                                       |

|             | 7/          |                        |                      |                                       |

| 注1) Reserve | ed の番地はプログラ | ラムでアクセスしないで            | <b>うください。</b>        |                                       |

|             | セスできません。    |                        |                      |                                       |

| ,           |             |                        |                      | 11 AA (CET CLD to FOL                 |

| 注 3) 書き込み   | 4車用レジスタお上   | び割り込みうッチに対し            | <u>して、リードモディファイラ</u> | イ アヨネ (2F) いえなどいに                     |

図2.1.2 スペシャルファンクションレジスタ (SFR) (2/2)

## 2.2 入出カポート

TMP86FM48は、8ポート54端子の入出力ポートを内蔵しています。

- (1) P0 ポート: 8 ビット入出力ポート (外部割り込み入力,シリアルインタフェース入出力, UART 入出力,タイマカウンタ入力)

- (2) P1 ポート: 8 ビット入出力ポート (外部割り込み入力, シリアルインタフェース入出力, タイマカウンタ入出力と兼用)

- (3) P2 ポート: 3 ビット入出力ポート (低周波発振子接続端子, 外部割り込み入力, STOP モード解除信号入力と兼用)

- (4) P3 ポート: 8 ビット入出力ポート

- (5) P5 ポート: 3 ビット入出力ポート (デバイダ出力,タイマカウンタ出力,シリアルバスインタフェース入出力と兼用)

- (6) P6 ポート: 8 ビット入出力ポート (アナログ入力, STOP モード解除信号と兼用)

- (7) P7ポート: 8ビット入出力ポート (アナログ入力と兼用) △

- (8) P8 ポート: 8 ビット入出力ポート

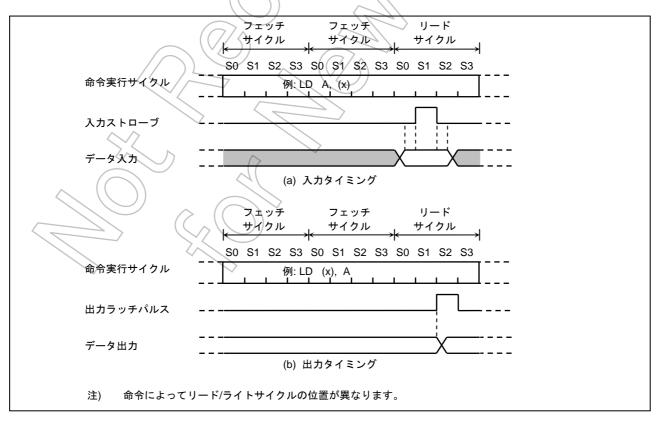

すべての出力ポートは、ラッチを内蔵していますので、出力データはラッチにより保持されます。 すべての入力ポートにはラッチがありませんので、外部から入力データを読み取るまでは、外部で データを保持しておくか、複数回読み取ってから処理することが望まれます。図 2.2.1に入出力タ イミングを示します。

入出力ポートから外部データを読み込むタイミングは、命令実行におけるリードサイクルの S1 ステートです。外部からはこのタイミングを認識できませんので、チャタリングなどの過渡的な入力データはプログラムで対処する必要があります。入出力ポートへデータを出力するタイミングは、命令実行におけるライトサイクルの S2 ステートです。

図2.2.1 入出力タイミング (例)

86FM48-47 2007-08-24

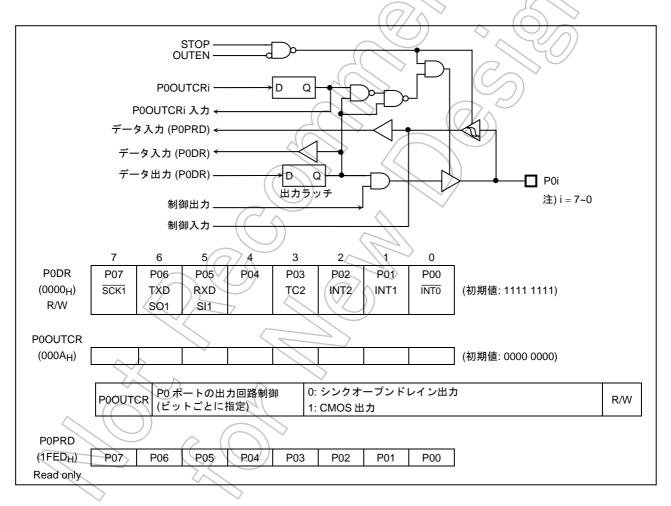

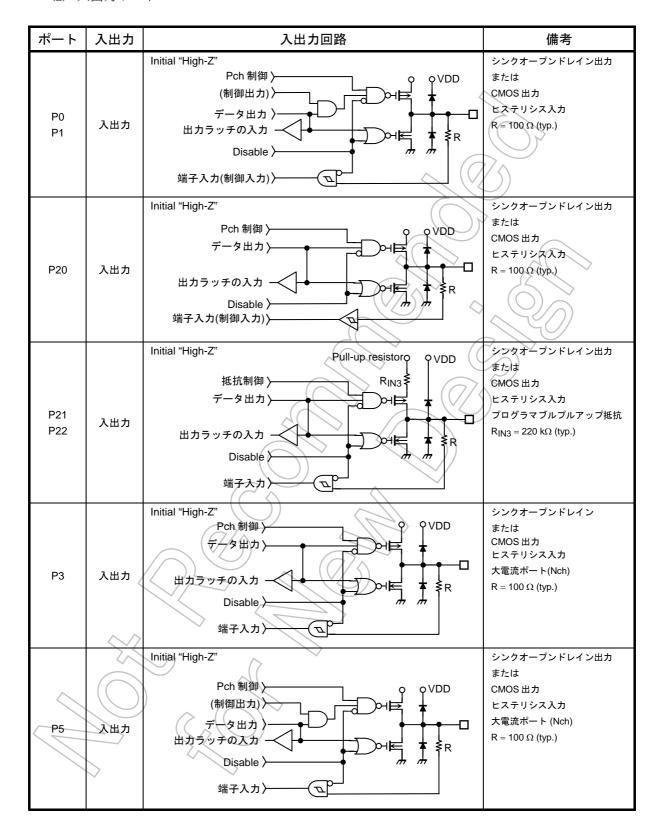

## 2.2.1 P0 (P07~P00) ポート

P0 ポートは8ビットの入出力ポートで、外部割り込み入力、シリアルインタフェース入出力、タイマカウンタ入力、UART 入出力と兼用です。P0 ポートは出力回路制御レジスタ(POOUTCR)により、出力回路をシンクオープンドレイン出力と、CMOS出力のいずれかに設定することができます。POOUTCRを"0"にクリアすると、対応するビットの出力回路はシンクオープンドレイン回路に、POOUTCRを"1"にセットすると、対応するビットの出力回路はCMOS出力となります。

入力ポートまたは、外部割り込み入力、シリアルインタフェース入力、タイマカウンタ入力、 UART 入力として用いる場合は、対応するビットの出力ラッチ (PODR) を "1" にセットし、 POOUTCR を "0" にクリアします。

シリアルインタフェース出力、UART 出力として使用する場合は、対応する PODR のビットを "1" にセットします。

リセット時、PODRは"1"に初期化され、POOUTCRは"0"にクリアされます。

P0ポートはデータ入力のレジスタが独立しています。出力ラッチの状態を読み込む場合は、P0DRを、端子の状態を読み込む場合は P0PRD レジスタを、それぞれ読み出してください。

図2.2.2 P0ポート

86FM48-48 2007-08-24

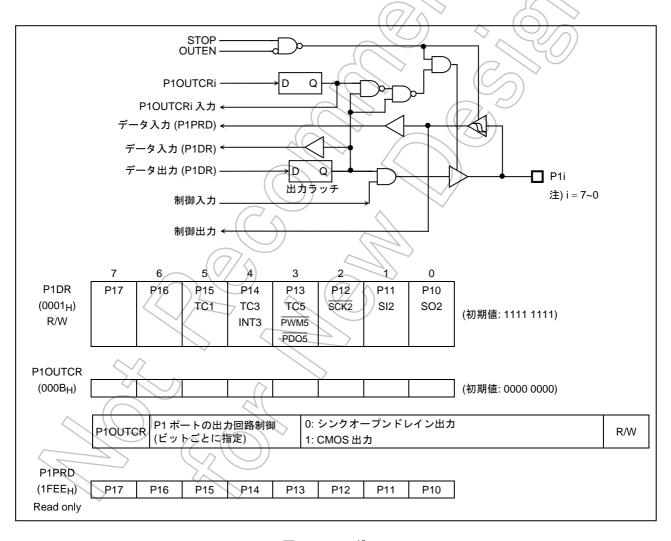

# 2.2.2 P1 (P17~P10) ポート

P1 ポートは8ビットの入出力ポートで、外部割り込み入力、シリアルインタフェース入出力、タイマカウンタ入出力と兼用です。P1ポートは出力回路制御レジスタ (P1OUTCR) により、出力回路をシンクオープンドレイン出力と、CMOS 出力のいずれかに設定することができます。P1OUTCRを"0"にクリアすると、対応するビットの出力回路はシンクオープンドレイン回路に、P1OUTCRを"1"にセットすると、対応するビットの出力回路はCMOS出力となります。

入力ポートまたは外部割り込み入力、シリアルインタフェース入力、タイマカウンタ入力として用いる場合は、対応するビットの出力ラッチ (P1DR) を "1" にセットし、P1OUTCR を "0" にクリアします。

シリアルインタフェース出力、タイマカウンタ出力として使用する場合は、対応する P1DR のビットを "1" にセットします。

リセット時、P1DRは"1"に初期化され、P1OUTCRは"0"にクリアされます。

P1 ポートはデータ入力のレジスタが独立しています。出力ラッチの状態を読み込む場合は P1DR を、端子の状態を読み込む場合は P1PRD レジスタを、それぞれ読み出してください。

図2.2.3 P1ポート

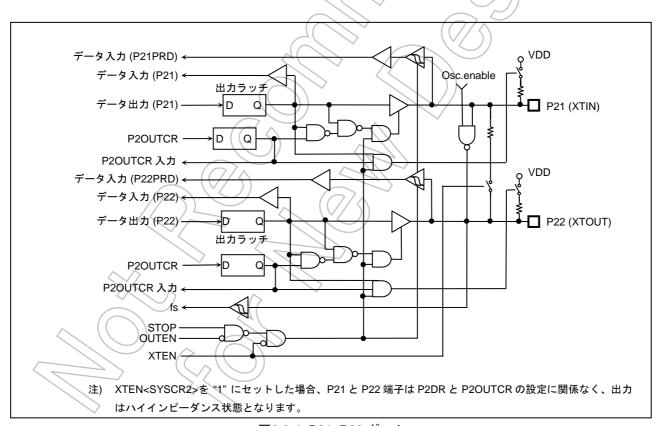

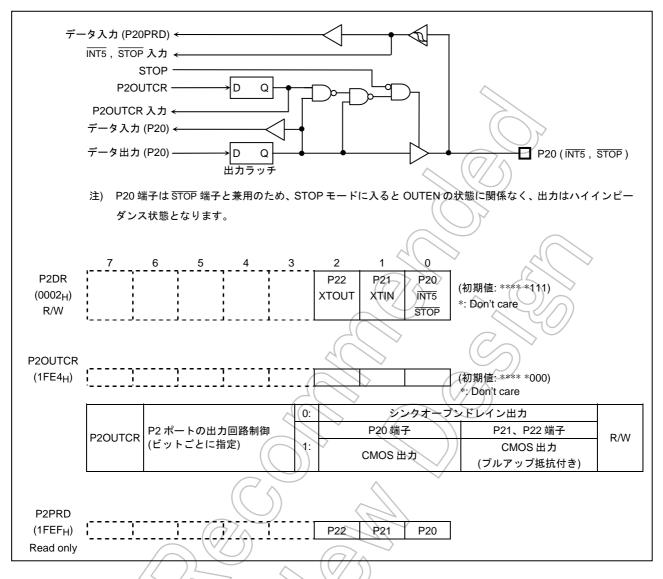

## 2.2.3 P2 (P22~P20) ポート

P2 ポートは 3 ビットの入出力ポートで、外部割り込み入力、STOP 解除信号入力、低周波発振子接続端子と兼用です。P2 ポートは出力回路制御レジスタ (P2OUTCR) により、出力回路をシンクオープンドレイン出力と、CMOS 出力 (P21、P22 端子はプルアップ抵抗付き)のいずれかに設定することができます。P2OUTCR を "0" にクリアすると、対応するビットの出力回路はシンクオープンドレイン回路に、P2OUTCR を "1" にセットすると、対応するビットの出力回路は CMOS 出力となります。

入力ポートまたは、外部割込み入力として用いる場合は、出力ラッチ (P2DR) を "1" にセットします。リセット時、P2DR は "1" に初期化されます。

デュアルクロックモードで動作させる場合は、P21 (XTIN)、P22 (XOUT) 端子に低周波発振子 (32.768 kHz) を接続します。シングルクロックモードで動作させる場合、P21、P22 端子は通常の入出力ポートとして使用できます。なお、P20 端子は外部割り込み入力、STOP 解除信号入力、入力ポートとして使用されることを推奨します(出力ポートとして使用すると、立ち下がりで割り込みラッチがセットされます)。

また、P2 ポートはデータ入力のレジスタが独立しています。出力ラッチの状態を読み込む場合は P2DR を、端子の状態を読み込む場合は P2PRD レジスタをそれぞれ読み出してください。

P2 ポートに対して P2DR、P2PRD のリード命令を実行した場合、ビット 7~3 は不定値が読み込まれます。

図2.2.4 P21, P22 ポート

図2.2.5 P20ポート

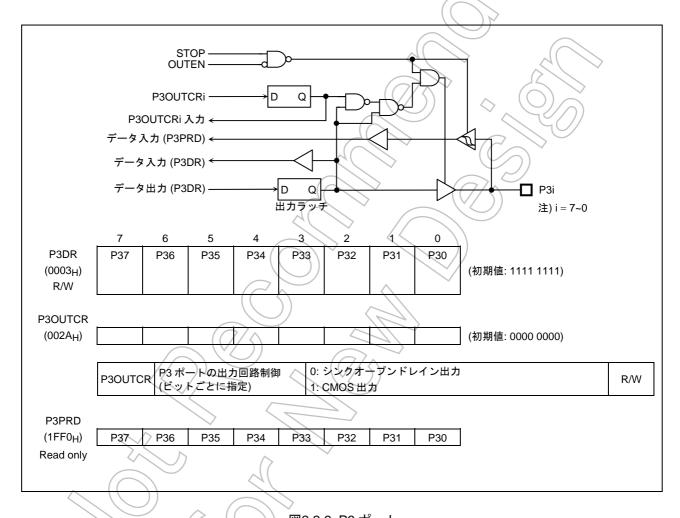

## 2.2.4 P3 (P37~P30) ポート

P3 ポートは、8 ビットの入出力ポートです。P3 ポートは出力回路制御レジスタ (P3OUTCR) により、出力回路をシンクオープンドレイン出力と、CMOS 出力のいずれかに設定することができます。P3OUTCR を "0" にクリアすると、対応するビットの出力回路はシンクオープンドレイン回路に、P3OUTCR を "1" にセットすると、対応するビットの出力回路は CMOS 出力となります。

入力ポートとして用いる場合は、対応するビットの出力ラッチ (P3DR) を "1" にセットし、P3OUTCR を "0" にクリアします。

リセット時、P3DRは"1"に初期化され、P3OUTCRは"0"にクリアされます。

P3 ポートはデータ入力のレジスタが独立しています。出力ラッチの状態を読み込む場合は P3DR を、端子の状態を読み込む場合は P3PRD レジスタをそれぞれ読み出してください。

図2.2.6 P3ポート

86FM48-52 2007-08-24

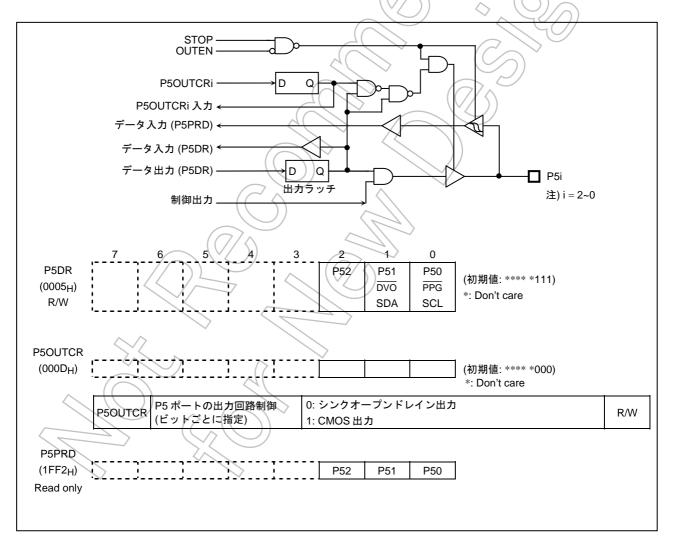

## 2.2.5 P5 (P52~P50) ポート

P5 ポートは 3 ビットの入出力ポートで、タイマカウンタ出力、デバイダ出力、シリアルインタフェース入出力と兼用です (N-ch 大電流)。P5 ポートは出力回路制御レジスタ (P5OUTCR) により、出力回路をシンクオープンドレイン出力と、CMOS 出力のいずれかに設定することができます。P5OUTCR を "0" にクリアすると、対応するビットの出力回路はシンクオープンドレイン回路に、P5OUTCR を "1" にセットすると、対応するビットの出力回路は CMOS 出力となります。

入力ポートまたは、シリアルバスインタフェース入出力として用いる場合は、対応するビットの出力ラッチ (P5DR) を "1" にセットし、P5OUTCR を "0" にクリアします。

タイマカウンタ出力、デバイダ出力として使用する場合は、対応する P5DR のビットを"1" にセットします。

リセット時、P5DRは"1"に初期化され、P5OUTCRは"0"にクリアされます。

P5 ポートはデータ入力のレジスタが独立しています。出力ラッチの状態を読み込む場合は P5DR を、端子の状態を読み込む場合は P5PRD レジスタをそれぞれ読み出してください。

P5DR, P5OUTCR, P5PRD に対してリード命令を実行した場合、ビット 7~3 は不定値が読み込まれます。

図2.2.7 P5ポート

86FM48-53 2007-08-24

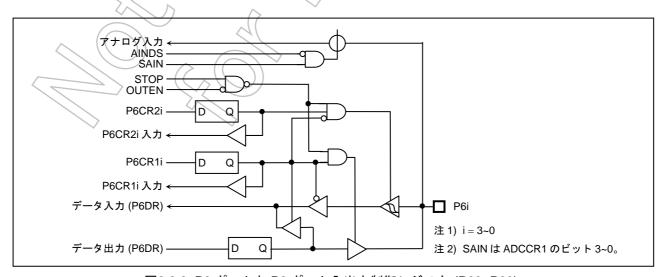

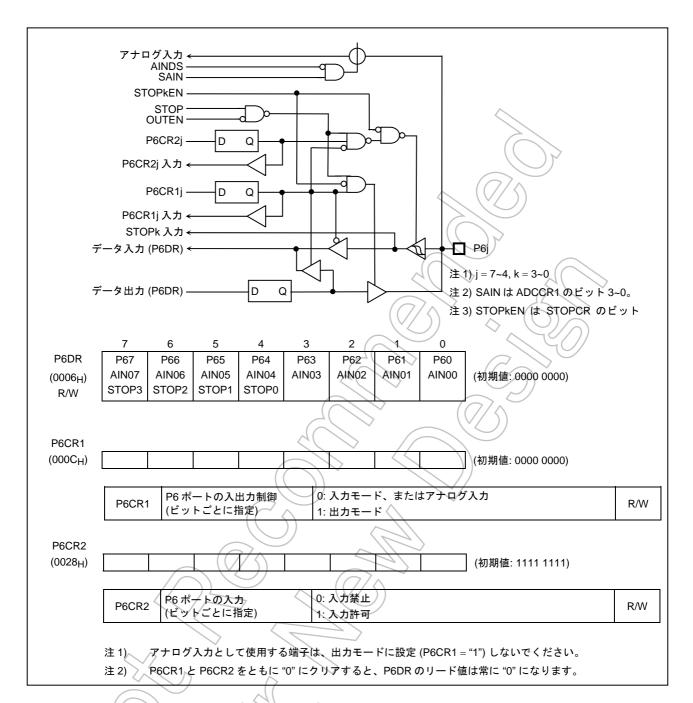

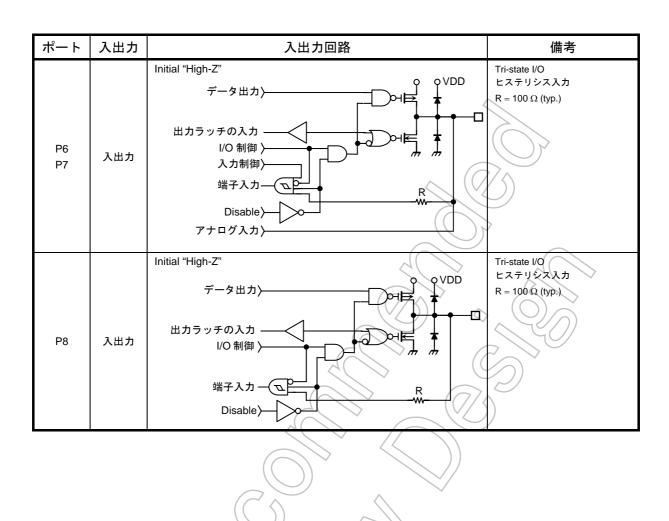

## 2.2.6 P6 (P67~P60) ポート

P6 ポートは、1 ビット単位で入出力の指定ができる 8 ビットの入出力ポートで、アナログ入力、キーオンウェイクアップ入力と兼用です。入出力の指定は、入出力制御レジスタ (P6CR1) と入力制御レジスタ (P6CR2) によって行います。

出力ポートとして使用する場合は、P6CR1の対応するビットを"1"に設定します。

入力ポートとして使用する場合は、P6CR1 の対応するビットを "0" にクリアし、P6CR2 の対応するビットを "1" にセットします。

アナログ入力として使用する場合は、P6CR1 の対応するビットを "0" にクリアした後、P6CR2 の対応するビットを "0" にクリアします。

キーオンウェイクアップ入力として使用する場合は、キーオンウェイクアップ制御レジスタ (STOPCR) により、入力を許可する端子に対応する STOPkEN ビットを "1" にセットします ( $k = 3 \sim 0$ )。

リセット時、P6CR1 と P6DR は "0" にクリアされ、P6CR2 は "1" に初期化されます。 表 2.2.1、表 2.2.2に各レジスタ設定値と端子状態を示します。

| P6CR1 | P6CR2 | P6DR | P6DR リード値   | 出力        | 備考    |

|-------|-------|------|-------------|-----------|-------|

| 0     | 0     | *    | "0"         | ハイインピーダンス | _     |

| 0     | 1     | *    | 端子入力        | ハイインピーダンス | 入力モード |

| 1     | *     | 0    | "0" (出カラッチ) | Low       | 出力モード |

| 1     | *     | 1    | "1" (出力ラッチ) | High      | 出力モード |

表2.2.1 各レジスタ設定値と P63~P60 端子状態

注) \*: Don't care.

| STOPKEN | P6CR1 | P6CR2 | P6DR     | P6DR リード値   | 出力        | 備考                |

|---------|-------|-------|----------|-------------|-----------|-------------------|

| 0       | 0     | 0     | ( ( *    | "0"         | ハイインピーダンス | -                 |

| 0       | 0     | 1 _   | *        | 端子入力        | ハイインピーダンス | 入力モード             |

| 0       | 1     | * ((  | 7/<9     | "0" (出カラッチ) | Low       | 出力モード             |

| 0       | 1 /   | * (   | <u> </u> | "1" (出力ラッチ) | High      | 出力モード             |

| 1       | *     | *     | *        | "1" (出カラッチ) | ハイインピーダンス | キーオンウェイクアップ<br>入力 |

表2.2.2 各レジスタ設定値と P67~P64 端子状態

注 1) \*: Don't care.

#### 注 2) STOPKEN は STOPCR レジスタのビット 7~4。

図2.2.8 P6 ポートと P6 ポート入出力制御レジスタ (P63~P60)

86FM48-54 2007-08-24

図2.2.9 P6ポートと P6ポート入出力制御レジスタ (P67~P64)

## 2.2.7 P7 (P77~P70) ポート

P7 ポートは、1 ビット単位で入出力の指定ができる 8 ビットの入出力ポートで、アナログ入力と兼用です。入出力の指定は、入出力制御レジスタ (P7CR1) と入力制御レジスタ (P7CR2) によって行います。

出力ポートとして使用する場合は、P7CR1の対応するビットを"1"に設定します。

入力ポートとして使用する場合は、P7CR1 の対応するビットを "0" にクリアし、P7CR2 の対応するビットを "1" にセットします。

アナログ入力として使用する場合は、P7CR1 の対応するビットを "0" にクリアした後、P7CR2 の対応するビットを "0" にクリアします。

リセット時、P7CR1 と P7DR は "0" にクリアされ、P7CR2 は "1" に初期化されます。 表 2.2.3に各レジスタ設定値と端子状態を示します。

表2.2.3 各レジスタ設定値と P7 端子状態

| P7CR1 | P7CR2 | P7DR | P7DR リード値   | 出力        | 備考    |

|-------|-------|------|-------------|-----------|-------|

| 0     | 0     | *    | "0"         | ハイインピーダンス | -     |

| 0     | 1     | *    | 端子入力        | ハイインピーダンス | 入力モード |

| 1     | *     | 0    | "0" (出カラッチ) | Low       | 出力モード |

| 1     | *     | 1    | "1" (出カラッチ) | High      | 出カモード |

図2.2.10 P7ポート

86FM48-56 2007-08-24

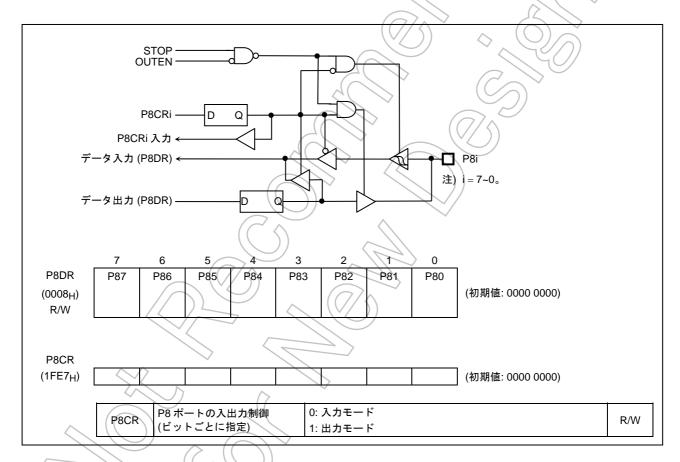

# 2.2.8 P8 (P87~P80)ポート

P8 ポートは、1 ビット単位で入出力の指定ができる 8 ビットの入出力ポートです。入出力の指定は、入出力制御レジスタ (P8CR) によって行います。

出力ポートとして使用する場合は、P8CR の対応するビットを"1"に設定します。 入力ポートとして使用する場合は、P8CR の対応するビットを"0"にクリアします。

リセット時、P8CRとP8DRは"0"にクリアされます。

表 2.2.4に各レジスタ設定値と端子状態を示します。

表2.2.4 各レジスタ設定値と P8 端子状態

| P8CR | P8DR | P8DR リード値   | 出力(   備考        |  |

|------|------|-------------|-----------------|--|

| 0    | *    | 端子入力        | ハイインピーダンス 入力モード |  |

| 1    | 0    | "0" (出カラッチ) | Low 出力モード       |  |

| 1    | 1    | "1" (出力ラッチ) | High 出力モード      |  |

<sup>\*:</sup> Don't care.

図2.2.11 P8ポート

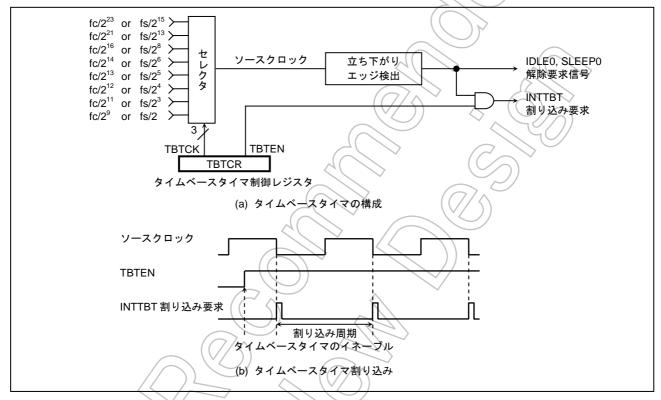

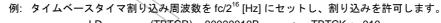

# 2.3 タイムベースタイマ (TBT)

タイムベースタイマは、キースキャンやダイナミック表示処理などの基準時間生成用タイマで、一定周期ごとにタイムベースタイマ割り込み (INTTBT) を発生します。

タイムベースタイマ割り込みは、タイムベースタイマをイネーブルにした後、ソースクロック(タイミングジェネレータのデバイダ出力を TBTCK で選択)の最初の立ち下がりから発生します。 なお、デバイダはプログラムでクリアされませんので、最初の割り込みに限り設定した割り込み周期よりも早く割り込みが発生することがあります (図 2.3.1 (b) 参照)。

割り込み周波数の選択は、タイムベースタイマがディセーブルの状態で行ってください (イネーブル状態からディセーブルにする際も割り込み周波数の設定を変更しないでください)。なお、周波数の選択とイネーブルを同時にすることはできます。

図2.3.1 タイムベースタイマ

SET (EIRL). 6

86FM48-58 2007-08-24

図2.3.2 タイムベースタイマ制御レジスタ

表2.3.1 タイムベースタイマ割り込み周波数 (例: fc = 16 MHz, fs = 32.768 kHz 時)

|       |              |             | 1 1 / 2 ) |

|-------|--------------|-------------|-----------|

|       | タイムベー        | 引波数 [Hz]    |           |

| TBTCK | NORMAL1/2, I | SLOW, SLEEP |           |

|       | DV7CK = 0    | DV7CK = 1   | ₹=k       |

| 000   | 1.91         | 1           | \\ 1      |

| 001   | 7.63         | 4           | // 4      |

| 010   | 244.14       | 128         |           |

| 011   | 976.56       | 512         | _         |

| 100   | 1953.13      | 1024        | -         |

| 101   | 3906.25      | 2048        | -         |

| 110   | 7812.5       | 4096        | =         |

| 111   | 31250        | 16384       | =         |

# 2.4 ウォッチドッグタイマ (WDT)

ウォッチドッグタイマは、ノイズなどの原因による誤動作(暴走)やデッドロック状態を速やかに 検出し、正常な状態に戻すことを目的としたフェイルセーフ機能です。

ウォッチドッグタイマによる暴走検出信号は、"リセット要求"または"ノンマスカブル割り込み要求"のいずれかにプログラムで選択することができます。ただし、選択は1回限りです。リセット解除時は、"リセット要求"に初期化されます。

なお、ウォッチドッグタイマを暴走検出用として使用しない場合、一定周期ごとに割り込みを発生するタイマとして利用できます。

注) 外乱ノイズなどの影響によっては、ウォッチドッグタイマが完全な機能を果たせない場合 がありますので、機器設計時には十分な考慮が必要です。

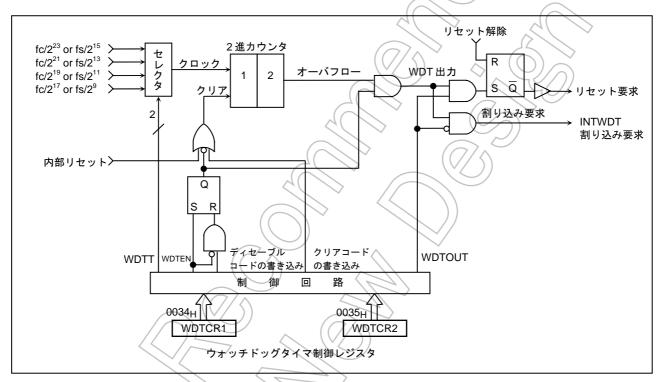

#### 2.4.1 ウォッチドッグタイマの構成

図2.4.1 ウォッチドッグタイマの構成

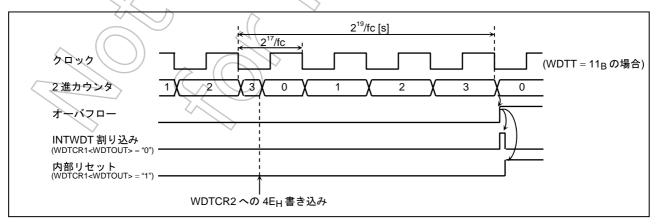

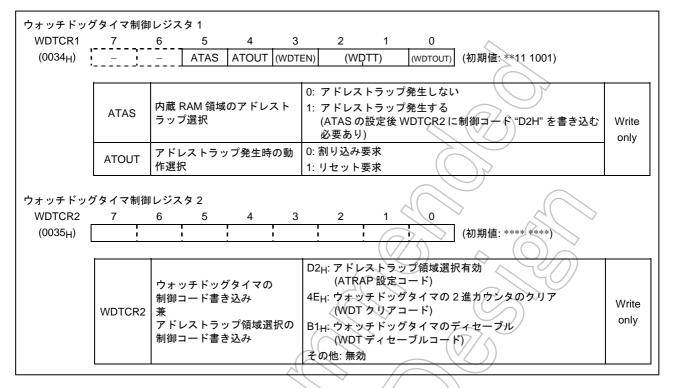

#### 2.4.2 ウォッチドッグタイマの制御

ウォッチドッグタイマの制御レジスタを図 2.4.2に示します。リセット解除後、ウォッチド ッグタイマはイネーブルになります。

(1) ウォッチドッグタイマによる暴走検出の方法

CPU の暴走検出を行うには、次のようにします。

- a. 検出時間の設定、出力の選択および2進カウンタのクリア

- b. 設定した検出時間以内ごとに、2進カウンタのクリアを繰り返し行います。

もし、何らかの原因で暴走またはデッドロック状態に陥り、2進カウンタのクリアが行 われないと、2 進力ウンタのオーバフローでウォッチドッグタイマ出力がアクティブにな ります。このとき WDTCR1<WDTOUT> = "1" ならリセットが発生し、内蔵ハードウエ アをリセットします。また、WDTCR1<WDTOUT>="0"なら、ウォッチドッグタイマ割 り込み (INTWDT) を発生します。

なお、STOP モード(ウォームアップ中を含む)または IDLE モード中、ウォッチドッグ タイマは一時的にカウントアップを停止し、STOP/IDLE モード解除後、自動的に再起動 (カウントアップ継続) します。

注) ウォッチドッグタイマは、内部デバイダと2段の2進カウンタによって構成され ており、クリアコード(4EH)を書き込んだ場合、2進カウンタはクリアされますが、 内部デバイダはクリアされません。従って 2 進力ウンタのオーバフロー時間は、 WDTCR2 レジスタにクリアコード (4En) を書き込むタイミングによって、最短で WDTCR1<WDTT>の設定時間の 3/4 となる場合がありますので、これより短い周 期でクリアコードを書き込んでください。

例:ウォッチドッグタイマ検出時間を 2<sup>21</sup>/fc [s] に設定し、暴走検出リセットを行う。

; 2進カウンタのクリア ΓÞ (WDTCR2), 4EH LĎ

(WDTCR1), 00001101B ; WDTT  $\leftarrow$  10, WDTOUT  $\leftarrow$  1

(WDTCR2), 4EH 2進カウンタのクリア (WDTT 変更直前直

後は必ずクリアします。)

(WDTCR2), 4EH : 2進カウンタのクリア

LD WDT 検出 時間 3/4 以内

/LØ

LD

WDT 検出 時間 3/4 以内

(WDTCR2), 4EH

; 2進カウンタのクリア

ウォッチドッグタイマ制御レジスタ 1 WDTCR1 7 6 5 4 3 2 1 0 (0034<sub>H</sub>) - - - (ATAS) (ATOUT) WDTEN WDTOUT (初期値: \*\*11 1001)

| WDTEN  | ウォッチドッグタイマの               | `         | 0: 禁止 (WDTCR2 にディセーブルコードを書き込む必要あり) |                      |                     |       |

|--------|---------------------------|-----------|------------------------------------|----------------------|---------------------|-------|

|        | 許可/禁止                     | 1: 許可     |                                    | $\wedge$             |                     |       |

|        |                           |           | NORMAL                             | 1/2 モード              | SLOW1/2             |       |

|        | ウォッチドッグタイマ<br>DTT 検出時間の設定 |           | DV7CK = 0                          | DV7CK = 1            | モード                 |       |

| WDTT   |                           | 00        | 2 <sup>25</sup> /fc                | 2 <sup>17</sup> /fs  | 2 <sup>17</sup> /fs | Write |

| WDII   | 単位: [s]                   | 01        | 2 <sup>23</sup> /fc                | 2 <sup>15</sup> /fs  | 2 <sup>15</sup> /fs | only  |

|        | 4 E. [9]                  | 10        | 2 <sup>21</sup> /fc                | (2 <sup>13</sup> /fs | 2 <sup>13</sup> /fs |       |

|        |                           | 11        | 2 <sup>19</sup> /fc                | 2 <sup>f1</sup> /fs  | 2 <sup>11</sup> /fs |       |

| WDTOUT | ウォッチドッグタイマ出力の             | 0: 割り込み要求 |                                    |                      |                     |       |

| WDTOOT | 選択                        | 1: リセット要求 | : ((                               | <u>) }</u>           |                     |       |

- 注 1) WDTOUT を "0" にクリア後は、プログラムで "1" に再セットできません。

- 注 2) fc: 高周波クロック[Hz]、fs: 低周波クロック[Hz]、\*: Don't care

- 注 3) WDTCR1 は書き込み専用レジスタですので、ビット操作などのリードモディファイライト命令ではアクセスしないでください。

- 注4) STOPモード起動時は、STOPモードに入る直前にウォッチドッグタイマを禁止するか、カウンタをクリアしてください。

また、カウンタをクリアした場合は、STOP モード解除直後に再度カウンタをクリアしてください。

注 5) WDTEN を "1" から "0" に切り替える場合は、誤動作の原因となる場合がありますので、直前に WDTCR2 へ "4EH" を書き込み、2 進カウンタをクリアした後、WDTCR2 へ "B1H" を書き込んでウォッチドッグタイマをディセーブルにしてください。また、これらの動作の直前に、割り込みマスタ許可フラグ (IMF) を "0" に設定してください。

#### ウォッチドッグタイマ制御レジスタ2

WDTCR2 (0035<sub>H</sub>)

|        | $(\bigcirc )$ | 4E <sub>H</sub> : ウォッチドッグタイマの 2 進カウンタのクリア<br>(クリアコード) |       |

|--------|---------------|-------------------------------------------------------|-------|

| WDTCR2 | 1/7/          | B1H: ウォッチドッグタイマのディセーブル                                | Write |

|        | 制御コード書き込み     | (ディセーブルコード)<br>D2 <sub>H</sub> : アドレストラップ領域選択有効       | only  |

|        |               | その他、無効                                                |       |

- 注 1) ディセーブルコードは、WDTCR1<WDTEN> = "0" のとき以外は書き込み無効です。

- 注 2) \*: Don't care

- 注 3) ウォッチドッグタイマの2進カウンタのクリアは、割り込みタスクで行わないでください。

- 注 4) クリアコード (4EH) は、WDTCR1<WDTT>の設定時間の 3/4 以内に書き込んでください。

## 図2.4.2 ウォッチドッグタイマ制御レジスタ

(2) ウォッチドッグタイマのイネーブル

WDTCR1<WDTEN> を "1" にセットするとイネーブルになります。リセット時、WDTCR1<WDTEN> は "1" に初期化されますので、リセット解除後ウォッチドッグタイマは直ちに動作します。

(3) ウォッチドッグタイマのディセーブル

ウォッチドッグタイマをディセーブルするには、割り込みマスタ許可フラグ (IMF) を "0" にし、WDTCR2 にクリアコード ( $4E_H$ ) を書き込んだ後、WDTCR1<WDTEN> を "0" にクリアします。その後 WDTCR2 にディセーブルコード ( $B1_H$ ) を書き込むことによりディセーブルになります。なお、逆に WDTCR2 にディセーブルコードを書き込んだ後、WDTCR1<WDTEN> を "0" にクリアしてもディセーブルになりません。ディセーブル中は、ウォッチドッグタイマの 2 進力ウンタはクリアされています。

例: ウォッチドッグタイマのディセーブル

DI ;  $\mathsf{IMF} \leftarrow \mathsf{0}$

LD (WDTCR2), 4E<sub>H</sub> ; 2 進カウンタのクリア

LDW (WDTCR1), 0B101H ; WDTEN  $\leftarrow$  0, WDTCR2  $\leftarrow$   $\vec{\tau}$   $\tau$   $\tau$   $\tau$   $\tau$   $\tau$

コード

#### 表2.4.1 ウォッチドッグタイマ検出時間 (例: fc = 16 MHz 時, fs = 32.768 kHz 時)

|      | ウォッチ      | ・ドックタイマ検出 | 時間 [s]                                  |

|------|-----------|-----------|-----------------------------------------|

| WDTT | NORMAL    | 1/2 モード   | SLOW                                    |

|      | DV7CK = 0 | DV7CK = 1 | <b>T</b>                                |

| 00   | 2.097     | 4         | ( \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| 01   | 524.288 m | 1         |                                         |

| 10   | 131.072 m | 250 m     | 250 m                                   |

| 11   | 32.768 m  | 62.5 m    | 62.5 m                                  |

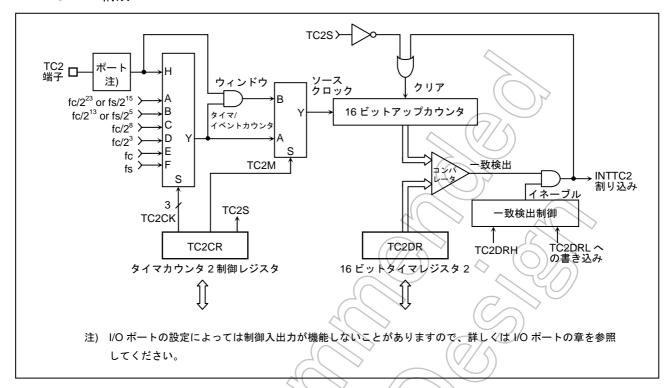

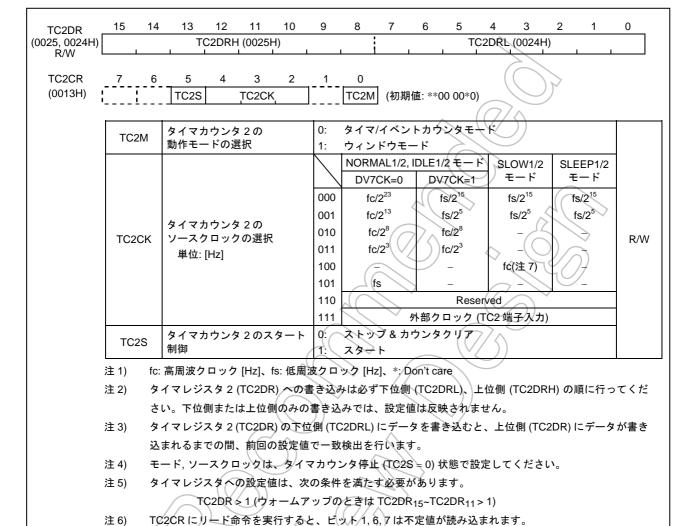

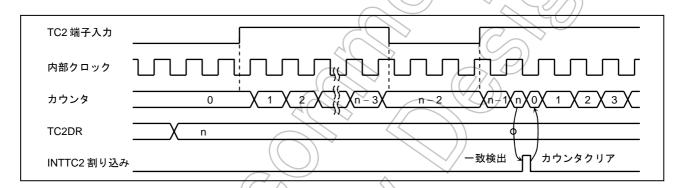

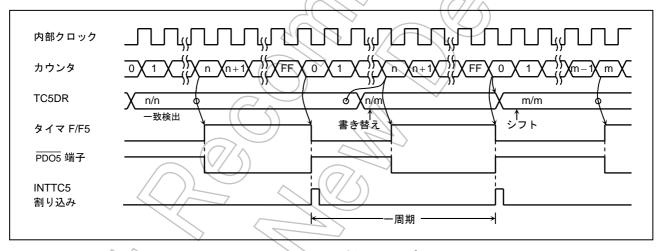

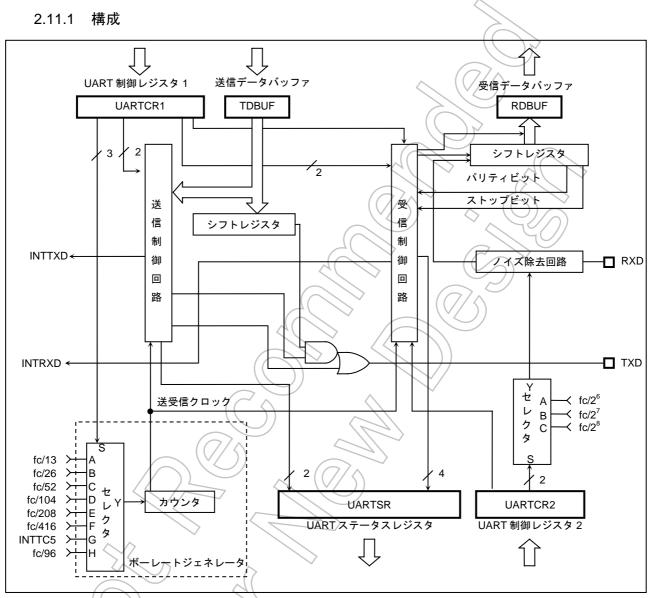

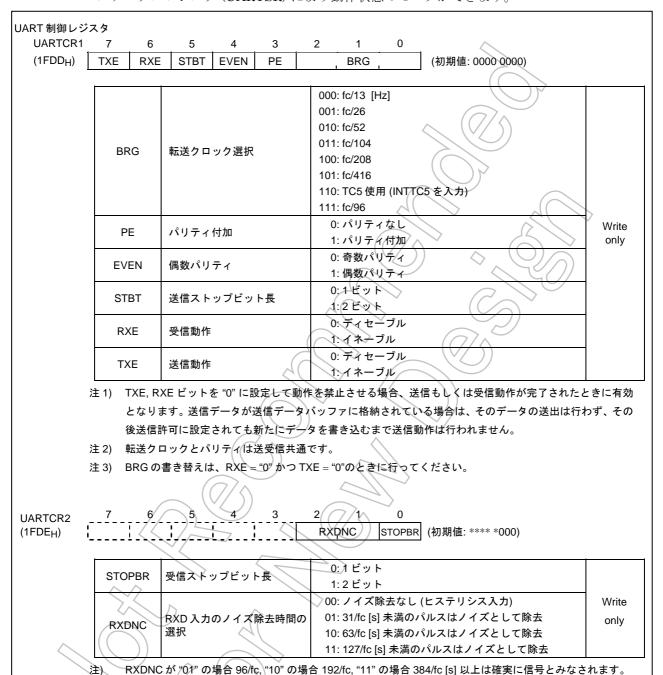

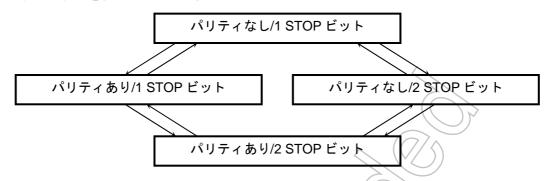

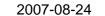

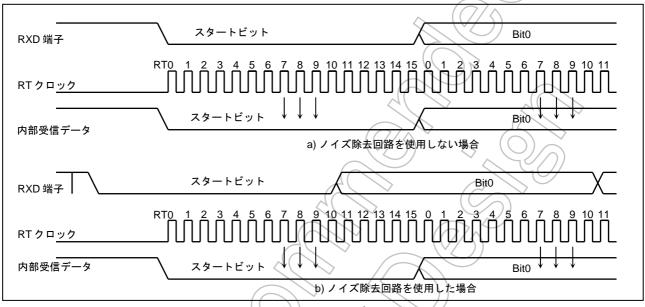

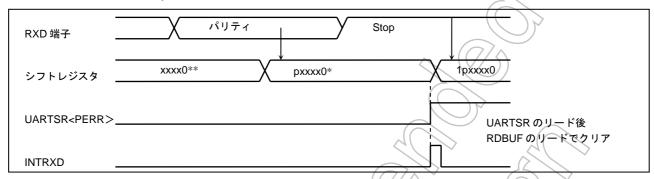

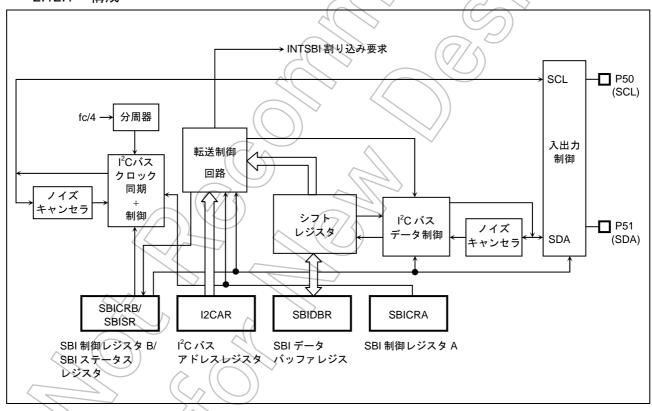

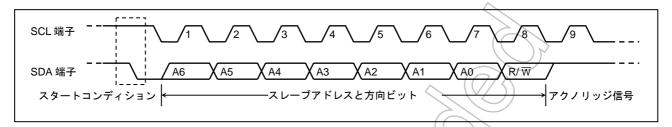

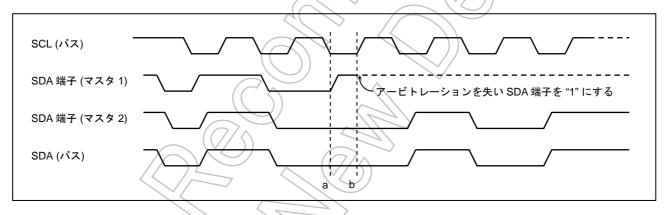

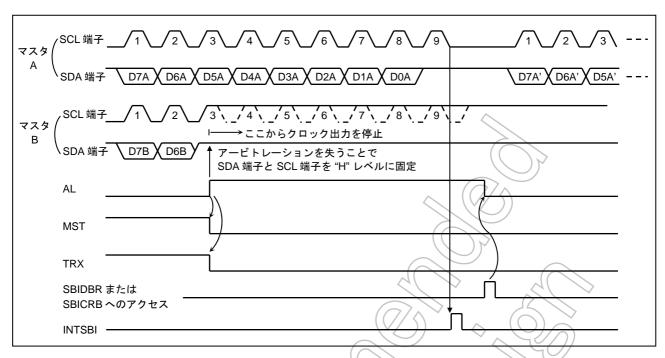

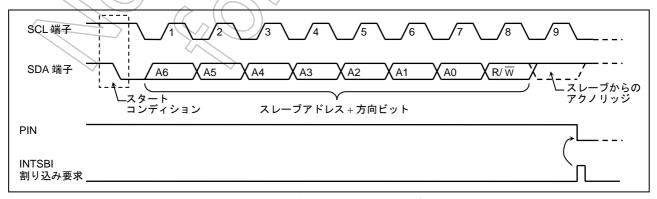

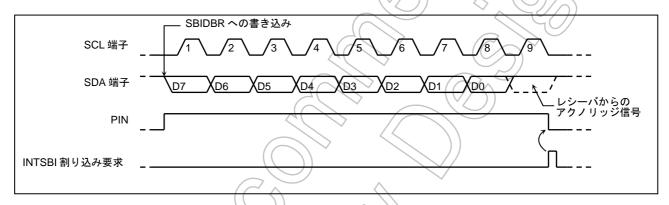

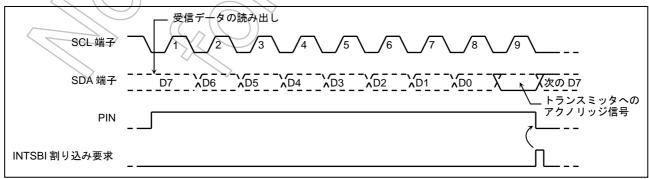

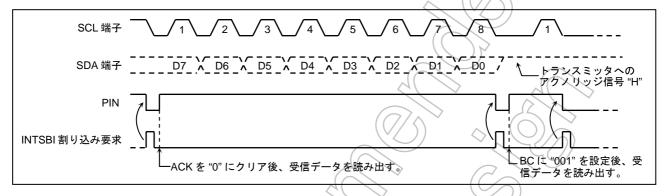

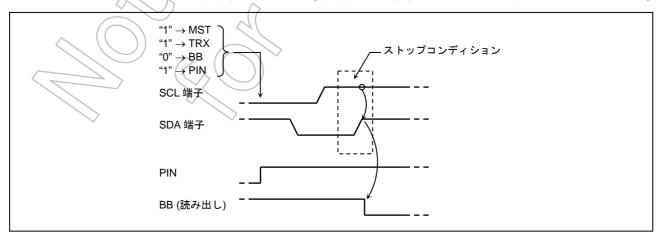

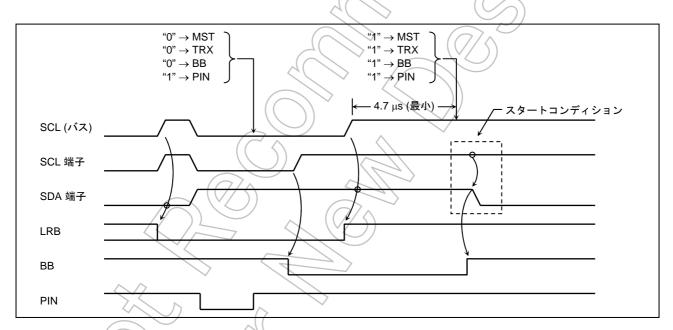

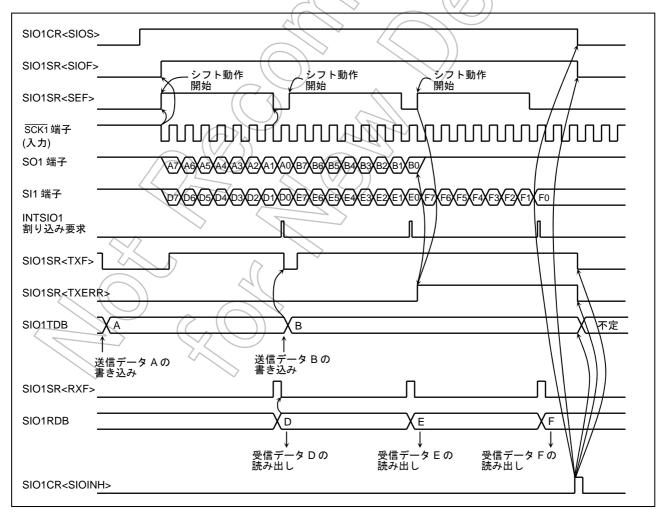

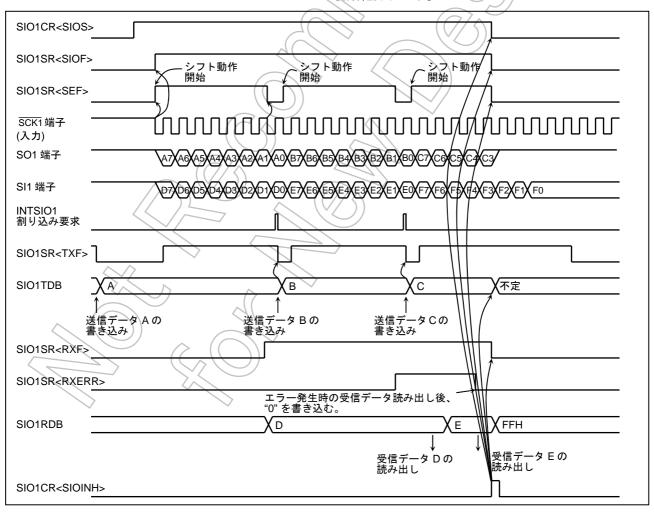

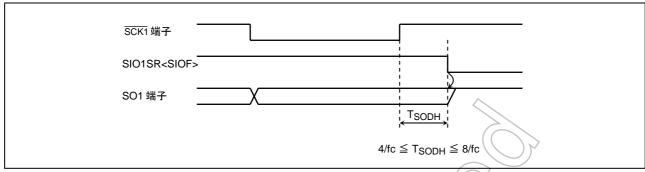

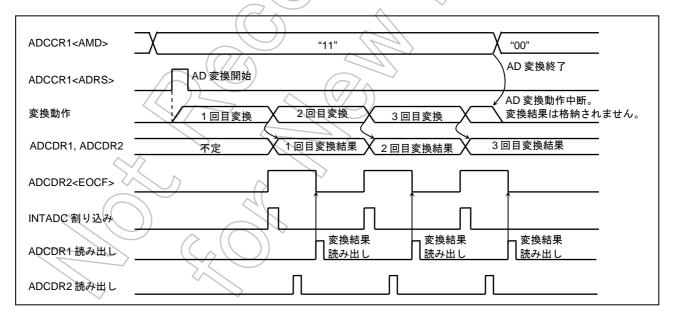

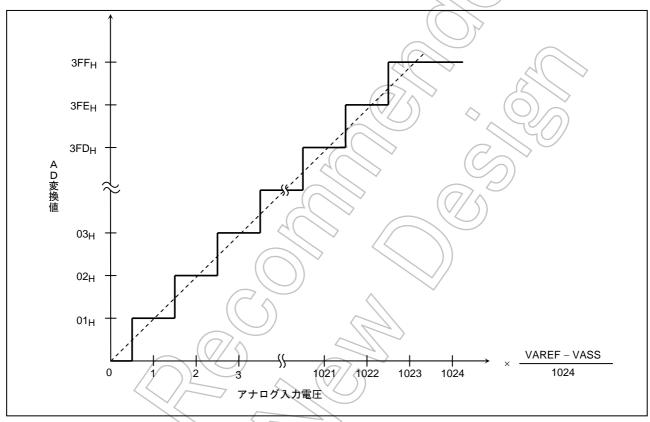

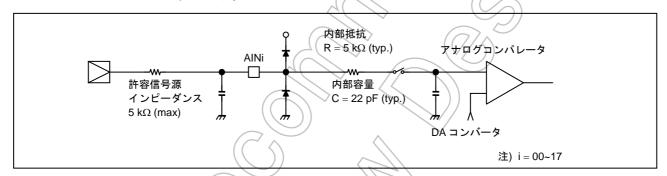

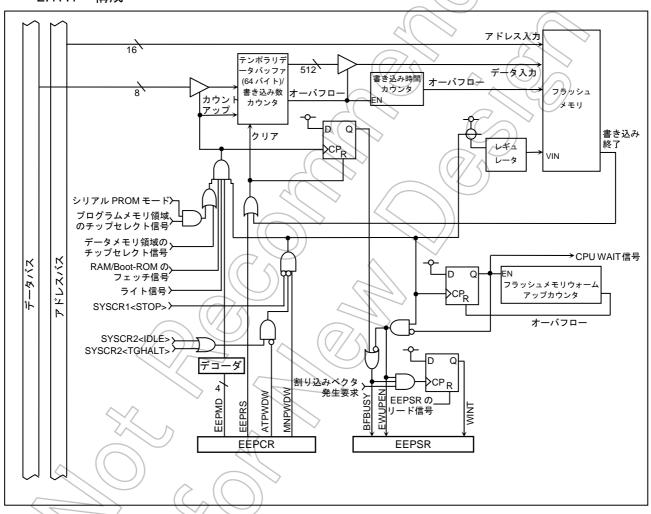

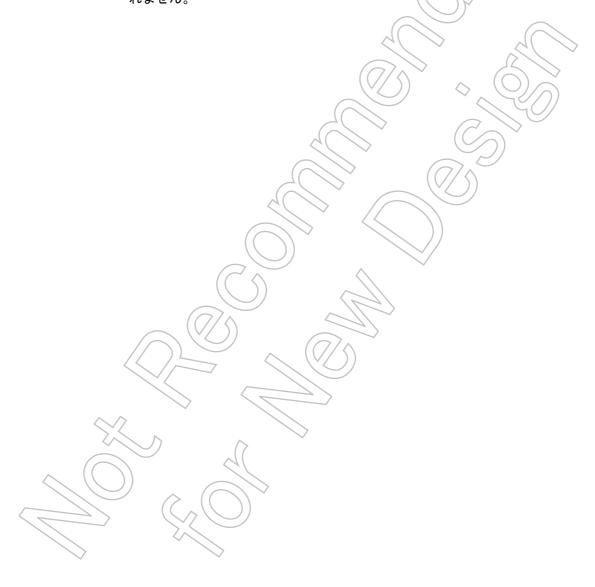

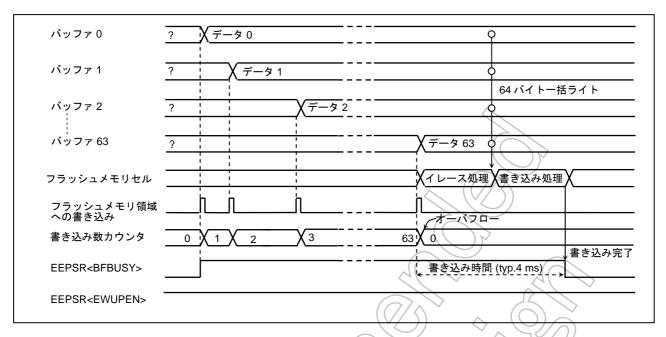

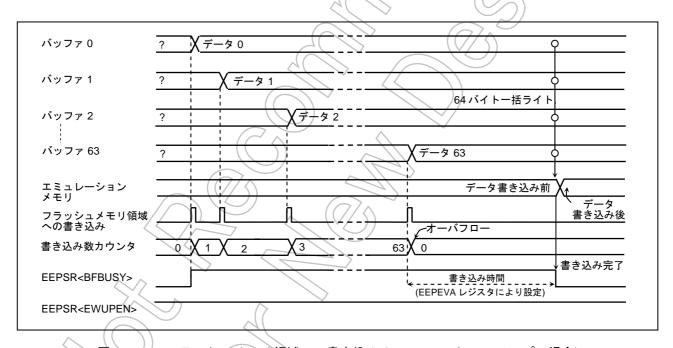

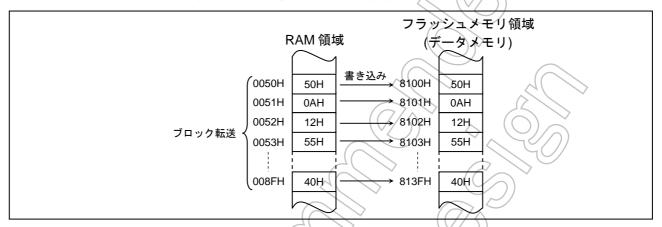

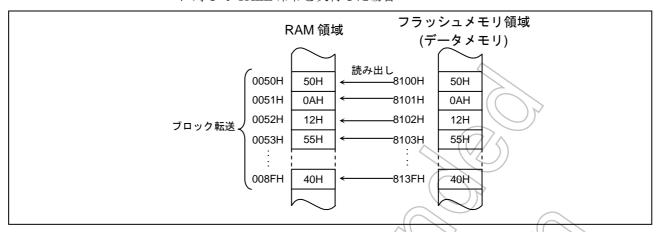

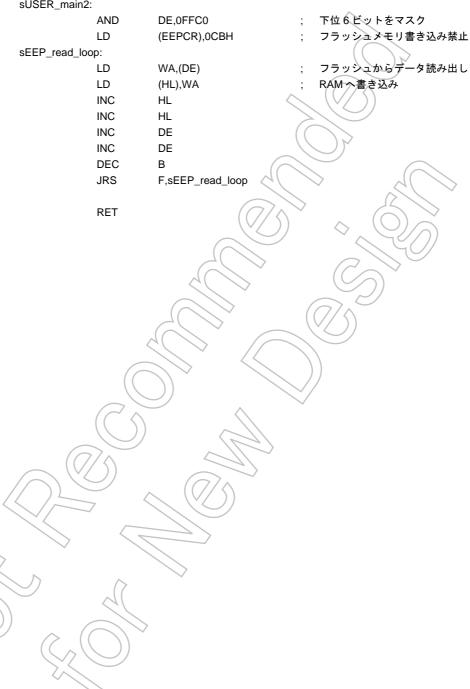

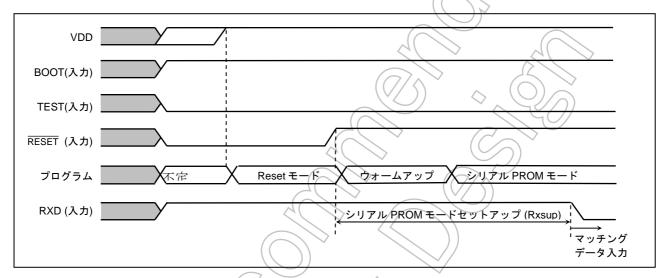

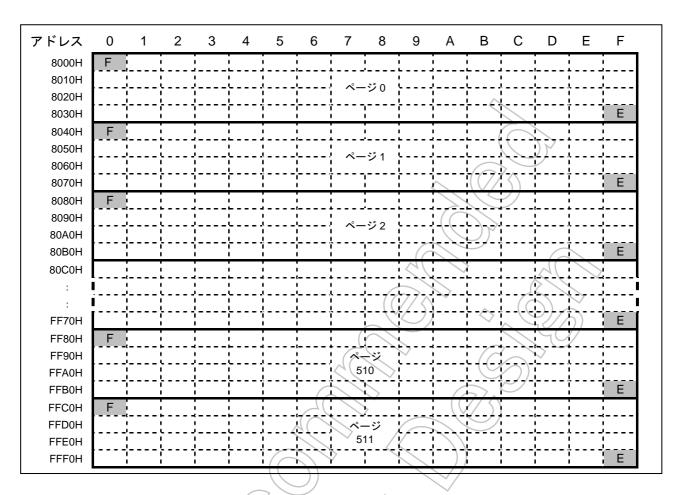

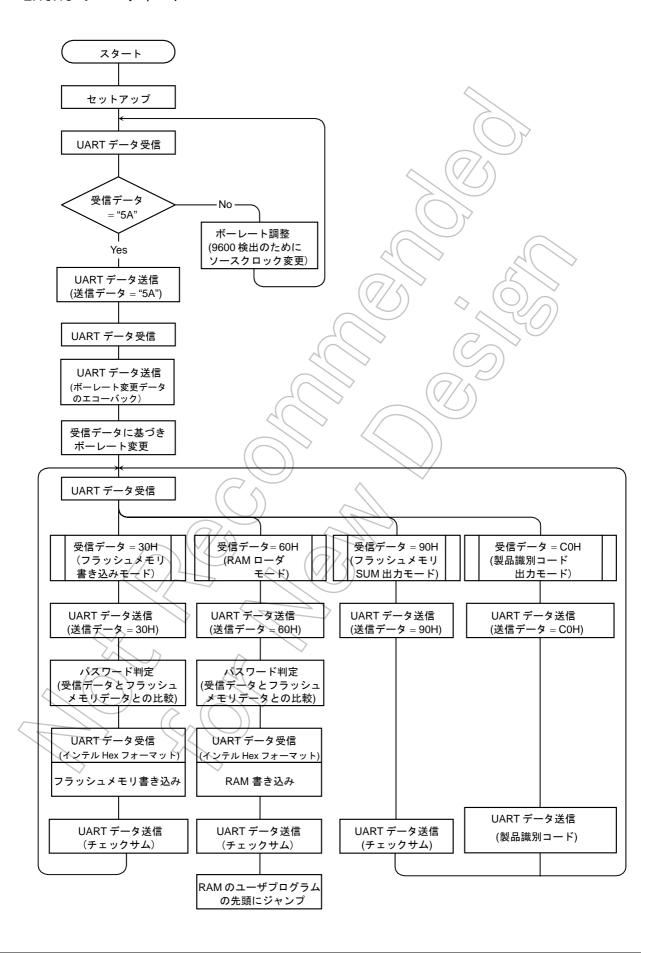

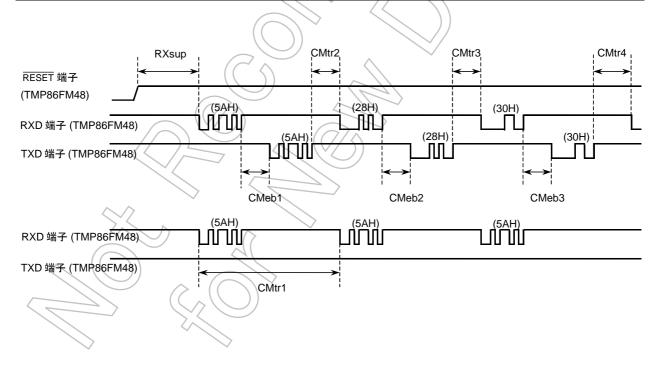

## 2.4.3 ウォッチドッグタイマ割り込み (INTWDT)