# <u>TB62781FNG / TB62D612FTG / TB62D786FTG / TB62D787FTG</u> <u>Usage considerations</u>

#### Summary

TB62781FNG and TB62D612FTG are constant current RGB-LED drivers using 2-wire BUS with a rating of 3.3 V to 5 V.

TB62D786FTG and TB62D787FTG are constant current RGB-LED drivers using a single-wire BUS with a rating of 5 V.

TB62781FNG and TB62D786FTG control three RGB-LEDs by 9 channel constant current outputs. TB62D612FTG and TB62D787FTG control eight RGB-LEDs by 24 channel constant current outputs. As for above products, 7-bit PWM control for each channel and configurations of 64 IDs are possible. TB62D786FTG and TB62D787FTG can operate with the main power supply (7 V to 28 V) by using the internal 5 V regulator.

## Contents

| Summary                                                                                                                     | 1    |

|-----------------------------------------------------------------------------------------------------------------------------|------|

| 1. Product Comparison (TB62781FNG, TB62D612FTG, TB62D786FTG, and TB62D787FTG)                                               | 7    |

| 1.1. Block diagram and application circuit examples                                                                         | 8    |

| 2. Power Supply Voltage                                                                                                     | .10  |

| 2.1. Operation range of power supply voltage                                                                                | . 10 |

| 2.2. Capacitor for power supply pin                                                                                         | . 10 |

| 2.3. 5 V regulator input (VL pin) and output (VLOUT pin)                                                                    | . 11 |

| 2.4. Power on reset circuit (POR)                                                                                           |      |

| 2.5. Setting of DATA input pin in power on and shutdown                                                                     | . 12 |

| 2.6. Rising period and falling period for input pins (tr / tf)                                                              | . 12 |

| 3. Output Current and Current Accuracy                                                                                      |      |

| 3.1. Absolute maximum ratings of output block                                                                               | . 13 |

| 3.2. Recommended range of output current                                                                                    |      |

| 3.2.1. Output current setting (TB62781FNG and TB62D612FTG)                                                                  |      |

| 3.2.2. Output current setting (TB62D786FTG and TB62D787FTG)                                                                 |      |

| 3.3. Heat dissipation by using an external resistor for outputs                                                             |      |

| 4. Specification of Communication for each Input                                                                            | .16  |

| 4.1. 2-wire input (TB62781FNG and TB62D612FTG)                                                                              | . 16 |

| 4.1.1. Basic specification of DATA input (2-wire input)                                                                     |      |

| 4.1.2. Input format (2-wire input)                                                                                          | .16  |

| 4.1.3. Start command (2-wire input)                                                                                         | .17  |

| 4.1.4. Period command (2-wire input)                                                                                        | .17  |

| 4.1.5. Slave address (2-wire input) (unique numbers of the IC set by ID0, ID1, and ID2 pins)                                | 18   |

| 4.1.6. Sub address (2-wire input) (Selecting LED output controlled for PWM DATA setting)                                    | 19   |

| 4.1.7. PWM DATA (2-wire input, 127 grayscales)                                                                              | 20   |

| 4.1.8. Packet input (2-wire input) (Data communication to two or more ICs)                                                  | 21   |

| 4.1.9. Errata: Errata make the next input format into non-reception state according to the end timing of SCLK transmission. | 22   |

| 4.1.10. Errata generation and their avoidance method (2-wire input)                                                         | 23   |

| 4.1.11. Detail description of errata (2-wire input)                                                                         |      |

| 4.2. Specification of communication: A single-wire input (TB62D786FTG and TB62D787FTG)                                      | .26  |

| 4.2.1. Basic specification of input DATA (Single-wire input)                                                                | 26   |

| 4.2.2. Input format (Single-wire input)                                                                                     | .28  |

| 4.2.3. Start command (Single-wire input)                                                                                    | .29  |

| 4.2.4. Period command (Single-wire input)                                                                                   | 29   |

| 4.2.5. Slave address (unique number of ICs set by ID0, ID1, and ID2 pins) (Single-wire input)                               | 30   |

| 4.2.6. Sub address (Single-wire input) (Selecting LED output controlled for PWM DATA setting)                               | 31   |

| 4.2.7. PWM DATA (Single-wire input)                                                                                         | .33  |

# TOSHIBA

#### TB62781FNG/TB62D612FTG/ TB62D786FTG/TB62D787FTG Application Note

| 4.2.8. Packet input (Single-wire input) (Data communication to two or more ICs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK transmission       35         4.2.10. Errata generation and their avoidance method (Single-wire input)       36         4.2.11. Detail description of errata (Single-wire input)       37         4.3. Method of generating the single-wire input signal (used for TB62D786FTG and TB62D787FTG) from the 2-wire input signal (used for TB62781FNG and TB62D612FTG)       39         5. Power Consumption and Heat Radiation Design       40         5.1. Power consumption       40         5.1.1. Power consumed by the constant current outputs: P(OUT)       40         5.2. Heat radiation design       40         5.3. Derating graphs       41         5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       41         5.3.2. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       42         5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43                        |

| 4.2.11. Detail description of errata (Single-wire input)       37         4.3. Method of generating the single-wire input signal (used for TB62D786FTG and TB62D787FTG) from the 2-wire input signal (used for TB62781FNG and TB62D612FTG)       39         5. Power Consumption and Heat Radiation Design       40         5.1. Power consumption       40         5.1.2. Power consumed by the constant current outputs: P(OUT)       40         5.2. Heat radiation design       40         5.3. Derating graphs       41         5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       41         5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       42         5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43                                                                                                                                                     |

| 4.3. Method of generating the single-wire input signal (used for TB62D786FTG and TB62D787FTG)<br>from the 2-wire input signal (used for TB62781FNG and TB62D612FTG)       39         5. Power Consumption and Heat Radiation Design       40         5.1. Power consumption       40         5.1.1. Power consumed by the constant current outputs: P(OUT)       40         5.1.2. Power consumed by the logic block and the 5 V regulator circuit       40         5.2. Heat radiation design       40         5.3. Derating graphs       41         5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and Vout(ON)=1.0 V, when mounted on a board.)       41         5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and Vout(ON)=1.0 V, when mounted on a board.)       42         5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and Vout(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and Vout(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and Vout(ON)=1.0 V, when mounted on a board.)       43 |

| from the 2-wire input signal (used for TB62781FNG and TB62D612FTG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.1. Power consumption       40         5.1.1. Power consumed by the constant current outputs: P(OUT)       40         5.1.2. Power consumed by the logic block and the 5 V regulator circuit       40         5.2. Heat radiation design       40         5.3. Derating graphs       41         5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       41         5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       42         5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       44                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.1.1. Power consumed by the constant current outputs: P(OUT)       40         5.1.2. Power consumed by the logic block and the 5 V regulator circuit       40         5.2. Heat radiation design       40         5.3. Derating graphs       41         5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       41         5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       42         5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.1.2. Power consumed by the logic block and the 5 V regulator circuit       40         5.2. Heat radiation design       40         5.3. Derating graphs       41         5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       41         5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       42         5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.2. Heat radiation design       40         5.3. Derating graphs       41         5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       41         5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       41         5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       42         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.3. Derating graphs       41         5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       41         5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       42         5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       43         5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and VouT(ON)=1.0 V, when mounted on a board.)       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>5.3.1. Derating graph and power dissipation of TB62781FNG (Vcc=5 V and V<sub>OUT(ON)</sub>=1.0 V, when mounted on a board.)</li> <li>5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and V<sub>OUT(ON)</sub>=1.0 V, when mounted on a board.)</li> <li>5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and V<sub>OUT(ON)</sub>=1.0 V, when mounted on a board.)</li> <li>5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and V<sub>OUT(ON)</sub>=1.0 V, when mounted on a board.)</li> <li>43</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul> <li>mounted on a board.)</li> <li>5.3.2. Derating graph and power dissipation of TB62D612FTG (Vcc=5 V and V<sub>OUT(ON)</sub>=1.0 V, when mounted on a board.)</li> <li>5.3.3. Derating graph and power dissipation of TB62D786FTG (Vcc=5 V and V<sub>OUT(ON)</sub>=1.0 V, when mounted on a board.)</li> <li>5.3.4. Derating graph and power dissipation of TB62D787FTG (Vcc=5 V and V<sub>OUT(ON)</sub>=1.0 V, when mounted on a board.)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| mounted on a board.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| mounted on a board.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| mounted on a board.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

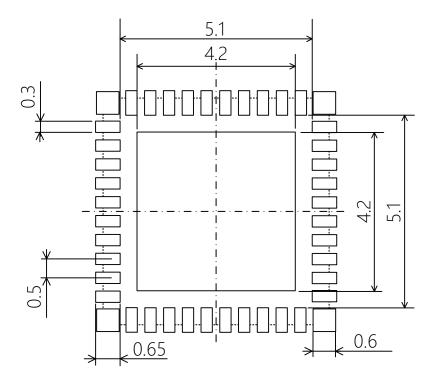

| 6. Foot Pattern (for reference only)45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

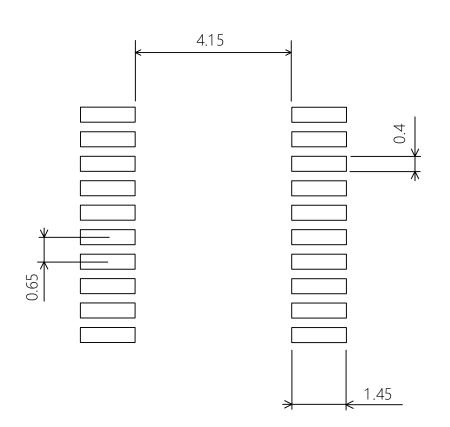

| 6.1. Foot pattern of TB62781FNG (for reference only)45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

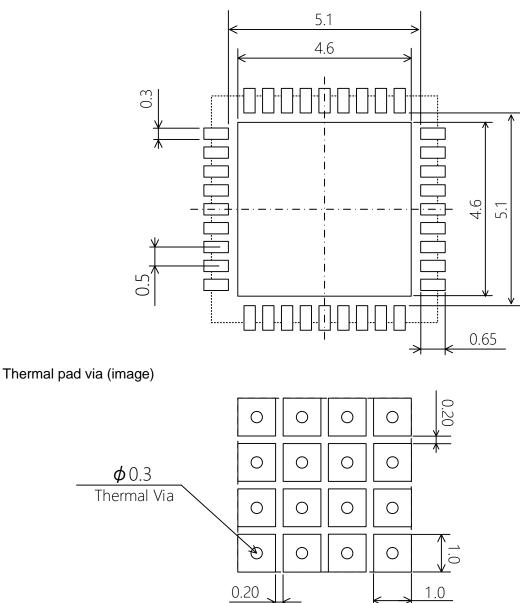

| 6.2. Foot pattern of TB62D612FTG (for reference only)46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

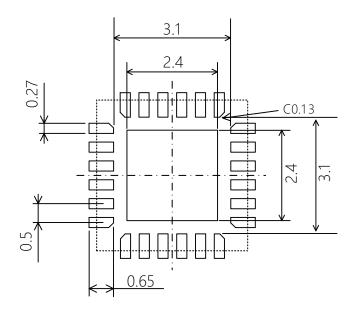

| 6.3. Foot pattern of TB62D786FTG (for reference only)47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

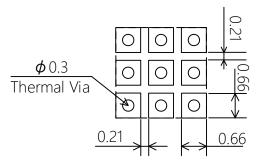

| 6.4. Foot pattern of TB62D787FTG (for reference only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Notes on Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IC Usage Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Notes on handling of ICs Notes on handling of ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Points to remember on handling of ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RESTRICTIONS ON PRODUCT USE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## **Table Contents**

| Table 1-1 Product comparison                                                    | 7  |

|---------------------------------------------------------------------------------|----|

| Table 2-1 Operation range of power supply voltage (TB62781FNG and TB62D612FTG)  | 10 |

| Table 2-2 Operation range of power supply voltage (TB62D786FTG and TB62D787FTG) | 10 |

| Table 2-3 Recommendation values (capacitor for power supply pin)                | 10 |

| Table 2-4 Data input pin                                                        | 12 |

| Table 3-1 Absolute maximum ratings of output block                              | 13 |

| Table 3-2 Output characteristics (TB62781FNG and TB62D612FTG)                   | 13 |

| Table 3-3 Output characteristics (TB62D786FTG and TB62D787FTG)                  | 14 |

| Table 4-1 Input timing (2-wire input)                                           | 16 |

| Table 4-2 Slave address (2-wire input) excerpted from the technical DATA        | 18 |

| Table 4-3 Sub address (2-wire input) excerpted from the technical DATA          | 19 |

| Table 4-4 PWM DATA (2-wire input) excerpted from the technical DATA             | 20 |

| Table 4-5 Input timing (Single-wire input)                                      | 27 |

| Table 4-6 Slave address (Single-wire input) excerpted from the technical DATA   | 30 |

| Table 4-7 Sub address (Single-wire input) excerpted from the technical DATA     | 32 |

| Table 4-8 PWM DATA (Single-wire input) excerpted from the technical DATA        | 33 |

## **Figure Contents**

| Figure 1.1            | Application circuit example (TB62781FNG)                                                                                    | . 8        |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 1.2            | Application circuit example (TB62D612FTG)                                                                                   | . 8        |

| Figure 1.3            | Application circuit example (TB62D786FTG)                                                                                   | . 9        |

| Figure 1.4            | Application circuit example (TB62D787FTG)                                                                                   | . 9        |

| Figure 2-1            | Connection of power supply                                                                                                  | 10         |

| Figure 2-2            | VL pin voltage and VLOUT pin voltage (TB62D786FTG and TB62D787FTG)                                                          | 11         |

| Figure 2-3            | Power on reset circuit (POR)                                                                                                | 11         |

| Figure 2-4            | Equivalent circuits (input)                                                                                                 | 12         |

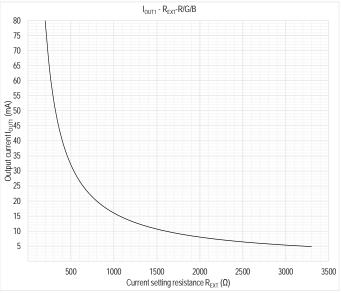

| Figure 3-1            | Relation of $I_{\text{OUT1}}$ and $R_{\text{EXT}}$ (TB62781FNG and TB62D612FTG)                                             | 13         |

| Figure 3-2            | Relation of $I_{\text{OUT1}}$ and $R_{\text{EXT}}$ (TB62D786FTG and TB62D787FTG)                                            | 14         |

| Figure 3-3            | Connection of external resistor (RR) example (in case of TB62D786FTG or TB62D787FTG).                                       | 15         |

| Figure 4-1            | Data input (2-wire input)                                                                                                   | 16         |

| Figure 4-2            | Basic format (2-wire input)                                                                                                 | 16         |

| Figure 4-3            | Start command (2-wire input)                                                                                                | 17         |

| Figure 4-4            | Period command (2-wire input)                                                                                               | 17         |

| Figure 4-5            | Period command (2-wire input) (Example 1)                                                                                   | 17         |

| Figure 4-6            | Period command (2-wire input) (Example 2)                                                                                   | 17         |

| Figure 4-7            | Slave address (2-wire input)                                                                                                | 18         |

| Figure 4-8            | Sub address (2-wire input)                                                                                                  | 19         |

| Figure 4-9            | PWM DATA (2-wire input)                                                                                                     | 20         |

| Figure 4-1<br>differe | 0 Image of packet communication to the IC with the same slave address when using two ICs ent slave addresses (2-wire input) | with<br>21 |

| Figure 4-1            | 1 Update and reception reset timing of PWM DATA after the period command (2-wire input)                                     | 22         |

| Figure 4-1            | 2 Timing of SCLK transmission when errata occur (2-wire input)                                                              | 22         |

| Figure 4-1            | 3 Errata generation by start command error                                                                                  | 23         |

| Figure 4-1            | 4 Errata avoidance method (1): Adding one SCLK (2-wire input) (Example)                                                     | 23         |

| -                     | 5 Errata avoidance method (2): Adding 8 SCLK (1 byte dummy DATA) (2-wire input) (Exam                                       | • •        |

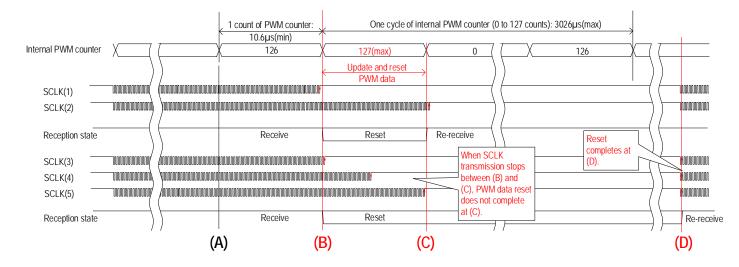

| Figure 4-1            | 6 Relation of SCLK and PWM counter: 127th PWM counter timing comes earlier (2-wire input)                                   | 24         |

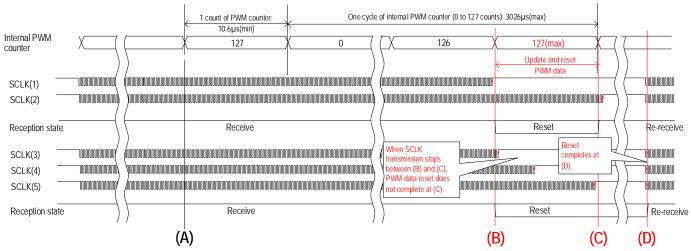

| Figure 4-1            | 7 Relation of SCLK and PWM counter: 127 <sup>th</sup> PWM counter timing comes later (2-wire input)                         | 24         |

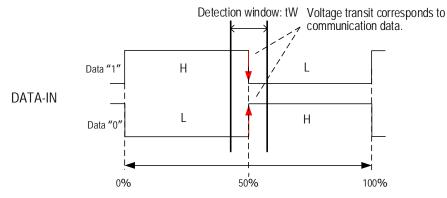

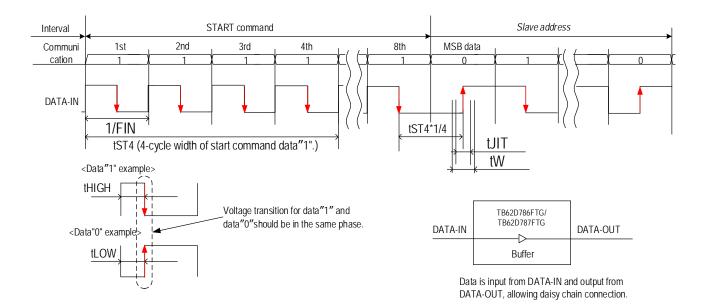

| Figure 4-1            | 8 Input DATA (Single-wire input)                                                                                            | 26         |

| Figure 4-1            | 9 Communication timing (Single-wire input)                                                                                  | 27         |

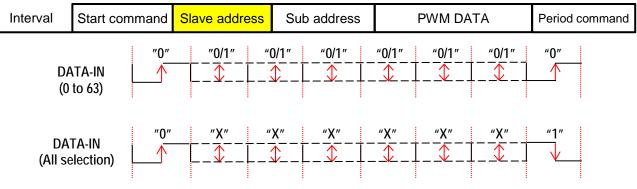

| Figure 4-2            | 0 Basic format (Single-wire input)                                                                                          | 28         |

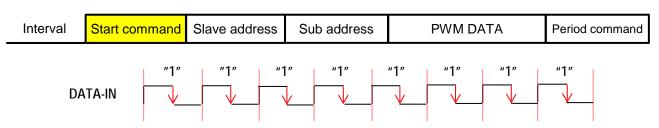

| Figure 4-2            | 1 Start command (Single-wire input)                                                                                         | 29         |

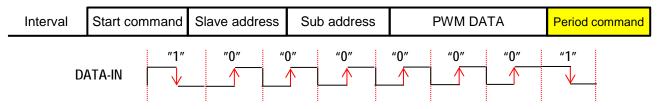

| Figure 4-2            | 2 Period command (Single-wire input)                                                                                        | 29         |

| Figure 4-2            | 3 Slave address (Single-wire input)                                                                                         | 30         |

| Figure 4-2            | 4 Sub address (Single-wire input)                                                                                           | 31         |

| Figure 4-2            | 5 PWM DATA (Single-wire input, 127 grayscales)                                                                              | 33         |

# TOSHIBA

| Figure 4-26 Image of packet communication to the IC with the same slave address when using two ICs different slave addresses (Single-wire input) |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 4-27 Update and reception reset timing of PWM DATA after the period command (after demodula                                               |      |

| Figure 4-28 Timing of SCLK transmission when errata occur (after demodulated)                                                                    | . 35 |

| Figure 4-29 Errata generation by start command error (after demodulated)                                                                         | . 36 |

| Figure 4-30 Errata avoidance method (1): Adding one data"1". (Single-wire input) (Example)                                                       | . 36 |

| Figure 4-31 Errata avoidance method (2): Adding 4 data "1" (Single-wire input) (Example)                                                         | . 36 |

| Figure 4-32 Relation of DATA-IN and PWM counter: 127 <sup>th</sup> PWM counter timing comes earlier (Single-<br>input)                           |      |

| Figure 4-33 Relation of DATA-IN and PWM counter: 127 <sup>th</sup> PWM counter timing comes later (Single-<br>input)                             |      |

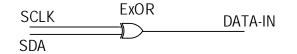

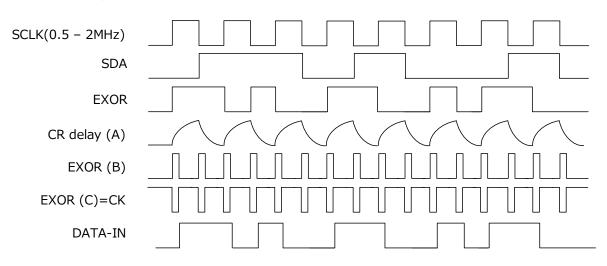

| Figure 4-34 Logic description of SCLK and SDA, and DATA-IN                                                                                       | . 39 |

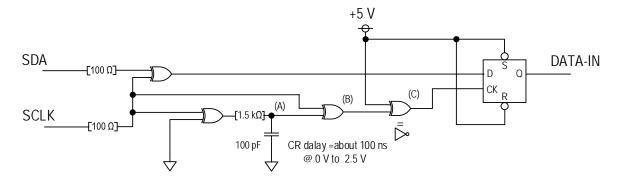

| Figure 4-35 Conversion circuit (from SCLK and SDA to DATA-IN)                                                                                    | . 39 |

| Figure 4-36 Timing charts of the conversion circuit                                                                                              | . 39 |

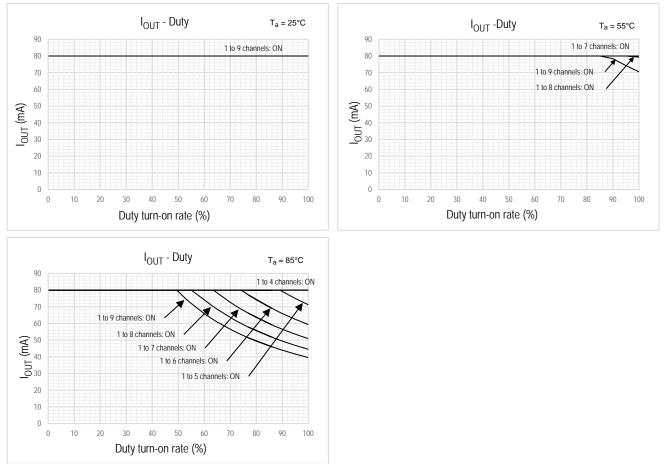

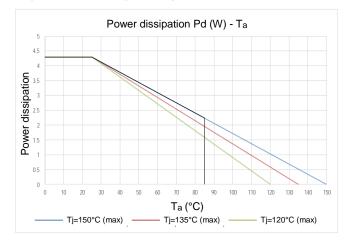

| Figure 5-1 Derating graph (Tj=135°C, T <sub>a</sub> =25°C, 55°C, or 85°C, and V <sub>OUT(ON)</sub> =1.0 V) (for reference only)                  | ) 41 |

| Figure 5-2 Power dissipation when maximum of Tj is 120°C, 135°C, or 150°C                                                                        | . 41 |

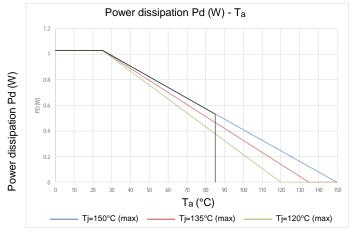

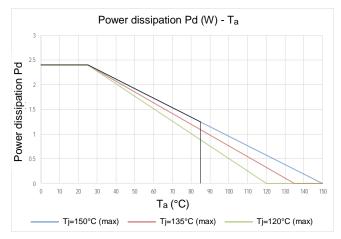

| Figure 5-3 Derating graph (Tj=135°C, T <sub>a</sub> =25°C, 55°C, or 85°C, and V <sub>OUT(ON)</sub> =1.0 V)                                       | . 42 |

| Figure 5-4 Power dissipation when maximum of Tj is 120°C, 135°C, or 150°C                                                                        | . 42 |

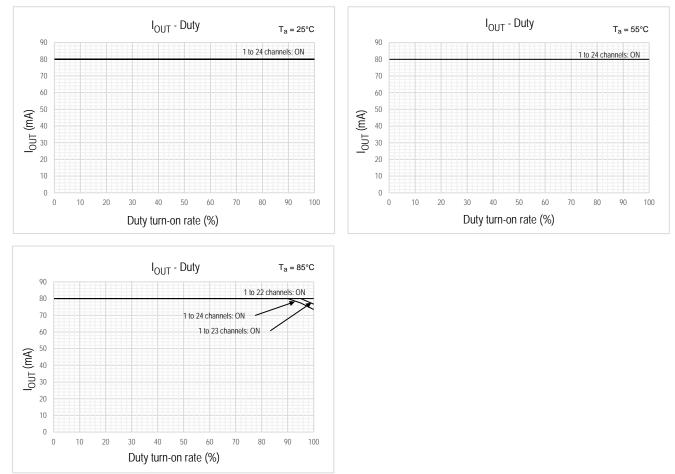

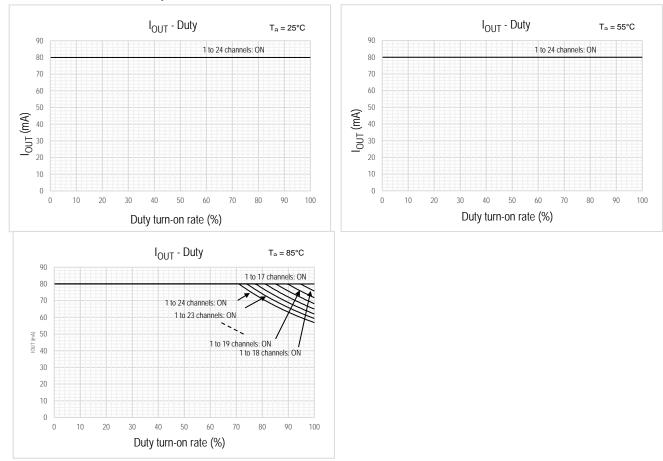

| Figure 5-5 Derating graph (Tj=135°C, T <sub>a</sub> =25°C, 55°C, or 85°C, and V <sub>OUT(ON)</sub> =1.0 V) (for reference only)                  | ) 43 |

| Figure 5-6 Power dissipation when maximum of Tj is 120°C, 135°C, or 150°C                                                                        | . 43 |

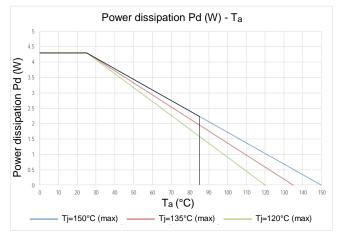

| Figure 5-7 Derating graph (Tj=135°C, T <sub>a</sub> =25°C, 55°C, or 85°C, and $V_{OUT(ON)}$ =1.0 V)                                              | . 44 |

| Figure 5-8 Power dissipation when maximum of Tj is 120°C, 135°C, or 150°C                                                                        | . 44 |

## 1. Product Comparison (TB62781FNG, TB62D612FTG, TB62D786FTG, and TB62D787FTG)

Main specification of each product is shown in the table 1-1.

| Item                               | TB62781FNG     | TB62D612FTG    | TB62D786FTG     | TB62D787FTG     |

|------------------------------------|----------------|----------------|-----------------|-----------------|

| Process                            | BiCD0.6        | BiCD0.13       | BiCD0.13        | BiCD0.13        |

| Interface                          | 2-wire SPI BUS | 2-wire SPI BUS | Single-wire BUS | Single-wire BUS |

| Linear regulator supply<br>voltage | —              | —              | 7.0 to 28 V     | 7.0 to 28 V     |

| Vcc supply voltage                 | 3.0 to 5.5 V   | 3.0 to 5.5 V   | 4.5 to 5.5 V    | 4.5 to 5.5 V    |

| LED anode supply voltage           | 28 V           | 28 V           | 28 V            | 28 V            |

| Recommend output current           | 5 to 40 mA     | 5 to 40 mA     | 5 to 40 mA      | 5 to 40 mA      |

| Number of channels                 | 9 channels     | 24 channels    | 9 channels      | 24 channels     |

| PWM control range                  | 7 bits         | 7 bits         | 7 bits          | 7 bits          |

| Number of IDs<br>(Slave address)   | 0 to 63        | 0 to 63        | 0 to 63         | 0 to 63         |

| Package                            | 20-pin SSOP    | 36-pin WQFN    | 24-pin VQFN     | 40-pin VQFN     |

#### Table 1-1 Product comparison

## 1.1. Block diagram and application circuit examples

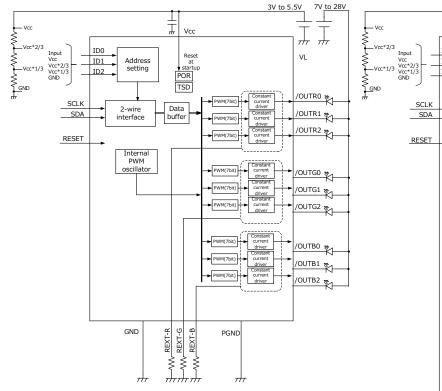

Constant current LED drivers with 9 channels or 24 channels controlled by 2-wire inputs (TB62781FNG / TB62D612FTG)

Figure 1.1 Application circuit example (TB62781FNG)

Figure 1.2 Application circuit example (TB62D612FTG)

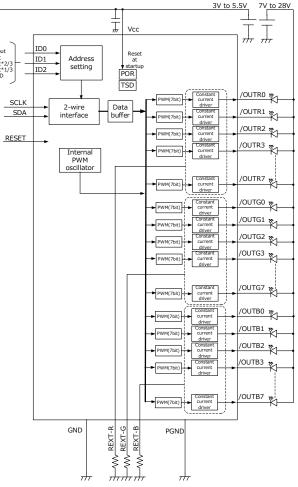

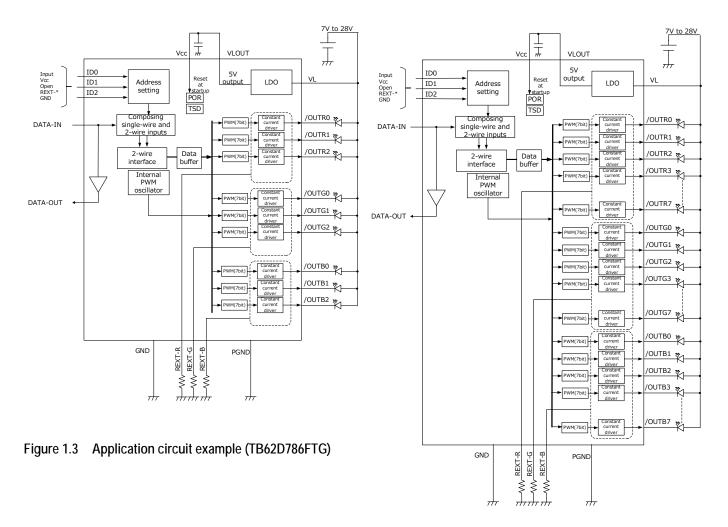

# Constant current LED drivers with 9 channels or 24 channels controlled by single-wire inputs (TB62D786FTG / TB62D787FTG)

Figure 1.4 Application circuit example (TB62D787FTG)

## 2. Power Supply Voltage

#### 2.1. Operation range of power supply voltage

#### Table 2-1 Operation range of power supply voltage (TB62781FNG and TB62D612FTG)

| Item           | Symbol | Operation<br>range | Absolute<br>maximum<br>ratings | Unit | Note    |

|----------------|--------|--------------------|--------------------------------|------|---------|

| Supply voltage | Vcc    | 3.0 to 5.5         | 6.0                            | V    | Vcc pin |

#### Table 2-2 Operation range of power supply voltage (TB62D786FTG and TB62D787FTG)

| Item                   | Symbol | Operation<br>range | Absolute<br>maximum<br>ratings | Unit | Note                            |

|------------------------|--------|--------------------|--------------------------------|------|---------------------------------|

| VL pin supply voltage  | VL     | 7.0 to 28          | 29                             | V    | VL pin<br>VLOUT pin outputs 5 V |

| Vcc pin supply voltage | Vcc    | 4.5 to 5.5         | 6.0                            | V    | Vcc pin<br>Connect to VLOUT pin |

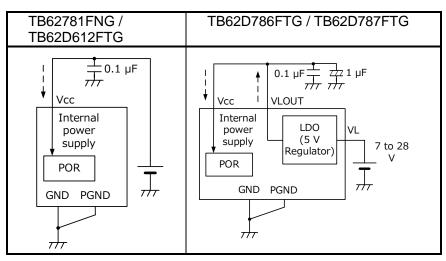

Connection of power supply:

TB62D786FTG and TB62D787FTG has a 5 V regulator (VL pin is for input and VLOUT pin is for output.) VL pin can be used as a main power supply by connecting VLOUT pin and Vcc pin.

Figure 2-1 Connection of power supply

## 2.2. Capacitor for power supply pin

Connect the capacitor as close as possible to the IC.

#### Table 2-3 Recommendation values (capacitor for power supply pin)

| Item                       | Recommendation value | Remarks                |

|----------------------------|----------------------|------------------------|

| Between Vcc pin<br>and GND | ≥ 0.1 µF             | Ceramic capacitor      |

| Between VLOUT              | ≥ 0.1 µF             | Ceramic capacitor      |

| pin and GND                | ≥1 µF                | Electrolytic capacitor |

#### 2.3. 5 V regulator input (VL pin) and output (VLOUT pin)

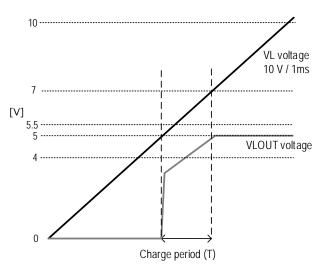

The internal 5 V regulator of TB62D786FTG and TB62D787FTG outputs voltage from VLOUT pin when VL pin voltage exceeds 5 V. Then, the voltage becomes stable when VL pin voltage is 7 V or more. The charge time (T) for the capacitor (1.0  $\mu$ F) between VLOUT pin and GND is approximately 0.5 ms.

Figure 2-2 VL pin voltage and VLOUT pin voltage (TB62D786FTG and TB62D787FTG)

#### 2.4. Power on reset circuit (POR)

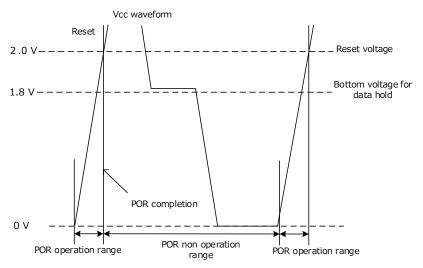

Power on reset function (POR) monitors Vcc pin, and reset at startup.

Start DATA input after Vcc voltage reaches the operation threshold. The same procedure should be taken when connecting VLOUT pin and Vcc pin.

Figure 2-3 Power on reset circuit (POR)

#### 2.5. Setting of DATA input pin in power on and shutdown

Data input setting in Vcc power on is shown in the table 2-4.

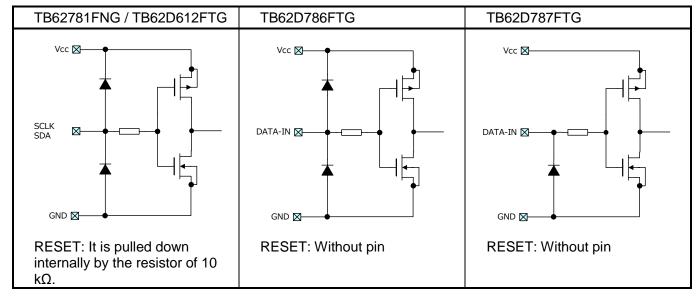

In case of TB62781FNG, TB62D612FTG, or TB62D786FTG that has the protection diode between the DATA input pin and Vcc pin, the low level is set in power on and then DATA input starts after Vcc voltage reaches the operation threshold (Shown in the figure 2-4).

Shutdown the power after the data input pin is set to low level.

TB62D787FTG has the tolerance input.

#### Table 2-4 Data input pin

| Communication<br>voltage system | Power supply<br>input                  | Data input<br>pin                                    |

|---------------------------------|----------------------------------------|------------------------------------------------------|

| 3.3 V to 5 V<br>CMOS            | Low                                    | SDA, SCLK                                            |

| 5 V CMOS                        | Low / High                             | DATA-IN                                              |

|                                 | voltage system<br>3.3 V to 5 V<br>CMOS | voltage system     input       3.3 V to 5 V     CMOS |

Note: Low: 0.3×Vcc, High: 0.7×Vcc

#### Figure 2-4 Equivalent circuits (input)

#### 2.6. Rising period and falling period for input pins (tr / tf)

Input pins have the hysteresis of 0.2 V to 0.4 V. When the voltage ripple of the input waveform is less than 0.2 V, tr and tf can be dulled by using the low pass filter, etc.

Values in the below table are experience ones for your reference.

Table 2.5tr and tf for input pins

| Item           | Symbol | Pin name              | Max | Unit |

|----------------|--------|-----------------------|-----|------|

| Rising period  | tr_max | SCLK, SDA,<br>DATA-IN | 500 | ns   |

| Falling period | tf_max | SCLK, SDA,<br>DATA-IN | 500 | ns   |

Be sure to confirm that there is no problem in controlling LEDs.

## 3. Output Current and Current Accuracy

#### 3.1. Absolute maximum ratings of output block

Since the absolute maximum rating must not be exceeded instantaneously, set the output current up to 80 mA in considering the current accuracy. Also, the output voltage should not exceed 29 V in considering the ripple of the LED power supply.

| Item           | Symbol | Absolute maximum<br>ratings | Unit | Note            |

|----------------|--------|-----------------------------|------|-----------------|

| Output current | Ιουτ   | 85                          | mA   | Per one channel |

| Output voltage | Vout   | -0.3 to 29                  | V    | —               |

#### Table 3-1 Absolute maximum ratings of output block

#### 3.2. Recommended range of output current

Output current of 5 mA to 40 mA per one channel is recommended.

The constant current characteristics are guaranteed when the output voltage during ON (VOUT(ON)) is as follows; TB62781FNG / TB62D612FTG: 0.4 V to 4.0 V, TB62D786FTG / TB62D787FTG: 0.5 V to 4.0 V Note that the output losses are large when the output voltage is very high.

#### 3.2.1. Output current setting (TB62781FNG and TB62D612FTG)

#### Table 3-2 Output characteristics (TB62781FNG and TB62D612FTG)

| Item                                     | Symbol   | Test conditions                                                | Min   | Тур. | Max   | Unit |

|------------------------------------------|----------|----------------------------------------------------------------|-------|------|-------|------|

| Output current                           | IOUT1    | V <sub>OUT(ON)</sub> =0.4 V, R <sub>EXT</sub> =1.2 kΩ, Vcc=5 V | 12.69 | 13.5 | 14.31 | mA   |

| Output current accuracy between channels | ΔΙΟυτ2   | Vouτ(on)=0.4 V, Rext=1.2 kΩ, All channels ON,<br>Vcc=5 V       | _     | _    | ±3.0  | %    |

| Output voltage                           | VOUT(ON) | All outputs                                                    | 0.4   |      | 4     | V    |

Figure 3-1 Relation of IOUT1 and REXT (TB62781FNG and TB62D612FTG)

Approximate equation: Output current (mA) =  $14.5 \times 1.12$ (V)/REXT ( $\Omega$ )

Above graph is only for reference that has a constant current error of REXT and output current between ICs and between channels.

Pin voltage of Rext-R/G/B is 1.12 V(typ.), and the power consumption of the resistor is as follows; V<sup>2</sup>/R=1.12×1.12/1.2 kΩ=1.04 mW

#### 3.2.2. Output current setting (TB62D786FTG and TB62D787FTG)

#### Table 3-3 Output characteristics (TB62D786FTG and TB62D787FTG)

| Item                                     | Symbol   | Test conditions                                          | Min  | Тур. | Max  | Unit |

|------------------------------------------|----------|----------------------------------------------------------|------|------|------|------|

| Output current                           | IOUT1    | Vout(on)=0.5 V, Rext=1.2 kΩ, Vcc=5 V                     | 12.5 | 13.3 | 14.1 | mA   |

| Output current accuracy between channels | ΔΙΟυτ2   | Vouτ(on)=0.5 V, Rext=1.2 kΩ, All channels ON,<br>Vcc=5 V | —    | _    | ±3.0 | %    |

| Output voltage                           | Vout(on) | All outputs                                              | 0.5  | _    | 4    | V    |

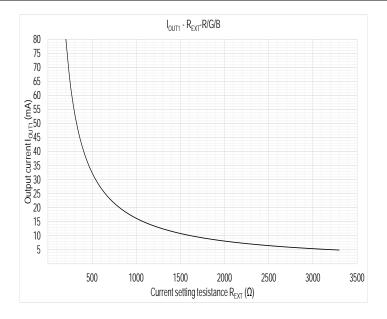

Figure 3-2 Relation of IOUT1 and REXT (TB62D786FTG and TB62D787FTG)

Approximate equation: Output current (mA) =  $14.18 \times 1.128(V)/REXT(\Omega)$

Above graph is only for reference that has a constant current error of REXT and output current between ICs and between channels.

Pin voltage of Rext-R/G/B is 1.128 V(typ.), and the power consumption of the resistor is as follows;

$V^{2}/R=1.128\times1.128/1.2 \text{ k}\Omega=1.06 \text{ mW}$

#### 3.3. Heat dissipation by using an external resistor for outputs

When the output voltage during ON exceeds 0.4 V (TB62781FNG or TB62D612FTG) or 0.5 V (TB62D786FTG or TB62D787FTG), each output generates heat due to its loss.

In the case 9 channels (TB62781FNG or TB62D786FTG) or 24 channels (TB62D612FTG or TB62D787FTG) are turned on simultaneously, the output loss is concentrated on the IC and so the output current should be limited. To solve this problem, connect the resistor externally to the outputs to reduce the power consumption. (Shown in the figure 3-3)

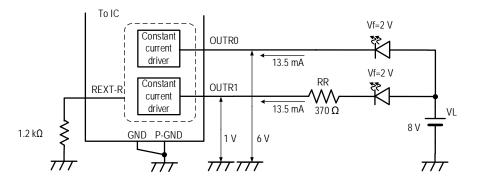

#### Figure 3-3 Connection of external resistor (RR) example (in case of TB62D786FTG or TB62D787FTG)

The figure 3-3 shows the case of OUTR0 and OUTR1 that illuminate red LEDs. OUTR0 pin consumes 81 mW that is the product of 6 V (output voltage during ON) and 13.5 mA (LED current).

Pw(OUTR0)≈(VL-Vf)×LED current=(8-2)×13.5 mA=81 mW

OUTR1 consumes 13.5 mW that is the product of 1 V (Note) (output voltage during ON) and 13.5 mA (LED current).

Note: Output voltage during ON is 1 V due to 5 V voltage drop at the external resistor (RR).

Pw(OUTR1)≈(VL-Vf-voltage drop)×LED current=(8-2-5)×13.5 mA=13.5 mW

Select the appropriate resistor (RR) that reduces voltage of 5 V when LED current is 13.5 mA.

$RR = 5 V / 13.5 mA = 370 \Omega$

This resistor (RR) is not necessary to be connected, but recommended to use according to the usage conditions in order to suppress heat concentration on the IC.

#### In case of TB62D786FTG and TB62D787FTG

They are single-wire input type and VL pin is used as a main power supply. So, note that the internal 5 V regulator, which is connected between VL pin and VLOUT pin, also generates the loss.

## 4. Specification of Communication for each Input

#### 4.1. 2-wire input (TB62781FNG and TB62D612FTG)

Specification of communication for 2-wire input type (TB62781FNG and TB62D612FTG) is described in this section.

#### 4.1.1. Basic specification of DATA input (2-wire input)

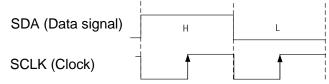

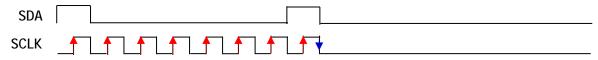

Basic unit is shown in the figure 4-1. "0" or "1" of SDA (DATA signal) is received at the rising edge of SCLK (clock).

SCLK clock frequency is up to 10 MHz. The frequency can be lower because of the clock synchronization type.

Each input timing is shown in the table 4-1.

Figure 4-1 Data input (2-wire input)

#### Table 4-1 Input timing (2-wire input)

| Item                      | Symbol  | Test conditions                          | Min | Тур. | Max | Unit |

|---------------------------|---------|------------------------------------------|-----|------|-----|------|

| SCLK clock frequency      | fCLK    | SCLK                                     | _   | —    | 10  | MHz  |

| Data setup time           | tSU;DAT | SDA-SCLK                                 | 10  | —    | _   |      |

| Data hold time            | tHD;DAT | SCLK-SDA                                 | 10  | —    | _   |      |

| "L" period of SCLK clocks | tLOW    | Pulse width of SCLK during low<br>level  | 50  | _    | —   | ns   |

| "H" period of SCLK clocks | tHIGH   | Pulse width of SCLK during high<br>level | 50  | _    | _   |      |

#### 4.1.2. Input format (2-wire input)

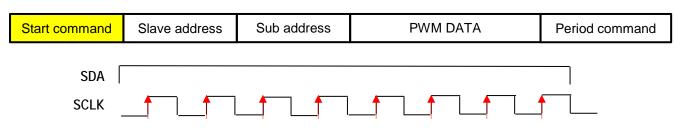

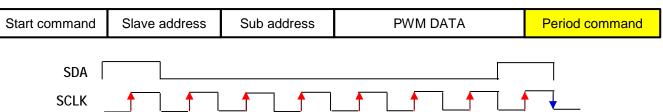

Input format for a single IC is shown in the figure 4-2.

Data is input to the input format in the order of the start command, the slave address, the sub address, the PWM DATA, and the period command with MSB first.

|               |               | <ul> <li>Input format</li> </ul> |                                          | >              |

|---------------|---------------|----------------------------------|------------------------------------------|----------------|

| Start command | Slave address | Sub address                      | PWM DATA                                 | Period command |

| 1 byte        | <             | <                                | <pre>1 to 9 bytes / 1 to 24 bytes </pre> | 1 byte >       |

#### Figure 4-2 Basic format (2-wire input)

| Start command (1 byte)<br>Slave address (1 byte)<br>Sub address (1 byte)<br>PWM DATA<br>(1 byte to 9 bytes or 1 byte to 24 bytes) | <ul> <li>: Judgement of start input</li> <li>: Configures ID numbers of the IC (up to 64).</li> <li>: Specifies LED output where PWM DATA is transmitted.</li> <li>: Configures 127-grayscale PWM DATA that is transmitted to the specified LED output.</li> <li>TB62781FNG: 1 byte (1 channel) to 9 bytes (9 channels)</li> <li>TB62D612FTG: 1 byte (1 channel) to 24 bytes (24 channels)</li> </ul> |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Period command (1 byte):                                                                                                          | channels) : Judgement of communication completion                                                                                                                                                                                                                                                                                                                                                     |

Description of each command is following from the next page.

#### 4.1.3. Start command (2-wire input)

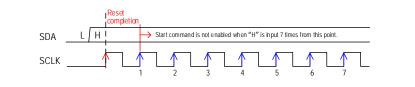

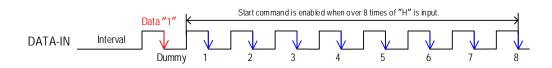

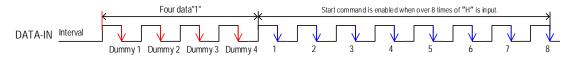

As shown in the figure 4-3, the start command is recognized when "1" is received over eight times in succession.

Make sure to receive "0" at the MSB of the slave address and then receive following DATA of the slave address.

Figure 4-3 Start command (2-wire input)

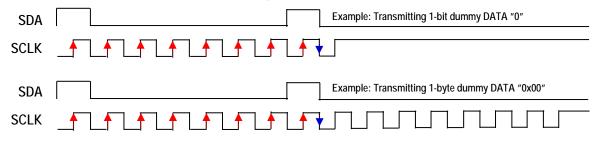

#### 4.1.4. Period command (2-wire input)

As shown in the figure 4-4, the period command is recognized when receiving "10000001". The eighth SCLK falling edge reflects the PWM DATA on the output. Then, the communication waits for the re-input of the start command.

Figure 4-4 Period command (2-wire input)

<Attention>

In using TB62D612FTG, SCLK DATA for the period command should be input until the eighth falling edge. The idle state of SCLK transmission is in high level or low level according to the usage environment. Refer to the figure 4-5 and the figure 4-6.

When SCLK transmission is in the idle state with low level

#### Figure 4-5 Period command (2-wire input) (Example 1)

When SCLK transmission is in the idle state with high level

#### Figure 4-6 Period command (2-wire input) (Example 2)

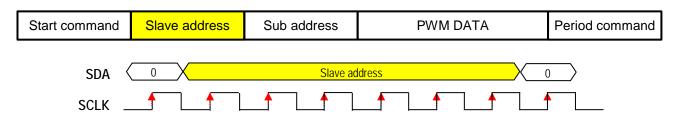

#### 4.1.5. Slave address (2-wire input) (unique numbers of the IC set by ID0, ID1, and ID2 pins)

As shown in the figure 4-7, ID numbers (0 to 63, up to 64 numbers) are set by ID0, ID1, and ID2 pins and input to the slave address.

MSB is input first. The slave address is configured by intermediate DATA (MSB and LSB are set "0") except all select setting.

When inputting "1" to LSB, the PWM DATA of all ICs can be set regardless of the intermediate DATA, allowing it to reset software.

Figure 4-7 Slave address (2-wire input)

The slave address of 0 to 11 and all selection mode are shown in the table 4-2. It is excerpted from the technical DATA.

Though the slave address that is not described in the technical DATA is not received, it is recommended to avoid inputting it for shipment to guarantee safety.

#### Table 4-2 Slave address (2-wire input) excerpted from the technical DATA

|    | Slave add        | lress             |        | D pin settin  | g        |

|----|------------------|-------------------|--------|---------------|----------|

| ID | Slave<br>address | Decimal<br>number | ID2    | ID1           | ID0      |

| 0  | "00000000"       | 0                 | GND    | GND           | GND      |

| 1  | "00000010"       | 1                 | GND    | GND           | Vcc×1/3  |

| 2  | "00000100"       | 2                 | GND    | GND           | Vcc×2/3  |

| 3  | "00000110"       | 3                 | GND    | GND           | Vcc      |

| 4  | "00001000"       | 4                 | GND    | Vcc×1/3       | GND      |

| 5  | "00001010"       | 5                 | GND    | Vcc×1/3       | Vccx*1/3 |

| 6  | "00001100"       | 6                 | GND    | Vcc×1/3       | Vcc×2/3  |

| 7  | "00001110"       | 7                 | GND    | Vcc×1/3       | Vcc      |

| 8  | "00010000"       | 8                 | GND    | Vccx2/3       | GND      |

| 9  | "00010010"       | 9                 | GND    | Vccx2/3       | Vcc×1/3  |

| 10 | "00010100"       | 10                | GND    | Vccx2/3       | Vcc×2/3  |

| 11 | "00010110"       | 11                | GND    | Vccx2/3       | Vcc      |

|    |                  | ~ \$              | Snip ~ |               |          |

| 63 | "01111110"       | 63                | Vcc    | Vcc           | Vcc      |

| —  | 0XXXXXX1         | -                 |        | All selection | n        |

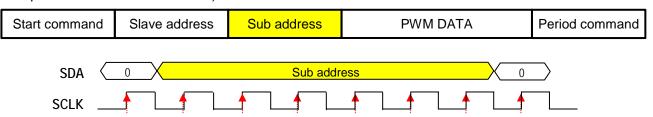

#### 4.1.6. Sub address (2-wire input) (Selecting LED output controlled for PWM DATA setting)

As shown in the figure 4-8, LED output is selected in the sub address for PWM DATA setting. MSB is input first. The sub address is configured by intermediate DATA (MSB and LSB are set "0"). Output selection has 3 modes.

- 1. Output channel setting: Select only specified LED outputs.

- 2. All channels setting: Select all LED outputs, 9 channels (in case of TB62781FNG), or 24 channels (in case of TB62D612FTG).

- 3. Special mode setting: LED outputs are selected in a sequence. (9 channels of OUTR0 to OUTB2 for TB62781FNG, and 24 channels of OUTR0 to OUTB7 for TB62D612FTG).

LED outputs are incremented as follows;  $OUTR0 \rightarrow G0 \rightarrow B0$ ,  $OUTR1 \rightarrow G1 \rightarrow B1 \cdots OUTR7 \rightarrow G7 \rightarrow B7$ (Example in case of TB62D612FTG)

Figure 4-8 Sub address (2-wire input)

Output channel setting mode is shown in the table 4-3. (From OUTR0 to OUTB2 and from OUTR7 to OUTB7 excerpted from the technical DATA, all channel setting mode, and special mode) Though the sub address that is not described in the technical DATA is not received, it is recommended to avoid inputting it for shipment to guarantee safety.

| Table 4-3 Sub address | 2-wire inpu | t) excerpted f | rom the technical DATA |

|-----------------------|-------------|----------------|------------------------|

|                       |             | .,             |                        |

| Sub address | LED                        | output                     | Sotting torget of DWM DATA                                    |

|-------------|----------------------------|----------------------------|---------------------------------------------------------------|

| Sub address | TB62781                    | TB62D612                   | Setting target of PWM DATA                                    |

| "00000010"  | /OU                        | TR0                        |                                                               |

| "00000100"  | /OU                        | TG0                        |                                                               |

| "00000110"  | /OU                        | TB0                        |                                                               |

| "00001000"  | /OU                        | TR1                        |                                                               |

| "00001010"  | /OU                        | TG1                        |                                                               |

| "00001100"  | /OU                        | TB1                        |                                                               |

| "00001110"  | /OU                        | TR2                        |                                                               |

| "00010000"  |                            | TG2                        |                                                               |

| "00010010"  | /OU                        | TB2                        | Select only specified LED outputs                             |

| "00010100"  | -                          | /OUTR3                     | TB62781: Select all LED outputs                               |

|             | ~ Snip ~                   |                            |                                                               |

| "00100000"  | All<br>channels<br>setting | /OUTR5                     |                                                               |

|             | ~ Snip ~                   |                            |                                                               |

| "00101100"  | -                          | /OUTR7                     |                                                               |

| "00101110"  | -                          | /OUTG7                     |                                                               |

| "00110000"  | -                          | /OUTB7                     |                                                               |

| "01000000"  | -                          | All<br>channels<br>setting | TB62D612: Select all LED outputs                              |

| "01100000"  | Special mo                 | ode setting                | Select LED outputs of 9 channels or 24 channel in a sequence. |

#### 4.1.7. PWM DATA (2-wire input, 127 grayscales)

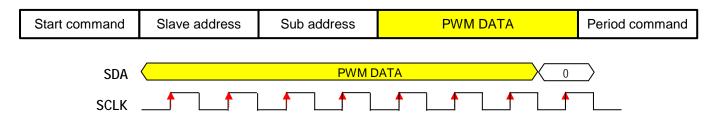

As shown in the figure 4-9, PWM DATA is configured to control the selected LED outputs.

- 1. Output channel setting: 1 byte

- 2. All channels setting: 1 byte

- 3. Special mode setting: 9 bytes or 24 bytes

In the case of sub address setting in the special mode, it can be interrupted by replacing the PWM DATA with the period command.

When LED outputs do not receive or update PWM DATA, former PWM DATA is used. MSB is input first. PWM DATA is set by intermediate DATA (LSB is set "0").

Figure 4-9 PWM DATA (2-wire input)

The table 4-4 shows the PWM DATA of 0/127 to 8/127 and 119/127 to 127/127 excerpted from the technical DATA.

Though the sub address that is not described in the technical DATA is not received, it is recommended to avoid inputting it for shipment to guarantee safety.

| Table 4-4 PWM DATA (2-wire input) excerpted from the technica |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Data     | PWM<br>dimmable | Remarks                                            |

|----------|-----------------|----------------------------------------------------|

| 00000000 | 0/127           |                                                    |

| 00000010 | 1/127           |                                                    |

| 00000100 | 2/127           |                                                    |

| 00000110 | 3/127           |                                                    |

| 00001000 | 4/127           |                                                    |

| 00001010 | 5/127           |                                                    |

| 00001100 | 6/127           |                                                    |

| 00001110 | 7/127           |                                                    |

| 00010000 | 8/127           | Initial state: Always off at the setting of 0/127. |

| ~ Sni    | р~              | LSB: Set "0". Do not set "1".                      |

| 11101110 | 119/127         | 127/127: Always on.                                |

| 11110000 | 120/127         |                                                    |

| 11110010 | 121/127         |                                                    |

| 11110100 | 122/127         |                                                    |

| 11110110 | 123/127         |                                                    |

| 11111000 | 124/127         |                                                    |

| 11111010 | 125/127         |                                                    |

| 11111100 | 126/127         |                                                    |

| 11111110 | 127/127         |                                                    |

#### 4.1.8. Packet input (2-wire input) (Data communication to two or more ICs)

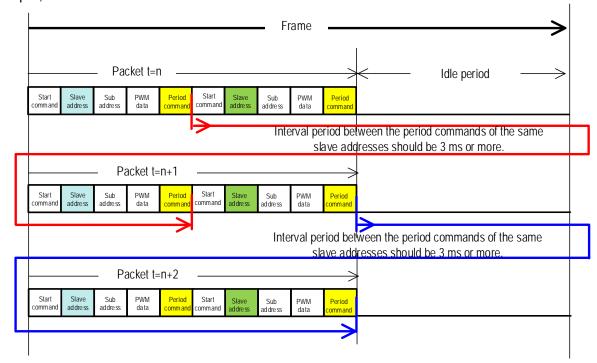

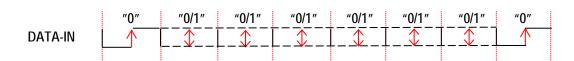

The figure 4-10 shows the communication model of two ICs whose slave addresses are different. Input format of the two ICs, whose slave addresses are different, are communicated by consecutive packets with a certain frame cycle (fps).

After the packet ends, SDA and SCLK transmissions become the idle states and do not perform DATA communication until the next frame starts.

As for the packet (t=n, n+1, n+2···) and the next packet (t=n+1, n+2, n+3···), the interval period should be 3 ms or more between 8th down edges of the period commands of the same slave address. One cycle of the internal PWM counter is up to 3 ms. PWM DATA is updated after the period command ends and the count value becomes maximum. It is because if PWM DATA is transmitted to the same LED output, it is not received while the count value does not reach the maximum.

Figure 4-10 Image of packet communication to the IC with the same slave address when using two ICs with different slave addresses (2-wire input)

#### <Attention>

# 4.1.9. Errata: Errata make the next input format into non-reception state according to the end timing of SCLK transmission.

Errata occur when using TB62D612FTG (2-wire input, 24 channels), and not occur in using TB62781FNG.

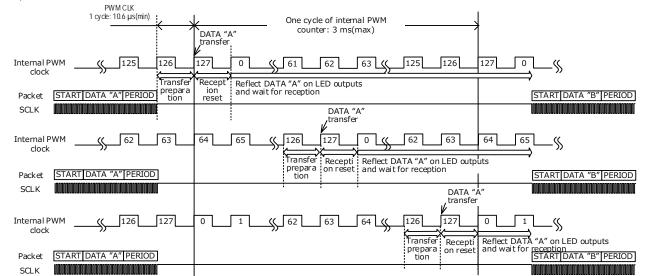

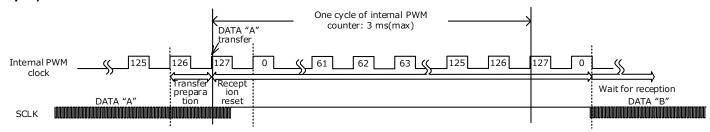

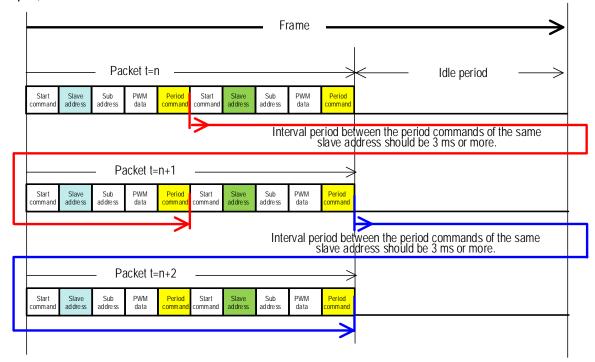

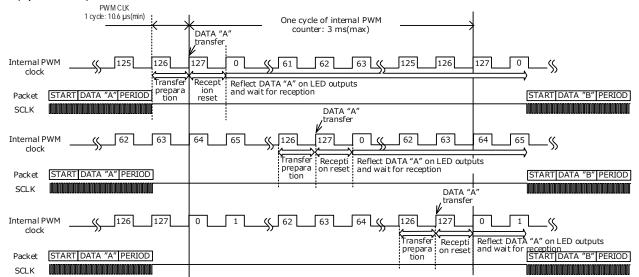

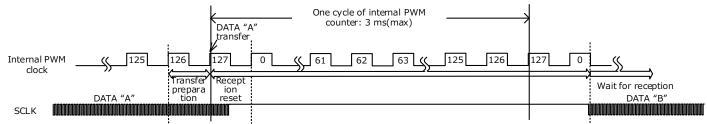

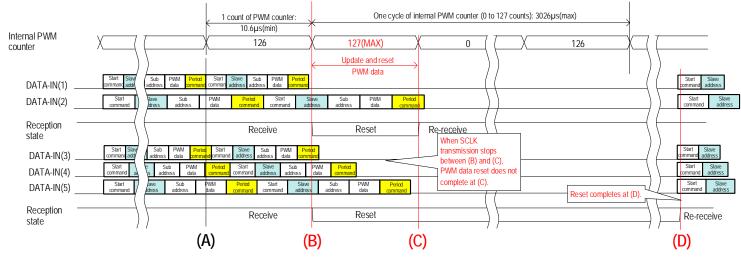

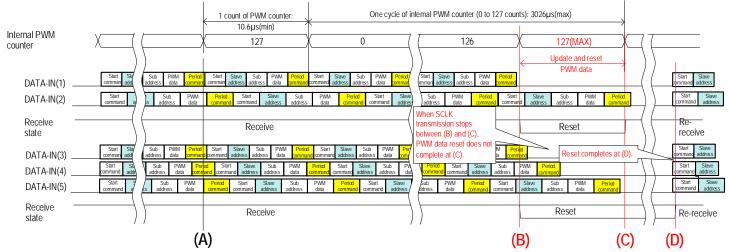

Figure 4-11 shows update and reception reset of PWM data (DATA "A") when the first internal PWM counter after the period command is 127.

The period of one packet varies depending on the number of input formats and the frequency of the SCLK. Since transmissions of the SCLK and the internal PWM clocks are asynchronous, the timing of the period command and that of PWM DATA transmission and reception reset exist randomly in one cycle (up to 3 ms) of the internal PWM counter.

## Figure 4-11 Update and reception reset timing of PWM DATA after the period command (2-wire input)

#### Figure 4-12 Timing of SCLK transmission when errata occur (2-wire input)

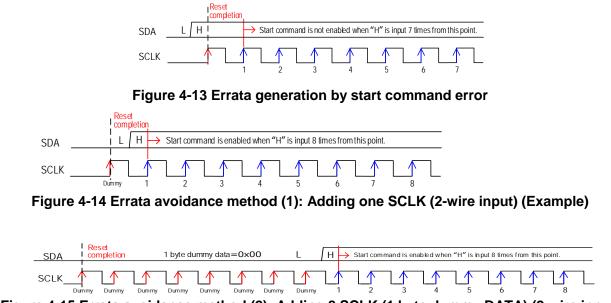

Errata occur in accordance with the end timing of SCLK transmission.

The timing of the Figure 4-12 nearly corresponds to the top timing chart in the Figure 4-11.

In this timing, SCLK transmission stops during reception reset.

Therefore, the reception reset continues until the next packet starts. After it finishes at the beginning of the next packet, the packet moves to the reception waiting status. So, DATA "B" at the beginning of the packet is not received.