Mar, 2018

### Datasheet Correction: Programmable Motor Driver (PMD)

We would like to inform customers the corrections of the following datasheets. If you have any questions or require any further information, please contact your local sales office.

#### 1. Products

TMP89FM82DUG, TMP89FM82TDUG

#### 2. Correction

The function of Programmable Motor Driver (PMD) use are changed. To use the Programmable Motor Driver (PMD), please keep the following restrictions and use.

Notice

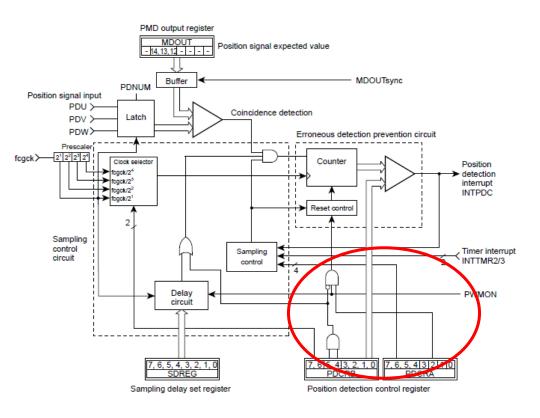

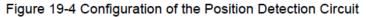

#### (1) 9.3.1 Configuration of the position detection unit

Figure 19-4 Configuration of the Position Detection Circuit

### (2) 19.3.2 Position Detection Circuit Register Functions

### Function of bit2

# <u>Error</u>

|             | 2          | RCEN | Recount occurrences of matching when PWM is on    | By setting "1",the match count is Recounted for each PWM on.<br>(when recounting occurrences of matching, the count is reset<br>each time PWM turns off).<br>When this bit is set to "0", occurrences of matching are counted<br>continuously when PWM is on (counting is held when PWM is off. |

|-------------|------------|------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Corr</u> | <u>ect</u> |      |                                                   |                                                                                                                                                                                                                                                                                                 |

|             | 2          | RCEN | Recount occurrences of<br>matching when PWM is on | 1" is prohibition of a setup.<br>When this bit is set to "0", occurrences of matching are counted<br>continuously when PWM is on (counting is held when PWM is off.                                                                                                                             |

### Register

|          | 7     | 6     | 5     | 4     | 3     | 2    | 1    | 0     |                            |

|----------|-------|-------|-------|-------|-------|------|------|-------|----------------------------|

| PDCRA    | SWSTP | SWSTT | SPTM3 | STTM2 | PDNUM | RCEN | DTMD | PDCEN | (Initial value: 0000 0000) |

| (0X0EC0) |       |       |       |       |       |      |      |       |                            |

|              | 7 | SWSTP | Stop sampling in software                           | 0: No operation<br>1: Stop sampling                                      |     |  |

|--------------|---|-------|-----------------------------------------------------|--------------------------------------------------------------------------|-----|--|

|              | 6 | SWSTT | Start sampling in software                          | 0: No operation<br>1: Start sampling                                     | w   |  |

|              | 5 | SPTM3 | Stop sampling using Timer 3                         | 0: Disable<br>1: Enable                                                  |     |  |

| <u>Error</u> | 4 | STTM2 | Start sampling using Timer 2                        | 0: Disable<br>1: Enable                                                  |     |  |

|              | 3 | PDNUM | Number of position signal input pins                | 0: Compare three pins (PDU/PDV/PDW)<br>1: Compare one pin (PDU) only     | DAM |  |

|              | 2 | RCEN  | Recount occurrences of match-<br>ing when PWM is on | 0: Continue counting from previously PWM on<br>It each time PWM turns on |     |  |

|              | 1 | DTMD  | Position detection mode                             | y mode<br>th detection mode                                              |     |  |

|              | 0 | PDCEN | Enable/Disable position detec-<br>tion function     | h je (Sampling starts)                                                   |     |  |

# <u>Correct</u>

| 2 RCEN Recount occurrences of<br>matching when PWM is on 0: Continue counting from previously PWM on<br>1: Reserved (Prohibit) R/W |

|------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------|

## (3) 19.7.2 Motor Control Circuit Control Registers

|    | Name  | Address | Bit    | R or W                                       | Description                                                                                                                                                            |  |  |

|----|-------|---------|--------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    |       |         | 5, 4   | R                                            | Detect the position-detected position.<br>00: Within the current pulse 01: When PWM is off<br>10: Within the current pulse 11: Within the preceding pulse              |  |  |

|    | PDCRC | 0x0EC2  | 3      | R                                            | Monitor the sampling status.<br>0: Sampling idle<br>1: Sampling in progress                                                                                            |  |  |

|    |       |         | 2 to 0 | R                                            | Holds the status of the position signal input during unmatch detection mode.<br>Bits 2, 1, and 0: W, V, and U phases                                                   |  |  |

|    |       | 0x0EC1  | 7,6    | R/W                                          | Select the sampling input clock [Hz].<br>00: fcgck/2 01: fcgck/2 <sup>2</sup><br>10: fcgck/2 <sup>3</sup> 11: fcgck/2 <sup>4</sup>                                     |  |  |

|    | PDCRB |         | 5, 4   | R/W                                          | Sampling mode.<br>00: When PWM is on<br>01: Regularly<br>10: When lower phases are turned on                                                                           |  |  |

|    |       |         | 3 to 0 | R/W Detection position match counts 1 to 15. |                                                                                                                                                                        |  |  |

|    |       | 0x0EC0  | 7      | w                                            | 0: No operation<br>1: Stop sampling in software                                                                                                                        |  |  |

|    |       |         | 6      | w                                            | 0: No operation<br>1: Start sampling in software                                                                                                                       |  |  |

|    |       |         | 5      | R/W                                          | Stop sampling using Timer 3.<br>0: Disable<br>1: Enable                                                                                                                |  |  |

|    |       |         | 4      | R/W                                          | Start sampling using Timer 2.<br>0: Disable<br>1: Enable                                                                                                               |  |  |

| or | PDCRA |         | 3      | R/W                                          | Number of position signal input pins.<br>0: Compare three pins (PDU/PDV/PDW)<br>1: Compare one pin (PDU) only                                                          |  |  |

|    |       |         | 2      | R/W                                          | Count occurrences of matching when PWM is on.<br>0: Subsequent to matching counts when PWM previously was on<br>1: Recount occurrences of matching each time PWM is on |  |  |

| Ī  |       |         | 1      | R/W                                          | Position detection mode.<br>0: Ordinary mode<br>1: Unmatch detection mode                                                                                              |  |  |

|    |       |         | 0      | R/W                                          | /Disable position detection function.<br>ible<br>ble (Sampling starts)                                                                                                 |  |  |

| ľ  | SDREG | 0x0EC3  | 7 to 0 | PAN                                          | ing delay time.<br>Zifcgck (resolution 250ns at fcgck = 8 MHz).                                                                                                        |  |  |

# <u>Correct</u>

|--|

$\checkmark$