## **TOSHIBA**

株式会社 東芝 セミコンダクター社

# はじめに

この度は弊社 32 ビットマイクロコントローラ TLCS-900/H1 シリーズ、TMP92CM27 をご利用いただき、誠にありがとうございます。

本LSIをご利用になる前に、「使用上の注意、制限事項」の章を参照されますことをお願い致します。

#### CMOS 32 ビット マイクロコントローラ

#### TMP92CM27FG

### 1. 概要と特長

TMP92CM27 は、東芝オリジナル CPU TLCS-900/H1 をコアに採用し、高速にデータ処理を必要と する各種組み込み用制御機器向けに開発した、高機能32ビットマイクロコントローラです。

TMP92CM27FG は 144 ピンフラットパッケージ製品です。

TMP92CM27 の特長は次のとおりです。

- (1) オリジナル高速 32 ビット CPU (TLCS-900/H1 CPU 使用)

- TLCS-900, TLCS-900/L, TLCS-900/H, TLCS-900/L1 と命令コード完全互換

- 16M バイトのリニアアドレス空間

- 汎用レジスタ&レジスタバンク方式

マイクロDMA :8チャネル (250nS/4 バイト@40MHz)

(2) 最小命令実行時間 : 50nS(@40MHz)

: 32K バイト(32 ビット 1 クロックアクセス、 (3) 内蔵RAM プログラム実行可能)

内蔵ROM :なし

(4) 外部メモリ拡張

• 16M バイト(プログラム、データエリア)まで拡張可能

外部データバス 8/16 ビット幅共存可能

・・・・ダイナミックデータバスサイジング

セパレートバス システム

(5) メモリコントローラ

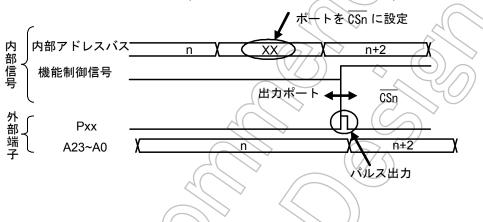

チップセレクト出力

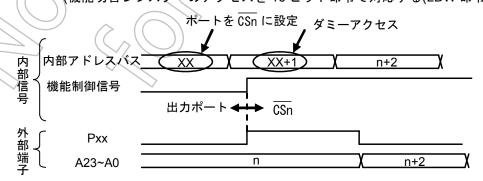

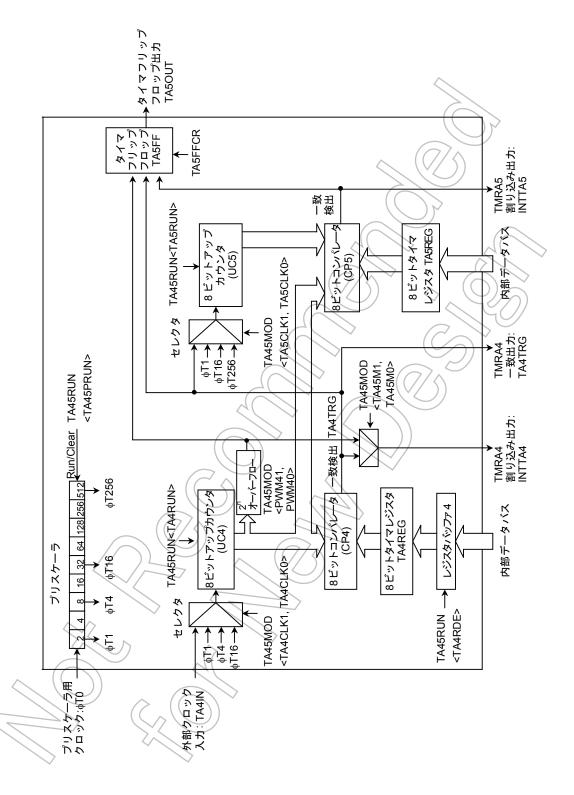

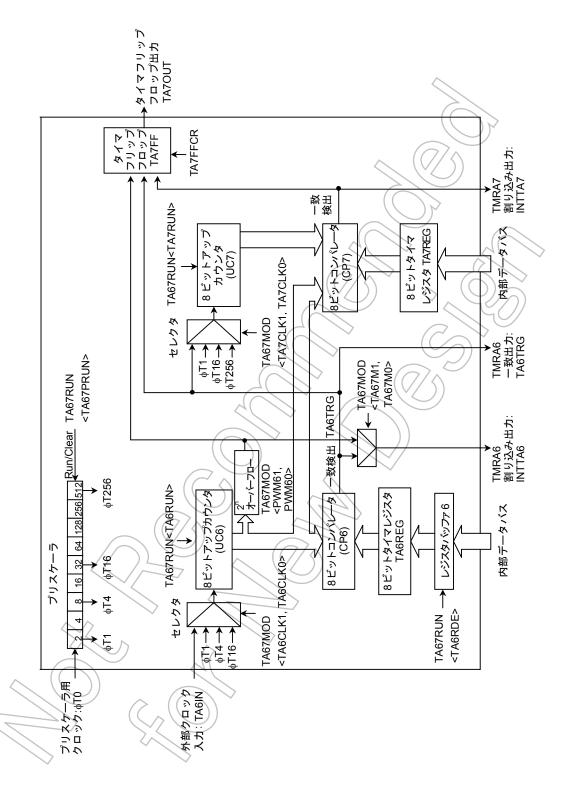

(6) 8ビットタイマ

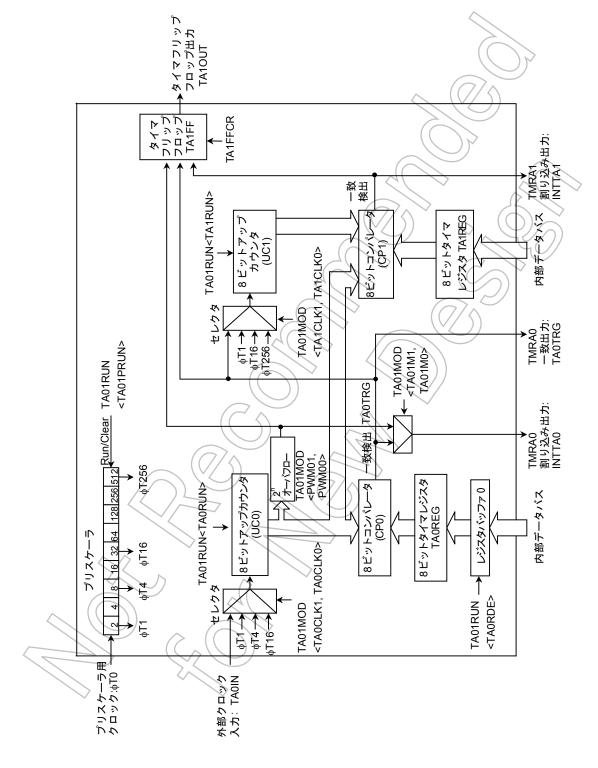

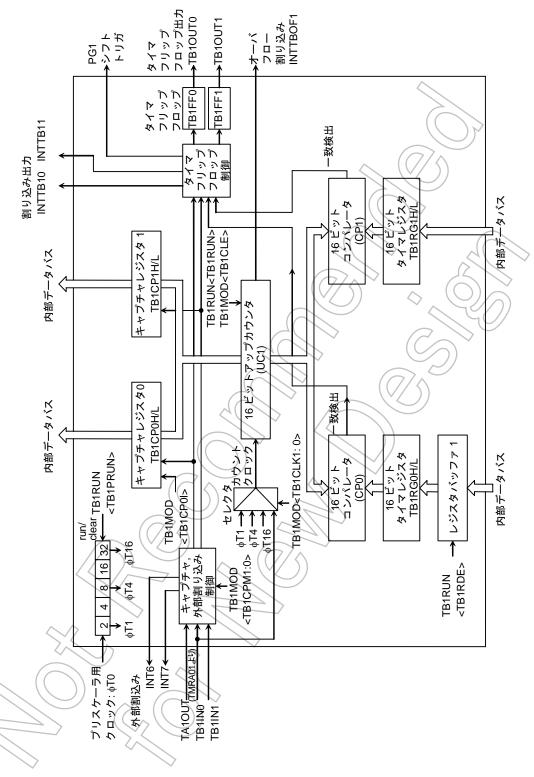

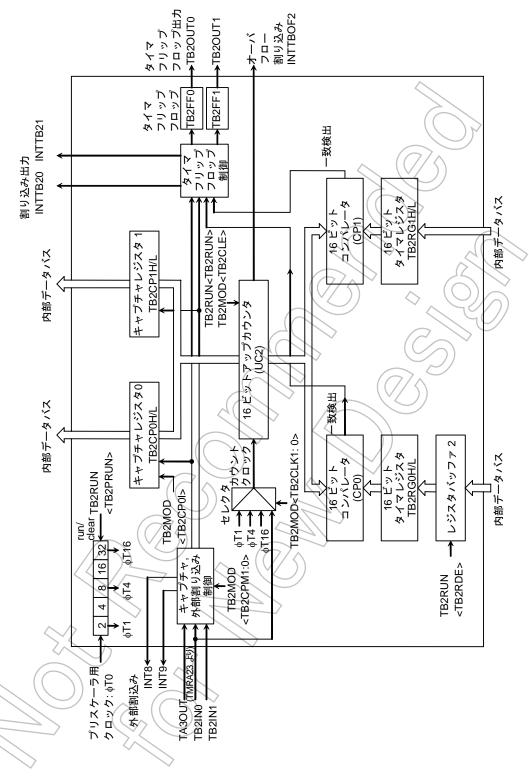

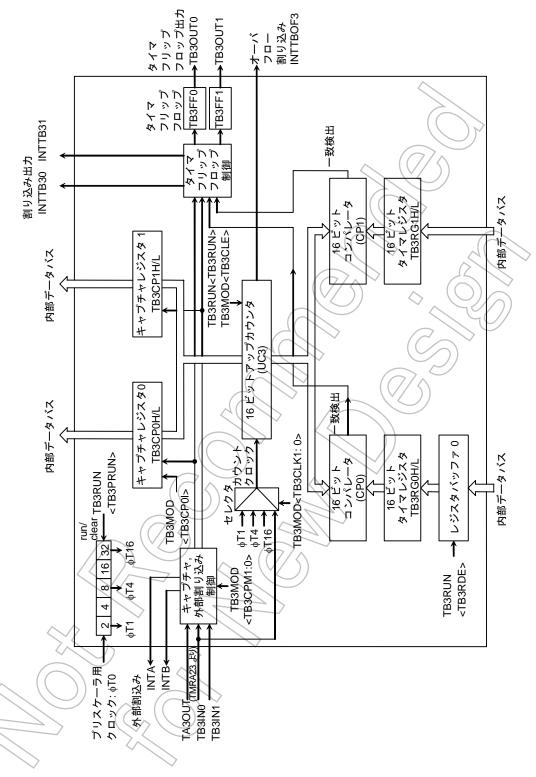

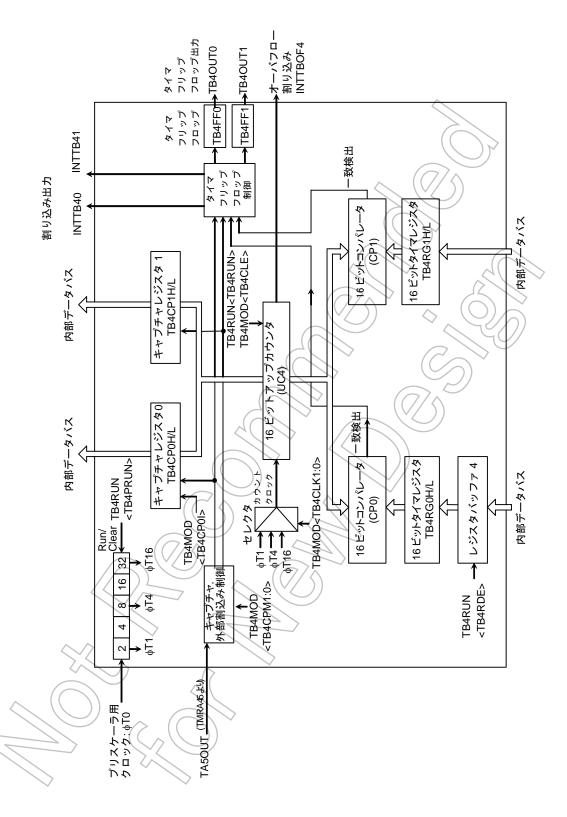

(7) 16 ビットタイマ

: 6 チャネル

:8 チャネル

6 チャネル

030519TBP1

- マイコン製品の信頼性予測については、「品質保証と信頼性 / 取り扱い上のご注意とお願い」の 1.3 項に記載されておりますので必 ずお読みください。

- ●当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり故障することがあります。当社半導体製品をご使用いただく場合は、半導体製品の誤作動や故障により、生命・身体・財産が侵害されることのないように、購入者側の責任におい

- 使用いただく場合は、半導体製品の誤作動や改障により、生命・身体・財産か受害されることのないように、内の自身の具はにあいて、機器の安全設計を行うことをお願いします。

なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用いただくと共に、考慮されるべき注意事項や条件について「東芝半導体製品の取り扱い上のご注意とお願い」、「半導体信頼性ハンドブック」などでご確認ください。

■本資料に掲載されている製品は、一般的電子機器(コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電機器など)に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や誤作動が直接人命を脅かしたり人体に危害を及ぼす恐れのある機器(原子力制御機器、航空宇宙機器、輸送機器、交通信号機器、燃焼制御、医療機器、各種安全装置など)にこれらの製品を使用すること(以下"特定用途"という)は意図もされていませんし、また保証もされていません。本資料に掲載されている製品を当該特定用途に使用することは、お客様の責任でなされることとなります。

■本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されているものです。

- ■本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されているものです。 ■本資料に掲載されている技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社および第三者の知 的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 本資料に掲載されている製品を、国内外の法令、規則および命令により製造、販売を禁止されている応用製品に使用することはで きません。

- 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

Purchase of TOSHIBA I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, Provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

> 92CM27 - 1 2005-04-12

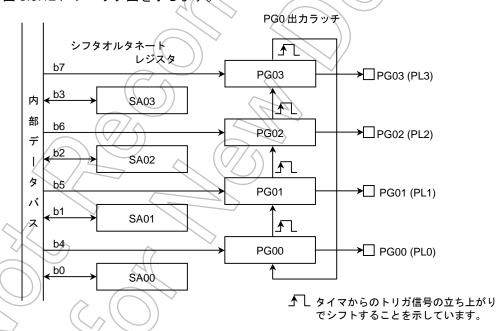

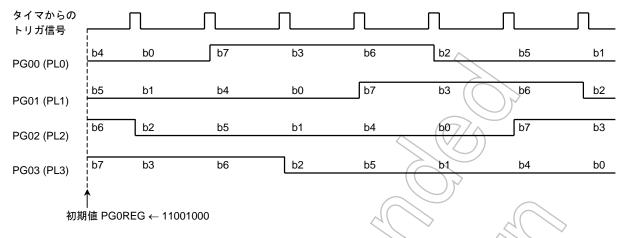

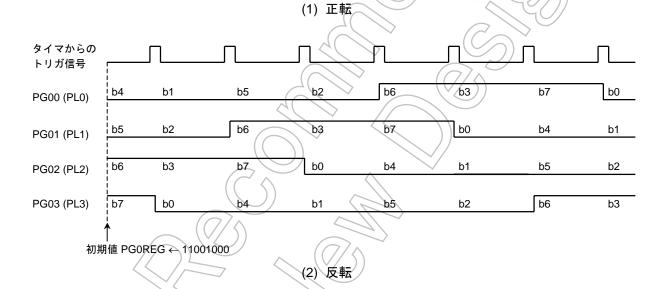

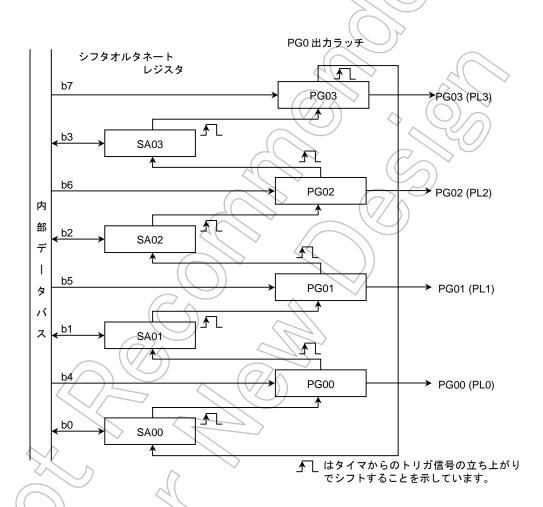

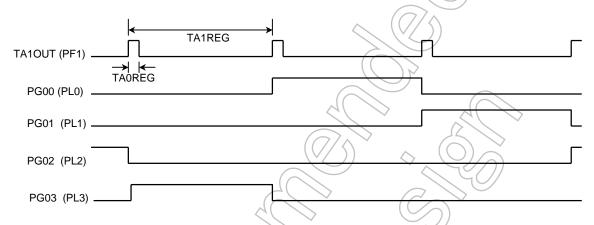

(8) パターンジェネレータ : 2 チャネル

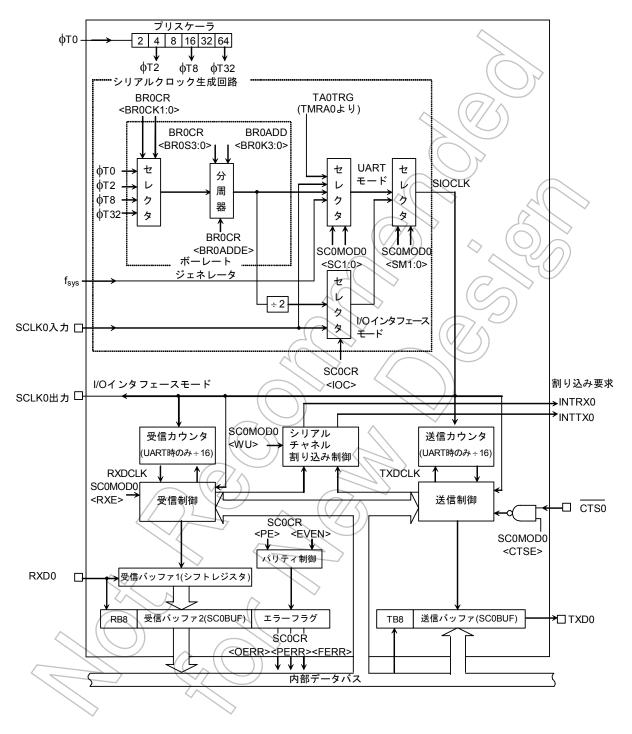

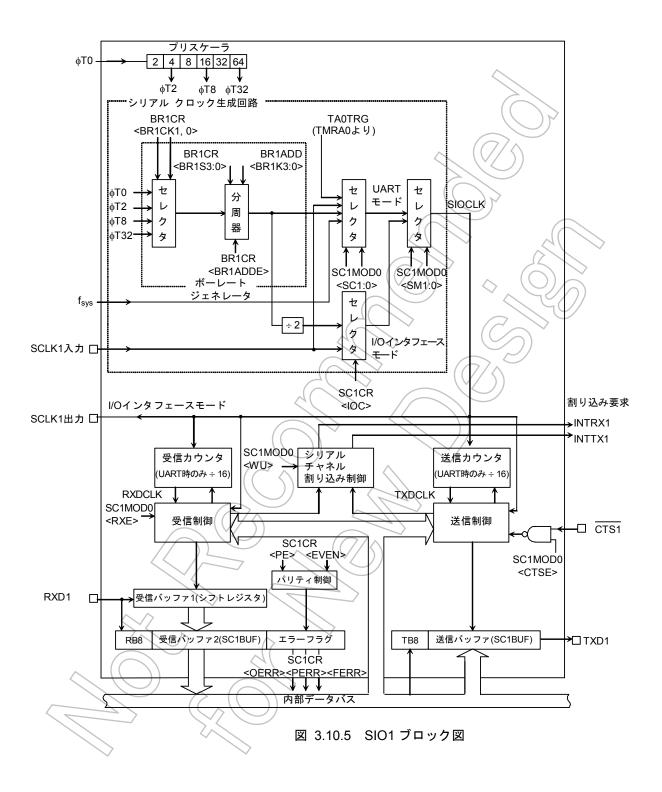

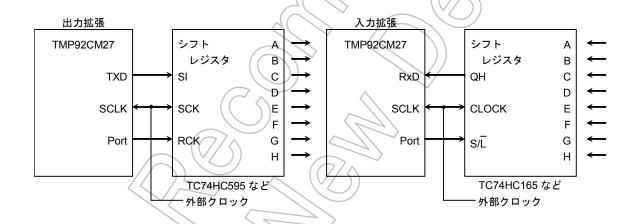

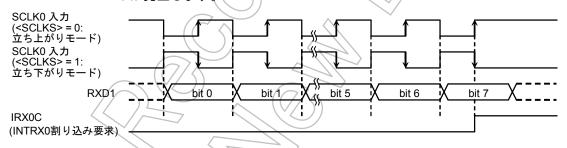

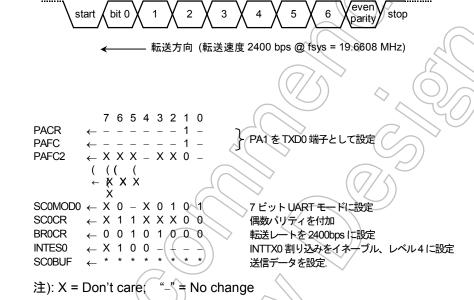

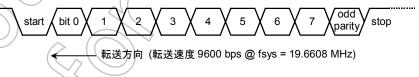

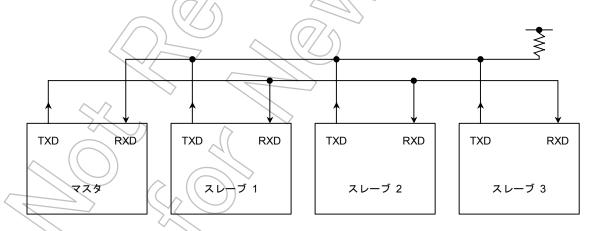

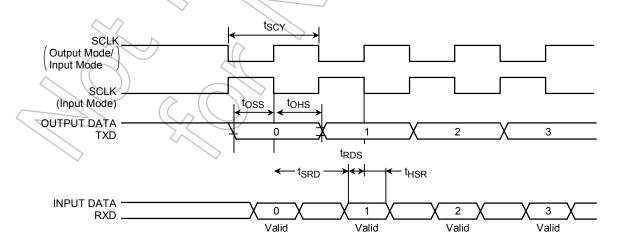

(9) 汎用シリアルインタフェース : 4 チャネル

● UART/同期両モード対応 : 4 チャネル

• IrDA ver1.0 (115.2kbps) 対応モード選択可能 : 1 チャネル

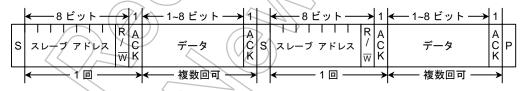

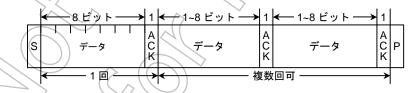

(10) シリアルバスインタフェース : 2 チャネル

I<sup>2</sup>Cバスモード

クロック同期モード

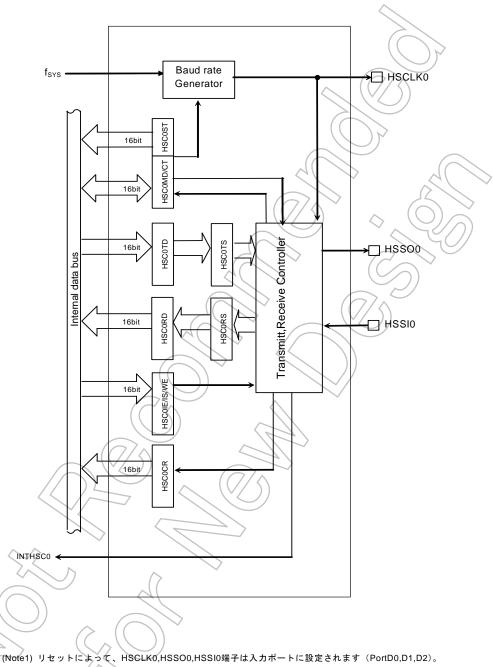

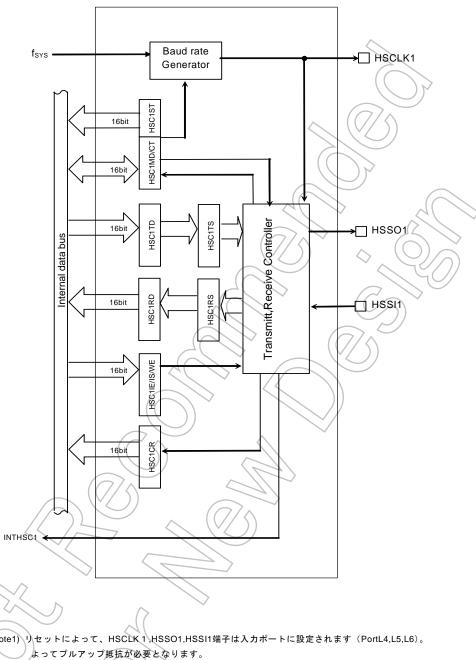

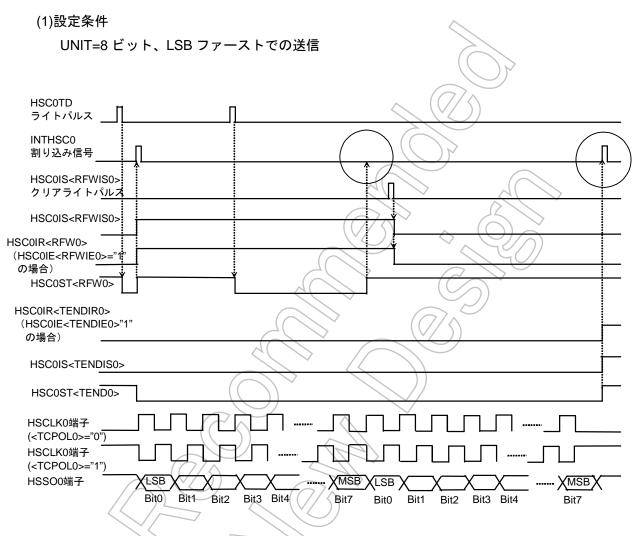

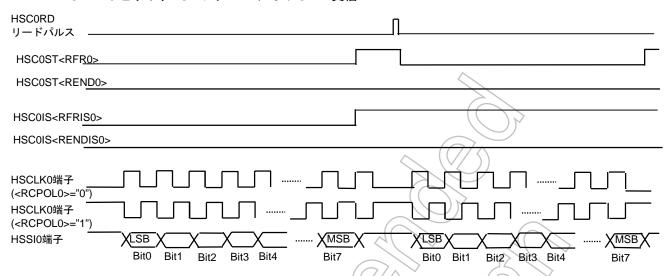

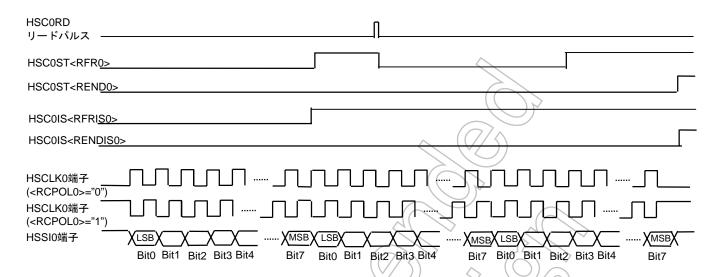

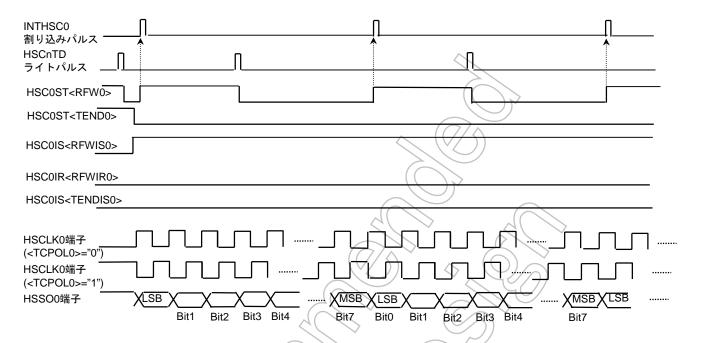

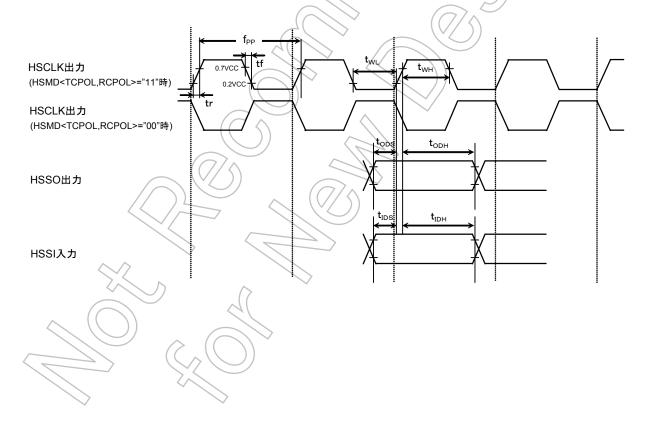

(11) 高速シリアルインタフェース(同期式) : 2 チャネル

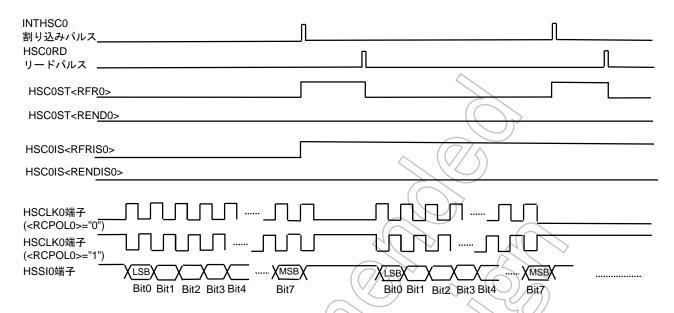

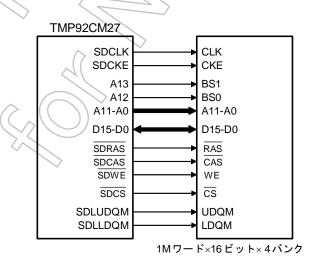

(12) SDRAMコントローラ : 1 チャネル

• 16Mおよび 64Mbit の SDR (Single-data-rate) SDRAM に対応

● データ RAM としてだけでなく、SDRAM から直接プログラムの動作が可能

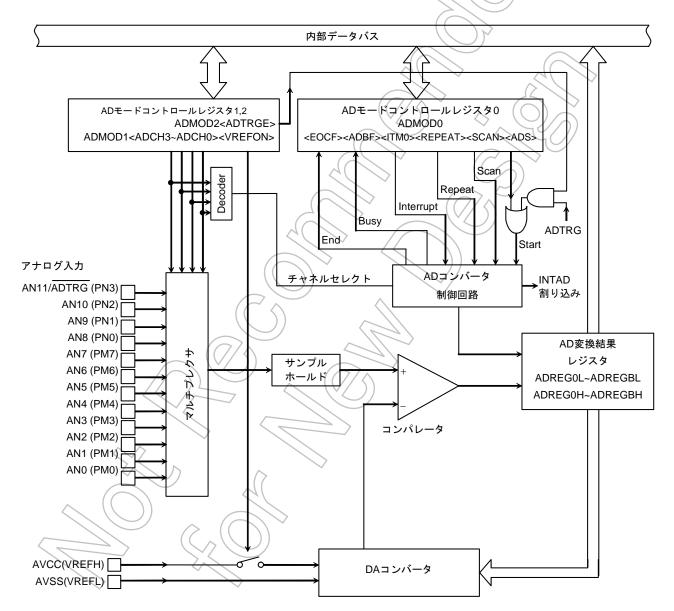

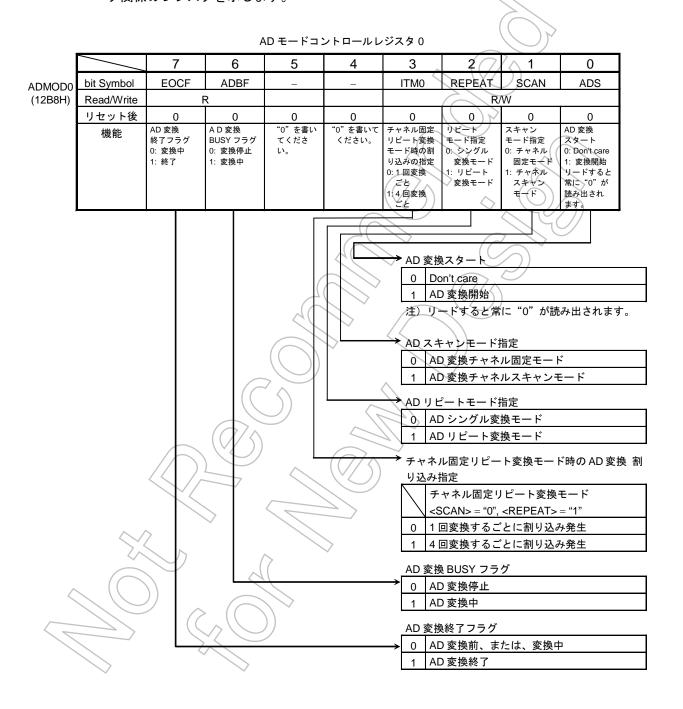

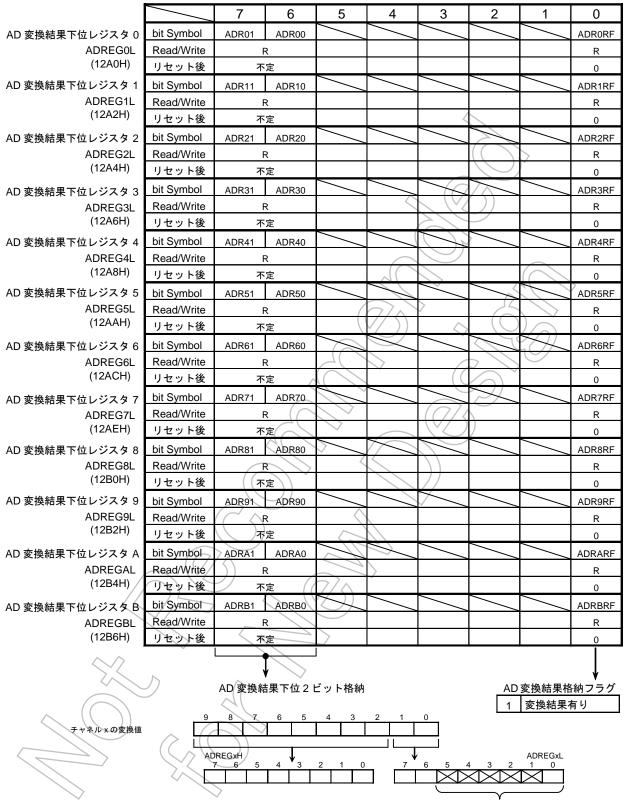

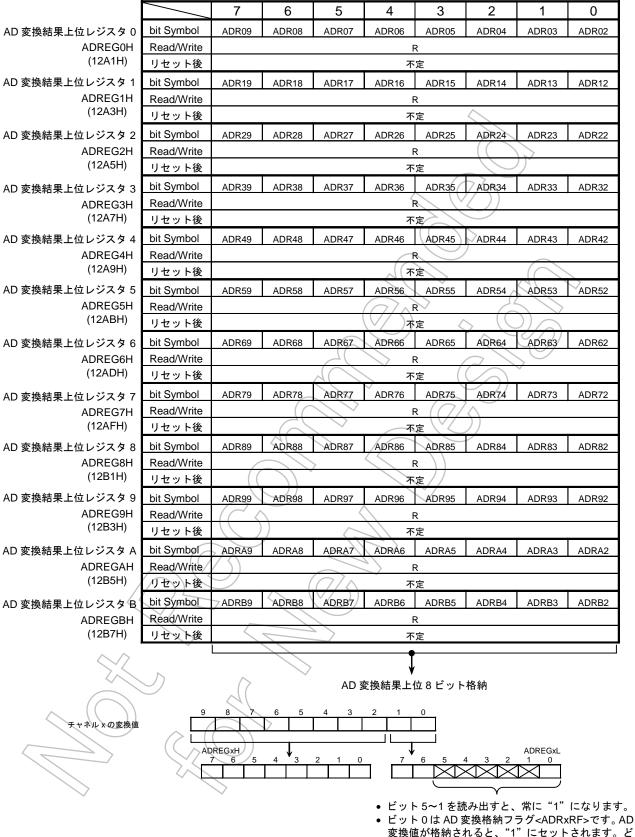

(13) 10ビットADコンバータ

: 12 チャネル

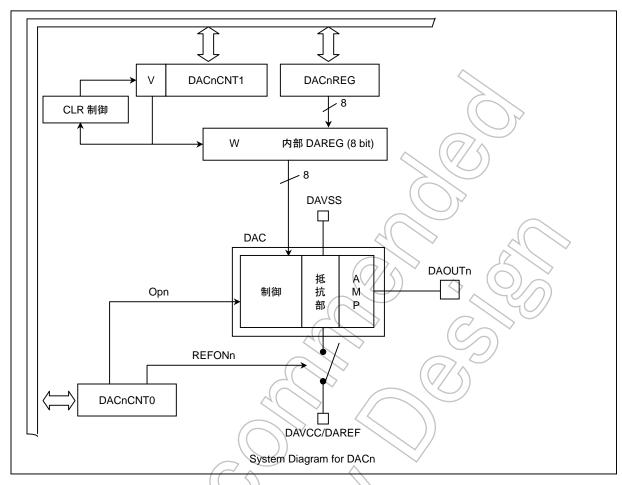

(14) 8ビットDAコンバータ

2 チャネル

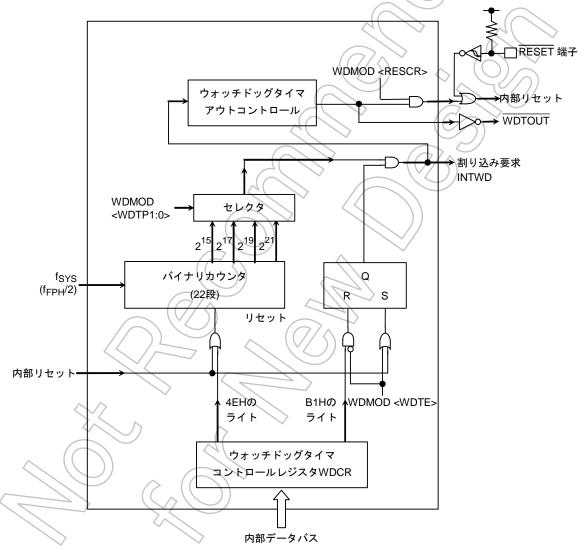

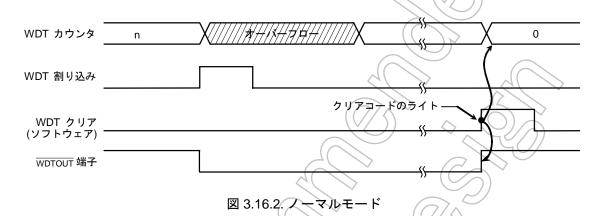

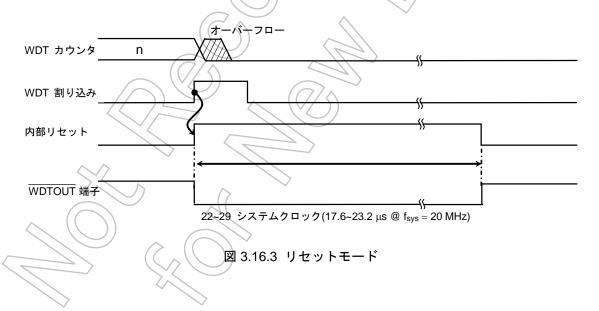

(15) ウォッチドッグタイマ

(16) キーオンウェイクアップ: 8 チャネル (HALT 解除機能のみ。キー入力割込みはありません)

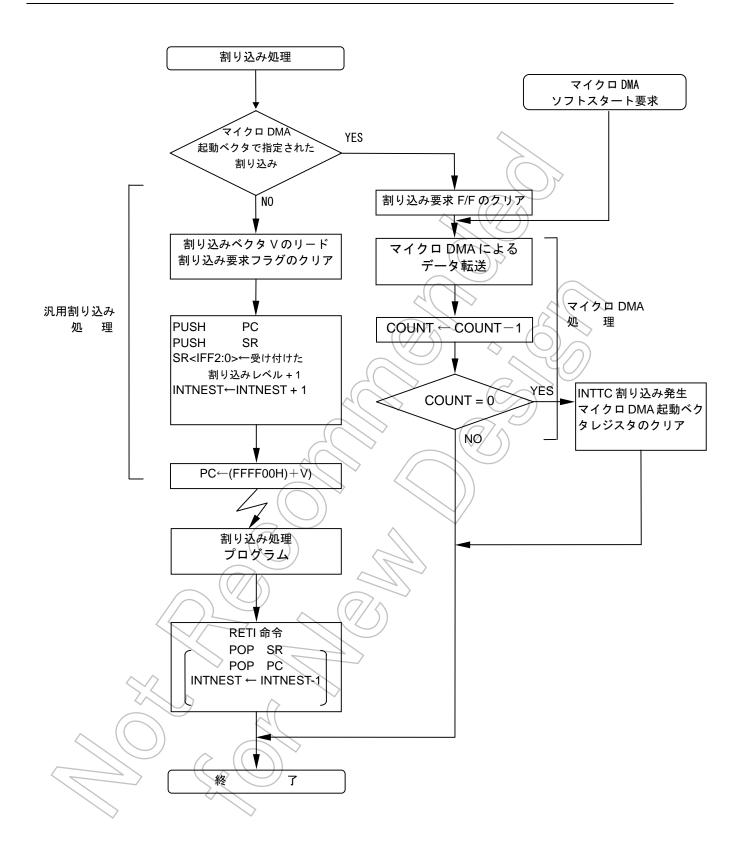

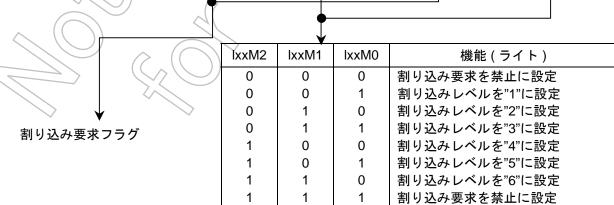

(17) 割り込み機能:71 本

• CPU 9本…… ソフトウエア割り込み命令、未定義命令実行違反

● 内部 49 本…… 7 レベルの優先順位の設定が可能。

兼用されている割り込み要因 (INTTA5/INT8,INTTA7/INT9,

INTTB30/INTTB31,INTTB40/INTTB41,INTTB50/INTTB51)があります。

詳細は、3.4章を参照ねがいます。

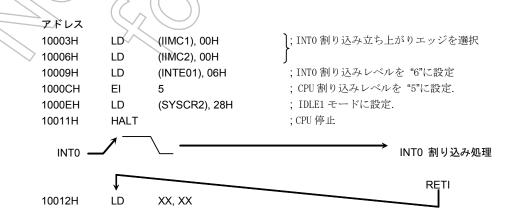

外部 13本(INTO~INTB, NMI)····· INTO~INTB は 7 レベルの優先順位の設定が可能で、 エッジまたはレベル割り込みの選択が可能です。

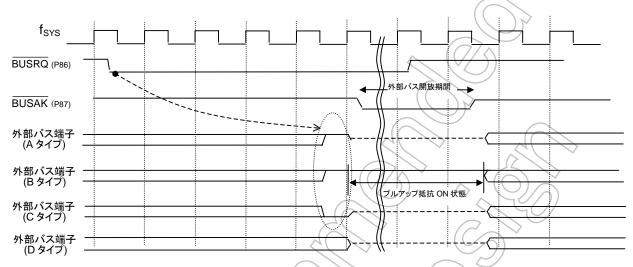

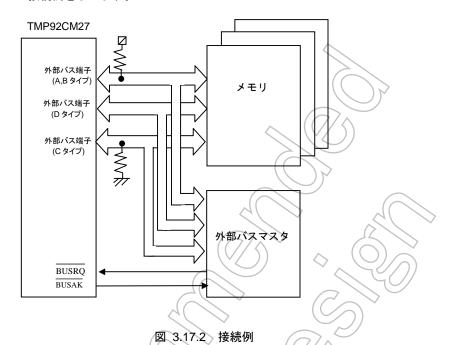

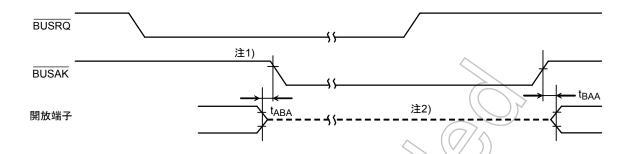

- (18) バス開放機能(BUSRQ, BUSAK)

- (19) 入出力ポート: 83 端子

- (20) スタンバイ機能

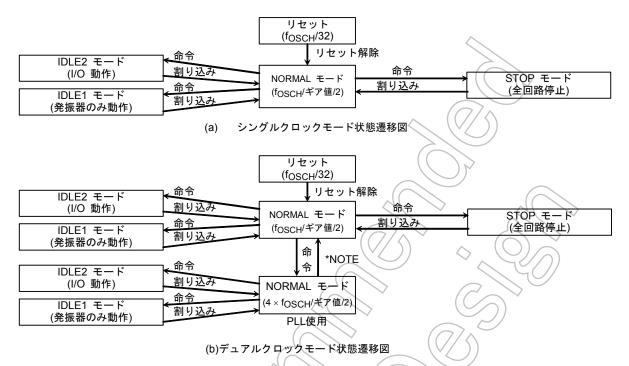

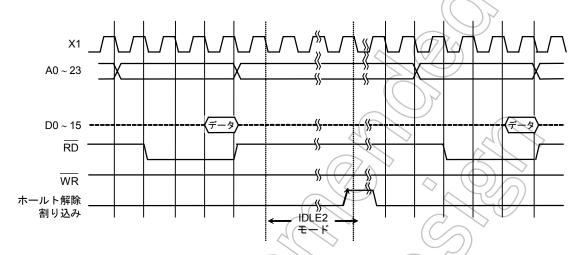

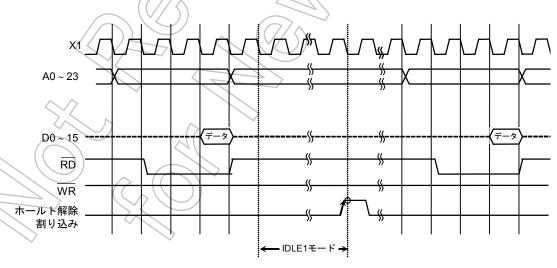

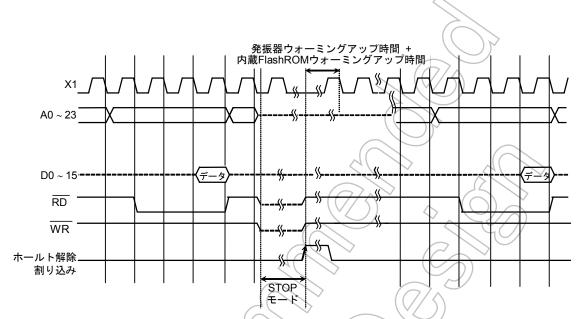

3 種類の HALT モード ······IDLE2(プログラマブル), IDLE1, STOP

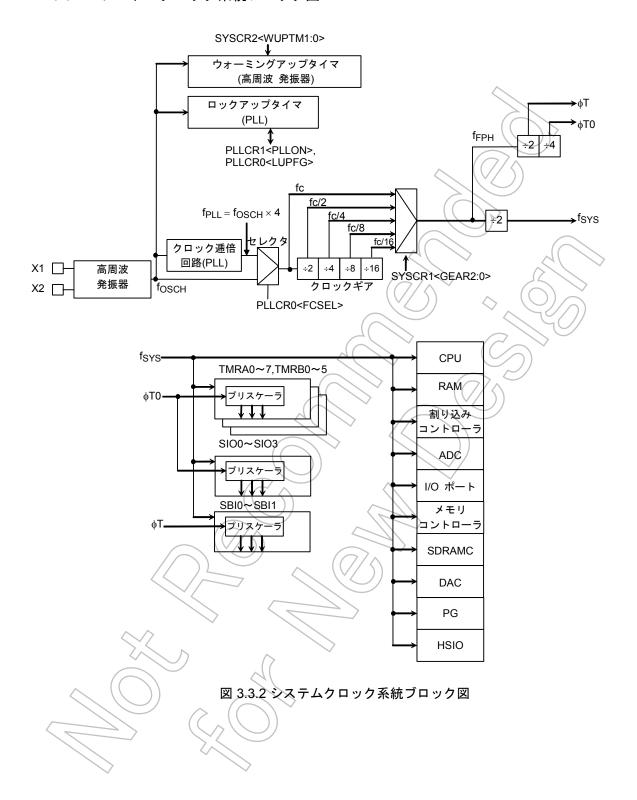

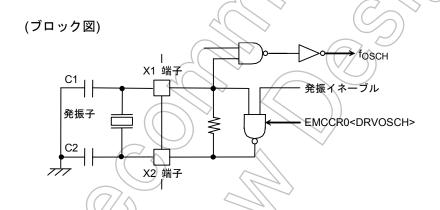

- (21) クロック制御機能

- クロック逓倍回路 (PLL) を内蔵

- クロックギア機能: 高周波クロック fc~fc/16 まで切り替え可能

- (22) 動作電圧

- $Vcc = 3.0 \sim 3.6 \text{ V}$  (fc max = 40 MHz)

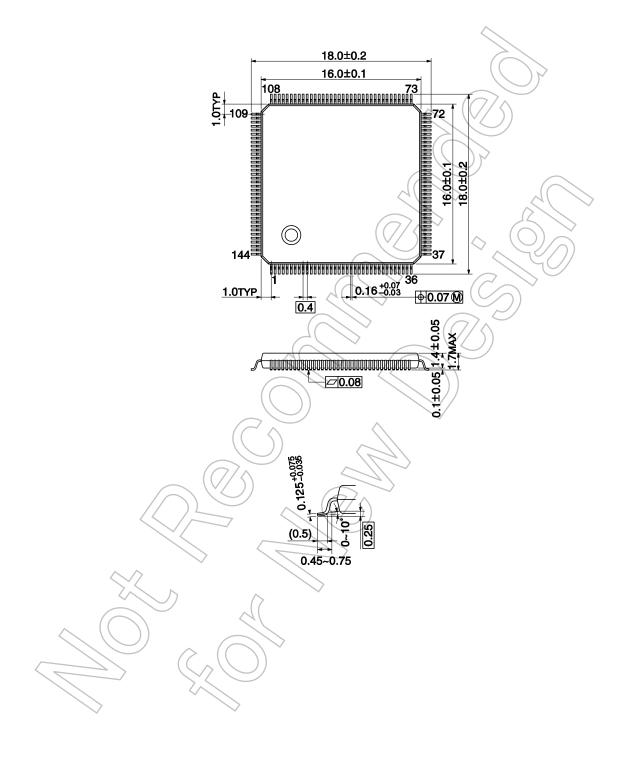

- (23) パッケージ

- 144 ピン QFP : P-LQFP144-1616-0.40C

92CM27 **-** 2 2005-04-12

TOSHIBA TMP92CM27

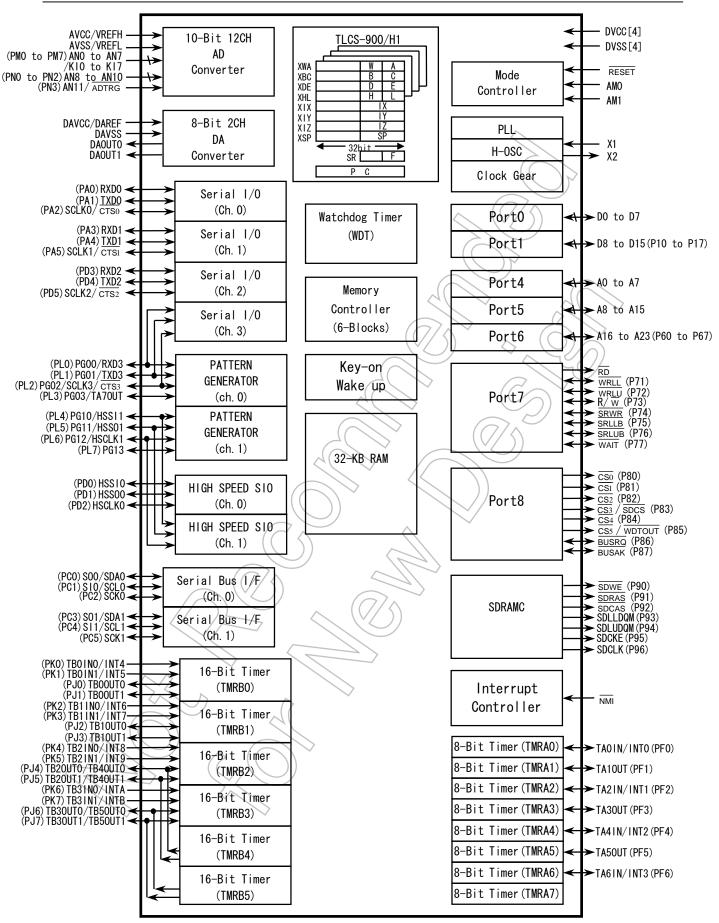

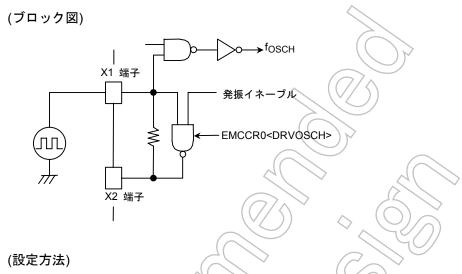

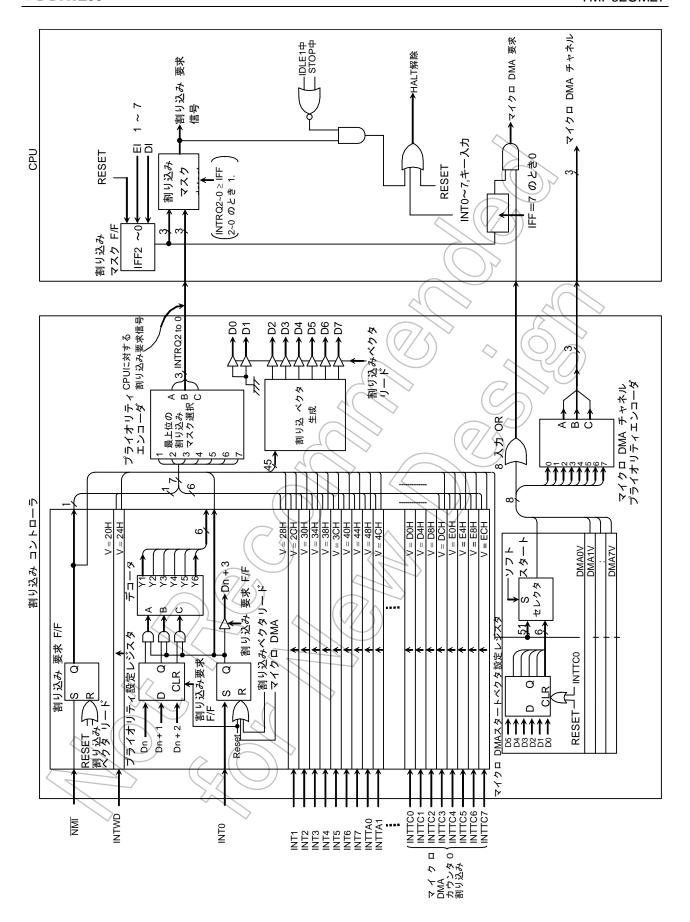

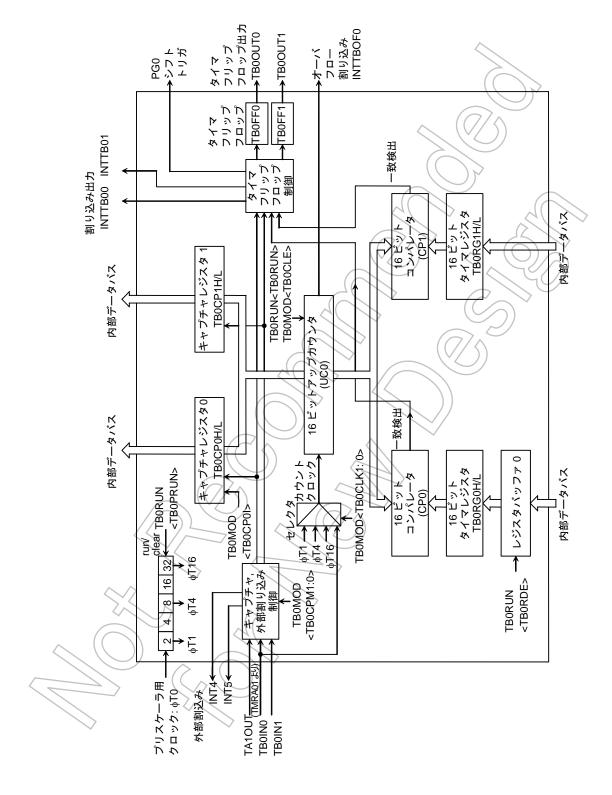

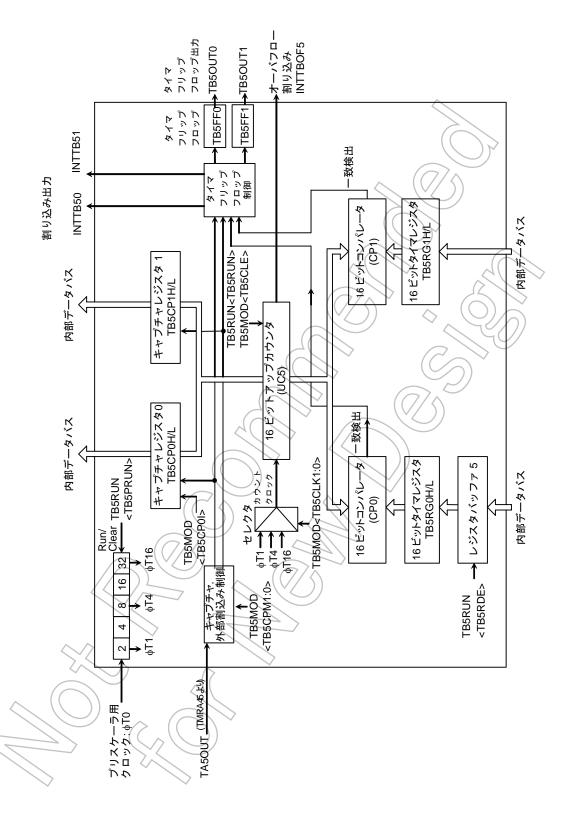

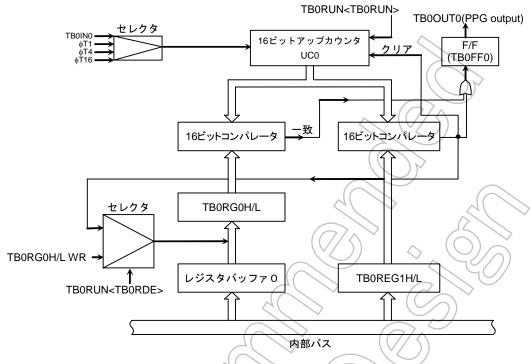

図 1.1 TMP92CM27 ブロック図

TOSHIBA TMP92CM27

## 2. ピン配置とピン機能

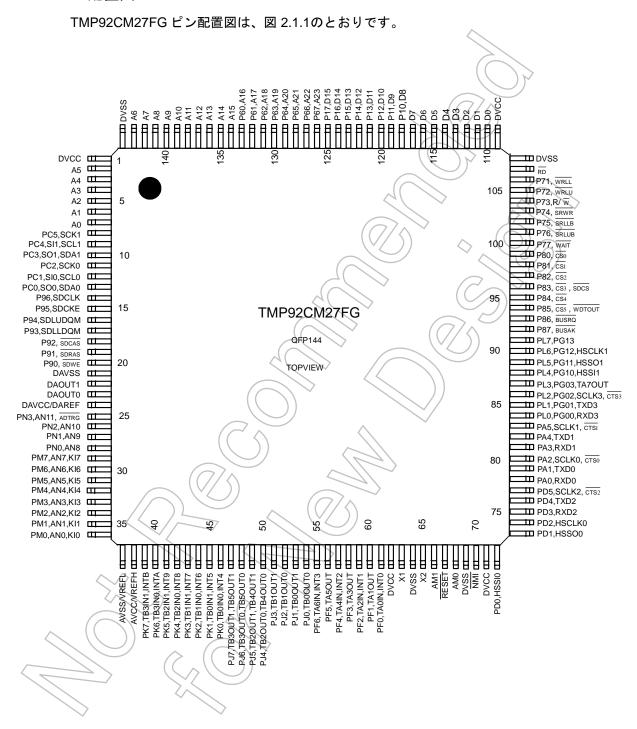

TMP92CM27のピン配置図および入出カピンの名称と概略機能を示します。

### 2.1 ピン配置図

図 2.1.1 ピン配置図 (144 ピン LQFP)

92CM27-4 2005-04-12

## 2.2 ピン名称と機能

入出力ピンの名称と機能は次のとおりです。

表 2.2.1 ピン名称と機能(1/5)

| ピン名称      | ピン数   | 入出力           | 機能                                           |

|-----------|-------|---------------|----------------------------------------------|

| D0 ~ D7   | 8     | 入出力           | データ(下位): データバス D0~D7                         |

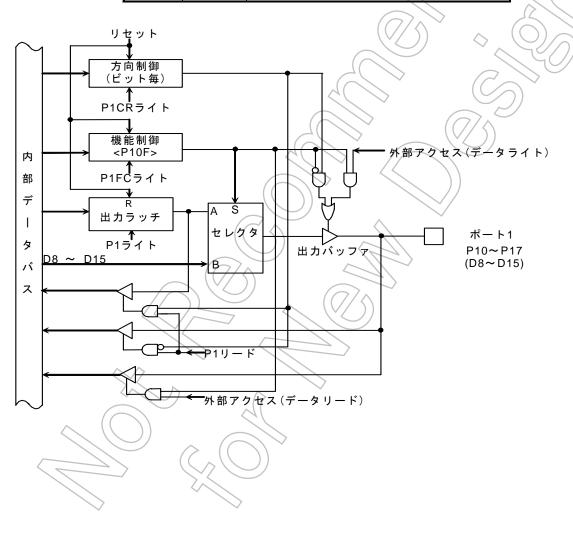

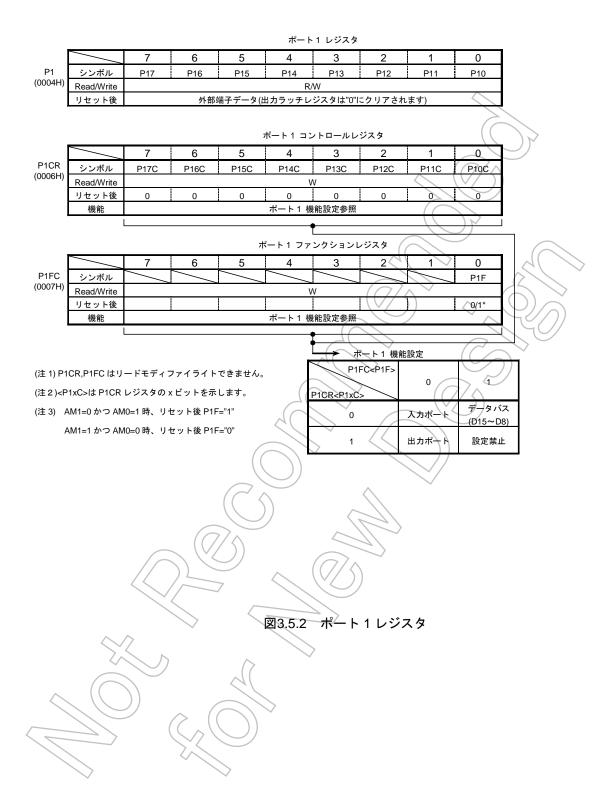

| P10 ~ P17 | 8     | 入出力           | ポート 1: ビット単位で入出力の設定可能な入出力ポート                 |

| D8 ~ D15  |       | 入出力           | データ(上位): データバス D8~D15                        |

| A0 ~ A7   | 8     | 出力            | アドレス: アドレスバス A0~A7                           |

| A8 ~ A15  | 8     | 出力            | アドレス: アドレスバス A8~A15                          |

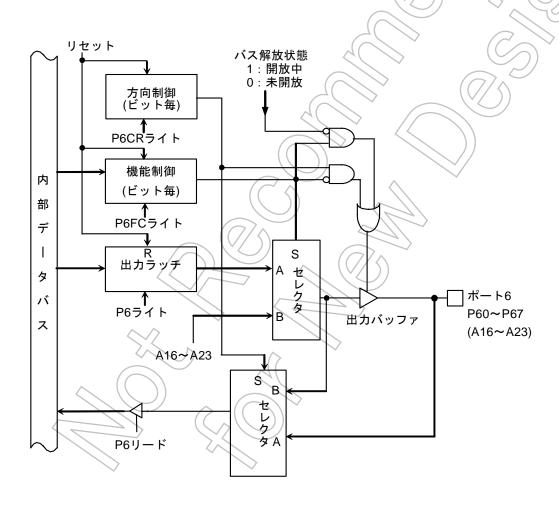

| P60 ~ P67 | 8     | 入出力           | ポート 6: 入出力ポート                                |

| A16 ~ A23 |       | 出力            | アドレス: アドレスバス A16~A23                         |

| RD        | 1     | 出力            | リード: 外部メモリをリードするためのストローブ信号(プルアップ抵抗付き)        |

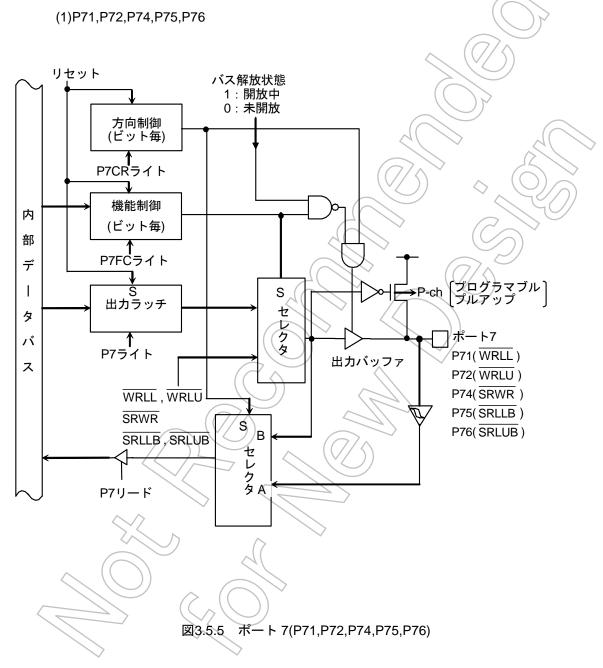

| P71       | 1     | 入出力           | ポート 71: 入出カポート(シュミット入力,プルアップ抵抗付き)            |

| WRLL      |       | 出力            | ライト: D0~D7 端子のデータをライトするためのストローブ信号            |

| P72       | 1     | 入出力           | ポート 72: 入出カポート(シュミット入力,プルアップ抵抗付き)            |

| WRLU      |       | 出力            | 上位ライト: D8~D15 端子のデータをライトするためのストローブ信号         |

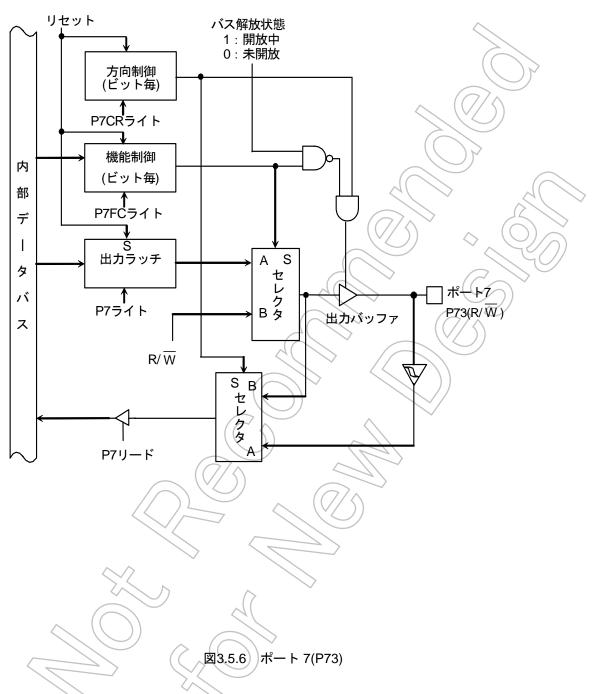

| P73       | 1     | 入出力           | ポート 73: 入出カポート (シュミット入力)                     |

| R/W       |       | 出力            | リード/ライト: 1 はリード,ダミーサイクルを、0 はライトサイクルを表す       |

| P74       | 1     | 入出力           | ポート 74: 入出カポート(シュミット入力,プルアップ抵抗付き)            |

| SRWR      |       | 出力            | SRAM 用ライトイネーブル:データ書き込み用ストロ→ブ信号               |

| P75       | 1     | 入出力           | ポート 75: 入出力ポート(シュミット入力、プルアップ抵抗付き)            |

| SRLLB     |       | 出力            | D0~D7 端子の SRAM 用データイネーブル                     |

| P76       | 1     | 入出力           | ポート 76: 入出カポート(シュミット入力,プルアップ抵抗付き)            |

| SRLUB     |       | 出力            | D8~D15 端子の SRAM 用データイネーブル                    |

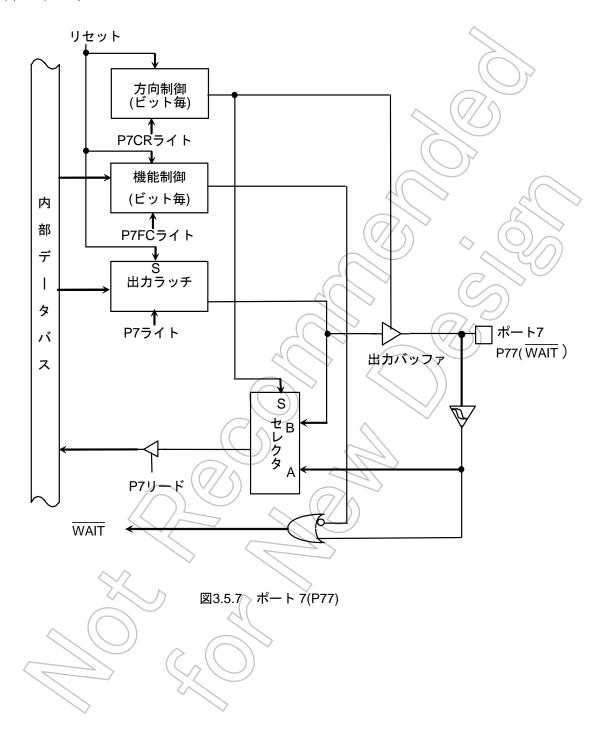

| P77       | 1     | 入出力           | ポート 77: 入出力ポート(シュミット入力)                      |

| WAIT      |       | 入力            | ウェイト: バスウェイトの要求入力端子                          |

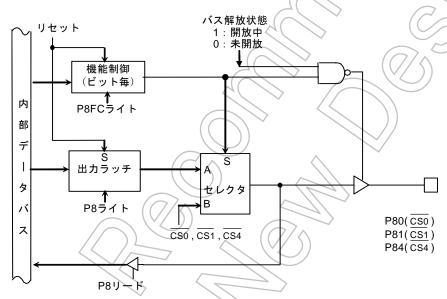

| P80       | 1     | 出力            | ポート 80: 出力ポート                                |

| CS0       |       | 出力            | チップセレクト 0: アドレスが指定したアドレス領域内なら"0"を出力          |

| P81       | 1     | 出力(//         | ポート 81: 出力ポート                                |

| CS1       |       | 出力            | チップセレクト 1: アドレスが指定したアドレス領域内なら"0"を出力          |

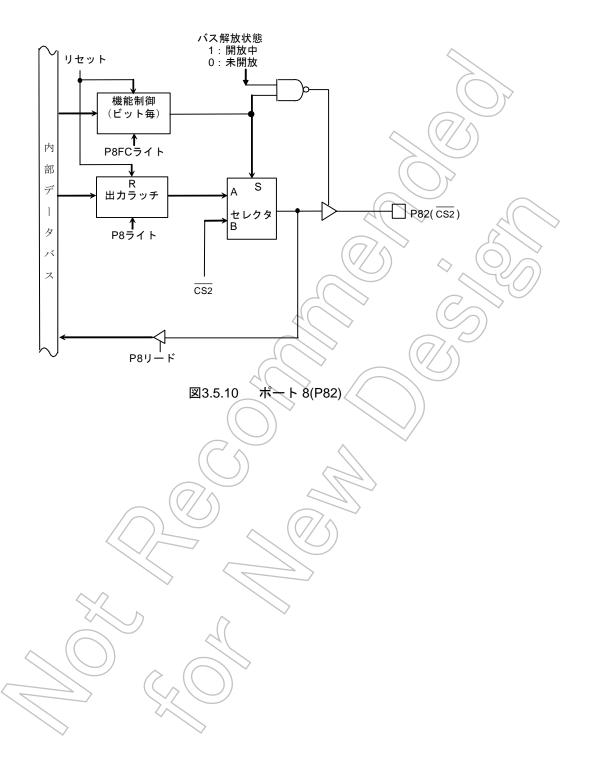

| P82       | 1//   | 出力            | ポート 82: 出力ポート                                |

| CS2       |       | 出力            | チップセレクト 2: アドレスが指定したアドレス領域内なら"0"を出力          |

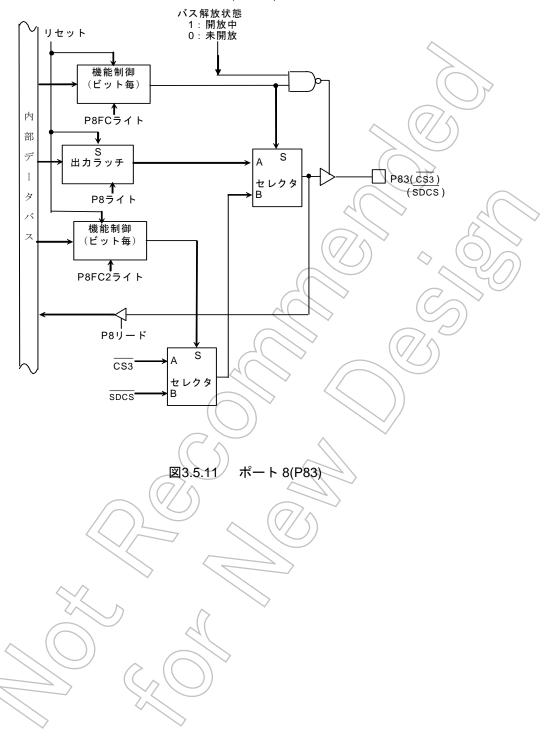

| P83       | 1     | 出力            | ポート 83: 出力ポート                                |

| CS3       | ^ ^   | 出力            | チップセレクト 3: アドレスが指定したアドレス領域内なら"0"を出力          |

| SDCS      |       | 出力            | SDRAM チップセレクト: アドレスが SDRAM アドレス領域内なら "0" を出力 |

| P84       | )<br> | <i>/</i> / 出力 | ポート 84: 出力ポート                                |

| CS4       |       | 出力            | チップセレクト 4: アドレスが指定したアドレス領域内なら"0"を出力          |

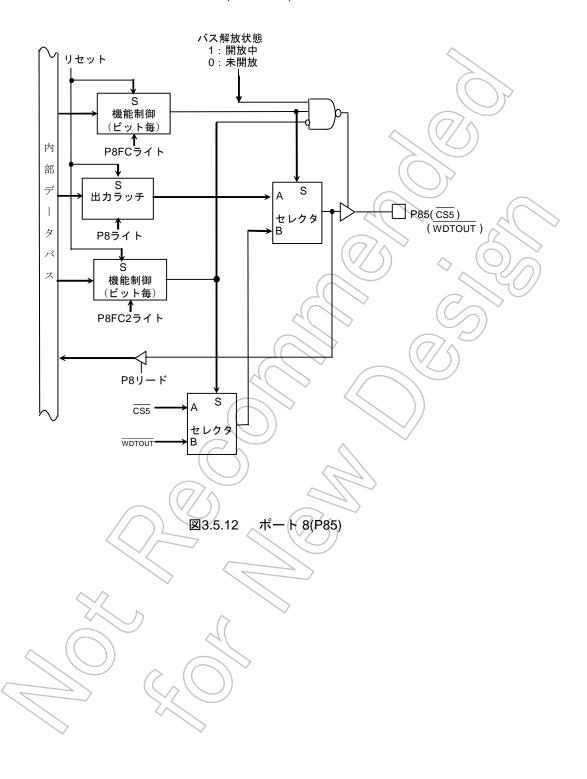

| P85       | 1)    | 出力            | ポート 85: 出力ポート                                |

| CS5       |       | (出力 ((        | チップセレクト 5: アドレスが指定したアドレス領域内なら"0"を出力          |

| WDTOUT    |       | 出力〉           | ウォッチドッグタイマ出力                                 |

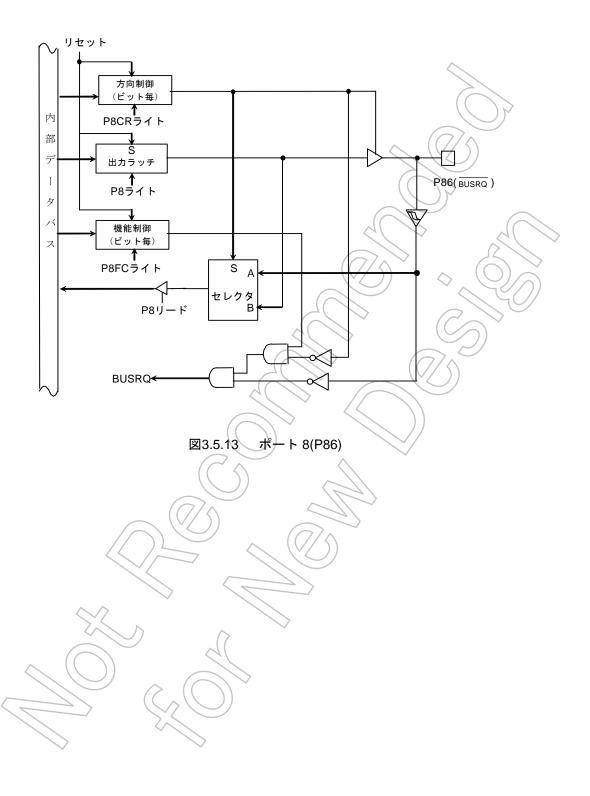

| P86       | 1     | 入出力           | ポート 86: 入出力ポート(シュミット入力)                      |

| BUSRQ     |       | 入力            | バスリクエスト: 外部メモリバスをハイインピーダンスにすることを要求する         |

|           |       |               | 端子(外付け DMAC 用)                               |

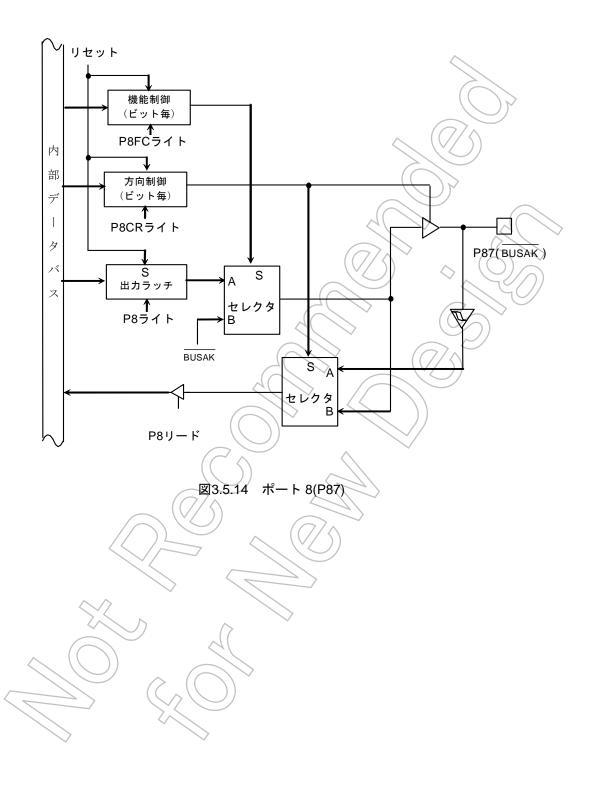

| P87       | 1     | 入出力           | ポート 87: 入出カポート(シュミット入力)                      |

| BUSAK     |       | 出力            | バスアクノリッジ: BUSRQ を受けて外部メモリバス端子が、ハイインピーダンス     |

|           |       |               | になったことを示す端子(外付け DMAC 用)                      |

### 表 2.2.2 ピン名称と機能(2/5)

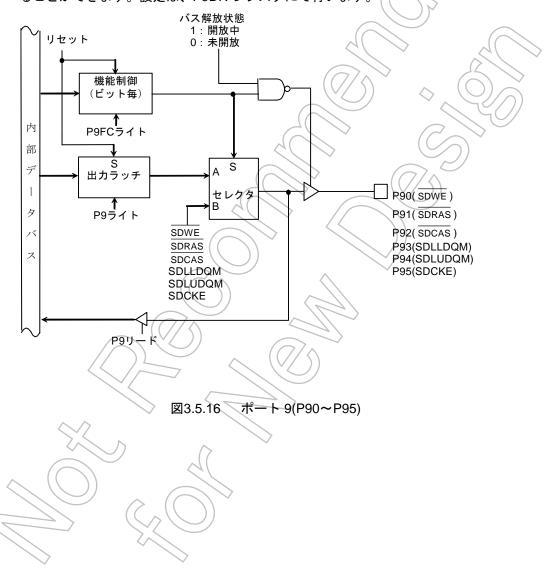

| P90       1       出力       ポート 90: 出力ポート         SDWE       出力       SDRAM 用ライトイネーブル         P91       1       出力       ポート 91: 出力ポート         SDRAS       出力       SDRAM 用ロウアドレスストローブ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| P91 1 出力 ポート 91: 出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | l             |

| P91 1 出力 ポート 91: 出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

| GBITATE TO THE TOTAL THE TOTAL TO THE TOTAL THE TOTAL TO |               |

| P92 1 出力 ポート 92: 出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

| 950.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

| P93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

| SDLLDQM   出力   D0~D7 端子の SDRAM 用データイネーブル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

| P94   1   出力   ポート 94: 出力ポート   1   出力   ポート 94: 出力ポート   1   1   1   1   1   1   1   1   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| SDLUDQM 出力 D8~D15 端子の SDRAM 用データイネーブル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

| P95 1 出力 ポート 95: 出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

| SDCKE 出力 SDRAM用クロックイネーブル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

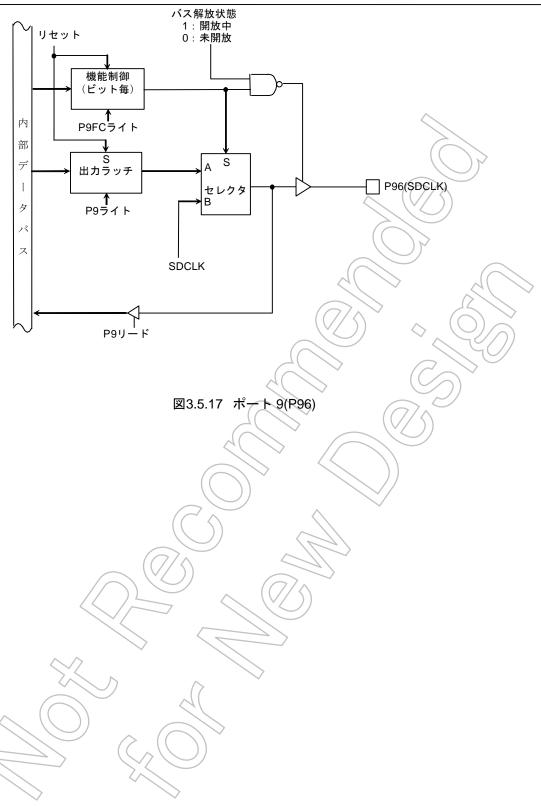

| P96   1   出力   ポート 96: 出力ポート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| SDCLK 出力 SDRAM用クロック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\rightarrow$ |

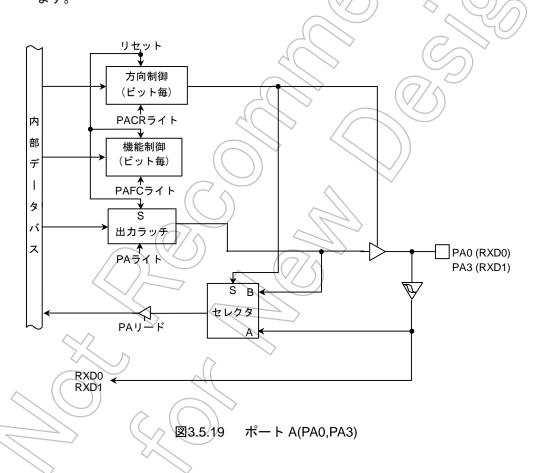

| PA0       1       入出力       ポート A0: 入出力ポート (シュミット入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| RXD0         入力         シリアル受信データ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

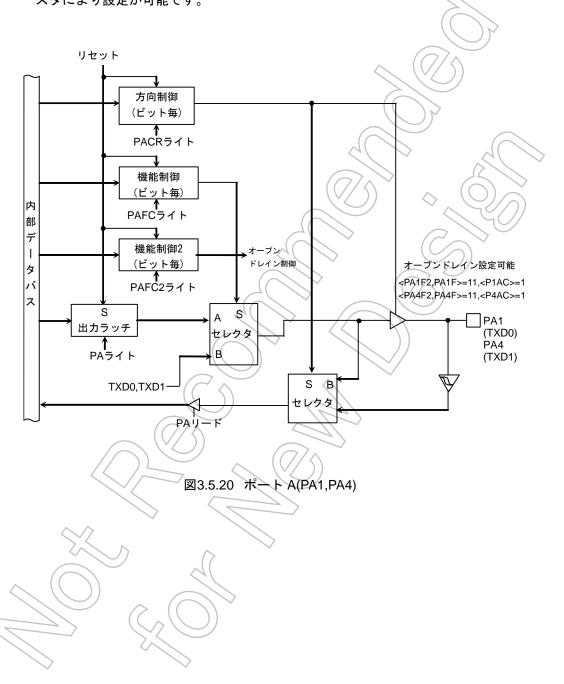

| PA1       1       入出力       ポート A1: 入出力ポート (シュミット入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| TXD0 出力 シリアル送信データ 0: プログラムによりオープンドレイン出力可能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

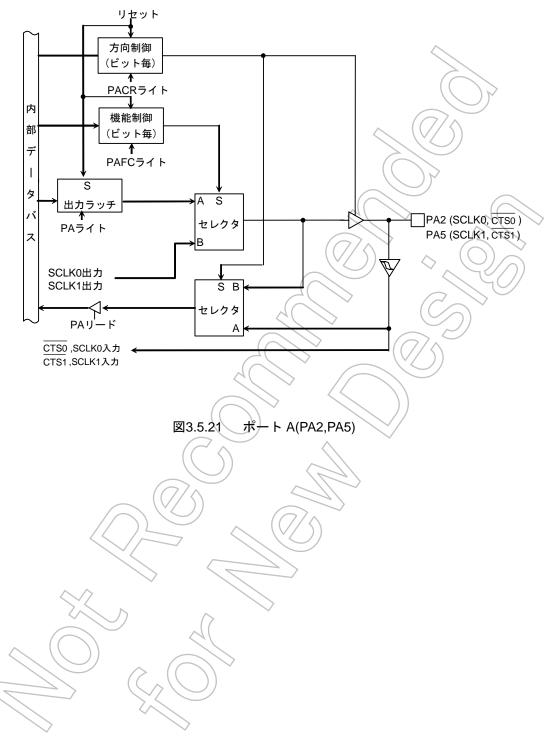

| PA2       1       入出力       ポート A2: 入出力ポート (シュミット入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| SCLK0 入出力 シリアルクロック入出力 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

| CTS0   入力   シリアルデータ送信可能 0 (Clear To Send)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| PA3 1 入出力 ポート A3: 入出力ポート(シュミット入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

| RXD1         入力         シリアル受信データ 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

| PA4 1 入出力 ポート A4:入出力ポート(シュミット入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

| TXD1 出力 シリアル送信データ 1: プログラムによりオープンドレイン出力可能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| PA5       1       入出力       ポート A5: 入出力ポート (シュミット入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| SCLK1 入出力 シリアルクロック入出力 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

| CTS1 入力 シリアルデータ送信可能 1 (Clear To Send)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

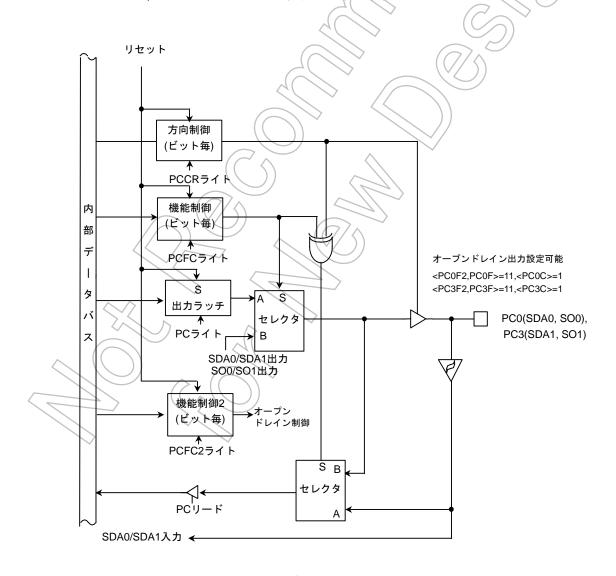

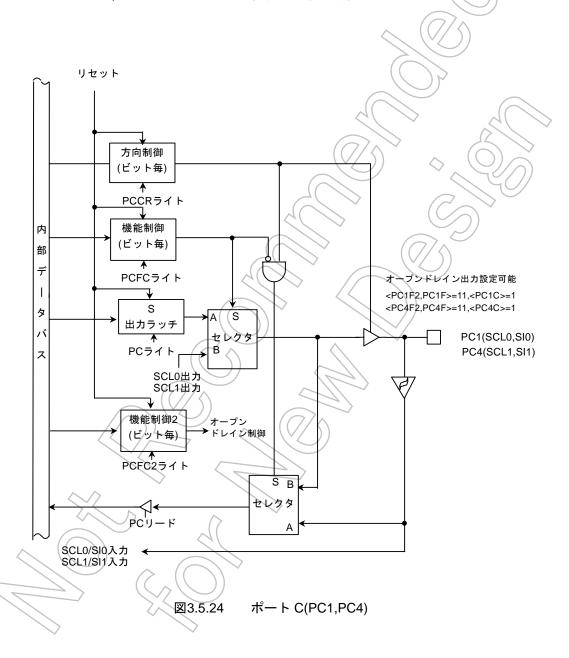

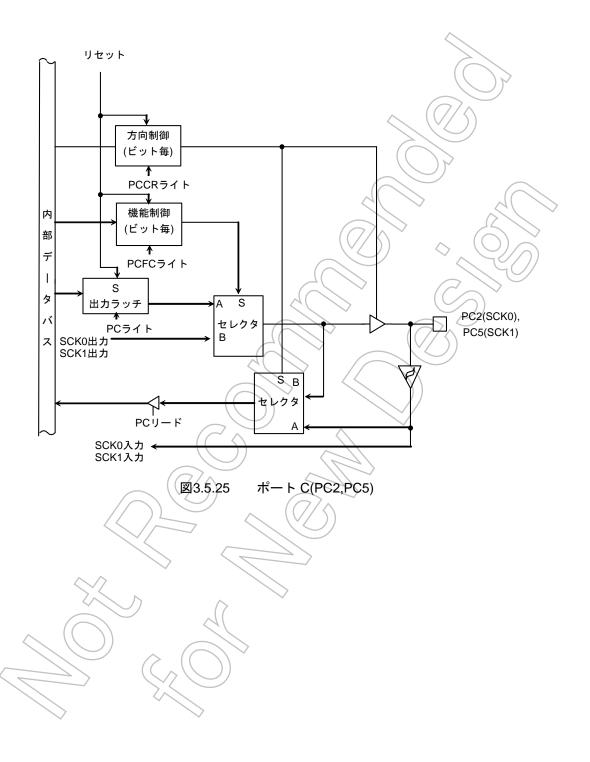

| PC0 1 入出力 ポート C0: 入出力ポート (シュミット入力)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| SOO 出力 シリアルバスインターフェース 0 の SIO モード時のデータ送信端子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| SDA0   入出力 / シリアルバスインターフェース 0 の I <sup>2</sup> C モード時のデータ送受信端子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

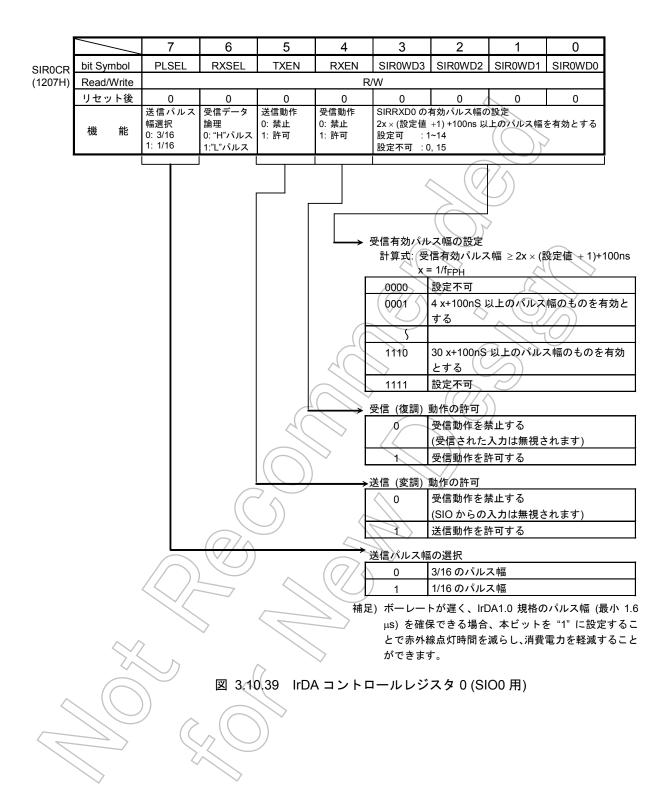

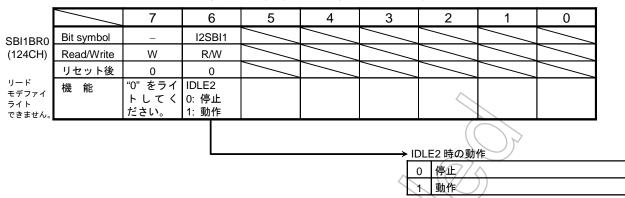

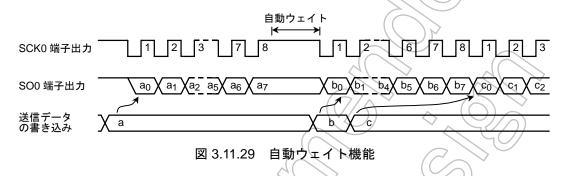

| プログラムによりオープンドレイン出力可能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |