CMOS Digital Integrated Circuit Silicon Monolithic

## TC358764XBG/TC358765XBG

#### **Mobile Peripheral Devices**

### Overview

The primary function of TC358764XBG/TC358765XBG is DSI-to-LVDS Bridge, enabling video streaming output over DSI link to drive LVDS-compatible display panels. The chip supports up to 1366×768 24-bit pixel resolution for single-link LVDS and up to WUXGA (1920x1200 18-bit pixels) resolution for dual-link LVDS. As a secondary function, the chip also supports an I<sup>2</sup>C Master which is controlled by the DSI link; this may be used as an interface to any other control functions through I<sup>2</sup>C. The chip can be configured through the DSI link by sending write register commands through DSI Generic Long Write-packets. It can also be configured through the I<sup>2</sup>C Slave interface.

### Features

#### • DSI Receiver

- ♦ Configurable 1- up to 4-Data-Lane DSI Link with bi-directional support on Data Lane 0

- ♦ Maximum bit rate of 800 Mbps/lane

- $\diamond$  Video input data formats:

- RGB565 16 bits per pixel

- RGB666 18 bits per pixel

- RGB666 loosely packed 24 bits per pixel

- RGB888 24 bits per pixel.

- $\diamond$  Video frame size:

- Up to 1366×768 24-bit/pixel resolution to single-link LVDS display panel

- Up to WUXGA resolutions (1920×1200 18-bit pixels) to dual-link LVDS display panel

- Supports Video Stream packets for video data transmission.

- Supports generic long packets for accessing the chip's register set

- Supports the path for Host to control the on-chip I<sup>2</sup>C Master

#### • LVDS FPD Link Transmitter

- ♦ Supports single-link or dual-link

- ♦ Maximum pixel clock frequency of 85 MHz

- Maximum throughput of 297.5 MBytes/sec for single-link or 595 Mbytes/sec for/dual-link

- Supports display up to 1366×768 24-bit/pixel resolution for single-link, or up to WUXGA (18 bit/pixel) resolutions for dual-link

- ♦ Supports the following pixel formats:

- RGB666 18 bits per pixel

- RGB888 24 bits per pixel

- ♦ Flexible mapping of parallel data input bit ordering

- ♦ Supports power-down

#### System Operation

- ♦ Host configures the chip through DSI link

- Through DSL link, Host accesses the chip register set using Generic Write and Read packets. One Generic Long Write packet can write to multiple contiguous register addresses

- Includes an I<sup>2</sup>C Master function which is controlled by Host through DSI link (multi-master is not supported)

- $\diamond$  (Power management features to save power

- ☆ Configuration registers is also accessible through I<sup>2</sup>C Slave interface

- I C Slave intern

### Clock Source

- $\bigstar$  LVDS pixel clock source is either from external

- ) clock EXTCLK or derived from DSICLK.

- ♦ A built-in PLL generates the high-speed LVDS serializing clock requiring no external components

#### Digital Input/Output Signals

- ♦ All Digital Input signals are 3.3V tolerant

- All Digital Output signals can output ranging from 1.8V to 3.3V depending on IO supply voltage

#### • Power supply

- ♦ MIPI<sup>®</sup> DSI D-PHY: 1.2 V

- ♦ LVDS PHY: 3.3 V

- ♦ I/O: 1.8 V 3.3V (all IO supply pins must be same level)

- ♦ Digital Core: 1.2 V

#### • Power Consumption

- $\diamond$  Power –down mode is achieved by:

- Disable PLL (0x04A0[8] = 1) and LVDS (0x049C[0] = 0) after stopping video stream (in DSI LP11 state)

- 2. Drive DSI Data Lanes to LP00 state

- 3. Stop DSIClk and/or RefClk

## TOSHIBA

$\diamond$  Power-down mode : Power Consumption: to 55  $\mu$ W

| - DSI-RX:  | 10.39 µA |

|------------|----------|

| LUDG 1 OV. | 2 10 4   |

| - LVDS_1.2V: | 3.10 µA  |

|--------------|----------|

| - LVDS_3.3V: | 0.015 µA |

- CORE: 31.96 µA

- IOs\_1.8V: 0.15 µA

- ♦ Normal Operation (2-DSI Data lane @ 200 MHz, Single LVDS @ 27 MHz): to 157.58 mW

- DSI-RX 2 lanes 8.25 mA

- 42.68 mA

- LVDS\_3.3V:

- LVDS\_1.2V: 1.25 mA

- CORE 4.34 mA - IOs\_1.8V 0.067 mA

- ♦ Normal Operation (2-DSI Data lane @ 314 MHz, Dual LVDS @ 44.25 MHz each): to 259.16 mW

- DSI-RX 2 lanes: 9.77 mA

- LVDS\_3.3V: 69.63 mA

- LVDS\_1.2V: 7.78 mA

- CORE: 6.83 mA

- IOs\_1.8V: 0.061 mA

### **Packaging Information**

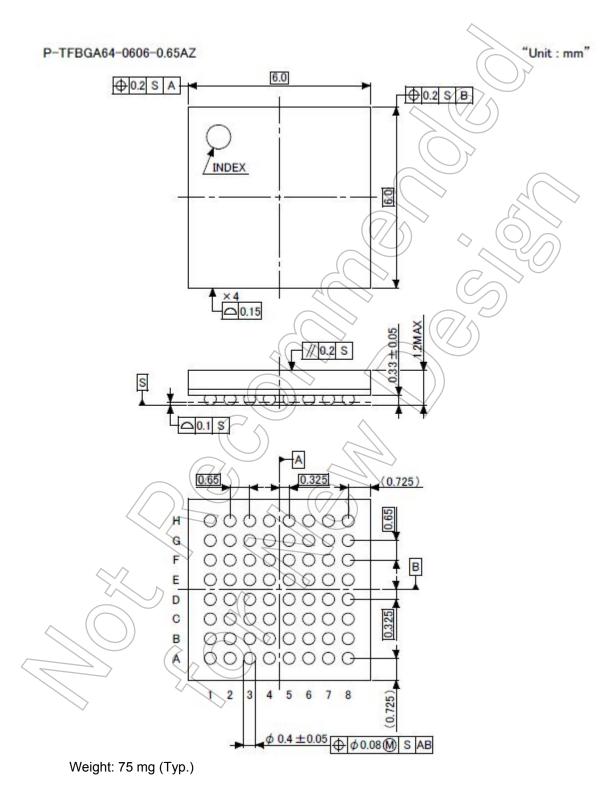

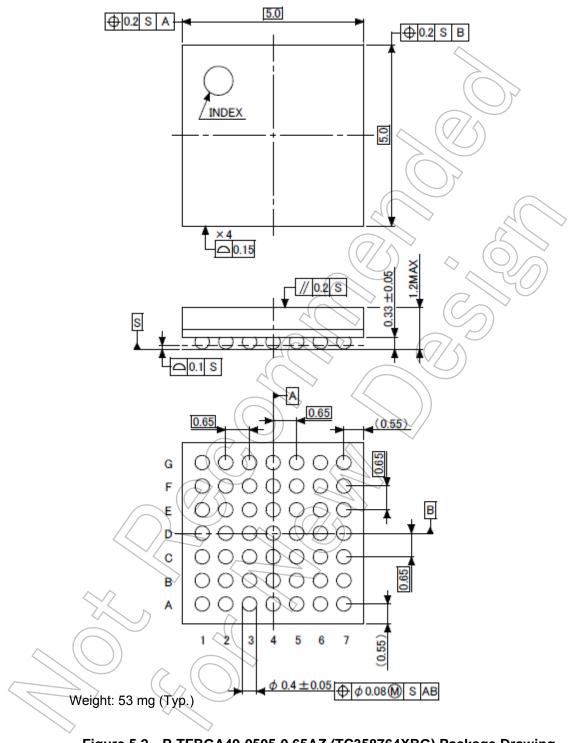

- ♦ TC358765XBG : BGA64 (0.65mm ball pitch) - Supports DSI-RX 4-data-lanes + Dual-Link LVDS-TX

- 6.0mm  $\times 6.0$ mm  $\times 1.2$ mm

- ♦ TC358764XBG : BGA49 (0.65mm ball pitch)

- Supports DSI-RX 4-data-lanes + Single-Link LVDS-TX

- 5.0mm  $\times 5.0$ mm  $\times 1.2$ mm

## Table of content

| REFERENCES                                     | 8  |

|------------------------------------------------|----|

| 1. Introduction                                | 9  |

| 1.1. Scope                                     | 9  |

| 1.2. Purpose                                   | 9  |

| 2. Device Overview                             | 10 |

| 3. Features                                    | 11 |

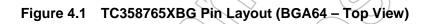

| 4. Pin Layout                                  | 13 |

| 4.1. TC358765XBG BGA64 Pin-out Description     | 14 |

| 4.2. TC358765XBG BGA64 Pin Count Summary       | 15 |

|                                                | 16 |

| 4.4. TC358764XBG BGA49 Pin Count Summary       | 17 |

| 5. Package                                     |    |

| 6. Electrical characteristics                  | 20 |

| 6.1. Absolute Maximum Ratings                  | 20 |

| 6.2. Operating Conditions                      | 21 |

| 6.3. DC Electrical Specification               | 22 |

| 6.3.1. Normal CMOS I/Os DC Specifications      | 22 |

| 6.3.2. DSI Differential I/Os DC Specifications | 22 |

| 6.3.2.1. LP Transmitter                        |    |

| 6.3.2.2. HS Receiver                           |    |

| 6.3.2.3. LP Receiver                           | 23 |

| 6.3.3. LVDS Transmitter DC Specifications      | 24 |

| 6.3.4. LVDS Transmitter Supply Current         | 24 |

| 7. Revision History                            | 25 |

| RESTRICTIONS ON PRODUCT USE                    | 26 |

|                                                |    |

## Table of Figures

**TOSHIBA**

| Figure 4.1<br>Figure 4.2<br>Figure 5.1<br>Figure 5.2 | TC358765XBG Pin Layout (BGA64 – Top View)<br>TC358764XBG Pin Layout (BGA49 – Top View)<br>P-TFBGA64-0606-0.65AZ (TC358765XBG) Package Drawing<br>P-TFBGA49-0505-0.65AZ (TC358764XBG) Package Drawing                                            | 13<br>18 |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                      |                                                                                                                                                                                                                                                 |          |

|                                                      | List of Tables                                                                                                                                                                                                                                  |          |

| Table 4.1<br>Table 4.2                               | TC358765XBG BGA64 Pin Count Summary                                                                                                                                                                                                             | 15<br>17 |

| Table 5.1                                            | DSI-TO-LVDS Package Information Summary                                                                                                                                                                                                         | 19       |

| Table 6.1<br>Table 6.2                               | TC358765XBG BGA64 Pin Count Summary<br>TC358764XBG BGA49 Pin Count Summary<br>DSI-TO-LVDS Package Information Summary<br>Absolute Maximum Ratings<br>TC358764XBG Operating Conditions                                                           | 20<br>21 |

| Table 6.3<br>Table 6.4                               | TC358765XBG Operating Conditions<br>TC358765XBG Operating Conditions<br>Normal CMOS IOs DC Specifications<br>DSI LP Transmitter DC Specifications<br>DSI HS Receiver DC Specifications<br>DSI LP Receiver DC Specifications<br>Revision History | 21       |

| Table 6.5                                            | DSI LP Transmitter DC Specifications                                                                                                                                                                                                            | 22       |

| Table 6.6<br>Table 6.7                               | DSI HS Receiver DC Specifications                                                                                                                                                                                                               | 23<br>23 |

| Table 7.1                                            | Revision History                                                                                                                                                                                                                                | 25       |

|                                                      |                                                                                                                                                                                                                                                 |          |

• MIPI is a trademark of MIPI Alliance, Inc.

**TOSHIBA**

• All other company names, product names, and service names may be trademarks of their respective companies.

#### **1** NOTICE OF DISCLAIMER

- 2 The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled

- 3 by any of the authors or developers of this material or MIPI<sup>®</sup>. The material contained herein is provided on

- 4 an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS

- 5 AND WITH ALL FAULTS, and the authors and developers of this material and MIPI<sup>®</sup> hereby disclaim all

- 6 other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if

- 7 any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of

- 8 accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of

- 9 negligence.

- 10 All materials contained herein are protected by copyright laws, and may not be reproduced, republished,

- 11 distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express

- 12 prior written permission of MIPI<sup>®</sup> Alliance. MIPI<sup>®</sup>, MIPI<sup>®</sup> Alliance and the dotted rainbow arch and all related

- 13 trademarks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance and

- 14 cannot be used without its express prior written permission.

- 15 ALSO, THERE IS NO WARRANTY OF CONDITION OF TITLE, QUIET ENJOYMENT, QUIET

- 16 POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD

- 17 TO THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT. IN NO EVENT WILL ANY

- 18 AUTHOR OR DEVELOPER OF THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT OR

- 19 MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE

- 20 GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL,

- 21 CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER

- 22 CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR

- 23 ANY OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL,

- 24 WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH

- 25 DAMAGES.

- 26 Without limiting the generality of this Disclaimer stated above, the user of the contents of this Document is

- 27 further notified that MIPI<sup>®</sup>: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the

- 28 contents of this Document; (b) does not monitor or enforce compliance with the contents of this Document;

- and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance

- 30 with the contents of this Document. The use or implementation of the contents of this Document may

- 31 involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents,

- 32 patent applications, or copyrights owned by one or more parties, whether or not Members of MIPI<sup>®</sup>. MIPI<sup>®</sup>

- 33 does not make any search or investigation for IPR, nor does MIPI<sup>®</sup> require or request the disclosure of any

- 34 IPR or claims of IPR as respects the contents of this Document or otherwise.

- 35 Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

- 36 MIPI<sup>®</sup> Alliance, Inc.

- 37 c/o IEEE-ISTO

- 38 445 Hoes Lane

- 39 Piscataway, NJ 08854

- 40 Attn: Board Secretary

## TOSHIBA

## Precautions and Usage Considerations Specific to Application Specific Standard Products and General-Purpose Linear Ics

#### Design

#### **A** CAUTION

Use an appropriate power supply fuse to ensure that a large current does not continuously flow in case of over current and/or IC failure. The IC will fully break down when used under conditions that exceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and the breakdown can lead smoke or ignition. To minimize the effects of the flow of a large current in case of breakdown, appropriate settings, such as fuse capacity, fusing time and insertion circuit location, are required.

If your design includes an inductive load such as a motor coil, incorporate a protection circuit into the design to prevent device malfunction or breakdown caused by the current resulting from the inrush current at power ON or the negative current resulting from the back electromotive force at power OFF. For details on how to connect a protection circuit such as a current limiting resistor or back electromotive force adsorption diode, refer to individual IC datasheets or the IC databook. IC breakdown may cause injury, smoke or ignition.

Use a stable power supply with ICs with built-in protection functions. If the power supply is unstable, the protection function may not operate, causing IC breakdown. IC breakdown may cause injury, smoke or ignition.

Carefully select external components (such as inputs and negative feedback capacitors) and load components (such as speakers), for example, power amp and regulator.

If there is a large amount of leakage current such as input or negative feedback condenser, the IC output DC voltage will increase. If this output voltage is connected to a speaker with low input withstand voltage, overcurrent or IC failure can cause smoke or ignition. (The over current can cause smoke or ignition from the IC itself.) In particular, please pay attention when using a Bridge Tied Load (BTL) connection type IC that inputs output DC voltage to a speaker directly.

#### Over current Protection Circuit

Over current protection circuits (referred to as current limiter circuits) do not necessarily protect ICs under all circumstances. If the Over current protection circuits operate against the over current, clear the over current status immediately.

Depending on the method of use and usage conditions, such as exceeding absolute maximum ratings can cause the over current protection circuit to not operate properly or IC breakdown before operation. In addition, depending on the method of use and usage conditions, if over current continues to flow for a long time after operation, the IC may generate heat resulting in breakdown.

#### Thermal Shutdown Circuit

Thermal shutdown circuits do not necessarily protect ICs under all circumstances. If the Thermal shutdown circuits operate against the over temperature, clear the heat generation status immediately.

Depending on the method of use and usage conditions, such as exceeding absolute maximum ratings can cause the thermal shutdown circuit to not operate properly or IC breakdown before operation.

Heat Radiation Design

When using an IC with large current flow such as power amp, regulator or driver, please design the device so that heat is appropriately radiated, not to exceed the specified junction temperature (T<sub>J</sub>) at any time and condition. These ICs generate heat even during normal use. An inadequate IC heat radiation design can lead to decrease in IC life, deterioration of IC characteristics or IC breakdown. In addition, please design the device taking into considerate the effect of IC heat radiation with peripheral components.

#### Mounting

#### Installation to Heat Sink

Please install the power IC to the heat sink not to apply excessive mechanical stress to the IC. Excessive mechanical stress can lead to package cracks, resulting in a reduction in reliability or breakdown of internal IC chip. In addition, depending on the IC, the use of silicon rubber may be prohibited. Check whether the use of silicon rubber is prohibited for the IC you intend to use, or not. For details of power IC heat radiation design and heat sink installation, refer to individual technical datasheets or IC databooks.

Also please refer to "RESTRICTIONS ON PRODUCT USE".

## REFERENCES

- MIPI<sup>®</sup> D-PHY, "DRAFT MIPI<sup>®</sup> Alliance Specification for D-PHY Version 0.91.00 r0.01 14-March-2008"

MIPI<sup>®</sup> Alliance Specification for DSI version 1.01, Feb 2008

- 3. MIPI<sup>®</sup> Alliance Specification for DPI version 2.0, Sep, 2005

- 4. An Introduction to FPD-Link, AN-1032, Application Note, National Semiconductor 2009

- 5. DS90C383/DS90CF384 LVDS Transmitter 24-Bit FPD Link, Data Sheet, National Semiconductor 2000

- 6. THC63LVD823 Single/Dual Link LVDS Transmitter, Data Sheet, Thine Electronics, 2000-2003.

- 7. SN75LVDS83 FlatLink Transmitter, Data Sheet, Texas Instrument, 1997-2009.

- 8. Toshiba LVDS183 CMOS5LA (TC320) 3.3V Cell Information, V1r2, 9/8/2008

- 9. Toshiba Dual Link LVDS Transmitter CMOS5LA 85MHz Application Note, V. 1.5, 12/2/2008

## 1. Introduction

The TC358764XBG/TC358765XBG Functional Specification defines operation of the DSI-to-LVDS chip.

The primary function of this chip is DSI-to-LVDS Bridge, enabling video streaming output over DSI link to drive LVDS-compatible display panels. The chip supports up to  $1366 \times 768$  24-bit pixel resolution for single-link LVDS and up to WUXGA ( $1920 \times 1200$  18-bit pixels) resolution for dual-link LVDS. As a secondary function, the chip also supports an I<sup>2</sup>C Master which is controlled by the DSI link; this may be used as an interface to any other control functions through I<sup>2</sup>C.

The chip can be configured through the DSI link by sending write register commands through DSI Generic Long Write-packets. It can also be configured through the I<sup>2</sup>C Slave interface.

This specification provides description of two chip versions:

TC358764XBG: In BGA49 package, it supports DSI-RX with up to 4 data lanes, and outputs to Single-Link LVDS.

TC358765XBG: In BGA64 package, it supports DSI-RX with up to 4 data lanes, and outputs to Dual-Link LVDS.

## 1.1. Scope

This document details the operation of the chip, description of each major function that the chip supports, description of the configuration register set, and includes pinout, package, and electrical characteristics information.

## 1.2. Purpose

This document serves as the vehicle for exchanging detailed technical information of the DSI-TO-LVDS chip and its usage within the target application systems at the customer side. It also serves as the chip functional specification for design implementation and verification.

## 2. Device Overview

The DSI-TO-LVDS chip functions primarily as a DSI-to-LVDS communication protocol bridge, enabling video streaming from a Host processor over DSI link to drive LVDS-compatible display panels. In other words, the chip receives video stream input through its DSI receiver (DSI-RX), buffers the received pixel data in a buffer, and then re-transmits the video stream out through the LVDS transmitter.

As a secondary function, the chip also ports an  $I^2C$  Master which is controlled by the DSI link; this may be used as a programming interface to other peripherals in the system.

The chip is configured through the DSI link. Alternatively, it can optionally be configured through the I<sup>2</sup>C Slave interface; in such case, the I<sup>2</sup>C Master function would be disabled.

The reference video pixel clock for the LVDS link is sourced either from an external clock via input pin EXTCLK or derived from DSICLK. The chip integrates a PLL which synthesizes the high-speed clock for use solely to serialize video data over the LVDS link.

The DSI-RX receiver supports from 1- to 4-Lane configurations at bit rate up to 800 Mbps per lane. Host can transmit video in video mode. In video mode, Host controls video timing by sending video frame and line sync events together with video pixel data; video data transmission can be burst or non-burst. Since the chip integrates only 1024-pixel of video buffer, Host still has to take care of transmitting pixel data at appropriate video line time in order to avoid buffer overflow (or underflow).

The LVDS transmitter supports a clock frequency of up to 85 MHz for either single- or dual-link. Correspondingly, the LVDS throughput is up to 297.5 Mbytes/sec for single-link or 595 Mbytes/sec for dual-link.

The chip supports power management to conserve power when its functions are not in use. Host manages the chip's power consumption modes by using ULPS messages over DSI link.

## TOSHIBA

## 3. Features

- DSI Receiver

- ♦ Configurable 1- up to 4-Data-Lane DSI Link with bi-directional support on Data Lane 0

- ♦ Maximum bit rate of 800 Mbps/lane

- $\diamond$  Video input data formats:

- RGB565 16 bits per pixel

- RGB666 18 bits per pixel

- RGB666 loosely packed 24 bits per pixel

- RGB888 24 bits per pixel

- $\diamond$  Video frame size:

- Up to 1366×768 24-bit/pixel resolution to single-link LVDS display panel

- Up to WUXGA resolutions (1920×1200 18-bit pixels) to dual-link LVDS display panel

- ♦ Supports Video Stream packets for video data transmission.

- ♦ Supports generic long packets for accessing the chip's register set

- $\diamond$  Supports the path for Host to control the on-chip  $\int^2 C$  Master

#### • LVDS FPD Link Transmitter

- ♦ Supports single-link or dual-link

- ♦ Maximum pixel clock frequency of 85 MHz

- Maximum throughput of 297.5 MBytes/sec for single-link or 595 Mbytes/sec for dual-link

- Supports display up to 1366×768 24-bit/pixel resolution for single-link, or up to WUXGA (18 bit/pixel) resolutions for dual-link

- ♦ Supports the following pixel formats:

- RGB666 18 bits per pixel

- RGB888 24 bits per pixel.

- ✤ Features Toshiba Magic Square algorithm which enables a RGB666 display panel to produce a display quality equivalent to that of an RGB888 24-bit panel

- ♦ Flexible mapping of parallel data input bit ordering

- ♦ Supports power-down

#### • System Operation

♦ Host configures the chip through DSI link

Through DSI link, Host accesses the chip register set using Generic Write and Read packets. One Generic Long Write packet can write to multiple contiguous register addresses

- Includes an I<sup>2</sup>C Master function which is controlled by Host through DSI link (multi-master is not supported)

- ♦ Power management features to save power

- $\diamond$  Configuration registers is also accessible through I<sup>2</sup>C Slave interface

#### • Clock Source

- ♦ LVDS pixel clock source is either from external clock EXTCLK or derived from DSICLK.

- ♦ A built-in PLL generates the high-speed LVDS serializing clock requiring no external components

**Digital Input/Output Signals**

- ∻ All Digital Input signals are 3.3V tolerant

- ∻ All Digital Output signals can output ranging from 1.8V to 3.3V depending on IO supply voltage

- **Power supply**

- MIPI<sup>®</sup> DSI D-PHY: ∻ 1.2 V

- ∻ LVDS PHY: 3.3 V

- ∻ I/O:

1.8 V - 3.3V (all IO supply pins must be same level)

- Digital Core: ∻

- **Power** Consumption

- Power -down mode is achieved by: ∻

- 1. Disable PLL (0x04A0[8] = 1) and LVDS  $(0x049C[0] \neq 0)$  after stopping video stream (in DSI LP11 state)

- 2. Drive DSI Data Lanes to LP00 state

- 3. Stop DSIClk and/or RefClk

- Power-down mode : Power Consumption: to 55 µW ∻

0.15 µA

1.2 V

- 10.39 µA DSI-RX:

- 3.10 µA LVDS 1.2V:

- LVDS 3.3V: 0.015 µA 31.96 µA

- CORE:

- IOs\_1.8V:

- Normal Operation (2-DSI Data lane @ 200 MHz, Single LVDS @ 27 MHz): to 157.58 mW ∻

- **DSI-RX 2 lanes** 8.25 mA

- LVDS 3.3V: 42.68 mA \_

- LVDS 1.2V: 1.25 mA \_

- 4.34 mA CORE:

- 0.067 mA IOs\_1.8V;

- (2-DSI Data lane @ 314 MHz, Dual LVDS @ 44.25 MHz each): to 259.16 mW Normal Operation ∻ DSI-RX 2 lanes 9.77 mA

- LVDS 3.3V: 69.63 mA

- LVDS\_1.2V: 7.78 mA \_

- CORE:

- 6.83 mA 0.061 mA IOs\_1.8V:

- **Packaging Information**

- TC358765XBG : BGA64 (0.65mm ball pitch) ∻

- Supports DSI-RX 4-data-lanes + Dual-Link LVDS-TX

- 6.0mm × 6.0mm × 1.2mm

- ∻ TC358764XBG : BGA49 (0.65mm ball pitch)

- Supports DSI-RX 4-data-lanes + Single-Link LVDS-TX

- 5.0mm  $\times 5.0$ mm  $\times 1.2$ mm

Note: Attention about ESD. This product is weak against ESD. Please handle it carefully.

## 4. Pin Layout

| A1           | A2     | A3      | A4      | A5           | A6           | A7           | A8           |

|--------------|--------|---------|---------|--------------|--------------|--------------|--------------|

| VSS_LVDS2_12 | LVTX2A | LVTX2B  | LVTX2C  | LVTX2DN      | LVTX2EN      | VSS_LVDS2_33 | VSS_LVDS1_12 |

| B1           | B2     | B3      | B4      | B5           | B6           | B7           | B8           |

| VDD_LVDS2_12 | LVTX2A | LVTX2B  | LVTX2C  | LVTX2DP      | LVTX2EP      | VDD_LVDS2_33 | VDD_LVDS1_12 |

| C1           | C2     | C3      | C4      | C5           | C6           | 67           | C8           |

| VSSI         | VDDI   | GPIO    | GPIO3   | VDD_LVDS2_33 | VSS_LVDS2_33 | LVTX1AP      | LVTX1AN      |

| D1           | D2     | D3      | D4      | D5           | <b>(D6</b> ) | D7           | D8           |

| EXTCL        | GPIO   | GPIO    | RESX    | ТМ           | VDD_LVDS1_33 | LVTX1BP      | LVTX1BN      |

| E1           | E2     | E3      | E4      | E5           | E6           | E7           | E8           |

| VSS          | VDD    | GPIO    | VDDC    | VSSC         | VSS_LVDS1_3  | LVTX1CP      | LVTX1CN      |

| F1           | F2     | F3      | F4      | F5           | <b>F6</b>    | F7 (         | <b>F8</b>    |

| VSSI         | VDDI   | VDD_MIP | VSS_MIP | VSS_MIP      | VDD_MIPI     | LVTX1DP      | LVTX1DN      |

| G1           | G2     | G3      | G4      | G5           | G6           | G7           | G8           |

| I2C_SCL      | DSRXD0 | DSRXD1  | DSRXC   | DSRXD2P      | DSRXD3P      | LVTX1EP      | LVTX1EN      |

| H1           | H2     | H3      | H4      | H5           | H6           |              | () Н8        |

| I2C_SD       | DSRXD0 | DSRXD1  | DSRXC   | DSRXD2M      | DSRXD3M      | VDD_LVDS1_33 | VSS_LVDS1_33 |

|         |         | $\frown$ |          |              |              |              |

|---------|---------|----------|----------|--------------|--------------|--------------|

| A1      | A2      | A3       | A4       | A5           | A6           | A7           |

| VSSIO   | VDDIO   | RESX     | GPIO0    | VSSC         | VDDC         | VSSC         |

| B1      | B2      | B3       | B4 <     | B5           | B6           | B7           |

| EXTCLK  | VDDC    | VSSC     | TM       | VDD_LVDS1_12 | LVTX1AP      | LVTX1AN      |

| C1      | C2      | C3       | C4       | C5           | C6           | C7           |

| I2C_SDA | GPIO3   | GPIO2    | GPIO1    | VSS_LVDS1_12 | LVTX1BP      | LVTX1BN      |

| D1      | D2      | D3       | D4       | ✓ D5         | D6           | D7           |

| I2C_SCL | GPIØ4   | VSS_MIPI | VDD_MIPI | VSS_LVDS1_33 | LVTX1CP      | LVTX1CN      |

| E1      | E2      | E3       | E4       | E5           | E6           | E7           |

| VDDIO   | VSSIO   | VSS_MIPI | VDD_MIPI | VDD_LVDS1_33 | LVTX1DP      | LVTX1DN      |

| F1      | F2 🗸    | F3       | F4       | F5           | F6           | F7           |

| DSRXD0P | DSRXD1P | DSRXCP   | DSRXD2P  | DSRXD3P      | LVTX1EP      | LVTX1EN      |

| G1      | G2      | G3       | G4       | G5           | G6           | G7           |

| DSRXD0M | DSRXD1M | DSRXCM   | DSRXD2M  | DSRXD3M      | VDD_LVDS1_33 | VSS_LVDS1_33 |

|         |         |          |          |              |              |              |

## Figure 4.2 TC358764XBG Pin Layout (BGA49 – Top View)

## 4.1. TC358765XBG BGA64 Pin-out Description

| Group               | Pin Name     | Ю Туре   | Pin<br>Cnt. | Description                                             | Power<br>Supply<br>Voltage |

|---------------------|--------------|----------|-------------|---------------------------------------------------------|----------------------------|

|                     | DSRXCP       | DSI-PHY  | 1           | DSI clock signal - positive                             | 1.2 V                      |

|                     | DSRXCM       | DSI-PHY  | 1           | DSI clock signal - negative                             | 1.2 V                      |

|                     | DSRXD0P      | DSI-PHY  | 1           | DSI data lane 0 - positive                              | 1.2 V                      |

|                     | DSRXD0M      | DSI-PHY  | 1           | DSI data lane 0 - negative                              | 1.2 V                      |

|                     | DSRXD1P      | DSI-PHY  | 1           | DSI data lane 1 - positive                              | 1.2 V                      |

| DSI-RX              | DSRXD1M      | DSI-PHY  | 1           | DSI data lane 1 - negative                              | 1.2 V                      |

| IF                  | DSRXD2P      | DSI-PHY  | 1           | DSI data lane 2 - positive                              | 1.2 V                      |

|                     | DSRXD2M      | DSI-PHY  | 1           | DSI data lane 2 - negative                              | 1.2 V                      |

|                     | DSRXD3P      | DSI-PHY  | 1           | DSI data lane 3 - positive                              | 1.2 V                      |

|                     | DSRXD3M      | DSI-PHY  | 1           | DSI data lane 3 – negative                              | 1.2 V                      |

|                     | VDD_MIPI     | Power    | 2           | MIPI <sup>®</sup> Analog Power Supply                   | 1.2 V                      |

|                     | VSS_MIPI     | Ground   | 2           | MIPI <sup>®</sup> Analog Ground                         | GND                        |

|                     | LVTX1AP      | LVDS-PHY | 1           | LVDS first-link data channel A - positive               | 3.3 V                      |

|                     | LVTX1AN      | LVDS-PHY | 1           | LVDS first-link data channel A - negative               | 3.3 V                      |

|                     | LVTX1BP      | LVDS-PHY | 1           | LVDS first-link data channel B - positive               | 3.3 V                      |

|                     | LVTX1BN      | LVDS-PHY | 1 (         | LVDS first-link data channel B - negative               | 3.3 V                      |

|                     | LVTX1CP      | LVDS-PHY | 1           | LVDS first-link data channel C - positive               | 3.3 V                      |

|                     | LVTX1CN      | LVDS-PHY | T           | LVDS first-link data channel C - negative               | 3.3 V                      |

| 1st-Link<br>LVDS-TX | LVTX1DP      | LVDS-PHY |             | VDS first-link data channel D (Clock) - positive        | 3.3 V                      |

| IF                  | LVTX1DN      | LVDS-PHY |             | LVDS first-link data channel D (Clock) - negative       | 3.3 V                      |

|                     | LVTX1EP      | LVDS-PHY | ))1         | LVDS first-link data channel E - positive               | 3.3 V                      |

|                     | LVTX1EN      | LVDS-PHY | 1           | LVDS first-link data channel E – negative               | 3.3 V                      |

|                     | VDD_LVDS1_33 | Power    | 2           | First-link LVDS 3.3V Power Supply                       | 3.3 V                      |

|                     | VSS_LVDS1_33 | Ground   | 2           | First-link LVDS 3.3V Ground                             | GND                        |

|                     | VDD_LVDS1_12 | Power    | 1           | First-link LVDS 1.2V Power Supply                       | 1.2 V                      |

|                     | VSS_LVDS1_12 | Ground   | _1_         | First-link LVDS 1.2V Ground                             | GND                        |

|                     | LVTX2AP      | LVDS-PHY | Ź           | LVDS second-link data channel A - positive              | 3.3 V                      |

|                     | LVTX2AN      | LVDS-PHY | 1           | LVDS second-link data channel A - negative              | 3.3 V                      |

|                     | LVTX2BP      | LVDS-PHY | 1           | LVDS second-link data channel B - positive              | 3.3 V                      |

|                     | LVTX2BN      | LVDS-PHY | 1           | LVDS second-link data channel B - negative              | 3.3 V                      |

| 4                   | LVTX2CP      | LVDS-PHY | >1          | LVDS second-link data channel C - positive              | 3.3 V                      |

|                     | LVTX2CN      | LVDS-PHY | ) 1         | LVDS second-link data channel C - negative              | 3.3 V                      |

| 2nd-Link            | LVTX2DP      | LVDS-PHY | 1           | LVDS second-link data channel D (Clock) - positive      | 3.3 V                      |

| LVDS-TX<br>IF       | LVTX2DN      | LVDS-PHY | 1           | LVDS second-link data channel D (Clock) - negative      | 3.3 V                      |

|                     | LVTX2EP      | LVDS-PHY | 1           | LVDS second-link data channel E - positive              | 3.3 V                      |

|                     | LVTX2EN      | LVDS-PHY | 1           | LVDS second-link data channel E – negative              | 3.3 V                      |

|                     | VDD_LVDS2_33 | Power    | 2           | Second-link LVDS 3.3V Power Supply                      | 3.3 V                      |

|                     | VSS LVDS2 33 | Ground   | 2           | Second-link LVDS 3.3V Ground                            | GND                        |

|                     | VDD LVDS2 12 | Power    | 1           | Second-link LVDS 1.2V Power Supply                      | 1.2 V                      |

|                     | VSS LVDS2 12 | Ground   | 1           | Second-link LVDS 1.2V Ground                            | GND                        |

| I2C IF              | I2C SCL      | S-OD     | 1           | I <sup>2</sup> C Master or Slave interface clock signal | 1.8V-3.3V                  |

|                     | I2C SDA      | S-OD     | 1           | I <sup>2</sup> C Master or Slave interface data signal  | 1.8V-3.3V                  |

## TOSHIBA

| GPIO   | GPIO[4:0] | N <sub>PD</sub> | 5 | GPIO bits 4-0               | 1.8V-3.3V |

|--------|-----------|-----------------|---|-----------------------------|-----------|

|        | RESX      | N               | 1 | Hardware reset, low active  | 1.8V-3.3V |

|        | EXTCLK    | N               | 1 | External pixel clock source | 1.8V-3.3V |

|        | ТМ        | N <sub>PD</sub> | 1 | Test mode select            | 1.8V-3.3V |

| SYSTEM | VDDIO     | Power           | 2 | IO Power Supply             | 1.8-3.3V  |

|        | VSSIO     | Ground          | 2 | IO Ground                   | GND       |

|        | VDDC      | Power           | 2 | Digital Core Power Supply   | 1.2 V     |

|        | VSSC      | Ground          | 2 | Digital Core Ground         | GND       |

### **Buffer Type Abbreviation:**

| N:                | Normal IO                               |    |

|-------------------|-----------------------------------------|----|

| N <sub>PD</sub> : | Normal IO with weak Internal Pull-Dow   | 'n |

| N <sub>PU</sub> : | Normal IO with weak Internal Pull-Up    |    |

| S-OD:             | Pseudo open-drain output, schmitt input |    |

| SCHMIDTT:         | Fail Safe schmitt input buffer          |    |

| DSI-PHY:          | front-end analog IO for DSI             |    |

| LVDS-PHY:         | front-end analog IO for LVDS            |    |

| A:                | Analog pad                              | (  |

## 4.2. TC358765XBG BGA64 Pin Count Summary

| Group Name                       | Pin Count | Notes                       |

|----------------------------------|-----------|-----------------------------|

| DSI-RX IF                        | ))14      | Include DSI Power & Ground  |

| 1st-Link /2nd-Link<br>LVDS-TX IF | 32        | Include LVDS Power & Ground |

| 126 IF                           | 2         | 7/~                         |

| GPIO                             | <5 ((     | $( \neq ) )$                |

| SYSTEM (POWER)                   | 11        |                             |

| Total Pin Count                  | 64        | $\rightarrow$               |

|                                  |           |                             |

## Table 4.1 TC358765XBG BGA64 Pin Count Summary

## 4.3. TC358764XBG Pin-out Description

| Group   | Pin Name     | Ю Туре   | Pin<br>Cnt. | Description                                             | Power<br>Supply<br>Voltage |

|---------|--------------|----------|-------------|---------------------------------------------------------|----------------------------|

|         | DSRXCP       | DSI-PHY  | 1           | DSI clock signal - positive                             | 1.2 V                      |

|         | DSRXCM       | DSI-PHY  | 1           | DSI clock signal - negative                             | 1.2 V                      |

|         | DSRXD0P      | DSI-PHY  | 1           | DSI data lane 0 - positive                              | 1.2 V                      |

|         | DSRXD0M      | DSI-PHY  | 1           | DSI data lane 0 - negative                              | 1.2 V                      |

|         | DSRXD1P      | DSI-PHY  | 1           | DSI data lane 1 - positive                              | 1.2 V                      |

| DSI-RX  | DSRXD1M      | DSI-PHY  | 1           | DSI data lane 1 - negative                              | 1.2 V                      |

| IF      | DSRXD2P      | DSI-PHY  | 1           | DSI data lane 2 - positive                              | 1.2 V                      |

|         | DSRXD2M      | DSI-PHY  | 1           | DSI data lane 2 - negative                              | 1.2 V                      |

|         | DSRXD3P      | DSI-PHY  | 1           | DSI data lane 3 - positive                              | 1.2 V                      |

|         | DSRXD3M      | DSI-PHY  | 1           | DSI data lane 3 - negative                              | 1.2 V                      |

|         | VDD_MIPI     | Power    | 2           | MIPI <sup>®</sup> Analog Power Supply                   | 1.2 V                      |

|         | VSS_MIPI     | Ground   | 2           | MIPI <sup>®</sup> Analog Ground                         | GND                        |

|         | LVTX1AP      | LVDS-PHY | 1           | LVDS first-link data channel A - positive               | 3.3 V                      |

|         | LVTX1AN      | LVDS-PHY | 1           | LVDS first-link data channel A - negative               | 3.3 V                      |

|         | LVTX1BP      | LVDS-PHY | 1           | LVDS first-link data channel B - positive               | 3.3 V                      |

|         | LVTX1BN      | LVDS-PHY | 1 (         | LVDS first-link data channel B - negative               | 3.3 V                      |

|         | LVTX1CP      | LVDS-PHY | 1           | LVDS first-link data channel C - positive               | 3.3 V                      |

|         | LVTX1CN      | LVDS-PHY | A C         | LVDS first-link data channel C - negative               | 3.3 V                      |

| LVDS-TX | LVTX1DP      | LVDS-PHY |             | LVDS first-link data channel D (Clock) - positive       | 3.3 V                      |

| IF      | LVTX1DN      | LVDS-PHY |             | LVDS first-link data channel D (Clock) - negative       | 3.3 V                      |

|         | LVTX1EP      | LVDS-PHY | ))1         | LVDS first-link data channel E - positive               | 3.3 V                      |

|         | LVTX1EN      | LVDS-PHY | 1           | LVDS first-link data channel E – negative               | 3.3 V                      |

|         | VDD_LVDS1_33 | Power    | 2           | First-link LVDS 3.3V Power Supply                       | 3.3 V                      |

|         | VSS_LVDS1_33 | Ground   | 2           | First-link LVDS 3.3V Ground                             | GND                        |

|         | VDD_LVDS1_12 | Power    | $\lambda$   | First-link LVDS 1.2V Power Supply                       | 1.2 V                      |

|         | VSS_LVDS1_12 | Ground   | 1           | First-link LVDS 1.2V Ground                             | GND                        |

| I2C IF  | I2C_SCL      | S-OD     |             | I <sup>2</sup> C Master or Slave interface clock signal | 1.8V-3.3V                  |

|         | I2C_SDA      | S-OD     | 1           | J <sup>2</sup> C Master or Slave interface data signal  | 1.8V-3.3V                  |

| GPIO    | GPIO[4:0]    | N        | 5           | GPIO bits 4-0                                           | 1.8V-3.3V                  |

|         | RESX         | N CI     | 1           | Hardware reset, low active                              | 1.8V-3.3V                  |

|         | EXTCLK       | N        | $>_1$       | External pixel clock source                             | 1.8V-3.3V                  |

|         | TM           | ( $N$    | ) 1         | Test mode select                                        | 1.8V-3.3V                  |

| SYSTEM  | VDDIO        | Power    | 2           | IO Power Supply                                         | 1.8-3.3V                   |

|         | VSSIO        | Ground   | 2           | IO Ground                                               | GND                        |

|         | VDDC         | Power    | 2           | Digital Core Power Supply                               | 1.2 V                      |

|         | VSSC         | Ground   | 3           | Digital Core Ground                                     | GND                        |

### **Buffer Type Abbreviation:**

| N:        | Normal IO                      |

|-----------|--------------------------------|

| SCHMIDTT: | Fail Safe schmitt input buffer |

| LVDS-PHY: | front-end analog IO for LVDS   |

| S-OD:   | Pseudo open-drain output, schmitt input |

|---------|-----------------------------------------|

| DSI-PHY | front-end analog IO for DSI             |

| A:      | Analog pad                              |

## 4.4. TC358764XBG BGA49 Pin Count Summary

| Group Name      | Pin Count | Notes                       |  |  |  |  |

|-----------------|-----------|-----------------------------|--|--|--|--|

| DSI-RX IF       | 14        | Include DSI Power & Ground  |  |  |  |  |

| LVDS-TX IF      | 16        | Include LVDS Power & Ground |  |  |  |  |

| I2C IF          | 2         | - (())?                     |  |  |  |  |

| GPIO            | 5         | -                           |  |  |  |  |

| SYSTEM (POWER)  | 12        | -                           |  |  |  |  |

| Total Pin Count | 49        |                             |  |  |  |  |

|                 |           |                             |  |  |  |  |

#### Table 4.2 TC358764XBG BGA49 Pin Count Summary

## 5. Package

All values are in mm unit.

"Unit : mm"

P-TFBGA49-0505-0.65AZ

### Figure 5.2 P-TFBGA49-0505-0.65AZ (TC358764XBG) Package Drawing

| Table 5.1 | DSI-TO-LVDS Package Information Summary  |

|-----------|------------------------------------------|

|           | bor ro Erbo raonago information caninary |

| Package Type        | Comment            |

|---------------------|--------------------|

| BGA64 (TC358765XBG) | 0.65 mm ball pitch |

| BGA49 (TC358764XBG) | 0.65 mm ball pitch |

## 6. Electrical characteristics

## 6.1. Absolute Maximum Ratings

Operating ambient Temperature range:  $Ta = -30^{\circ}C - +85^{\circ}C$

All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

| Parameter                                            | Symbol                        | Rating                     | Unit |  |  |  |  |

|------------------------------------------------------|-------------------------------|----------------------------|------|--|--|--|--|

| Supply voltage<br>(1.8V – Digital IO)                | VDDIO                         | -0.3 to +3.9               | V    |  |  |  |  |

| Supply voltage<br>(1.2V – Digital Core)              | VDDC                          | -0.3 to +1.8               | <    |  |  |  |  |

| Supply voltage<br>(1.2V – MIPI <sup>®</sup> DSI PHY) | VDD_MIPI                      | -0.3 to +1.8               | <>`v |  |  |  |  |

| Supply voltage<br>(3.3V – LVDS PHY)                  | VDD_LVDS1_33,<br>VDD_LVDS2_33 | -0.3 (to +3.9              | V    |  |  |  |  |

| Supply voltage<br>(1.2V – LVDS PHY)                  | VDD_LVDS1_12<br>VDD_LVDS2_12  | -0.3 to +1.8               | V    |  |  |  |  |

| Input voltage<br>(DSI I/O)                           | V <sub>IN_DSI</sub>           | -0.3 to VDD_MIPI+0.3       | V    |  |  |  |  |

| Output voltage<br>(DSI I/O)                          | Vout_dsi                      | -0.3 to VDD_MIPI+0.3       | V    |  |  |  |  |

| Input voltage<br>(Digital IO)                        | VINJO                         | -0.3 to VDDIO+0.3          | V    |  |  |  |  |

| Output voltage<br>(Digital IO)                       | Vout_io                       | -0.3 to VDDIO+0.3          | V    |  |  |  |  |

| Output voltage<br>(LVDS Driver)                      | V <sub>OUT_LVDS</sub>         | -0.3 to<br>VDD_LVDS_33+0.3 | V    |  |  |  |  |

| Junction temperature                                 | T <sub>i</sub>                | 125                        | °C   |  |  |  |  |

| Storage temperature                                  | T <sub>stg</sub>              | -40 to +125                | °C   |  |  |  |  |

| Table 6.1 | Absolute | Maximum | Ratings |

|-----------|----------|---------|---------|

## 6.2. Operating Conditions

| Parameter                                                        | Symbol          | Min           | Тур.           | Max  | Unit                |  |

|------------------------------------------------------------------|-----------------|---------------|----------------|------|---------------------|--|

| Supply voltage (1.8V – Digital IO)                               | VDDIO           | 1.65          | 1.8            | 1.95 | V                   |  |

| Supply voltage (3.3V – Digital IO)                               | VDDIO           | 3.0           | 3.3            | 3.6  | V                   |  |

| Supply voltage (1.2V – Digital Core)                             | VDDC            | 1.1           | 1.2            | 1.3  | V                   |  |

| Supply voltage (1.2V – LVDS PHY)                                 | VDD_LVDS1_12    | <u>J</u> il ( | 1.2            | 1.3  | V                   |  |

| Supply voltage (3.3V – LVDS PHY)                                 | VDD_LVDS1_33    | 3.0           | 3.3            | 3.6  | V                   |  |

| Supply voltage (1.2V – MIPI <sup>®</sup> -DSI PHY)               | VDD_MIPI        | 1.1           | 1.2            | 1.3  | V                   |  |

| Operating temperature (ambient temperature with voltage applied) | Ta              | -30           | +25            | +85  | °C                  |  |

| Supply Noise Voltage                                             | V <sub>SN</sub> | ) - <         | <u>&gt; _C</u> | 100  | ${\sf mV}_{\sf pp}$ |  |

|                                                                  |                 |               | 2              | ,    |                     |  |

#### Table 6.2 TC358764XBG Operating Conditions

| Table 6.3 TC358765XBG Operating Conditions                       |                                |      |      |      |                  |  |  |

|------------------------------------------------------------------|--------------------------------|------|------|------|------------------|--|--|

| Parameter                                                        | Symbol                         | Min  | Тур. | Max  | Unit             |  |  |

| Supply voltage (1.8V – Digital IO)                               | VDDIO                          | 1.65 | 1.8  | 1.95 | V                |  |  |

| Supply voltage (3.3V – Digital IO)                               |                                | 3.0  | 3.3  | 3.6  | V                |  |  |

| Supply voltage (1.2V – Digital Core)                             | VDDC                           | 11   | 1.2  | 1.3  | V                |  |  |

| Supply voltage (1.2V – LVDS PHY)                                 | VDD_LVD\$1_12<br>VDD_LVD\$2_12 | 1.1  | 1.2  | 1.3  | V                |  |  |

| Supply voltage (3.3V – LVDS PHY)                                 | VDD_LVDS1_33<br>VDD_LVDS2_33   | 3.0  | 3.3  | 3.6  | V                |  |  |

| Supply voltage (1.2V – MIPI <sup>®</sup> -DSI PHY)               | VDD_MIPI                       | 1.1  | 1.2  | 1.3  | V                |  |  |

| Operating temperature (ambient temperature with voltage applied) | Ta                             | -30  | +25  | +85  | °C               |  |  |

| Supply Noise Voltage                                             | V <sub>SN</sub>                | -    | -    | 100  | mV <sub>pp</sub> |  |  |

$\supset$

## 6.3. DC Electrical Specification

All typical values are at normal operating conditions unless otherwise specified.

## 6.3.1. Normal CMOS I/Os DC Specifications

| Table 6.4 Normal CMOS IOs DC Specifications                            |                              |                                     |              |      |              |      |  |  |

|------------------------------------------------------------------------|------------------------------|-------------------------------------|--------------|------|--------------|------|--|--|

| Parameter – CMOS I/Os                                                  | Symbol                       | Conditions                          | Min          | Тур. | Max          | Unit |  |  |

| Input voltage, High level Input<br>Note1                               | V <sub>IH</sub>              | -                                   | 0.7<br>VĐDIO | -    | VDDIO        | V    |  |  |

| Input voltage, Low level Input Note1                                   | V <sub>IL</sub>              | -                                   | )<br>O       | -    | 0.3<br>VDDIO | V    |  |  |

| Input voltage High level<br>CMOS Schmitt Trigger<br>Note 1,2           | V <sub>IHS</sub>             |                                     | 0.7<br>VDDIO | -    | VDDIO        | V    |  |  |

| Input voltage Low level<br>CMOS Schmitt Trigger<br>Note 1,2            | V <sub>ILS</sub>             |                                     |              | Õ    | 0.3<br>VDDIO | V    |  |  |

| Output voltage, High level                                             | V <sub>OH</sub>              | I <sub>OH</sub> = -0.4mA            | 0.8<br>VDDIO | -    | VDDIO        | V    |  |  |

| Output voltage, Low level                                              | V <sub>OL</sub>              | I <sub>OL</sub> = 2mA               | 0            | -    | 0.2<br>VDDIO | V    |  |  |

| Input leakage current, High level<br>on Normal pin or Pull-up I/O pin  | I <sub>ILH1</sub><br>(Note4) | $V_{\rm IN}$ = +VDDIO, VDDIO = 3.6V | -10          | -    | 10           | μA   |  |  |

| Input leakage current, High level<br>on Pull-down I/O pin              | I <sub>ILH2</sub><br>(Note4) | $V_{IN} = +VDDIO, VDDIO = 3.6V$     | -            | -    | 100          | μA   |  |  |

| Input leakage current, Low level<br>On Normal pin or Pull-down I/O pin | I <sub>ILL1</sub><br>(Note5) | V <sub>IN</sub> = 0V, VDDIO = 3.6V  | -10          | -    | 10           | μA   |  |  |

| Input leakage current, Low level<br>On Pull-up I/O pin                 | I <sub>ILL2</sub><br>(Note5) | V <sub>IN</sub> = 0V, VDDIO = 3.6V  | -            | -    | -200         | μA   |  |  |

Note1: Each power source is operating within recommended operating condition.

Note2: Current output value is specified to each IO buffer individually. Output voltage changes with output current value.

Note4: Normal pin or Pull-up I/O pin applied VDDIO supply voltage to Vin (input voltage)

Note5: Normal pin, or Pull-down I/O pin applied VSSIO (0V) to Vin (input voltage)

## 6.3.2. DSI Differential I/Os DC Specifications

## 6.3.2.1. LP Transmitter

The low power transmitter is used for driving the lines in all low-power operating modes. The DC characteristics of the LP transmitter are given below.

| Parameter                              | Symbol           | Min | Тур. | Max | Unit |

|----------------------------------------|------------------|-----|------|-----|------|

| Thevenin output high level             | V <sub>OH</sub>  | 1.1 | 1.2  | 1.3 | V    |

| Thevenin output low level              | V <sub>OL</sub>  | -50 | -    | 50  | mV   |

| Output impedance of the LP transmitter | Z <sub>OLP</sub> | 110 | -    | -   | Ω    |

#### Table 6.5 DSI LP Transmitter DC Specifications

#### 6.3.2.2. HS Receiver

The high-speed receiver is a differential line receiver with a switch able parallel input termination. It is used to receive data during high speed transmission from the host. The DC characteristics of the HS receiver are given below.

| Parameter                                        | Symbol                | Min                      | Тур. | Max | Unit |  |  |  |

|--------------------------------------------------|-----------------------|--------------------------|------|-----|------|--|--|--|

| Common-mode voltage HS receive mode              | V <sub>CMRX(DC)</sub> | 70                       |      | 330 | mV   |  |  |  |

| Differential input high threshold                | V <sub>IDTH</sub>     | - <                      | (7/  | 70  | mV   |  |  |  |

| Differential input low threshold                 | V <sub>IDTL</sub>     | -70                      |      | -   | mV   |  |  |  |

| Single-ended input high voltage                  | V <sub>IHHS</sub>     | Ć                        | )-   | 460 | mV   |  |  |  |

| Single-ended input low voltage                   | V <sub>ILHS</sub>     | -40                      | .)~- | -   | mV   |  |  |  |

| Single-ended threshold for HS termination enable | V <sub>TERM-EN</sub>  |                          |      | 450 | mV   |  |  |  |

| Differential input impedance                     | Z <sub>ID</sub>       | 80                       | 100  | 125 | Ω    |  |  |  |

|                                                  |                       | $( \frown ) \setminus ($ |      |     |      |  |  |  |

#### Table 6.6 DSI HS Receiver DC Specifications

### 6.3.2.3. LP Receiver

The low-power receiver is used to detect the Low-Power state on each pin. It is used to receive data during low speed transmission from the host. The DC characteristics of the LP receiver are given below.

Table 6.7 DSI LP Receiver DC Specifications

| Parameter             | Symbol | Min      | Тур. | Max | Unit |

|-----------------------|--------|----------|------|-----|------|

| Logic 1 input voltage | VjH    | 880      | × -  | -   | mV   |

| Logic 0 input voltage | VIL    | <u> </u> | -    | 550 | mV   |

# TOSHIBA

## 6.3.3. LVDS Transmitter DC Specifications

| Parameter                                                               | Symbol           | Min      | Тур.   | Max      | Unit |

|-------------------------------------------------------------------------|------------------|----------|--------|----------|------|

| Output voltage High Normal range (RLOAD = $100\Omega \pm 1\%$ )         | V <sub>OH</sub>  | -        | ~      | 1600     | mV   |

| Output voltage High Reduced range (RLOAD = $100\Omega \pm 1\%$ )        | V <sub>OH</sub>  | -        | - 2    | 1500     | mV   |

| Output voltage Low Normal range (RLOAD = $100\Omega \pm 1\%$ )          | V <sub>OL</sub>  | 900      | Ō      | <u> </u> | mV   |

| Output voltage Low Reduced range (RLOAD = $100\Omega \pm 1\%$ )         | V <sub>OL</sub>  | 1000 🔷   |        | -        | mV   |

| Output differential voltage Normal (RLOAD = $100\Omega \pm 1\%$ )       | V <sub>od</sub>  | 250      | -<br>T | 450      | mV   |

| Output differential voltage Reduced (RLOAD = $100\Omega \pm 1\%$ )      | V <sub>OD</sub>  | 150      |        | 300      | mV   |

| Output Offset Voltage<br>(Normal and Reduce range)<br>(RLOAD = 100Ω±1%) | V <sub>OS</sub>  | 1125     | 1250   | 1375     | mV   |

| Change in  VOD  between "0" and "1"<br>(RLOAD = 100Ω±1%)                | ΔV <sub>OD</sub> |          | -      | 30       | mV   |

| Output offset voltage<br>(RLOAD = 100Ω±1%)                              | ΔV <sub>OS</sub> | <u> </u> | S      | 25       | mV   |

| Output current<br>(Driver shorted together)                             | Isab             |          |        | 12       | mA   |

| Output current<br>(Driver shorted to ground)                            | Isab, Isb        | -        | -      | 30       | mA   |

## 6.3.4. LVDS Transmitter Supply Current

| (77)                                                                             |                   | $\checkmark$ |      |     |      |

|----------------------------------------------------------------------------------|-------------------|--------------|------|-----|------|

| Parameter                                                                        | Symbol            | Min          | Тур. | Max | Unit |

| Transmitter supply current (Clk + 4 data lanes)<br>(75MHz – 3.3V supply current) | ITCCW             | -            | 45   | 65  | mA   |

| Transmitter power down supply current                                            | I <sub>TCCS</sub> | -            | 5    | 500 | μA   |

## 7. Revision History

| ,        |            |                                                                                    |  |  |

|----------|------------|------------------------------------------------------------------------------------|--|--|

| Revision | Date       | Description                                                                        |  |  |

| 1.281    | 2014-04-21 | Newly released                                                                     |  |  |

| 1.282    | 2016-04-01 | Package's weight is rounding up digits after the decimal point to form an integer. |  |  |

| 1.31a    | 2017-10-13 | Changed header, footer and the last page.<br>Changed corporate name.               |  |  |

| 1.33     | 2018-04-04 | Remove LVDS Clock Polarity function.                                               |  |  |

Table 7.1 Revision History

## **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.

Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances,

including without limitation, the EU RoHS Directive, TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES

OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

## **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**