TOSHIBA Photocoupler IRED & Photo IC

# **TLP558**

Isolated Bus Driver

High Speed Line Receiver

Microprocessor System Interfaces

MOS FET Gate Driver

Transistor Inverter

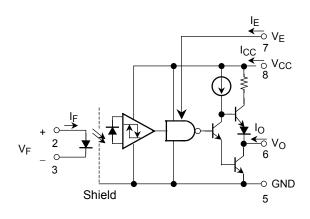

The TOSHIBA TLP558 consists of an infrared emitting diode and integrated high gain, high speed photodetector.

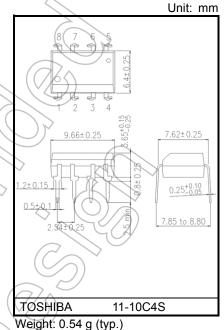

This unit is 8-lead DIP package.

The detector has a three state output stage that provides source drive and sink drive, and built-in schmitt trigger. The detector IC has an internal shield that provides a guaranteed common mode transient immunity of 1000V / µs. TLP558 is inverter logic type. For buffer logic type, TLP555 is in line-up.

- Input current: IF=1.6 mA (max)

- Power supply voltage: VCC=4.5 to 20 V

- Switching speed: tpHL, tpLH=400ns (max)

- Common mode transient immunity: ±1000V/µs (min)/

- Guaranteed performance over temperature: -25 to 85°C

- Isolation voltage: 2500Vrms (min)

- UL-recognized: UL 1577, File No.E67349

- cUL-recognized: CSA Component Acceptance Service

No.5A File No.E67349

### **Truth Table**

| Input | Enable | Output |

|-------|--------|--------|

| Н     | H      |        |

| L     | Н      | Н      |

| Н     | Ĺ      | Z      |

| L     | ⟨\Q    | Z      |

A  $0.1\mu F$  bypass capacitor must be connected between pins 8 and 5.

Weight. 0.54 g (typ.)

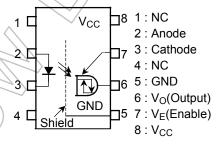

# Pin Configuration (top view)

#### **Schematic**

Start of commercial production 1987-05

# **Absolute Maximum Ratings**

|          | Charactersitic                                        |          | Symbol           | Rating     | Unit  |

|----------|-------------------------------------------------------|----------|------------------|------------|-------|

|          | Forward current                                       |          | lF               | 10         | mA    |

|          | Peak transient forward current                        | (Note 1) | IFPT             | 1          | Α     |

| 쁘        | Reverse voltage                                       |          | VR               | 5          | V     |

|          | Diode power dissipation                               |          | $P_{D}$          | 45         | mW    |

|          | Output current                                        |          | lo               | 40 / -25   | mA    |

|          | Peak output current                                   | (Note 2) | lop              | 80 / -50   | mA    |

|          | Output voltage                                        |          | ⟨Vo (            | -0.5 to 20 | V     |

| or       | Supply voltage                                        |          | Vcc              | -0.5 to 20 | V     |

| Detector | Three state enabel voltage                            |          | VE               | -0.5 to 20 | V     |

| ۵        | Output power dissipation                              |          | Po               | 100        | mW    |

|          | Output power dissipation derating (Ta > 70 °C)        | <        | ΔΡΟ/ΔΤα          | -1.8       | mW/°C |

|          | Total package power dissipation                       | 6        | Рт               | 200        | mW    |

|          | Total package power dissipation derating (Ta > 70 °C) |          | ΔΡΤ/ΔΤα          | -3.6       | mW/°C |

| Оре      | erating temperature range                             |          | T <sub>opr</sub> | -40 to 85  | /,c   |

| Sto      | Storage temperature range                             |          |                  | -55 to 125 | °C    |

| Lea      | d solder temperature(10 s)                            | (Note 3) | T <sub>sol</sub> | 260        | °C    |

| Isol     | ation voltage (AC, 60 s, R.H. ≤ 60 %, Ta=25°C)        | BVs      | 2500             | Vrms       |       |

Note: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/"Derating Concept and Methods") and individual reliability data (i.e. reliability test report and estimated failure rate, etc).

- Note 1: Pulse width  $\leq$  1 µs, 300 pps.

- Note 2: Pulse width  $\leq 5\mu$  s, duty ratio  $\leq 0.025$ .

- Note 3: 1.6 mm below seating plane.

- Note 4: Device considered a two terminal device: Pins 1, 2, 3 and 4 shorted together, and pins 5, 6, 7 and 8 shorted together.

## **Recommended Operating Conditions**

| Characteristic        | Symbol             | Min        | Тур. | Max | Unit |

|-----------------------|--------------------|------------|------|-----|------|

| Input current, on     | I <sub>F(ON)</sub> | 2 (Note 1) | _    | 5   | mA   |

| Input voltage, off    | VF(OFF)            | 0          | _    | 0.8 | V    |

| Supply voltage        | Vcc                | 4.5        | _    | 20  | V    |

| Enable voltage high   | VEH                | 2.0        | _    | 20  | V    |

| Enable voltage low    | V <sub>EL</sub>    | 0          | _    | 0.8 | V    |

| Fan out(TTL load)     | N                  | _          | _    | 4   | _    |

| Operating temperature | T <sub>opr</sub>   | -25        | _    | 85  | °C   |

Note: Recommended operating conditions are given as a design guideline to obtain expected performance of the device. Additionally, each item is an independent guideline respectively. In developing designs using this product, please confirm specified characteristics shown in this document.

Note 1: 2 mA condition permits at least 20 % CTR degradation guardband. Initial switching threshold is 1.6 mA or less.

# Electrical Characteristics (unless otherwise specified, Ta = -25 to 85°C, Vcc = 4.5 to 20V)

| Characteristic                             | Symbol                | Test (                                                              | Min                                      | Тур.             | Max                                                     | Unit    |      |

|--------------------------------------------|-----------------------|---------------------------------------------------------------------|------------------------------------------|------------------|---------------------------------------------------------|---------|------|

| Input forward voltage                      | V <sub>F</sub>        | I <sub>F</sub> = 5 mA, Ta =                                         | _                                        | 1.55             | 1.7                                                     | V       |      |

| Temperature coefficient of forward voltage | ΔV <sub>F</sub> / ΔTa | IF = 5 mA                                                           | _                                        | -2.0             | _                                                       | mV / °C |      |

| Input reverse current                      | I <sub>R</sub>        | V <sub>R</sub> = 5 V, Ta = 2                                        | 5 °C                                     | -                | _                                                       | 10      | μΑ   |

| Input capacitance                          | Ст                    | V <sub>F</sub> = 0 V, f = 1 M                                       | 1Hz, Ta = 25 °C                          | +(               | 45                                                      | ı       | pF   |

| Output leakage current                     | Іонн                  | V                                                                   | V <sub>O</sub> = V <sub>E</sub> = 5.5 V  |                  |                                                         | 100     | μA   |

| (Vo > Vcc)                                 | IONN                  | V <sub>CC</sub> = 4.5 V                                             | V <sub>O</sub> = V <sub>E</sub> = 20 V   | (//-5)           | 0.01                                                    | 500     | μΛ   |

| Logic low output voltage                   | VoL                   | I <sub>OL</sub> = 6.4 mA, I <sub>F</sub><br>V <sub>E</sub> = 2 V    | = 1.6 mA                                 |                  | 0.4                                                     | 0.5     | ٧    |

| Logic high output voltage                  | Voн                   | I <sub>OH</sub> = -2.6 mA, V <sub>E</sub> = 2 V                     | /F = 0.8 V                               | 2.4              | 3.3                                                     | _       | V    |

| Logic low enable current                   | lEL                   | VE = 0.4 V                                                          | 4/ >                                     | _                | -0.13                                                   | -0.32   | mA   |

|                                            |                       | VE = 2.7 V                                                          | V <sub>E</sub> = 2.7 V                   |                  |                                                         | > 20    |      |

| Logic high enable current                  | IEH                   | V <sub>E</sub> = 5.5 V                                              |                                          | ♦- (             | $\mathcal{O}_{\mathcal{I}_{\mathcal{I}_{\mathcal{I}}}}$ | 100     | μΑ   |

|                                            |                       | V <sub>E</sub> = 20 V                                               |                                          |                  | 0.01                                                    | 250     |      |

| Logic low enable voltage                   | VEL                   |                                                                     |                                          | (4               | <u> </u>                                                | 0.8     | V    |

| Logic high enable voltage                  | VEH                   |                                                                     | $\stackrel{\searrow}{}$                  | 2.0              | / —                                                     | _       | V    |

| Logic low supply current                   | Iccl                  | IF = 5 mA                                                           | $V_{CC} = V_E = 5.5 V$                   | 74               | 4.0                                                     | 6.0     | mA   |

|                                            |                       |                                                                     | Vcc = VE = 20 V                          | J}               | 4.6                                                     | 7.5     |      |

| Logic high supply current                  | Іссн                  | VF = 0.V                                                            | $V_{CC} = V_E = 5.5 \text{ V}$           | _                | 4.2                                                     | 6.0     | mA   |

|                                            |                       | 7. 4.                                                               | V <sub>CC</sub> = V <sub>E</sub> = 20 V  | _                | 4.7                                                     | 7.5     |      |

|                                            | IOZL                  | V <sub>E</sub> = 0 V<br>V <sub>E</sub> = 0.8 V                      | V <sub>O</sub> = 0.4 V                   | _                | _                                                       | -20     |      |

| High impedance state output current        | lozh                  | I <sub>F</sub> = 5 mA<br>V <sub>E</sub> = 0.8 V                     | Vo = 2.4 V                               | _                | _                                                       | 20      | μΑ   |

|                                            |                       |                                                                     | V <sub>O</sub> = 5.5 V                   | _                | _                                                       | 100     |      |

|                                            |                       |                                                                     | V <sub>O</sub> = 20 V                    | _                | 1                                                       | 500     |      |

| Logic low short circuit                    | Jost                  | NF = 5 mA                                                           | V <sub>O</sub> = V <sub>CC</sub> = 5.5 V | 25               | 55                                                      | _       | mA   |

| output current (Note 1)                    | 1032                  | VE = 2 V                                                            | V <sub>O</sub> = V <sub>CC</sub> = 20 V  | 40               | 80                                                      | _       | 110. |

| Logic high short circuit                   | Iosh                  | VF = 0 V, VO = 0                                                    | OND VCC = 5.5 V                          | -10              | -25                                                     | _       | - mA |

| output current (Note 1)                    | IOSH                  | V <sub>E</sub> = 2 V                                                | V <sub>CC</sub> = 20 V                   | -25              | -60                                                     | _       |      |

| Input current logic low output             | IFD                   | V <sub>E</sub> = 2 V, I <sub>O</sub> = 6.<br>V <sub>O</sub> < 0.4 V | _                                        | 0.4              | 1.6                                                     | mA      |      |

| Input voltage logic high output            | VFH                   | VE = 2 V, I <sub>O</sub> = -2.6 mA<br>V <sub>O</sub> > 2.4 V        |                                          | 0.8              | _                                                       | _       | V    |

| Input current hysteresis                   | IHYS                  | V <sub>C</sub> C = V <sub>E</sub> = 5 V                             | _                                        | 0.05             | ı                                                       | mA      |      |

| Resistance (input-output)                  | Rs                    | V <sub>S</sub> = 500 V, R.H<br>Ta = 25 °C                           | 5×10 <sup>10</sup>                       | 10 <sup>14</sup> | _                                                       | Ω       |      |

| Capacitance(input-output)                  | Cs                    | V <sub>S</sub> = 0 V, f = 1 N                                       | 1Hz, Ta = 25 °C<br>(Note 2)              | _                | 1.0                                                     | _       | pF   |

Note: All typical values are at Ta = 25 °C, VCC = 5 V, IF(ON) = 3 mA unless otherwise specified.

Note 2: Device considered a two terminal device: Pins 1, 2, 3 and 4 shorted together, and pins 5, 6, 7 and 8 shorted together.

Note 1: Duration of output short circuit time should not exceed 10 ms.

## Switching Characteristics (unless otherwise specified, Vcc = 4.5 to 20V, Ta = 25°C)

| Characteristic                                      |          | Symbol           | Test<br>Circuit | Test Condition                                                                  | Min   | Тур. | Max | Unit   |

|-----------------------------------------------------|----------|------------------|-----------------|---------------------------------------------------------------------------------|-------|------|-----|--------|

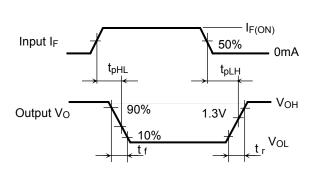

| Propagation delay time to logic high output         | (Note 1) | t <sub>pLH</sub> |                 | I <sub>F</sub> = 3→ 0 mA                                                        | _     | 250  | 400 | ns     |

| Propagation delay time to logic low output          | (Note 1) | t <sub>pHL</sub> | 1               | I <sub>F</sub> = 0→ 3 mA                                                        |       | 270  | 400 | ns     |

| Output rise time (10-90%)                           |          | tr               |                 | I <sub>F</sub> = 3→ 0 mA, V <sub>CC</sub> = 5 V                                 | +     | 35   | 75  | ns     |

| Output fall time (90-10%)                           |          | t <sub>f</sub>   |                 | I <sub>F</sub> = 0→ 3 mA, V <sub>CC</sub> = 5 V                                 |       | 20   | 75  | ns     |

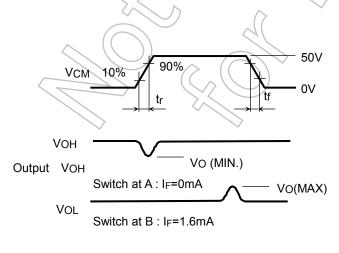

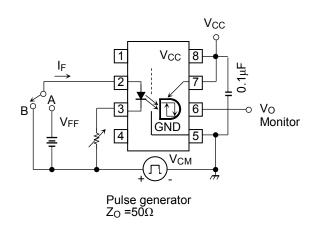

| Common mode transient immunity at logic high output | (Note 2) | Смн              |                 | I <sub>F</sub> = 0 mA, V <sub>CM</sub> = 50 V<br>V <sub>O</sub> (Min) = 2 V     | 1000  | _    | -   | V / µs |

| Common mode transient immunity at logic low output  | (Note 2) | Смь              | 3               | I <sub>F</sub> = 1.6 mA, V <sub>CM</sub> = 50 V<br>V <sub>O (Max)</sub> = 0.8 V | -1000 | _    | -   | V / µs |

Note: All typical values are at Ta = 25 °C, Vcc = 5 V

- Note: A ceramic capacitor (0.1 µF) should be connected from pin 8 to pin 5 to stabilize the operation of the high gain linear amplifier. Failure to provide the bypassing may impair the switching property. The total lead length between capacitor and coupler should not exceed 1cm.

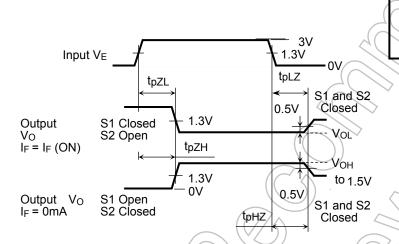

- Note 1: The tpLH propagation delay is measured from the 50 % point on the trailing edge of the input pulse to the 1.3 V point on the leading edge of the output pulse. The tpHL propagation delay is measured from the 50 % point on the leading edge of the input pulse to the 1.3 V point on the trailing edge of the output pulse.

- Note 2: CML is the maximum rate of fall of the common mode voltage that can be sustained with the output voltage in the logic low state (VO < 0.8 V).

CMH is the maximum rate of rise of the common mode voltage that can be sustained with the output voltage in the logic state (VO > 2.0 V).

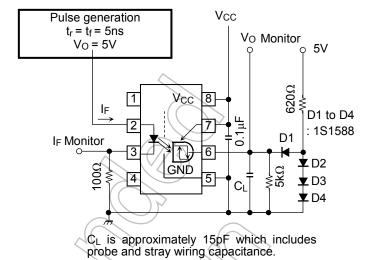

## Test Circuit 1: tplh, tphl, tr and tf

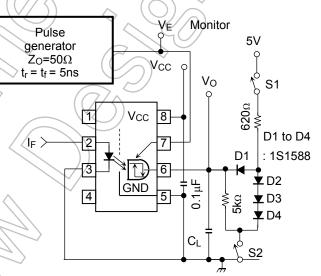

Test Circuit 2: tpHz, tpZH, tpLz and tpZL

C<sub>L</sub> is approximately 15<sub>p</sub>F which includes probe and stray wiring capacitance.

# **Test Circuit 3: Common Mode Transient Immunity**

$$CMH = \frac{45(V)}{tf(\mu s)}, CML = \frac{45(V)}{tf(\mu s)}$$

#### RESTRICTIONS ON PRODUCT USE

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE

EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH

MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT

("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without

limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical

equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to

control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE

PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your

TOSHIBA sales representative or contact us via our website.

- . Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE

FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR

LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND

LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO

SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- GaAs (Gallium Arsenide) is used in Product. GaAs is harmful to humans if consumed or absorbed, whether in the form of dust or vapor. Handle with care and do not break, cut, crush, grind, dissolve chemically or otherwise expose GaAs in Product.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of

Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled

substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES

OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

# **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

https://toshiba.semicon-storage.com/