Bi-CMOS 形リニアー集積回路 シリコン モノリシック

# TB9104FTG

Automotive 1ch H-bridge (2ch Half-bridge) Gate Driver

## 1. 概要

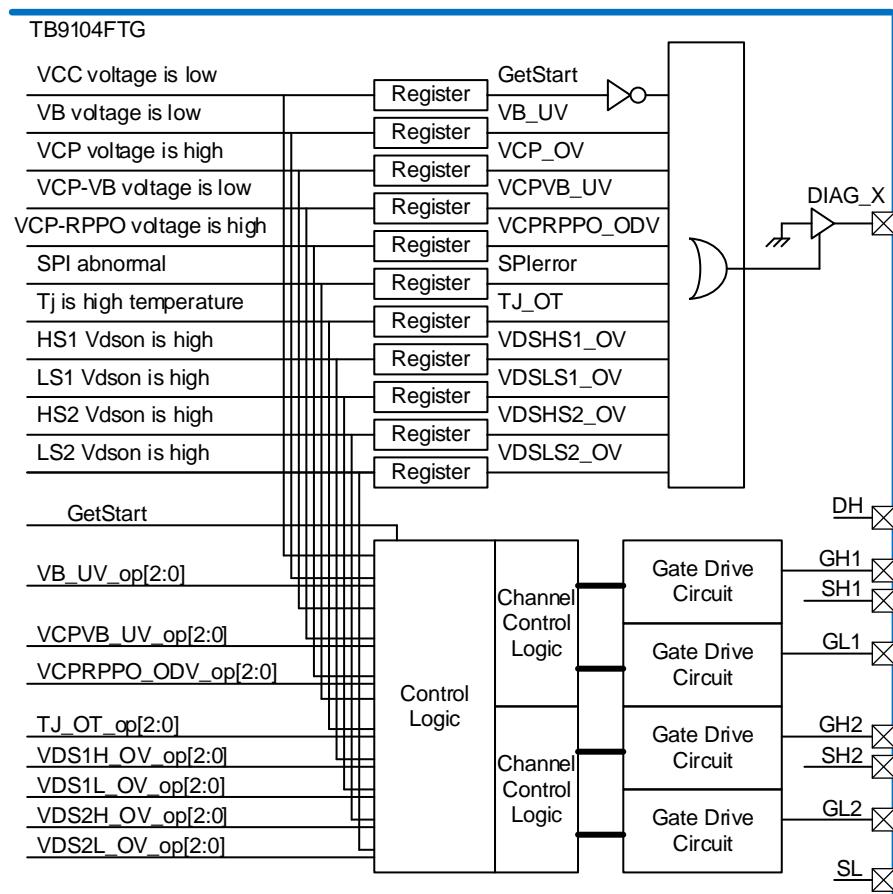

TB9104FTG は、車載用 1 チャネル(ch) H-bridge Gate Driver および 2 チャネル Half-bridge Gate Driver です。スタンバイモードにすることで、低消費電力で待機可能です。チャージポンプ回路、電流センスアンプ、SPI 通信回路、PWM 回路、各種異常検出回路を搭載しています。モーターへの回転の指示は、ピンからの他、SPI からも可能です。

異常検出時は事前の設定に従い、ゲート駆動をシャットダウンし、DIAG\_X 端子から異常を通知する他、SPI 通信を介して詳細な情報を提供します。

## 2. 用途

n 型 MOSFET と組み合わせて使用し、スライドドア、バックドア、シート、ウインドウ、ミラーなどのモーター制御用途に適しています。回転の指示も SPI から制御できますので、複数の IC で配線を共有できます。

## 3. 特長

- スタンバイモード： 低消費電力で動作待機可能

- チャージポンプ搭載： 2 倍昇圧構成。

- バッテリー逆接防止回路へ給電可能

- ゲートドライバー部は 2 モード搭載： ハーフブリッジモード、H ブリッジモード

- ハーフブリッジモードは 2 チャネル使用可能

- チャネルごとに独立してハイサイド、ローサイド MOSFET を時間管理し 貫通電流を防止

- H ブリッジモードはハーフブリッジを組み合わせ 1 チャネルとして使用可能

- 4 つの n 型 MOSFET を時間管理し 貫通電流を防止

- 各種異常検出機能搭載：

- VCC 端子（アナログ系電源）低電圧検出

- VB 端子（バッテリー）低電圧検出

- VCP 端子（チャージポンプ電圧）高電圧検出、昇圧不足検出

- RPPO 端子（外部バッテリー逆接防止回路用電源）異常電圧降下検出

- SPI 異常（フォーマット異常、コマンド違反など）

- 過熱検出

- 外部 n 型 MOSFET、ドレイン、ソース間電圧監視（過電流検出）

- 異常検出時 DIAG\_X 端子から通知

- モーター電流センスアンプ回路内蔵

- オフセットキャリブレーション機能内蔵

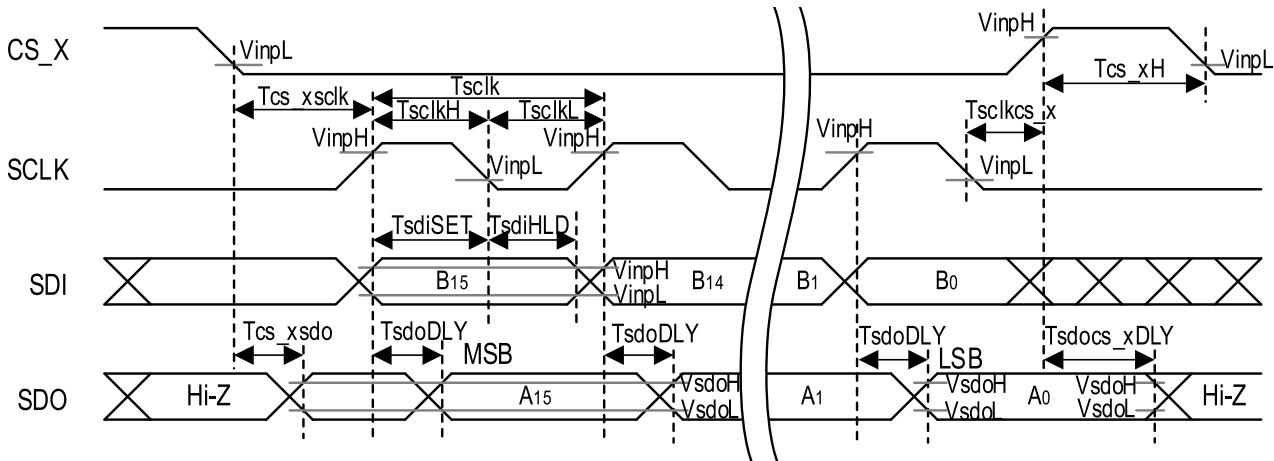

- SPI 通信回路内蔵 SPI からもドライブ指示が可能 H ブリッジモード用 PWM 波形生成回路内蔵

- バッテリー電源(5.7~18V)、MCU 系電源(4.5~5.5V)、アナログ系電源(4.5~5.5V)の 3 電源が必要

- 周囲温度 (Ta) = -40~125°C、ジャンクション温度(Tj) = -40~150°C

- AEC-Q100 グレード 1 適合予定

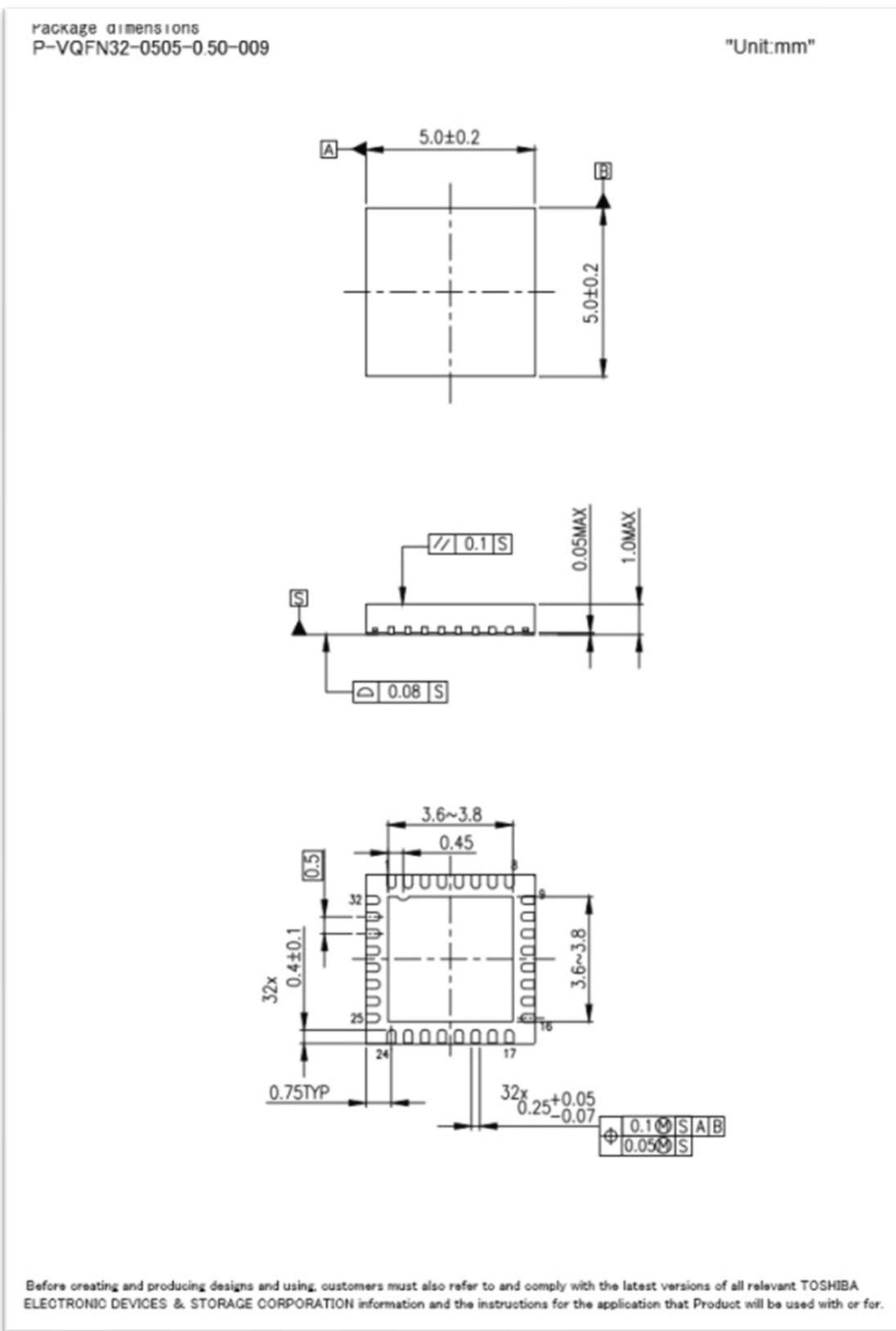

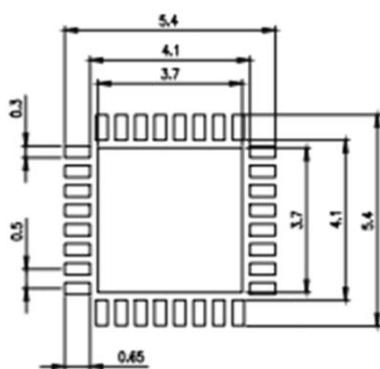

- 小型パッケージ VQFN32 5x5mm

これは参考資料です。本資料での最終機器設計はしないでください。

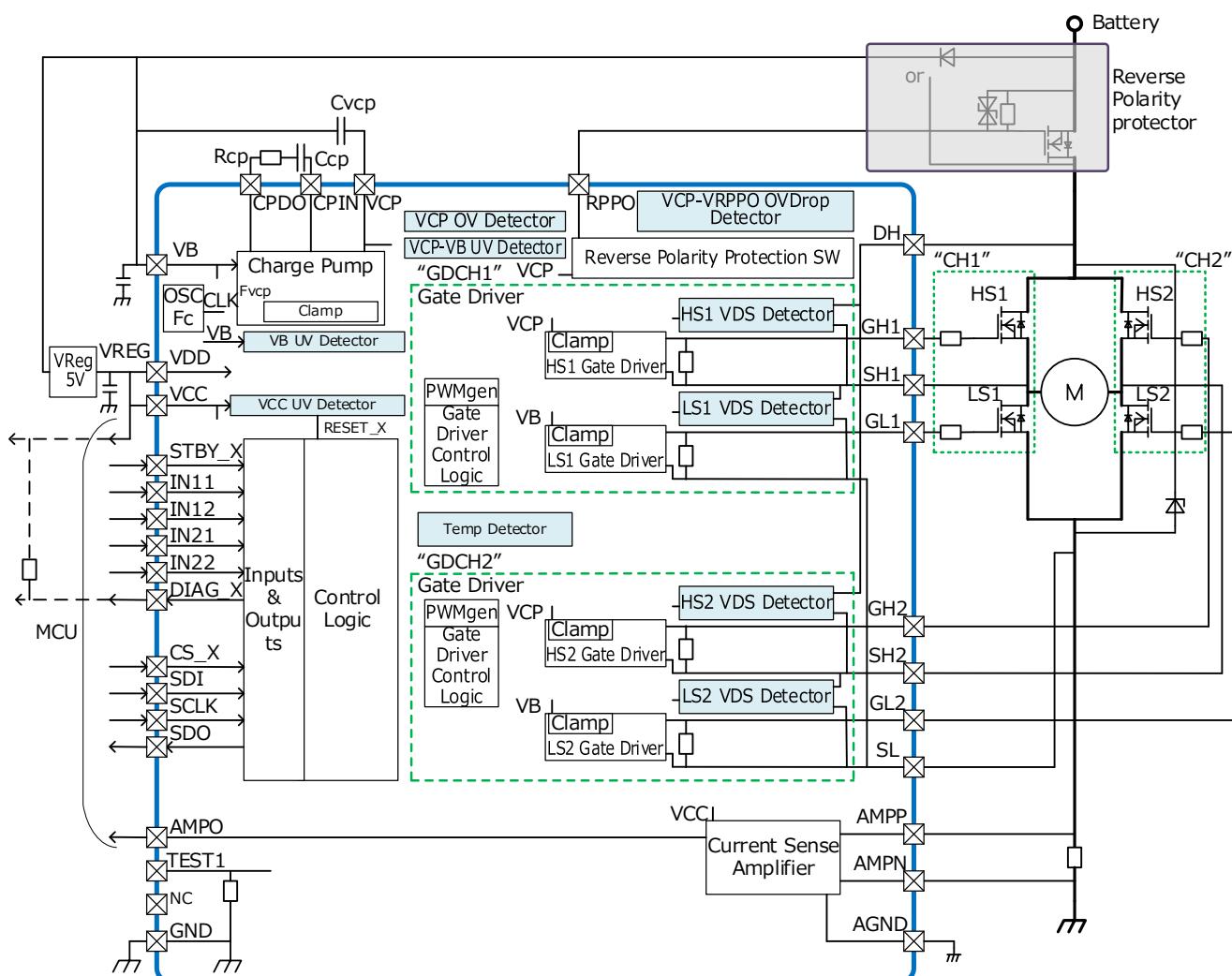

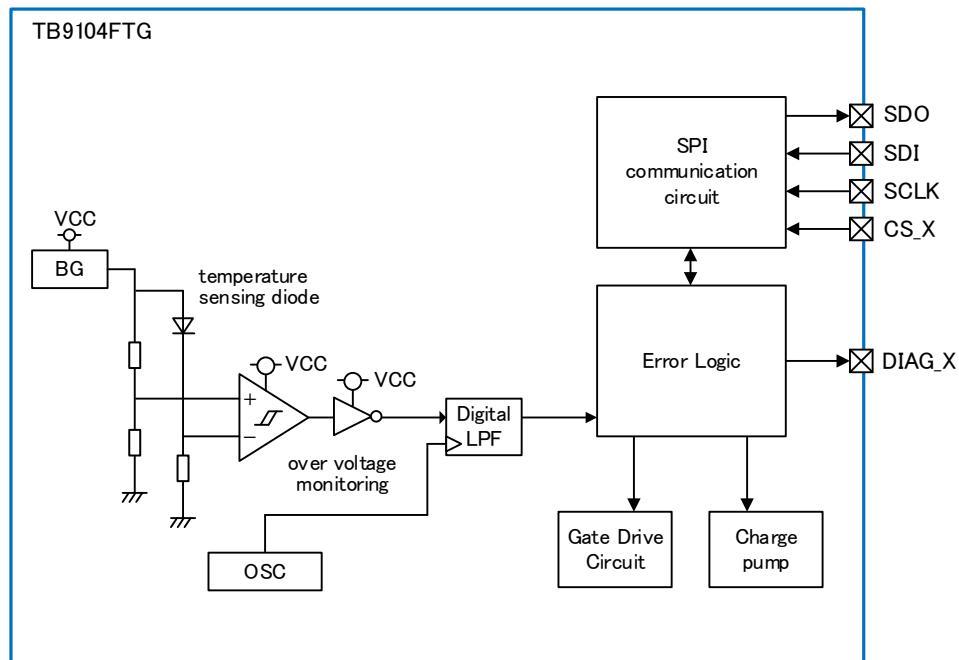

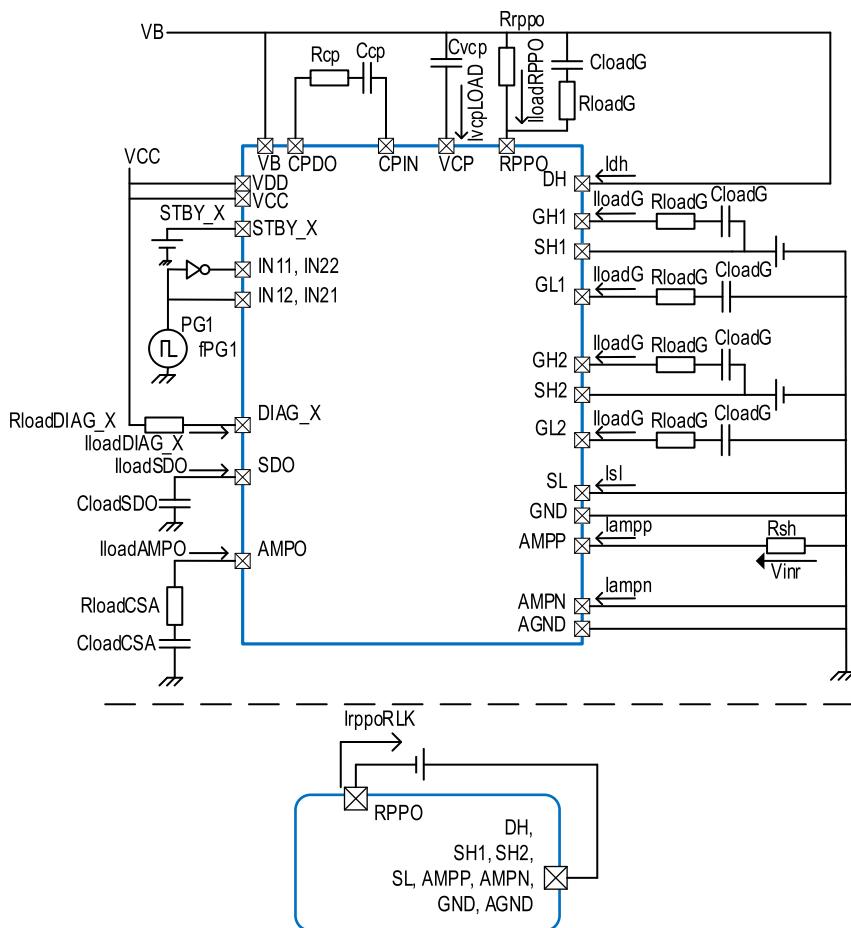

## 4. ブロック図

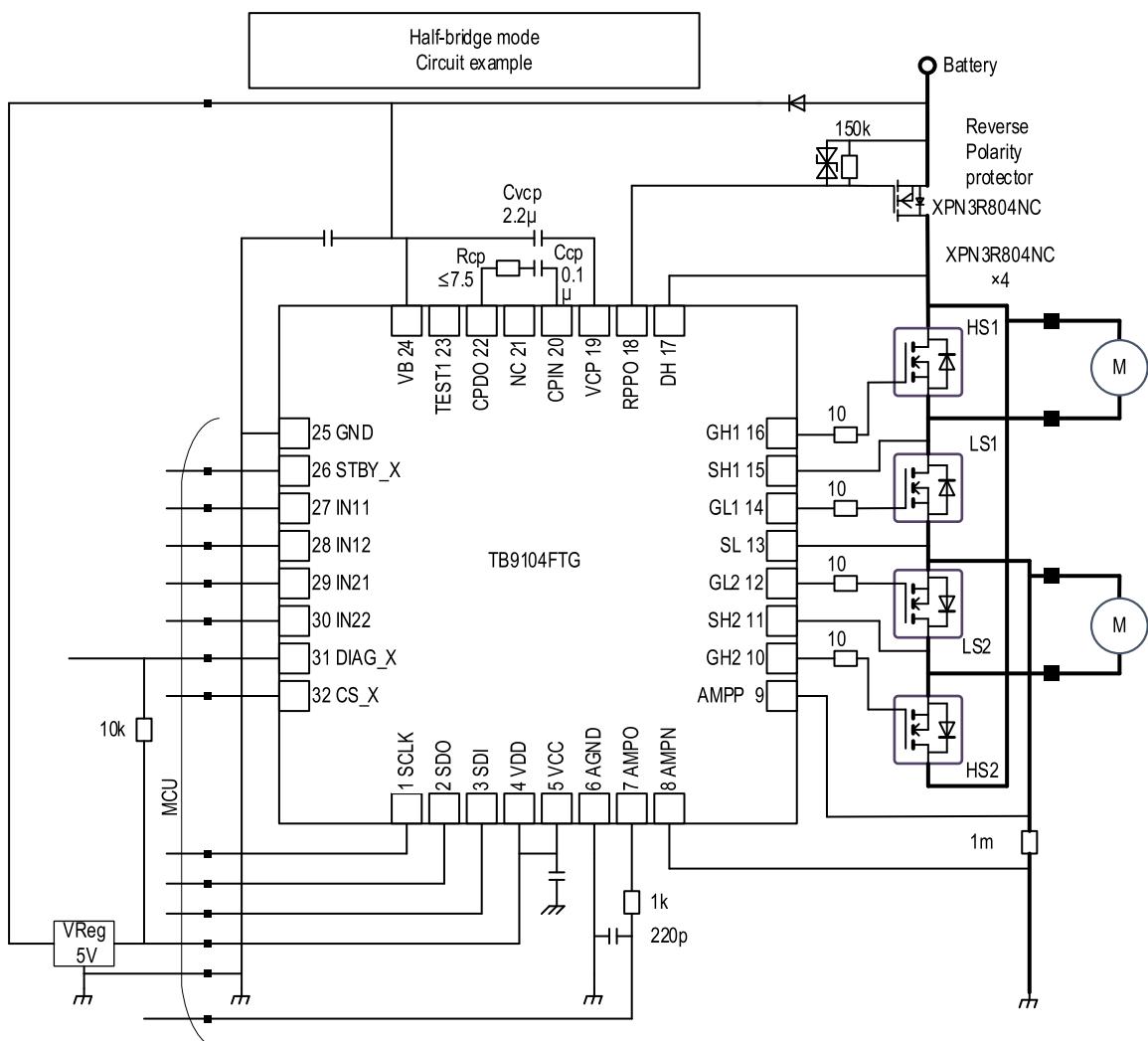

図 4.1 ブロック図

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。また、IC 外部の回路や定数は例であり、動作保証をするものではありません。使用環境を考慮し、評価・確認を十分に実施の上、決定してください。

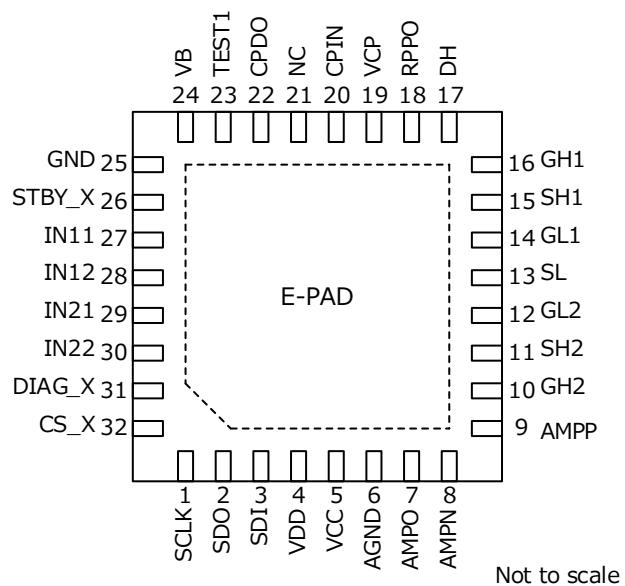

## 5. 端子配置図

図 5.1 端子配置図 (Top view)

## 6. 端子説明

表 6.1 TB9104FTG 端子表

| 端子番号 | 名称     | 入出力           | 端子説明                                                                      |

|------|--------|---------------|---------------------------------------------------------------------------|

| 1    | SCLK   | Input         | SPI: Serial clock input pin. プルダウン抵抗内蔵                                    |

| 2    | SDO    | Output        | SPI: Serial data output pin. 3 state out                                  |

| 3    | SDI    | Input         | SPI: Serial data input pin. プルダウン抵抗内蔵                                     |

| 4    | VDD    | Power Input   | デジタル回路 電源入力端子<br>VCC 端子と VDD 端子は同一の電源に接続してください。                           |

| 5    | VCC    | Power Input   | アナログ回路 電源入力端子<br>低電圧時 IC 初期化信号生成 LPF 内蔵<br>VCC 端子と VDD 端子は同一の電源に接続してください。 |

| 6    | AGND   | Ground        | 電流検出アンプ グラウンド端子                                                           |

| 7    | AMPO   | Analog Output | 電流検出アンプ 出力端子                                                              |

| 8    | AMPN   | Analog Input  | 電流検出アンプ 差動入力端子 (負入力)                                                      |

| 9    | AMPP   | Analog Input  | 電流検出アンプ 差動入力端子 (正入力)                                                      |

| 10   | GH2    | Output        | ゲートドライバーGDCH2 ハイサイド n 型 MOSFET ゲート出力端子                                    |

| 11   | SH2    | Bidirectional | ゲートドライバーGDCH2 ハイサイド n 型 MOSFET ソース端子                                      |

| 12   | GL2    | Output        | ゲートドライバーGDCH2 ローサイド n 型 MOSFET ゲート出力端子                                    |

| 13   | SL     | Bidirectional | ローサイド n 型 MOSFET ソース端子                                                    |

| 14   | GL1    | Output        | ゲートドライバーGDCH1 ローサイド n 型 MOSFET ゲート出力端子                                    |

| 15   | SH1    | Bidirectional | ゲートドライバーGDCH1 ハイサイド n 型 MOSFET ソース端子                                      |

| 16   | GH1    | Output        | ゲートドライバーGDCH1 ハイサイド n 型 MOSFET ゲート出力端子                                    |

| 17   | DH     | Input         | ハイサイド n 型 MOSFET ドレイン入力端子                                                 |

| 18   | RPPO   | Power Output  | バッテリー逆接続保護回路用 電源出力端子                                                      |

| 19   | VCP    | Bidirectional | チャージポンプ部 平滑キャパシター接続端子                                                     |

| 20   | CPIN   | Bidirectional | チャージポンプ部 昇圧入力端子                                                           |

| 21   | NC     | -             | Non-Connection どこにも接続しないでください。                                            |

| 22   | CPDO   | Output        | チャージポンプ部 ドライブ出力端子                                                         |

| 23   | TEST1  | Test terminal | テスト信号端子 どこにも接続しないでください。 プルダウン抵抗内蔵                                         |

| 24   | VB     | Power Input   | 電源入力端子                                                                    |

| 25   | GND    | Ground        | グラウンド端子                                                                   |

| 26   | STBY_X | Input         | スタンバイ指示入力端子 (負論理)<br>プルダウン抵抗内蔵 LPF 内蔵                                     |

| 27   | IN11   | Input         | ゲートドライバー1 コントロール入力 1 プルダウン抵抗内蔵                                            |

| 28   | IN12   | Input         | ゲートドライバー1 コントロール入力 2 プルダウン抵抗内蔵                                            |

| 29   | IN21   | Input         | ゲートドライバー2 コントロール入力 1 プルダウン抵抗内蔵                                            |

| 30   | IN22   | Input         | ゲートドライバー2 コントロール入力 2 プルダウン抵抗内蔵                                            |

| 31   | DIAG_X | Output        | 異常状態検出通知 出力端子 (負論理)<br>正常時ハイインピーダンス 異常時 Low 出力                            |

| 32   | CS_X   | Input         | SPI: Chip select. (負論理) プルアップ抵抗内蔵                                         |

## 7. 機能動作説明

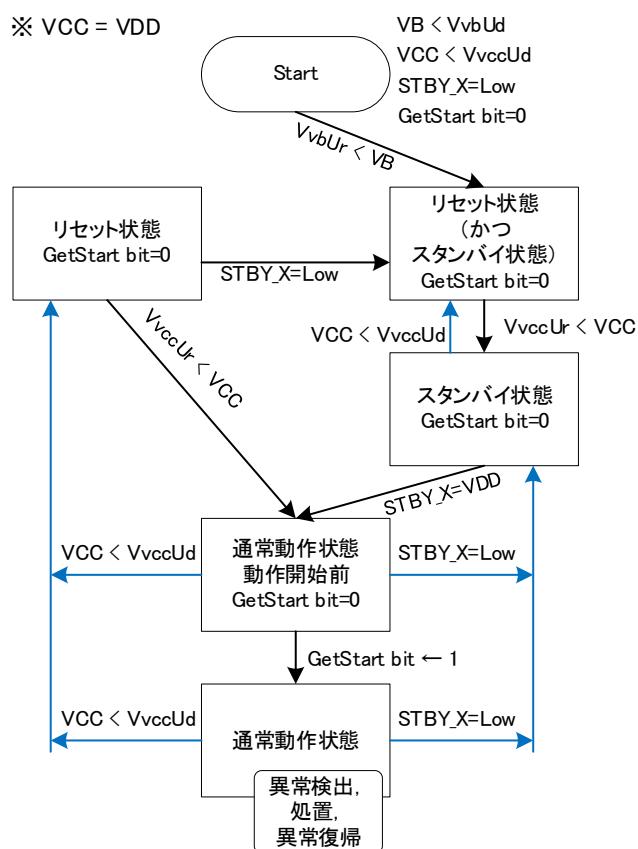

### 7.1. 動作状態

TB9104FTG は動作状態としてスタンバイ状態、リセット状態、通常動作状態の 3 状態があります。スタンバイ状態は、全回路について、電源をオフにしたり、動作を停止したりして、消費電力を抑えた状態です。リセット状態は、各回路を停止し、レジスターを初期状態にしますが、一部の回路は通常状態に移行するのに備えて待機しています。通常動作状態は、各回路を動作させ、MCU からの指示を待って、外部 n 型 MOSFET のゲートをドライブします。なお、通常動作状態では、異常発生に応じて各回路を停止します。動作状態について、表 7.1.1 に示します。

異常を検出したときの動作は、あらかじめユーザーが SPI から設定しておかなければなりません。異常が複数同時に発生した場合は、それぞれの異常における停止指示が足し合わされます。異常状態が解消した後の復帰手順は、あらかじめ SPI から選択することができます。異常状態の種類について、表 7.1.2 に示します。

VDD 端子と VCC 端子は同一の電源へ接続してください。VCC 端子の電圧は、リセット信号の生成に関係しています。

リセットが解除されるのは、VCC 端子の電圧が低電圧検出復帰電圧 VvccUr を超え、かつ、STBY\_X 端子が VinpH 以上となったときです。リセットの解除の前に、チャージポンプ回路やローサイドゲートドライバ一部の電源である VB 端子の電圧を VvbRNG としてください。

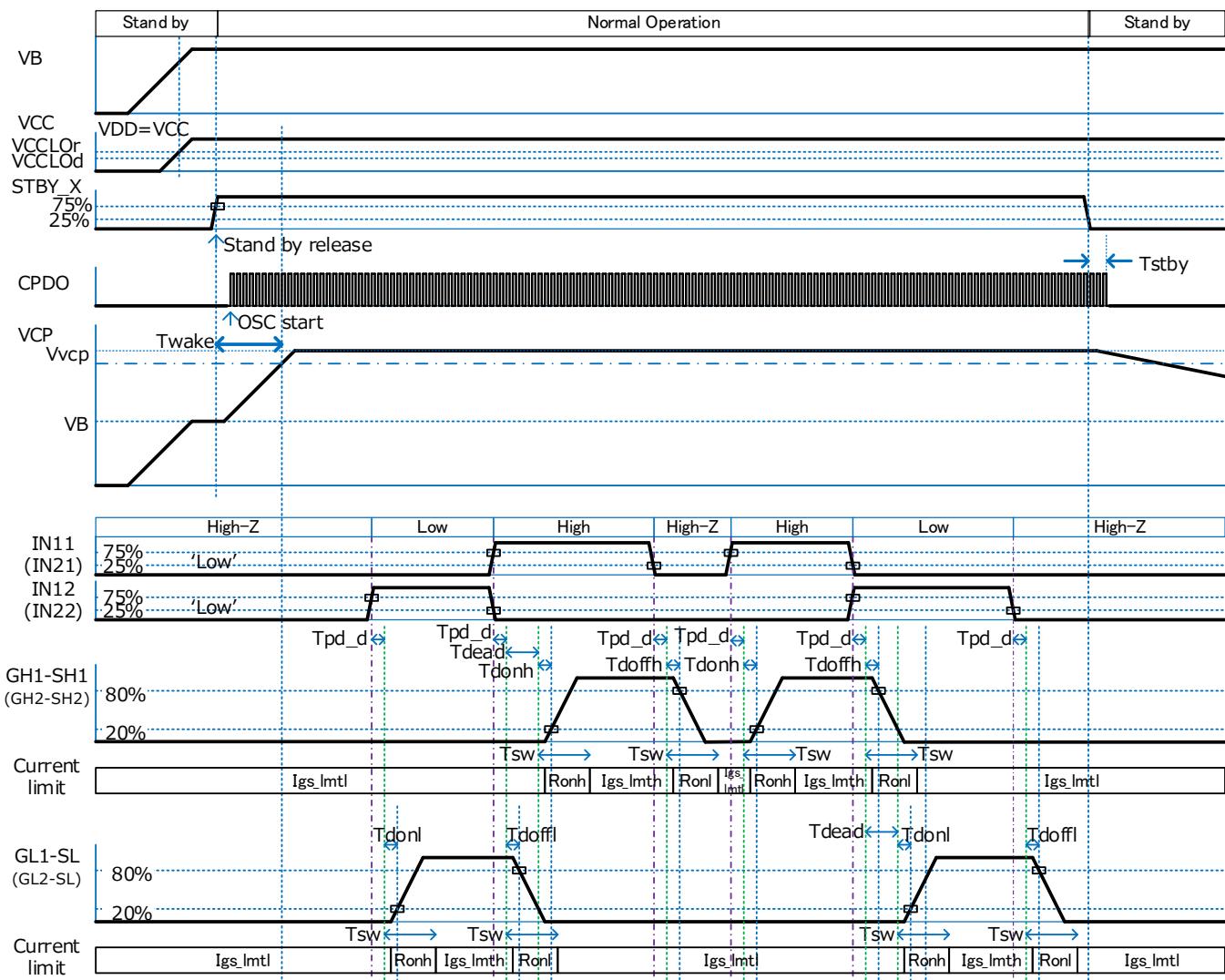

図 7.1.1 に VDD, VCC と STBY\_X などについて遷移を示します。また、図 7.2.1 に VB, VCC, VDD, STBY\_X を含めた通常動作への遷移波形を示します。

表 7.1.1 動作状態説明

| No. | IC 動作状態          | VB 電圧 ,<br>VCC 電圧 ,<br>VDD 電圧            | STBY_X<br>端子   | IN11,<br>IN12,<br>IN21,<br>IN22<br>端子 | OSC | Control<br>logic ,<br>レジスター,<br>GetStart-<br>bit | Charge<br>pump ,<br>CPDO<br>端子 | RPPO<br>端子 | GH1-SH1,<br>GL1-SL,<br>GH2-SH2,<br>GL2-SL          | DIAG_X<br>端子 |

|-----|------------------|------------------------------------------|----------------|---------------------------------------|-----|--------------------------------------------------|--------------------------------|------------|----------------------------------------------------|--------------|

| 1   | リセット<br>状態       | VvbRNG,<br>VCC 電圧が<br>VvccUd を<br>下回る    | Do not<br>care | Do<br>not<br>care                     | -   | 停止 ,<br>初期値,<br>0(L)                             | 停止,<br>Z                       | Z          | RL,<br>RL,<br>RL,<br>RL                            | Z            |

| 2   | スタンバイ<br>状態      | 運用電圧<br>VvbRNG ,<br>VvccRNG ,<br>VvddRNG | L              | Do<br>not<br>care                     | 停止  | 停止 ,<br>初期値,<br>0(L)                             | 停止,<br>Z                       | Z          | RL,<br>RL,<br>RL,<br>RL                            | Z            |

| 3   | 通常動作状態<br>動作開始前  | 運用電圧<br>VvbRNG ,<br>VvccRNG ,<br>VvddRNG | H              | Do<br>not<br>care                     | 発振  | 動作 ,<br>動作 ,<br>0(L)                             | 動作,<br>動作                      | VCP<br>電圧  | L,<br>L,<br>L,<br>L                                | L            |

| 4   | 通常動作状態<br>異常不検出時 | 運用電圧<br>VvbRNG ,<br>VvccRNG ,<br>VvddRNG | H              | 動作<br>指示<br>入力                        | 発振  | 動作 ,<br>動作 ,<br>1(H)                             | 動作,<br>動作                      | VCP<br>電圧  | 動作 H/L,<br>動作 H/L,<br>動作 H/L,<br>動作 H/L<br>7.17 参照 | Z            |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

表 7.1.2 検出可能な異常の種類

| No. | 異常の内容                     | 説明                                          |

|-----|---------------------------|---------------------------------------------|

| 1   | VCC 端子電圧 低電圧              | VCC 低電圧による初期化を行った                           |

| 2   | VB 端子電圧 低電圧               | ゲートドライブ電圧が不十分となる可能性がある                      |

| 3   | VCP 端子電圧 高電圧              | VCP 端子耐圧を超過する可能性がある                         |

| 4   | VCP, VB 間電圧 低電圧           | チャージポンプの昇圧が不十分である<br>ゲートドライブ電圧が不十分となる可能性がある |

| 5   | VCP, RPPO 間電圧 高電圧         | RPPO 端子外部に地絡など異常がある                         |

| 6   | SPI 異常                    | 通信フォーマットが合っていない。<br>禁止された空間にアクセスした。         |

| 7   | T <sub>j</sub> (接合温度) 高温  | 動作温度範囲の上限を超えている                             |

| 8   | HS1 V <sub>dson</sub> 高電圧 | オンしている外部 n 型 MOSFET "HS1"に過大電流が流れている        |

| 9   | LS1 V <sub>dson</sub> 高電圧 | オンしている外部 n 型 MOSFET "LS1"に過大電流が流れている        |

| 10  | HS2 V <sub>dson</sub> 高電圧 | オンしている外部 n 型 MOSFET "HS2"に過大電流が流れている        |

| 11  | LS2 V <sub>dson</sub> 高電圧 | オンしている外部 n 型 MOSFET "LS2"に過大電流が流れている        |

図 7.1.1 動作状態 遷移図

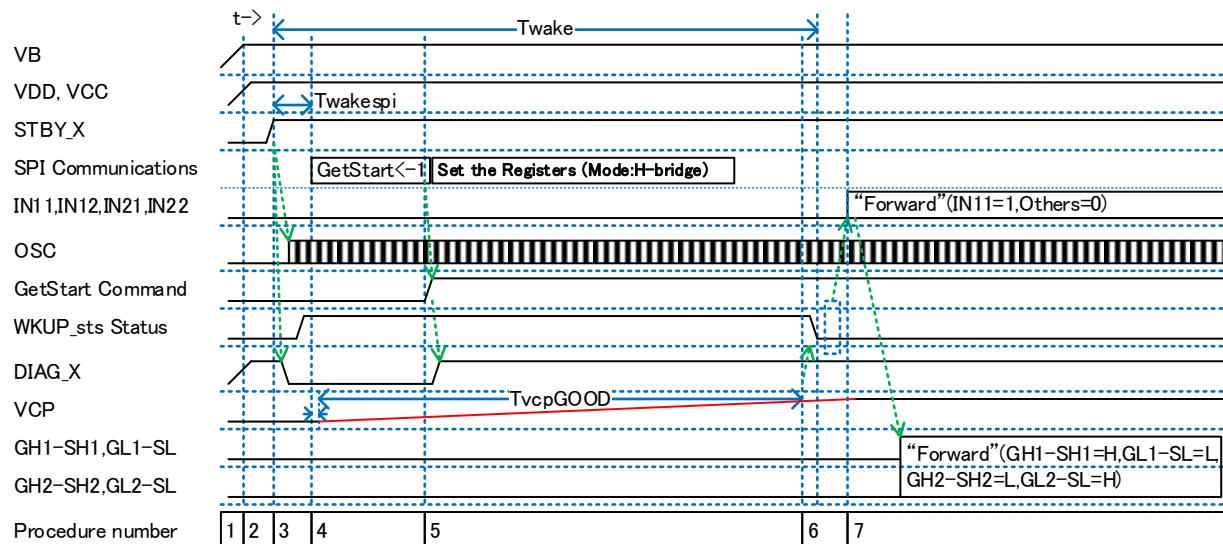

## 7.2. 使用開始コマンド (Getting Started Command)と手順

GetStart Command/Status 初期値： 0

TB9104FTG を使用中に、VCC 低電圧による初期化が起こったことを MCU に知らせるためのレジスターです。

TB9104FTG を使用開始する際は、最初に GetStart レジスターに 1 をライトします。このレジスターが 0 であると、全てのレジスターは MCU からはライトできません。ただしリードすることは可能です。

このコマンドの状態に関わらず内部回路は動作しており、エラーステータスは設定と状態に従って値が書き換えられます。GetStart レジスターに 1 をライトした後は、使用したい動作に応じた値を各レジスターへ設定していきます。特に異常を検出したときの動作を決める VB\_UV\_op[2:0], VCPVB\_UV\_op[2:0], VCPRPPO\_ODV\_op[2:0], TJ\_OT\_op[2:0], VDS1H\_OV\_op[2:0], VDS1L\_OV\_op[2:0], VDS2H\_OV\_op[2:0], VDS2L\_OV\_op[2:0] は、通常動作状態に移行後速やかに設定してください。異常検出回路はすぐに設定に応じた動作を始める上、エラーステータスが 1 であると、該当するレジスターへのライトができません。少なくともゲートドライブ実行前までに設定してください。

表 7.2.1 初期化後 使用開始動作手順の例

| 手順 | IC 動作状態、MCU からの指示                                  | VB 電圧 , VCC 電圧 , VDD 電圧         | STBY_X 端子 | IN11, IN12, IN21, IN22 端子 | OSC | Control logic , レジスター, GetStart-bit | Charge pump , CPDO 端子 | RPPO 端子 | GH1-SH1, GL1-SL, GH2-SH2, GL2-SL | DIAG_X 端子 |

|----|----------------------------------------------------|---------------------------------|-----------|---------------------------|-----|-------------------------------------|-----------------------|---------|----------------------------------|-----------|

| 1  | リセット状態 , STBY_X: L                                 | VvbRNG , VCC 電圧が VvccUd を下回る    | L         | Do not care               | 停止  | 停止, 初期値, 0(L)                       | 停止, Z                 | Z       | RL, RL, RL, RL                   | Z         |

| 2  | スタンバイ状態, STBY_X=L                                  | 運用電圧 VvbRNG , VvccRNG , VvddRNG | L         | Do not care               | 停止  | 停止, 初期値, 0(L)                       | 停止, Z                 | Z       | RL, RL, RL, RL                   | Z         |

| 3  | 通常動作状態 VvddRNG<br>VvccRNG<br>異常不検出時 , STBY_X: L->H | 運用電圧 VvbRNG , VvccRNG , VvddRNG | H         | Do not care               | 発振  | Twakespi 後動作, 動作, 0(L)              | 動作 (昇圧中), 動作          | VCP 電圧  | Twake 期間 L, L, L, L              | L         |

| 4  | 通常動作状態<br>異常不検出時 , GetStart-bit に 1 をライト           | 運用電圧 VvbRNG , VvccRNG , VvddRNG | H         | Do not care (L,L,L,L)     | 発振  | 動作, 動作, 1(H)                        | 動作 (昇圧中), 動作          | VCP 電圧  | Twake 期間 L, L, L, L              | Z         |

| 5  | チャージポンプ<br>昇圧中<br>Twake 期間 , 各レジスターへ設定をライト         | 運用電圧 VvbRNG , VvccRNG , VvddRNG | H         | Do not care (L,L,L,L)     | 発振  | 動作, 設定値, 1(H)                       | 動作 (昇圧中), 動作          | VCP 電圧  | Twake 期間 L, L, L, L              | Z         |

| 6  | チャージポンプ<br>昇圧完了 , WKUP_sts=0 を確認                   | 運用電圧 VvbRNG , VvccRNG , VvddRNG | H         | L,L,L,L                   | 発振  | 動作, 動作, 1(H)                        | 動作, 動作                | VCP 電圧  | L, L, L, L                       | Z         |

| 7  | 通常動作状態<br>異常不検出時 , 動作指示                            | 運用電圧 VvbRNG , VvccRNG , VvddRNG | H         | 動作指示                      | 発振  | 動作, 動作, 1(H)                        | 動作, 動作                | VCP 電圧  | 動作指示通り駆動(H/L)<br>7.17 参照         | Z         |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

図 7.2.1 使用開始動作手順の例 (表 7.2.1)

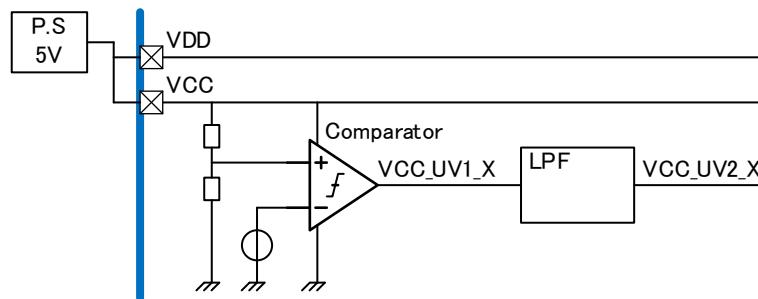

### 7.3. VDD 端子、VCC 端子、VCC 低電圧検出回路

VCC 端子と VDD 端子は、同一の電源へ接続してください。VDD は、STBY\_X, IN11, IN12, IN21, IN22, SPI と関係する回路の電源です。VCC は、アナログ回路の電源です。

VCC 端子の電圧 (VCC 電圧) が  $V_{vccUd}$  以下であると、TB9104FTG は動作を停止し各部は初期状態になります。これをリセット状態と呼びます。VCC 電圧が  $V_{vccUr}$  以上であると、TB9104FTG は STBY\_X, IN11, IN12, IN21, IN22, SPI の指示に従い動作します。

VCC 電圧を比較するコンパレーターは VCC 端子の電圧に重畠するノイズによるグリッチを除去するため、ヒステリシス電圧  $V_{vccUhys}$  を備えています。さらに後段にアナログ Low Pass Filter(以降 LPF)を備え、 $T_{vccUpw}$  を超えた幅の信号だけを利用します。

図 7.3.1 VDD, VCC 端子と VCC 低電圧検出回路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

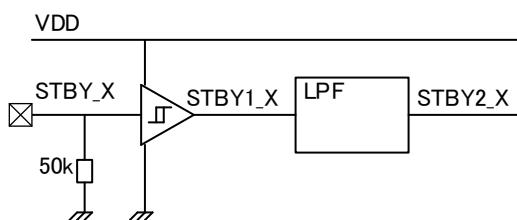

## 7.4. STBY\_X 端子、スタンバイ回路

STBY\_X 端子は TB9104FTG を低消費電力状態にすることができます。

どの動作状態であっても、STBY\_X 端子の電圧(STBY\_X 電圧)を  $V_{inPL}$  以下にすることで、内部回路は電源オフまたは動作停止となります。レジスターの設定値も初期値となります。スタンバイ状態と呼びます。TB9104FTG はゲートドライブ中であってもスタンバイ状態に移行できてしまい、その場合、異常検知もゲート制御もできません。このような使い方をする場合は、十分に検証をしてください。通常、無用なトラブルを避けるため、ゲートドライブをオフにしてから、スタンバイ状態にしてください。

STBY\_X 電圧を  $V_{inPH}$  以上にすると、VCC 電圧に応じて、リセット状態か通常動作状態に遷移します。STBY\_X 端子は、端子オープン時に TB9104FTG が通常動作状態にならないよう、 $50k\Omega$  の抵抗で GND ヘプルダウンしています。

STBY\_X 端子の入力バッファーは信号に重畳するノイズによるグリッチを除去するため、ヒステリシス電圧  $V_{inPHYS}$  を備えています。さらに後段にアナログ LPF を備え、 $T_{stby\_xPW}$  を超えた幅の信号だけを利用します。

図 7.4.1 STBY\_X 端子と LPF

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

## 7.5. 発振回路

TB9104FTG は発振回路を内蔵しています。発振周波数は 4MHz(Typ.)です。発振回路は、ロジック部品などが誤動作しないよう、発振開始から停止までグリッチが無く十分なパルス幅と振幅のクロックを供給します。発振回路は、リセット期間やスタンバイ期間は、発振を停止します。

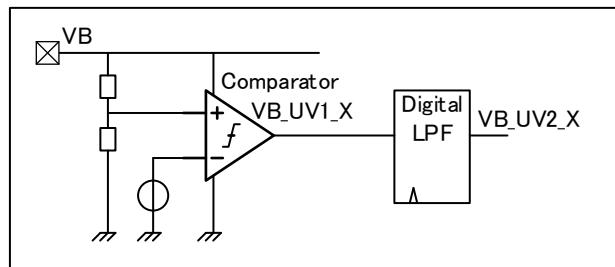

## 7.6. VB 端子、VB 低電圧検出回路

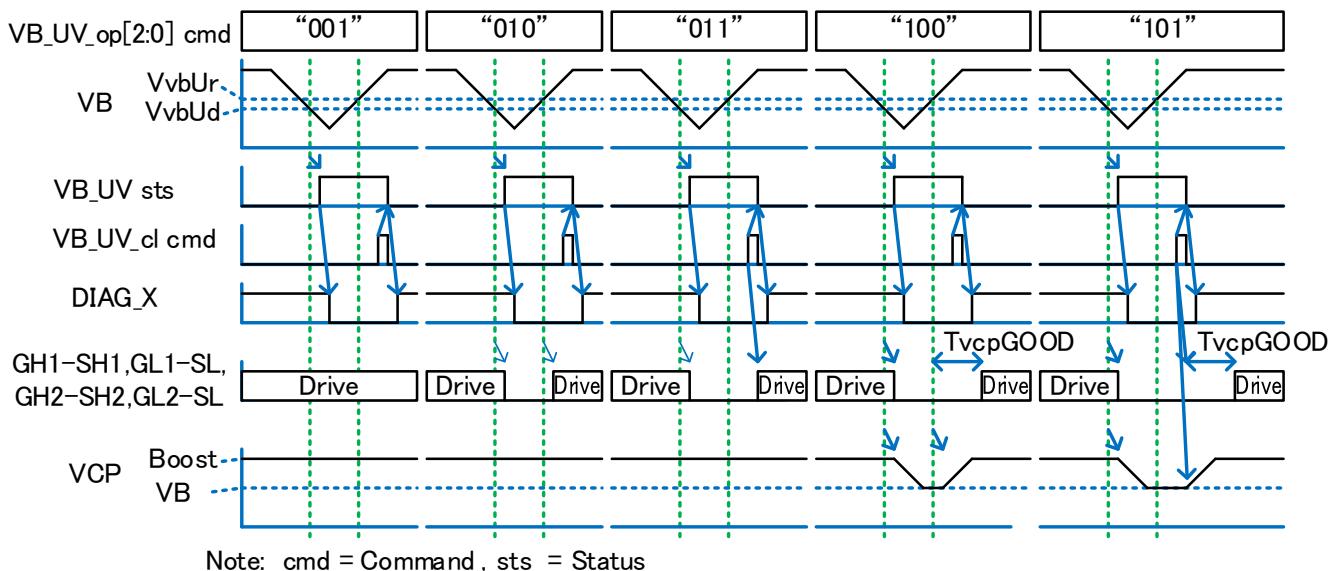

VB 端子の電圧が  $VvbUd$  以下であると、TB9104FTG は異常と判断します。

VB 端子の電圧が  $VvbUr$  以上であると、TB9104FTG は正常と判断します。

VB 端子のコンパレーターは VB 端子の電圧に重畠するノイズによるグリッチを除去するため、ヒステリシス電圧  $VvbUphys$  を備えています。さらに後段に LPF を備え、 $TvbUpw$  を超えた幅の信号だけを利用します。VB 低電圧を検出したときの動作は、SPI から動作設定コマンド  $VB\_UV\_op[2:0]$  によって、選択することができます。

図 7.6.1 VB 端子と VB 低電圧検出回路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

表 7.6.1 VB 低電圧検出時の動作設定（概要）

| 動作設定コマンド<br>VB_UV_op[2:0] | 検出<br>推移          | 動作概要<br>R=レジスター、G=ゲートドライブ、C=チャージポンプ                                                                                    |

|---------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------|

| “000”                     | -<br>(検出、<br>復帰 ) | R: 影響を与えない<br>G: 影響を与えない<br>C: 影響を与えない                                                                                 |

| “001”                     | 検出                | R: ステータスレジスターVB_UV を 1 にする。<br>G: 影響を与えない<br>C: 影響を与えない                                                                |

|                           | 復帰                | R: VB_UV=1 を保持。その後、クリアコマンド VB_UV_cl=1 とすることで、VB_UV=0 となる。<br>G: 影響を与えない<br>C: 影響を与えない                                  |

| “010”                     | 検出                | R: VB_UV=1<br>G: 全てのゲートドライブを停止する。<br>C: 影響を与えない                                                                        |

|                           | 復帰                | R: VB_UV=1 を保持。その後 VB_UV_cl=1 で VB_UV=0。<br>G: 速やかにゲートドライブを再開する。<br>C: 影響を与えない                                         |

| “011”                     | 検出                | R: VB_UV=1<br>G: 全てのゲートドライブを停止する。<br>C: 影響を与えない                                                                        |

|                           | 復帰                | R: VB_UV=1 を保持。その後 VB_UV_cl=1 で VB_UV=0。<br>G: ゲートドライブ停止を保持。その後 VB_UV_cl=1 で再開。<br>C: 影響を与えない                          |

| “100”                     | 検出                | R: VB_UV=1<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                  |

|                           | 復帰                | R: VB_UV=1 を保持。その後 VB_UV_cl=1 で VB_UV=0。<br>G: 速やかにゲートドライブを再開する。<br>C: 速やかにチャージポンプを動作させる。                              |

| “101”                     | 検出                | R: VB_UV=1<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                  |

|                           | 復帰                | R: VB_UV=1 を保持。その後 VB_UV_cl=1 で VB_UV=0。<br>G: ゲートドライブ停止を保持。その後 VB_UV_cl=1 で再開。<br>C: チャージポンプ停止を保持。その後 VB_UV_cl=1 で再開。 |

| “110”                     | -                 | Reserved. 指定すると、SPI エラーになります。                                                                                          |

| “111”                     | -                 | Reserved. 指定すると、SPI エラーになります。                                                                                          |

注: “Reserved”としてある設定は使用しないでください。

表 7.6.2 VB 低電圧検出時の動作設定 (詳細)

| 動作設定<br>コマンド<br>VB_UV_op<br>[2:0]<br>7.18.13 | 検出<br>推移 | IN11,IN12,<br>IN21,IN22 | Charge<br>Pump | CPDO<br>端子 | RPPO<br>端子 | GH1-SH1,<br>GL1-SL,<br>GH2-SH2,<br>GL2-SL | VB_UV<br>レジスター |

|----------------------------------------------|----------|-------------------------|----------------|------------|------------|-------------------------------------------|----------------|

| "000"                                        | -        | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | 0              |

| "001"                                        | 検出       | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | 1              |

|                                              | 復帰       | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | クリア後<br>0      |

| "010"                                        | 検出       | Do not care             | 動作             | 動作         | VCP        | L, L, L, L                                | 1              |

|                                              | 復帰       | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作再開                                      | クリア後<br>0      |

| "011"                                        | 検出       | Do not care             | 動作             | 動作         | VCP        | L, L, L, L                                | 1              |

|                                              | 復帰       | 指示(H,L)                 | 動作             | 動作         | VCP        | クリア後<br>再開                                | クリア後<br>0      |

| "100"                                        | 検出       | Do not care             | 停止             | Z          | VCP        | RL,RL,RL,RL                               | 1              |

|                                              | 復帰       | 指示(H,L)                 | 再開             | 再開         | VCP        | 動作再開                                      | クリア後<br>0      |

| "101"                                        | 検出       | Do not care             | 停止             | Z          | VCP        | RL,RL,RL,RL                               | 1              |

|                                              | 復帰       | 指示(H,L)                 | クリア後<br>再開     | クリア後<br>再開 | VCP        | クリア後<br>再開                                | クリア後<br>0      |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

図 7.6.2 VB 低電圧検出時の動作

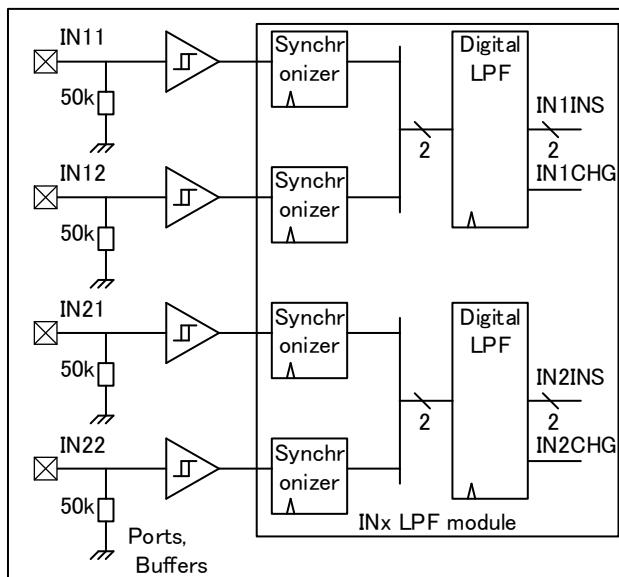

## 7.7. ゲートドライバー指示入力端子

IN11,IN12,IN21,IN22 各端子は、MCU からゲートドライバ一部への指示を受け取ります。各 IN 端子は、端子オープン時に不用意に動作しないよう、 $50k\Omega$  の抵抗で GND へプルダウンしています。各 IN 端子の入力バッファーは信号に重畳するノイズによるグリッチを除去するため、ヒステリシス電圧  $V_{inphys}$  を備えています。信号はその後デジタル回路領域に入り、直ちに内蔵クロックに同期化します。さらに一定時間以上連続する信号だけを通過させる LPF を備えています。このため各 IN 端子から PWM 駆動する際は、駆動周波数に上限が生じます。

INspiSEL コマンドを 1 にすると、IN11,IN12,IN21,IN22 端子の代わりに、INspi11, INspi12, INspi21, INspi22 コマンドから指示を出すことができます。

なおゲートドライバーへオンの指示を出す前に、コマンドレジスターへ設定を済ませてください。オンしている間でも設定することができますが、その場合思わぬ動作となる可能性があります。

図 7.7.1 IN11,IN12,IN21,IN22 端子とデジタル LPF

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

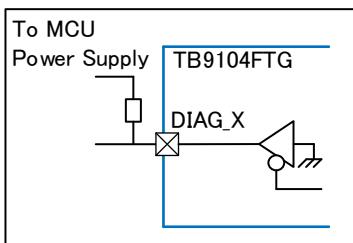

## 7.8. DIAG\_X 端子

DIAG\_X 端子は、TB9104FTG 内部の動作状態を診断した結果を表しています。異常を検出すると、**Low** を出力します。不検出時は、ハイインピーダンスとなります。DIAG\_X 端子は、外付け抵抗を介して接続先の電源に接続する必要があります。DIAG\_X 端子は、出力レベルに関わらず VDD レベルへの天絡または地絡した際に破壊しない能力を持っています。

図 7.8.1 DIAG\_X 端子

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

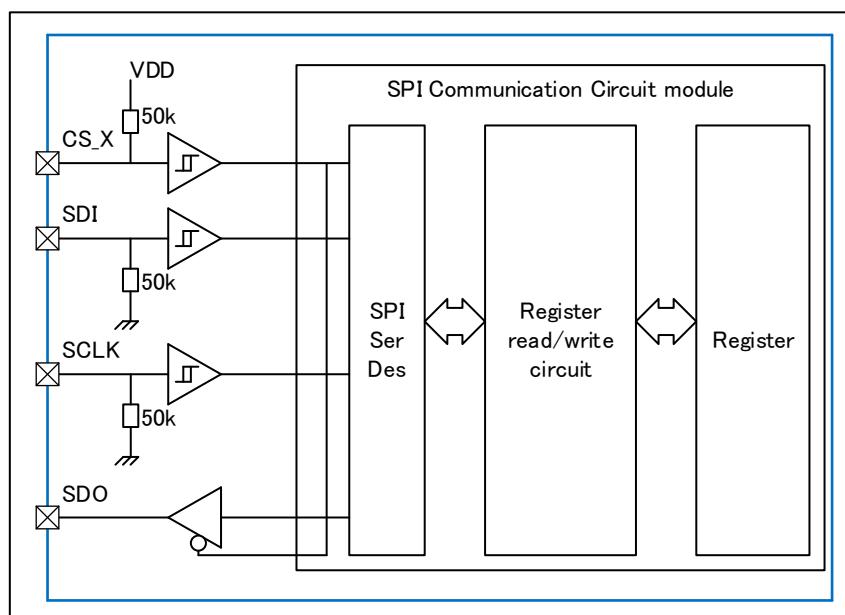

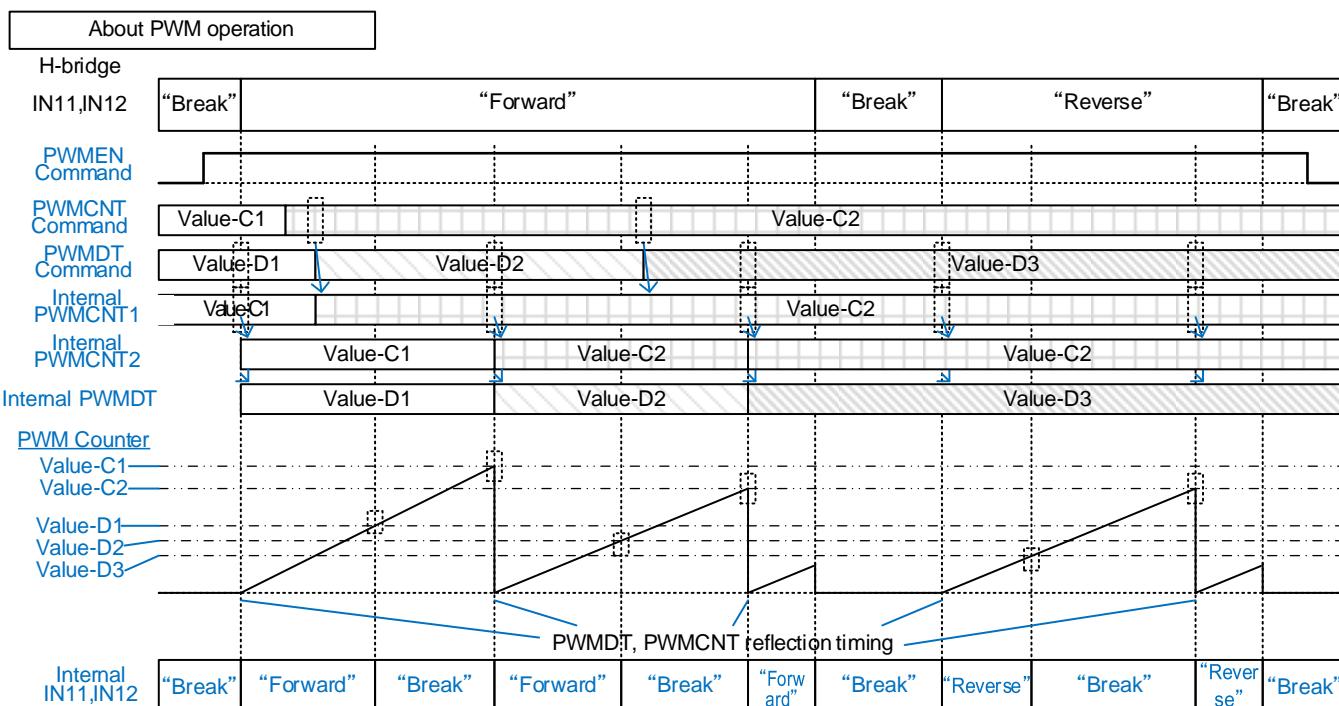

## 7.9. SPI 端子、SPI 回路

SPI の各入力端子は、端子オープン時に不用意に動作しないよう、 $50\text{k}\Omega$  の抵抗でプルアップまたはプルダウンしてあります。CS\_X 端子は、VDD へプルアップしています。SDI 端子、SCLK 端子は、GND へプルダウンしています。SDO 端子は、3 ステートバッファーでドライブします。CS\_X 端子が High の場合、SDO 端子はハイインピーダンスとなります。通信するには、CS\_X 端子を Low にしなければなりません。SDO 端子は、出力レベルに関わらず VDD レベルへの天絡または地絡した際に破壊しない能力を持っています。

TB9104FTG の SPI(Serial Peripheral Interface)モードは、SPI モード 1 (CPOL=Low, CPHA=High) です。SPI モード 1 では、SDI 端子のレベルを SCLK の立ち下がりで取り込みます。SDO 端子からは SCLK の立ち上がりでビットをシフトして出力します。

SPI モジュールは、リセット状態やスタンバイ状態では動作しません。またレジスターに設定した値も初期値になります。CS\_X 信号の立ち下がり後、SCLK 信号の立ち上がりまでに待機時間  $T_{cs\_xsclk}$  が必要です。さらにその後、SDO 信号がハイインピーダンスから有効なデータになるまで  $T_{sdoDLY}$  が必要です。

SCLK 信号の立ち上がりで MCU は SDI 信号にデータを出力してください。次の SCLK 信号の立ち下がりで TB9104FTG は SDI 信号からデータを取得します。なお、SDI 信号上のデータは SCLK 立ち下がりに対し、セットアップタイム  $T_{sdiSET}$ 、ホールドタイム  $T_{sdiHLD}$  が必要です。SCLK 信号の立ち上がりで TB9104FTG は SDO 信号にデータを出力します。次の SCLK 信号の立ち下がりで MCU は SDO 信号からデータを取得してください。

クロック SCLK の最後の立ち下がりから CS\_X 信号の立ちあがりまで、待機時間  $T_{sclkcs\_x}$  が必要です。さらにその後、SDO 信号がハイインピーダンスになるまで  $T_{sdocs\_xDLY}$  が必要です。CS\_X 信号が立ち上がってから、次に立ち下がるまで、待機時間  $T_{cs\_xH}$  が必要です。

これらタイミングについては、図 10.4.1 を参照ください。SDI 信号上でデータは、MSB から LSB の順に送られることを想定しています。SDO 信号上でデータは、MSB から LSB の順に送ります。

図 7.9.1 SPI 各端子と SPI 回路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

### 7.9.1. SPI 通信動作

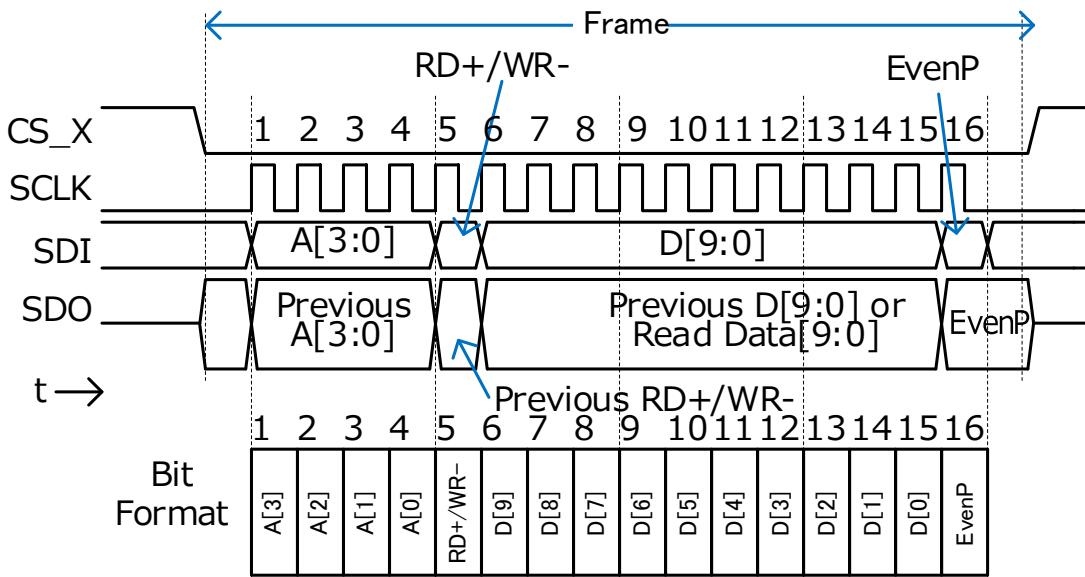

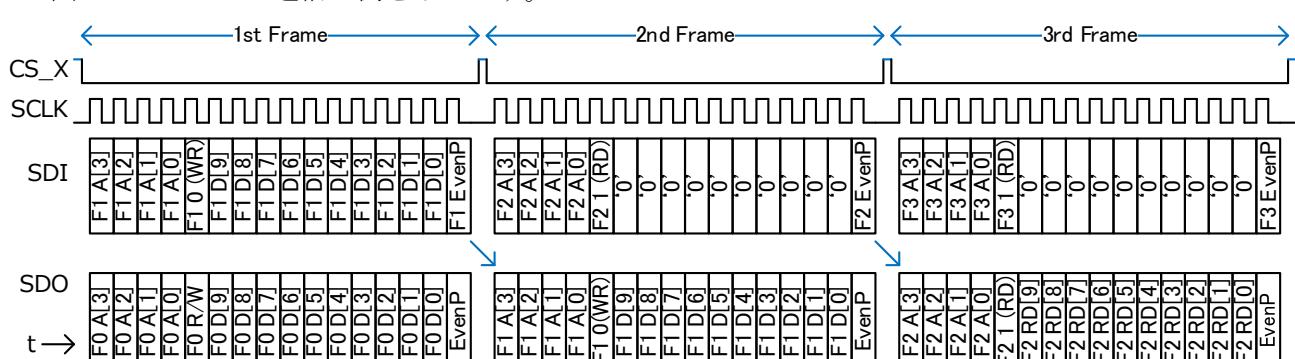

フレーム長は 16 ビットです。フレームは、SDI 信号上アドレス指定ビット‘A[3:0]’、リード、ライト指定ビット‘RD+/WR-’、データ指定ビット‘D[9:0]’、データチェック用偶数パリティービット‘EvenP’により構成されます。機能としてはリード動作、ライト動作の 2 種類があり、リード、ライト指定ビット‘RD+/WR-’により選択します。フレームの構成を図 7.9.1.1 に示します。

図 7.9.1.1 フレームフォーマット

ライトを実行するときは、表 7.18.1 を参照し、ライトしたいレジスターのアドレスを求め、ライトするデータを用意します。次に図 7.9.1.1 のように TB9104FTG の各端子へアクセスします。SDI 端子へは、アドレスを MSB から LSB へ、”RD+/WR-”ビットの 0、ライトデータを MSB から LSB へと順に入力し、最後にアドレスから、”RD+/WR-”ビットの 0、ライトデータまでの全てのビットを対象とした、偶数パリティを入力します。

リードを実行するときは、表 7.18.1 を参照し、リードしたいレジスターのアドレスを求めます。次に図 7.9.1.1 のように TB9104FTG の各端子へアクセスします。SDI 端子へは、アドレスを MSB から LSB へ、”RD+/WR-”ビットの 1、ライトデータとして”0”を入力し、最後にここまでビットを対象として生成した偶数パリティを入力します。リードデータは次のフレームで SDO 端子から出力します。ビットの順序はライト時と同じです。リードデータを取り出すための次のフレームとしてダミーフレーム (NOP レジスターへのライトやリード) も使用できます。

図 7.9.1.2 に SPI 通信の例を示します。

図 7.9.1.2 SPI 通信 送受信の例

### 7.9.2. SPI に関する異常

SPIError になるのは、次の動作をしたときです。

- シリアル通信のフレーム長が **16 SCLK** ではない場合

- ビット幅を持つコマンドで、ライトすることを禁じている組み合わせをライトした場合

- パリティーエラー

フレーム長のエラーは、SCLK の数が 0~16 クロック未満の場合、CS\_X 立ち上がりの時点でエラーとなります。また、17 クロック以上の場合は SDO 端子からは 0(Low)が出力され、その後 CS\_X 立ち上がりの時点でエラーとなります。

パリティーエラーは、16 ビットのデータで、1 であるビットが奇数だった場合、エラーとなります。なお、パリティーエラーは、ビット誤りが 2 ビット以上あると異常を正確に検出できません。

上記の動作が行われると TB9104FTG は、SPIError レジスターを 1 にセットします。SPIError が 1 になると、DIAG\_X 端子は Low になります。異常を検出した後に正常な通信ができなくなる可能性はありますが、復帰するまで継続してアクセスすべきです。異常を検出した後、最初の正常な通信では TB9104FTG は SDO 端子から 1 つ前のアドレス 4 ビットと "RD+/WR-" ビットに続き、10 ビットの 0 と故意に誤ったパリティービットを返します。その後の通信でパリティービットが正常に復帰することを期待します。

正常な通信が可能となった後 SPIError\_cl レジスターに 1 をライトすることで、SPIError レジスターを 0 にすることができます。正常な通信が可能となった後、TB9104FTG 内の各種設定が異常前の状態と同じであるかどうか、確認をしてください。

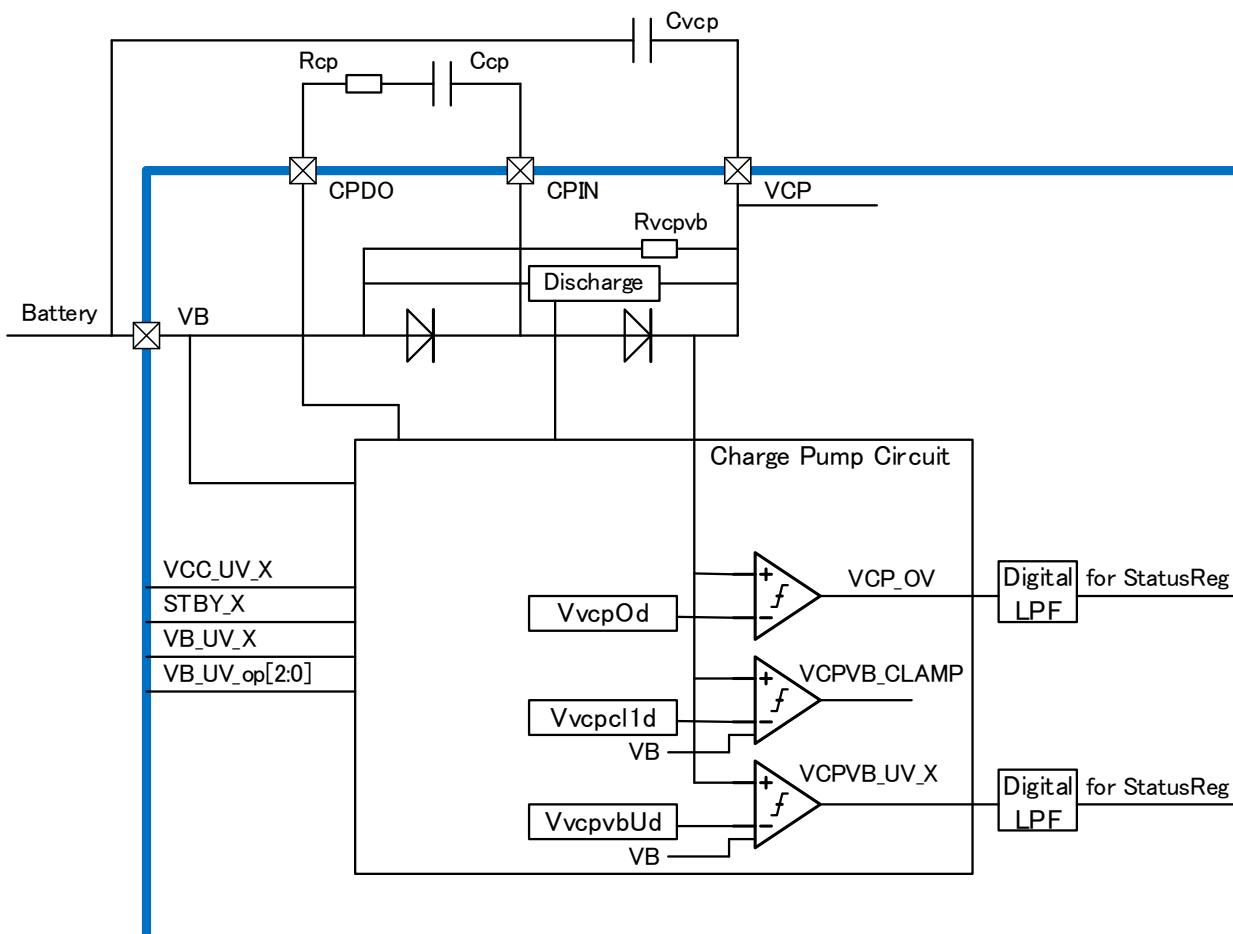

## 7.10. チャージポンプ回路

TB9104FTG はハイサイド外部 n 型 MOSFET のゲートを駆動するため、チャージポンプ回路を内蔵しています。2 倍昇圧です。チャージポンプ回路は、リセット状態やスタンバイ状態の間は動作を停止します。通常動作状態に移行した直後の  $T_{wake}$  期間とチャージポンプ起動後の  $T_{VCPGOOD}$  期間は、昇圧が不十分ですので、ゲートドライブはオフにして、VCP,VB 間低電圧検出異常、VCP,RPPO 間高電圧検出異常は判定しません。

チャージポンプ回路は、動作中に VCP 電圧がクランプ電圧  $VCPCL1d$  を上回った場合は直ちに昇圧を停止し、下回れば再開することで VCP 電圧を一定に保ちます。CPDO 端子は、駆動周波数に応じて、GND 電圧と VB 電圧の間で振動します。駆動周波数は、ラジオの中波帯域より下である、200kHz(Typ.) です。CPDO 端子は、停止時は GND 電圧です。

CPIN 端子は、昇圧電圧の入力端子です。

VCP 端子は、昇圧電圧を安定化させるための平滑コンデンサーを接続する端子です。

VCP 電圧は、チャージポンプ動作を停止し続けると、徐々に VB 電圧に移行します。

VCP 端子には外部から電圧を印加しないでください。

図 7.10.1 チャージポンプ回路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

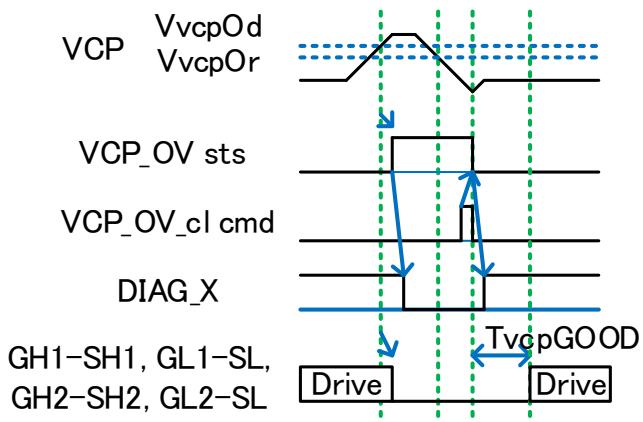

### 7.10.1.1. VCP 高電圧検出回路と異常処理

VCP 高電圧検出回路は、VCP 端子の電圧を監視し、過電圧を検出します。VCP 端子の電圧が  $V_{vcopOd}$  以上であると、TB9104FTG は異常と判断します。VCP 端子の電圧が  $V_{vcopOr}$  以下であると、TB9104FTG は正常と判断します。

VCP 端子のコンパレーターは VCP 端子の電圧に重畠するノイズによるグリッチを除去するため、ヒステリシス電圧  $V_{vcopOphys}$  を備えています。

チャージポンプコントローラー回路は、VCP 端子の耐圧超過を防ぐため、VCP 高電圧検出回路から過電圧の通知を受けた際は、直ちにチャージポンプ回路の昇圧動作を停止させ、ディスチャージ回路を動作させます。さらに、コンパレーターの後段に LPF を備え、 $T_{vcopOpw}$  を超えた幅の信号だけを通過させます。この信号が異常を知らせると、ステータスレジスター VCP\_OV を 1 とし、チャージポンプ回路の昇圧停止と、ゲートドライブの停止を行います。

復帰は、VCP 端子の電圧が正常と判断されているときにクリアコマンド VCP\_OV\_cl を 1 にすることで、VCP\_OV ステータスは 0 になり、同時にチャージポンプ回路は昇圧を開始し、 $t_{vcopGOOD}$  を経た後、ゲートドライブの動作も再開します。

表 7.10.1.1 VCP 高電圧検出時の動作設定（概要）

| 検出推移 | 動作概要                                                                                                                        |  |

|------|-----------------------------------------------------------------------------------------------------------------------------|--|

|      | R=レジスター、G=ゲートドライブ、C=チャージポンプ                                                                                                 |  |

| 検出   | R: VCP_OV=1<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                      |  |

| 復帰   | R: VCP_OV=1 を保持。その後 VCP_OV_cl=1 で VCP_OV=0。<br>G: ゲートドライブ停止を保持。その後 VCP_OV_cl=1 で再開。<br>C: チャージポンプ停止を保持。その後 VCP_OV_cl=1 で再開。 |  |

表 7.10.1.2 VCP 高電圧検出時の動作設定（詳細）

| 検出推移 | IN11,IN12, IN21,IN22 | Charge Pump | CPDO 端子    | RPPO 端子 | GH1-SH1, GL1-SL, GH2-SH2, GL2-SL           | VCP_OV レジスター |

|------|----------------------|-------------|------------|---------|--------------------------------------------|--------------|

| 検出   | Do not care          | 停止          | Z          | VCP     | RL, RL, RL, RL<br>HS1,LS1, HS2,LS2 は<br>オフ | 1            |

| 復帰   | 指示(H,L)              | クリア後<br>再開  | クリア後<br>再開 | VCP     | クリア後<br>再開                                 | クリア後<br>0    |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

Note cmd = Command, sts = Status

図 7.10.1.1 VCP 高電圧検出時の動作

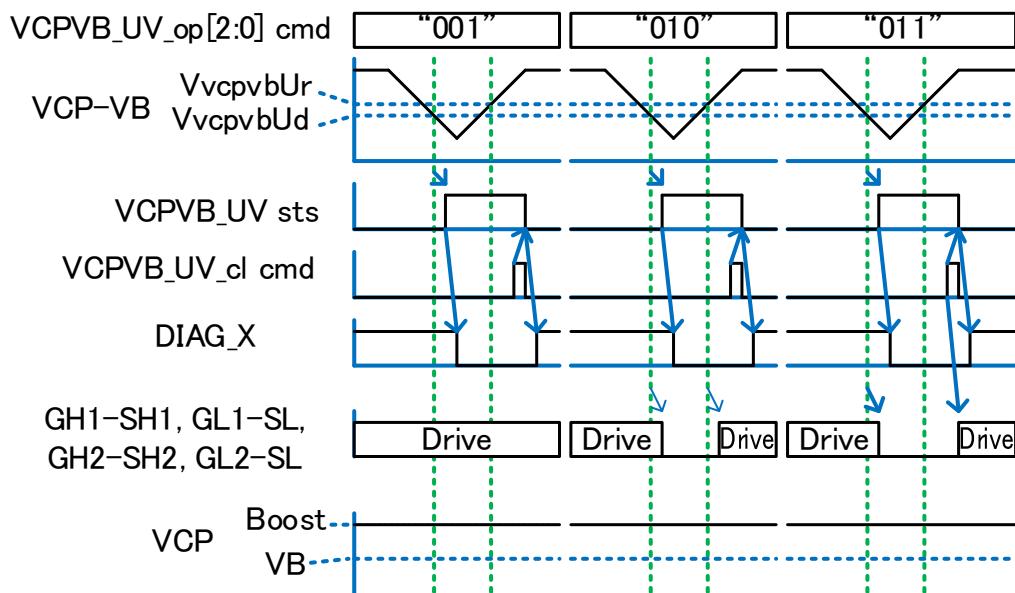

### 7.10.2. VCP-VB 低電圧検出回路と異常処理

VCP-VB 低電圧検出回路は、VCP 端子の電圧を監視し、昇圧不足を検出します。昇圧不足のときは、ゲートドライブを停止することができます。

通常動作状態に移行した直後の **Twake** 期間とチャージポンプ起動後の **TvcpvbGOOD** 期間は、昇圧が不十分ですので、VCP,VB 間低電圧検出異常とは判定しません。VCP、VB 端子間の電圧が **VvcpvbUd** 以下であると、TB9104FTG は異常と判断します。VCP、VB 端子間の電圧が **VvcpvbUr** 以上であると、TB9104FTG は正常と判断します。

VCP、VB 端子間の電圧を比較するコンパレーターは VCP、VB 端子間の電圧に重畠するノイズによるグリッッチを除去するため、ヒステリシス電圧 **VvcpvbUhys** を備えています。さらに後段に LPF を備え、**TvcpvbUpw** を超えた幅の信号だけを利用します。VCP-VB 低電圧検出したときの動作は、SPI から動作設定コマンド **VCPVB\_UV\_op[2:0]** によって、選択することができます。

表 7.10.2.1 VCP-VB 低電圧検出時の動作設定（概要）

| 動作設定コマンド<br>VCPVB_UV_op[2:0] | 検出<br>推移         | 動作概要<br>R=レジスター、G=ゲートドライブ、C=チャージポンプ                                                                       |

|------------------------------|------------------|-----------------------------------------------------------------------------------------------------------|

| “000”                        | -<br>(検出、<br>復帰) | R: 影響を与えない<br>G: 影響を与えない<br>C: 影響を与えない                                                                    |

| “001”                        | 検出               | R: ステータスレジスターVCPVB_UV を 1 にする。<br>G: 影響を与えない<br>C: 影響を与えない                                                |

|                              | 復帰               | R: VCPVB_UV=1 を保持。<br>その後、クリアコマンド VCPVB_UV_cl=1 とすることで、VCPVB_UV=0 となる。<br>G: 影響を与えない<br>C: 影響を与えない        |

| “010”                        | 検出               | R: VCPVB_UV=1<br>G: 全てのゲートドライブを停止する。<br>C: 影響を与えない                                                        |

|                              | 復帰               | R: VCPVB_UV=1 を保持。その後 VCPVB_UV_cl=1 で VCPVB_UV=0。<br>G: 速やかにゲートドライブを再開する。<br>C: 影響を与えない                   |

| “011”                        | 検出               | R: VCPVB_UV=1<br>G: 全てのゲートドライブを停止する。<br>C: 影響を与えない                                                        |

|                              | 復帰               | R: VCPVB_UV=1 を保持。その後 VCPVB_UV_cl=1 で VCPVB_UV=0。<br>G: ゲートドライブ停止を保持。その後 VCPVB_UV_cl=1 で再開。<br>C: 影響を与えない |

| “100”                        | -                | Reserved. 指定すると、SPI エラーになります。                                                                             |

| “101”                        | -                | Reserved. 指定すると、SPI エラーになります。                                                                             |

| “110”                        | -                | Reserved. 指定すると、SPI エラーになります。                                                                             |

| “111”                        | -                | Reserved. 指定すると、SPI エラーになります。                                                                             |

注: “Reserved”としてある設定は使用しないでください。

表 7.10.2.2 VCP-VB 低電圧検出時の動作設定（詳細）

| 動作設定<br>コマンド<br>VCPVB_UV_op<br>[2:0]<br>7.18.14 | 検出<br>推移 | IN11,IN12,<br>IN21,IN22 | Charge<br>Pump | CPDO<br>端子 | RPPO<br>端子 | GH1-SH1,<br>GL1-SL,<br>GH2-SH2,<br>GL2-SL | VCPVB_UV<br>レジスター |

|-------------------------------------------------|----------|-------------------------|----------------|------------|------------|-------------------------------------------|-------------------|

| “000”                                           | -        | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | 0                 |

| “001”                                           | 検出       | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | 1                 |

|                                                 | 復帰       | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | クリア後<br>0         |

| “010”                                           | 検出       | Do not care             | 動作             | 動作         | VCP        | L, L, L, L                                | 1                 |

|                                                 | 復帰       | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作再開                                      | クリア後<br>0         |

| “011”                                           | 検出       | Do not care             | 動作             | 動作         | VCP        | L, L, L, L                                | 1                 |

|                                                 | 復帰       | 指示(H,L)                 | 動作             | 動作         | VCP        | クリア後<br>再開                                | クリア後<br>0         |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

Note cmd = Command , sts = Status

図 7.10.2.1 VCP-VB 低電圧検出時の動作

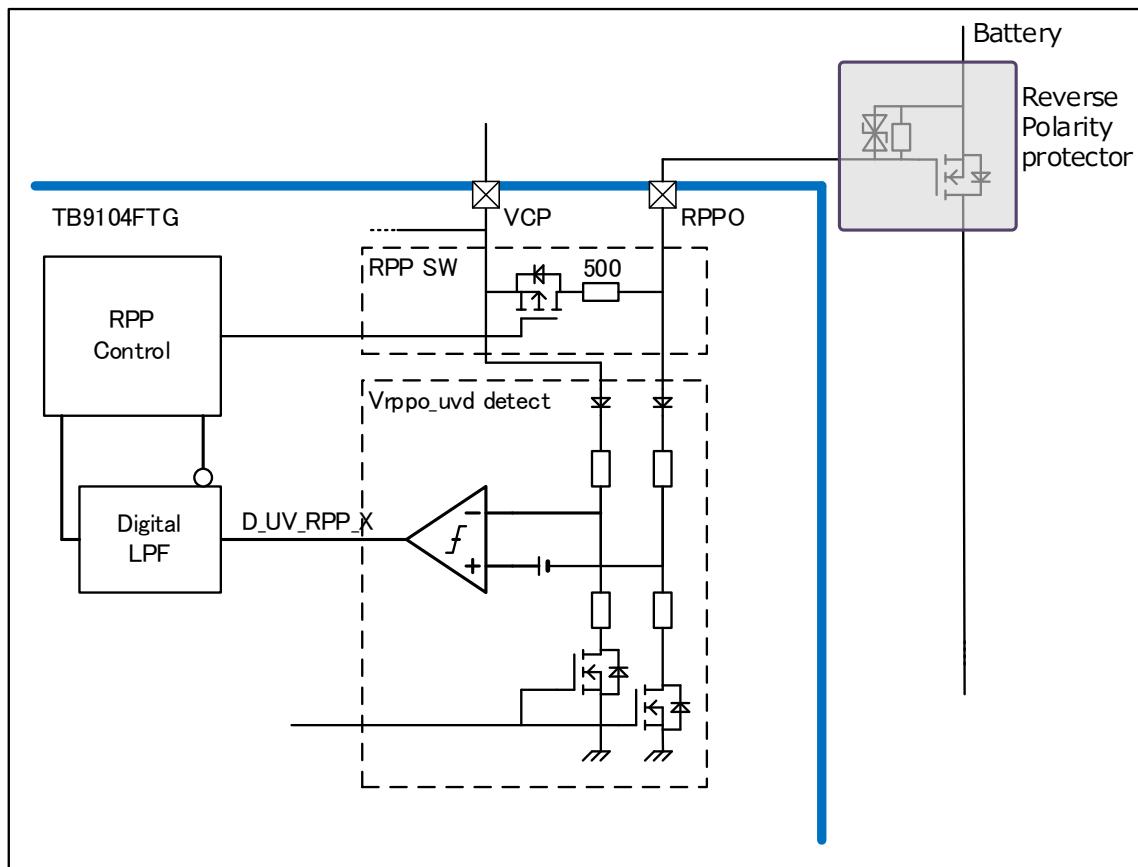

## 7.11. 逆接保護回路駆動用ゲートドライバ回路

逆接保護回路駆動用ゲートドライバーは、バッテリーと、外部n型MOSFETで構成されるブリッジ回路の間に設けられる、逆接保護のための外部n型MOSFET（以下逆接保護FETと略します）を駆動する回路です。バッテリーが逆極性で接続されたとき、逆接保護回路駆動用ゲートドライバーは逆接保護FETをオフにします。バッテリーが正しい極性で接続されているときは、チャージポンプ回路が動作している間は常に逆接保護FETをオンにします。また、逆接保護FETがオフであってもボディーダイオードを通してブリッジ回路へ電流が供給されます。逆接保護回路駆動用ゲートドライバーは、バッテリー逆接続時にあらゆる経路でRPPO端子へ逆流しないよう設計されています。逆接保護回路駆動用ゲートドライバーは、リセット状態やスタンバイ状態で、RPPO端子からの電流を遮断します。

図 7.11.1 逆接保護回路駆動用ゲートドライバー回路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

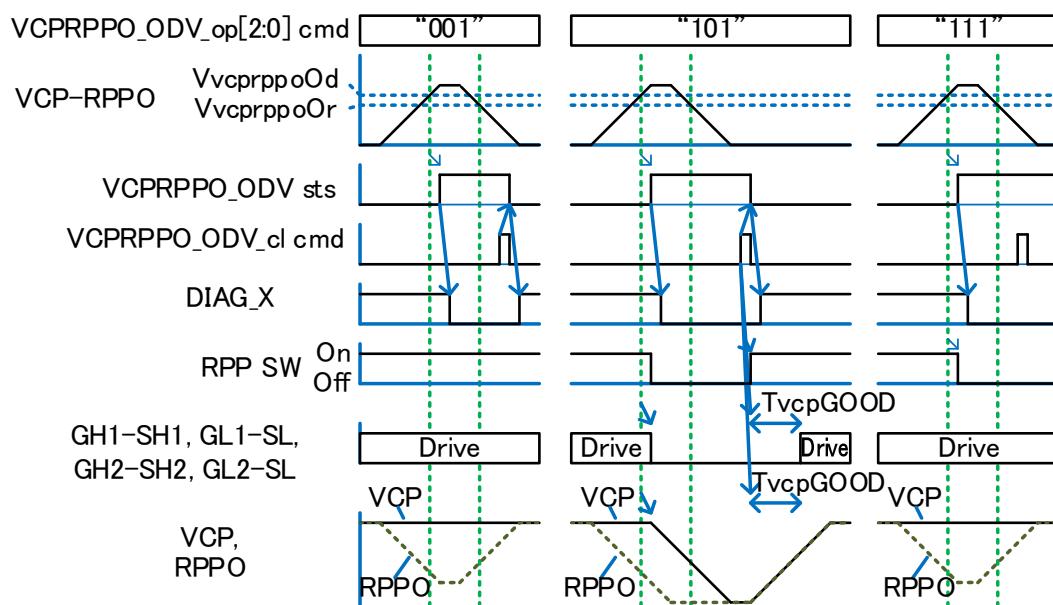

### 7.11.1. VCP-RPPO 高電圧検出回路と異常処理

VCP-RPPO 高電圧検出回路は、RPPO 端子の過電流を検出するため、VCP 端子と RPPO 端子の間の電圧を監視します。通常動作状態に移行した直後の  $T_{wake}$  期間とチャージポンプ起動後の  $T_{vcppGood}$  期間は、昇圧が不十分ですので、VCP,RPPO 間高電圧検出異常とは判定しません。

VCP 端子、RPPO 端子間の電圧が  $V_{vcprppoOd}$  以上であると、TB9104FTG は異常と判断します。

VCP 端子、RPPO 端子間の電圧が  $V_{vcprppoOr}$  以下であると、TB9104FTG は正常と判断します。

コンパレーターは端子間電圧に重畠するノイズによるグリッチを除去するため、ヒステリシス電圧  $V_{vcprppoOphys}$  を備えています。さらに後段に LPF を備え、 $T_{vcprppoOpw}$  を超えた幅の信号だけを利用します。

VCP-RPPO 高電圧検出したときの動作は、SPI から動作設定コマンド  $VCPRPPO\_ODV\_op[2:0]$  によって、選択することができます。

表 7.11.1.1 VCP-RPPO 高電圧検出時の動作設定（概要）

| 動作設定コマンド<br>VCPRPPO_ODV_op[2:0] | 検出<br>推移     | 動作概要<br>R=レジスター、G=ゲートドライブ、C=チャージポンプ、P=RPPO スイッチ                                                                                                                                                                                         |

|---------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| “000”                           | -<br>(検出、復帰) | R: 影響を与えない<br>G: 影響を与えない<br>C: 影響を与えない<br>P: RPPO 端子への VCP 電圧の供給を行う。                                                                                                                                                                    |

| “001”                           | 検出           | R: ステータスレジスター- $VCPRPPO\_ODV$ を 1 にする。<br>G: 影響を与えない<br>C: 影響を与えない<br>P: RPPO 端子への VCP 電圧の供給を行う。                                                                                                                                        |

|                                 | 復帰           | R: $VCPRPPO\_ODV=1$ を保持。その後、クリアコマンド $VCPRPPO\_ODV\_cl=1$ とすることで、 $VCPRPPO\_ODV=0$ となる。<br>G: 影響を与えない<br>C: 影響を与えない<br>P: RPPO 端子への VCP 電圧の供給を行う。                                                                                        |

| “010”                           | -            | Reserved. 指定すると、SPI エラーになります。                                                                                                                                                                                                           |

| “011”                           | -            | Reserved. 指定すると、SPI エラーになります。                                                                                                                                                                                                           |

| “100”                           | -            | Reserved 注 4                                                                                                                                                                                                                            |

| “101”                           | 検出           | R: $VCPRPPO\_ODV=1$<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。<br>P: RPPO 端子への VCP 電圧の供給を停止する。                                                                                                                                          |

|                                 | 復帰<br>注 1    | R: $VCPRPPO\_ODV=1$ を保持。<br>その後 $VCPRPPO\_ODV\_cl=1$ で $VCPRPPO\_ODV=0$ 。<br>G: ゲートドライブ停止を保持。その後 $VCPRPPO\_ODV\_cl=1$ で再開。<br>C: チャージポンプ停止を保持。その後 $VCPRPPO\_ODV\_cl=1$ で再開。<br>P: RPPO 端子への VCP 電圧供給停止を保持。その後 $VCPRPPO\_ODV\_cl=1$ で再開。 |

| “110”                           | -            | Reserved. 指定すると、SPI エラーになります。                                                                                                                                                                                                           |

| “111”                           | 検出           | R: $VCPRPPO\_ODV=1$<br>G: ゲートドライブ動作には影響を与えない。<br>C: チャージポンプ動作には影響を与えない。<br>P: RPPO 端子への VCP 電圧の供給を停止する。                                                                                                                                 |

|                                 | 復帰<br>注 2    | R: $VCPRPPO\_ODV=1$ を保持。<br>G: ゲートドライブ動作には影響を与えない。<br>C: チャージポンプ動作には影響を与えない。<br>P: RPPO 端子への VCP 電圧供給停止を保持。                                                                                                                             |

注 1: 異常を検出しチャージポンプが停止すると、VCP 端子は VB 電圧となります。RPPO 端子への VCP 電圧の供給を停止すると、RPPO 端子の電圧は外部回路に依存しており、復帰できない可能

性があります。強制的に動作を再開させるには、**REGreset** コマンドを発行するか、**STBY\_X** 端子を **Low** にして、初期化する必要があります。

注 2: 異常を検出してもチャージポンプは動作しており、VCP 電圧は VB を上回ったままで復帰できない可能性があります。強制的に動作を開始させるには、**REGreset** コマンドを発行するか、**STBY\_X** 端子を **Low** にして、全動作を初期化する必要があります。

注 3: “Reserved”としてある設定は使用しないでください。

注 4: **VCPRPPO\_ODV\_op** に”110”を設定すると、異常検出時にゲートドライブ、チャージポンプを停止しますが、VCP 端子と RPPO 端子の電位差が無くなり、正常に戻ったと判断して動作を再開してしまう現象が見られます。そのため、これらの設定を薦めません。

表 7.11.1.2 VCP-RPPO 高電圧検出時の動作設定（詳細）

| 動作設定コマンド<br>VCPRPPO_ODV_op<br>[2:0]<br>7.18.15 | 検出<br>推移 | IN11,IN12,<br>IN21,IN22 | Charge<br>Pump | CPDO<br>端子 | RPPO<br>端子 | GH1-SH1,<br>GL1-SL,<br>GH2-SH2,<br>GL2-SL | VCPRPPO_ODV<br>レジスター |

|------------------------------------------------|----------|-------------------------|----------------|------------|------------|-------------------------------------------|----------------------|

| “000”                                          | 一        | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | 0                    |

| “001”                                          | 検出       | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | 1                    |

|                                                | 復帰       | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | クリア後<br>0            |

| “101”                                          | 検出       | Do not care             | 停止             | Z          | 停止         | RL,RL,RL,RL                               | 1                    |

|                                                | 復帰       | 指示(H,L)                 | クリア後<br>再開     | クリア<br>後再開 | クリア<br>後再開 | クリア後<br>再開                                | クリア後<br>0            |

| “111”                                          | 検出       | 指示(H,L)                 | 動作             | 動作         | 停止         | 動作                                        | 1                    |

|                                                | 復帰       | 指示(H,L)                 | 動作             | 動作         | 停止         | 動作                                        | 1                    |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

図 7.11.1.1 VCP-RPPO 高電圧検出時の動作

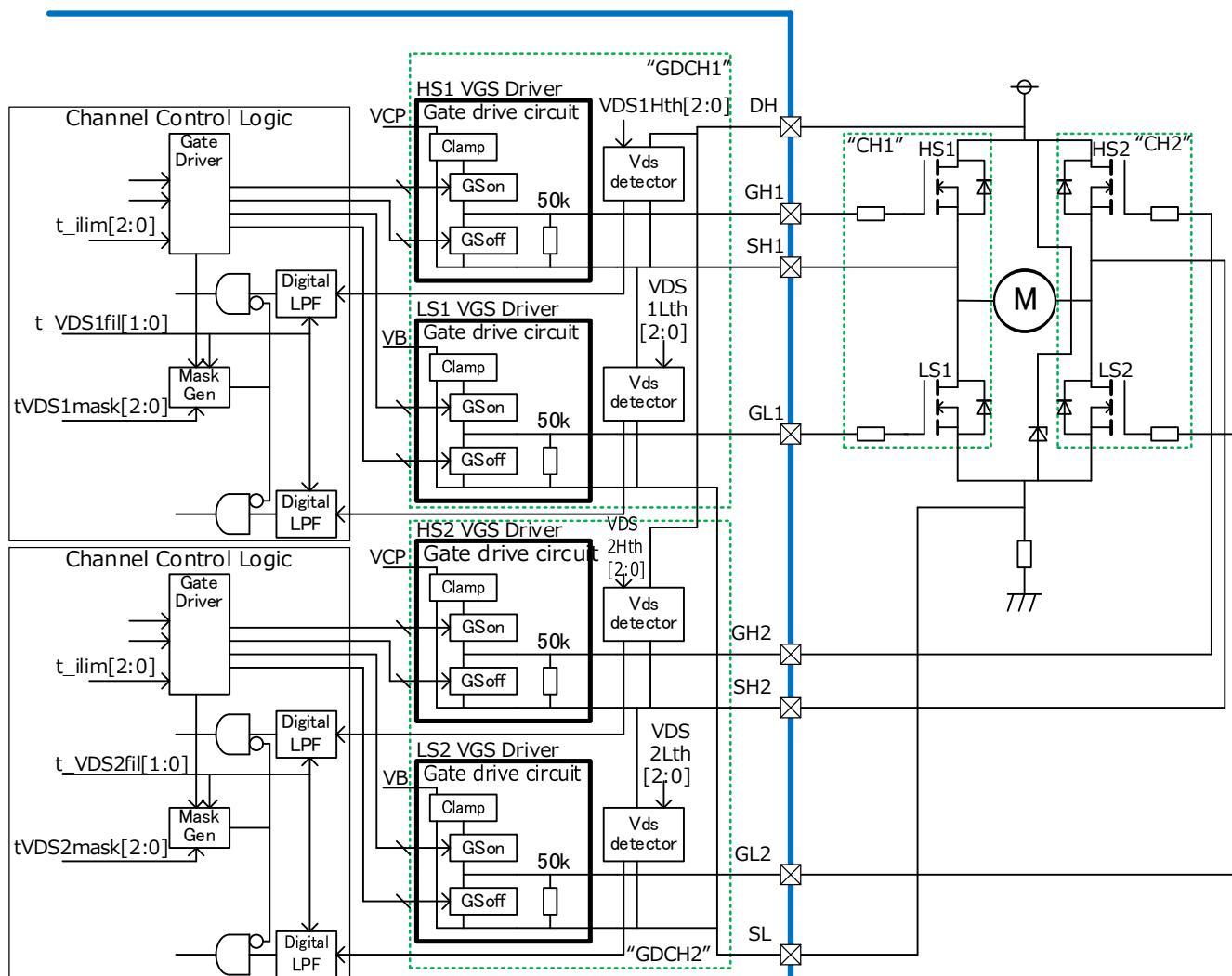

## 7.12. ゲートドライバー回路

ゲートドライバー回路は、ハイサイドは VCP を電源とします。ゲートドライバー回路は、外部 n 型 MOSFET をオン、オフ、ハイインピーダンスの 3 状態にします。

オンにするととき、ゲート・ソース間耐電圧を超えないようするため、ソース端子の電圧を基にゲート・ソース間電圧の上限を制限します。オフにするととき、内蔵する MOSFET でゲート・ソース間をシャントします。ハイインピーダンスの時、外部 n 型 MOSFET のゲートを保護するため、ゲート・ソース間は、 $50\text{k}\Omega$  の抵抗を通してシャントしています。

通常動作状態に移行した直後の  $\text{T}_{\text{wake}}$  期間とチャージポンプ起動後の  $\text{T}_{\text{VCPGOOD}}$  期間は、昇圧が不十分ですので、ゲートドライブは停止とします。

$\text{GH1}, \text{GL1}, \text{GH2}, \text{GL2}$  端子は天絡地絡しても破壊しません。

ハイサイドおよびローサイドの駆動は、 $\text{Turn on}, \text{Turn off}$  時間と  $t_{\text{ilim}}$  コマンドで設定した時間経過後、 $\text{I}_{\text{GS}}\text{,Imth}, \text{I}_{\text{GS}}\text{,Imtl}$  に電流を制限します。

詳細は図 7.17.1.4.1 を参照してください。

図 7.12.1 ゲートドライバー回路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

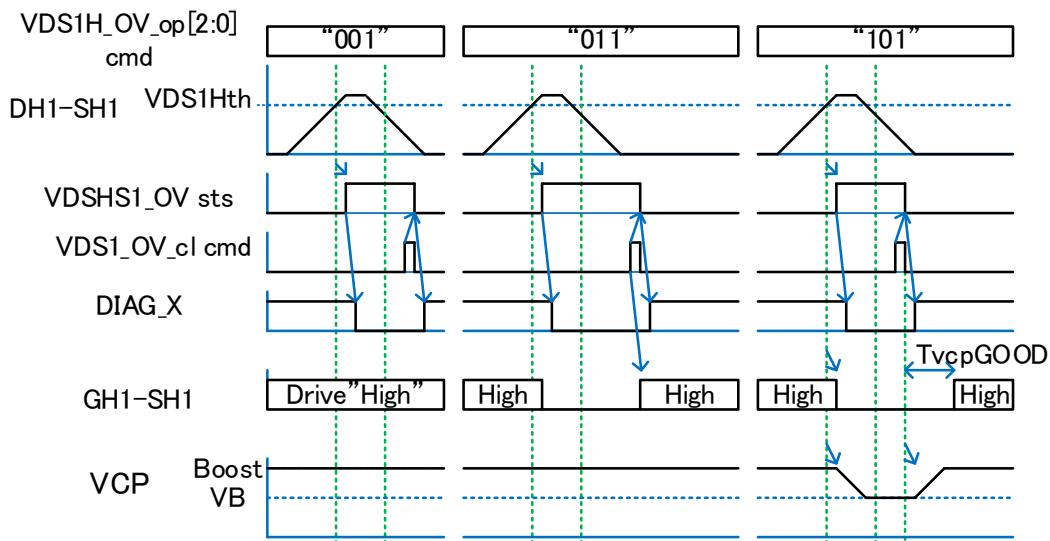

## 7.13. Vdson 高電圧検出回路と異常処理

TB9104FTG は、外部 n 型 MOSFET のゲートが駆動されている期間にドレイン、ソース間電圧  $V_{ds}$  が  $VDS1Hth[2:0]$ ,  $VDS1Lth[2:0]$ ,  $VDS2Hth[2:0]$ ,  $VDS2Lth[2:0]$  で設定した電圧  $V_{dhshOd0} \sim V_{dhshOd7}$ ,  $V_{shsOd0} \sim V_{shsOd7}$  より低い正常な状態であるかを監視します。

$V_{dhshOd0} \sim V_{dhshOd7}$ ,  $V_{shsOd0} \sim V_{shsOd7}$  より高かった場合、過電流が流れている異常な状態と判断します。TB9104FTG は検出回路の後段に LPF を備え、 $t_{\_VDS1fil}[1:0]$ ,  $t_{\_VDS2fil}[1:0]$  で設定された幅を超えた信号だけを利用します。なお、IN11, IN12, IN21, IN22 端子によって駆動の指示が変更された場合、変更から SPI で設定した時間  $T_{Vds1MASK}[2:0]$ ,  $T_{Vds2MASK}[2:0]$  の間は、監視を中断します。

ハーフブリッジモードの場合、VDS1 高電圧と判断されたチャネルは、自チャネルに接続されている外部 n 型 MOSFET の駆動をシャットダウンします。

H ブリッジモードの場合は、どのチャネルで VDS1 高電圧と判断しても、ブリッジを構成する 4 外部 FET をシャットダウンします。

ここに出てきた  $V_{ds}$  高電圧検出電圧、デジタル LPF カットオフパルス幅  $T_{VdsOpw}$ 、指示変更時のマスク時間  $T_{VdsMASK}$  は、使用する外部回路で十分に検証の上、設定願います。

表 7.13.1 HS1 Vdson 高電圧検出時の動作設定（概要）

| 動作設定コマンド<br>VDS1H_OV_op[2:0] | 検出推移      | 動作概要<br>R=レジスター、G=ゲートドライブ、C=チャージポンプ                                                                                                                                    |

|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| “000”                        | 検出、<br>復帰 | R: 影響を与えない<br>G: 影響を与えない<br>C: 影響を与えない                                                                                                                                 |

| “001”                        | 検出        | R: ステータスレジスターVDSHS1_OV を 1 にする。<br>G: 影響を与えない<br>C: 影響を与えない                                                                                                            |

|                              | 復帰        | R: VDSHS1_OV を保持。<br>その後、クリアコマンド VDS1_OV_cl=1 とすることで、VDSHS1_OV =0, VDSLS1_OV =0 となる。<br>G: 影響を与えない<br>C: 影響を与えない                                                       |

| “010”                        | -         | Reserved 注 2                                                                                                                                                           |

| “011”                        | 検出        | R: ステータスレジスターVDSHS1_OV を 1 にする。<br>G: ・ハーフブリッジモード時、GDCH1 のゲートドライブをオフにする。<br>・H ブリッジモード時、全てのゲートドライブを停止する。<br>C: 影響を与えない                                                 |

|                              | 復帰        | R: VDSHS1_OV を保持。<br>その後、クリアコマンド VDS1_OV_cl=1 とすることで、VDSHS1_OV =0, VDSLS1_OV =0 となる。<br>G: ゲートドライブ停止を保持。その後 VDS1_OV_cl=1 で再開。<br>C: 影響を与えない                            |

| “100”                        | -         | Reserved 注 2                                                                                                                                                           |

| “101”                        | 検出        | R: ステータスレジスターVDSHS1_OV を 1 にする。<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                                             |

|                              | 復帰        | R: VDSHS1_OV を保持。<br>その後、クリアコマンド VDS1_OV_cl=1 とすることで、VDSHS1_OV =0, VDSLS1_OV =0 となる。<br>G: ゲートドライブ停止を保持。その後 VDS1_OV_cl=1 で再開。<br>C: チャージポンプ停止を保持。その後 VDS1_OV_cl=1 で再開。 |

| “110”                        | -         | Reserved 指定すると、SPI エラーになります。                                                                                                                                           |

| “111”                        | -         | Reserved 指定すると、SPI エラーになります。                                                                                                                                           |

注 1: “Reserved”としてある設定は使用しないでください。

注 2: VDS1H\_OV\_op に“010”, “100”を設定すると、異常検出時にゲートドライブを停止しますが、ドレイン、ソース間の電圧が正常に復帰したと判断して動作を再開してしまう現象が見られます。この現象が発生する環境では、停止と再開を繰り返してしまいます。そのため、これらの設定を薦めません。

表 7.13.2 HS1 Vdson 高電圧検出時の動作設定（詳細）

| 動作設定<br>コマンド<br>VDS1H_OV<br>_op[2:0]<br>7.18.17 | 検出<br>推移  | IN11,IN12   | Charge<br>Pump | CPDO<br>端子     | RPPO<br>端子 | GH1 - SH1,<br>GL1 - SL                   | VDSHS1_OV<br>レジスター |

|-------------------------------------------------|-----------|-------------|----------------|----------------|------------|------------------------------------------|--------------------|

| “000”                                           | 検出、<br>復帰 | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | 0                  |

| “001”                                           | 検出        | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | 1                  |

|                                                 | 復帰        | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | クリア後 0             |

| “011”                                           | 検出        | Do not care | 動作             | 動作             | VCP        | L, L<br>H ブリッジモード時は<br>GH2,GL2 も<br>L, L | 1                  |

|                                                 | 復帰        | 指示(H,L)     | 動作             | 動作             | VCP        | クリア後<br>動作再開                             | クリア後 0             |

| “101”                                           | 検出        | Do not care | 停止             | Z              | VCP        | 全ゲートドライブを RL<br>とする                      | 1                  |

|                                                 | 復帰        | 指示(H,L)     | クリア後<br>再開     | クリア<br>後<br>再開 | VCP        | クリア後<br>動作再開                             | クリア後 0             |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

表 7.13.3 LS1 Vdson 高電圧検出時の動作設定（概要）

| 動作設定コマンド<br>VDS1L_OV_op[2:0] | 検出推移      | 動作概要<br>R=レジスター、G=ゲートドライブ、C=チャージポンプ                                                                                                                                    |

|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| “000”                        | 検出、<br>復帰 | R: 影響を与えない<br>G: 影響を与えない<br>C: 影響を与えない                                                                                                                                 |

| “001”                        | 検出        | R: ステータスレジスターVDSLS1_OV を 1 にする。<br>G: 影響を与えない<br>C: 影響を与えない                                                                                                            |

|                              | 復帰        | R: VDSLS1_OV を保持。<br>その後、クリアコマンド VDS1_OV_ci=1 とすることで、VDSHS1_OV =0, VDSLS1_OV =0 となる。<br>G: 影響を与えない<br>C: 影響を与えない                                                       |

| “010”                        | -         | Reserved 注 2                                                                                                                                                           |

| “011”                        | 検出        | R: ステータスレジスターVDSLS1_OV を 1 にする。<br>G: ・ハーフブリッジモード時、GDCH1 のゲートドライブをオフにする。<br>・H ブリッジモード時、全てのゲートドライブを停止する。<br>C: 影響を与えない                                                 |

|                              | 復帰        | R: VDSLS1_OV を保持。<br>その後、クリアコマンド VDS1_OV_ci=1 とすることで、VDSHS1_OV =0, VDSLS1_OV =0 となる。<br>G: ゲートドライブ停止を保持。その後 VDS1_OV_ci=1 で再開。<br>C: 影響を与えない                            |

| “100”                        | -         | Reserved 注 2                                                                                                                                                           |

| “101”                        | 検出        | R: ステータスレジスターVDSLS1_OV を 1 にする。<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                                             |

|                              | 復帰        | R: VDSLS1_OV を保持。<br>その後、クリアコマンド VDS1_OV_ci=1 とすることで、VDSHS1_OV =0, VDSLS1_OV =0 となる。<br>G: ゲートドライブ停止を保持。その後 VDS1_OV_ci=1 で再開。<br>C: チャージポンプ停止を保持。その後 VDS1_OV_ci=1 で再開。 |

| “110”                        | -         | Reserved 指定すると、SPI エラーになります。                                                                                                                                           |

| “111”                        | -         | Reserved 指定すると、SPI エラーになります。                                                                                                                                           |

注 1: “Reserved”としてある設定は使用しないでください。

注 2: VDS1L\_OV\_op に”010”, “100”を設定すると、異常検出時にゲートドライブを停止しますが、ド

レイン、ソース間の電圧が正常に復帰したと判断して動作を再開してしまう現象が見られます。

この現象が発生する環境では、停止と再開を繰り返してしまいます。そのため、これらの設定を薦めません。

表 7.13.4 LS1 Vdson 高電圧検出時の動作設定（詳細）

| 動作設定<br>コマンド<br>VDS1L_OV<br>_op[2:0]<br>7.18.18 | 検出<br>推移  | IN11,IN12   | Charge<br>Pump | CPDO<br>端子     | RPPO<br>端子 | GH1 - SH1,<br>GL1 - SL                   | VDSLS1_OV<br>レジスター |

|-------------------------------------------------|-----------|-------------|----------------|----------------|------------|------------------------------------------|--------------------|

| “000”                                           | 検出、<br>復帰 | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | 0                  |

| “001”                                           | 検出        | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | 1                  |

|                                                 | 復帰        | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | クリア後 0             |

| “011”                                           | 検出        | Do not care | 動作             | 動作             | VCP        | L, L<br>H ブリッジモード時は<br>GH2,GL2 も<br>L, L | 1                  |

|                                                 | 復帰        | 指示(H,L)     | 動作             | 動作             | VCP        | クリア後<br>動作再開                             | クリア後 0             |

| “101”                                           | 検出        | Do not care | 停止             | Z              | VCP        | 全ゲートドライブを RL<br>とする                      | 1                  |

|                                                 | 復帰        | 指示(H,L)     | クリア後<br>再開     | クリア<br>後<br>再開 | VCP        | クリア後<br>動作再開                             | クリア後 0             |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

表 7.13.5 HS2 Vdson 高電圧検出時の動作設定（概要）

| 動作設定コマンド<br>VDS2H_OV_op[2:0] | 検出推移      | 動作概要<br>R=レジスター、G=ゲートドライブ、C=チャージポンプ                                                                                                                                    |

|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| “000”                        | 検出、<br>復帰 | R: 影響を与えない<br>G: 影響を与えない<br>C: 影響を与えない                                                                                                                                 |

| “001”                        | 検出        | R: ステータスレジスターVDSHS2_OV を 1 にする。<br>G: 影響を与えない<br>C: 影響を与えない                                                                                                            |

|                              | 復帰        | R: VDSHS2_OV を保持。<br>その後、クリアコマンド VDS2_OV_ci=1 とすることで、VDSHS2_OV =0, VDSLS2_OV =0 となる。<br>G: 影響を与えない<br>C: 影響を与えない                                                       |

| “010”                        | -         | Reserved 注 2                                                                                                                                                           |

| “011”                        | 検出        | R: ステータスレジスターVDSHS2_OV を 1 にする。<br>G: ・ハーフブリッジモード時、GDCH2 のゲートドライブをオフにする。<br>・H ブリッジモード時、全てのゲートドライブを停止する。<br>C: 影響を与えない                                                 |

|                              | 復帰        | R: VDSHS2_OV を保持。<br>その後、クリアコマンド VDS2_OV_ci=1 とすることで、VDSHS2_OV =0, VDSLS2_OV =0 となる。<br>G: ゲートドライブ停止を保持。その後 VDS2_OV_ci=1 で再開。<br>C: 影響を与えない                            |

| “100”                        | -         | Reserved 注 2                                                                                                                                                           |

| “101”                        | 検出        | R: ステータスレジスターVDSHS2_OV を 1 にする。<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                                             |

|                              | 復帰        | R: VDSHS2_OV を保持。<br>その後、クリアコマンド VDS2_OV_ci=1 とすることで、VDSHS2_OV =0, VDSLS2_OV =0 となる。<br>G: ゲートドライブ停止を保持。その後 VDS2_OV_ci=1 で再開。<br>C: チャージポンプ停止を保持。その後 VDS2_OV_ci=1 で再開。 |

| “110”                        | -         | Reserved 指定すると、SPI エラーになります。                                                                                                                                           |

| “111”                        | -         | Reserved 指定すると、SPI エラーになります。                                                                                                                                           |

注 1: “Reserved”としてある設定は使用しないでください。

注 2: VDS2H\_OV\_op に“010”, “100”を設定すると、異常検出時にゲートドライブを停止しますが、ド

レイン、ソース間の電圧が正常に復帰したと判断して動作を再開してしまう現象が見られます。

この現象が発生する環境では、停止と再開を繰り返してしまいます。そのため、これらの設定を薦めません。

表 7.13.6 HS2 Vdson 高電圧検出時の動作設定 (詳細)

| 動作設定<br>コマンド<br>VDS2H_OV<br>_op[2:0]<br>7.18.23 | 検出<br>推移 | IN21,IN22   | Charge<br>Pump | CPDO<br>端子     | RPPO<br>端子 | GH2 - SH2,<br>GL2 - SL                   | VDSHS2_OV<br>レジスター |

|-------------------------------------------------|----------|-------------|----------------|----------------|------------|------------------------------------------|--------------------|

| “000”                                           | -        | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | 0                  |

| “001”                                           | 検出       | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | 1                  |

|                                                 | 復帰       | 指示(H,L)     | 動作             | 動作             | VCP        | 動作、動作                                    | クリア後 0             |

| “011”                                           | 検出       | Do not care | 動作             | 動作             | VCP        | L, L<br>H ブリッジモード時は<br>GH1,GL1 も<br>L, L | 1                  |

|                                                 | 復帰       | 指示(H,L)     | 動作             | 動作             | VCP        | クリア後<br>動作再開                             | クリア後 0             |

| “101”                                           | 検出       | Do not care | 停止             | Z              | VCP        | 全ゲートドライブを RL<br>とする                      | 1                  |

|                                                 | 復帰       | 指示(H,L)     | クリア後<br>再開     | クリア<br>後<br>再開 | VCP        | クリア後<br>動作再開                             | クリア後 0             |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

表 7.13.7 LS2 Vdson 高電圧検出時の動作設定（概要）

| 動作設定コマンド<br>VDS2L_OV_op[2:0] | 検出推移 | 動作概要<br>R=レジスター、G=ゲートドライブ、C=チャージポンプ                                                                                                                                  |

|------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| “000”                        | -    | R: 影響を与えない<br>G: 影響を与えない<br>C: 影響を与えない                                                                                                                               |

| “001”                        | 検出   | R: ステータスレジスターVDSL2_OV を 1 にする。<br>G: 影響を与えない<br>C: 影響を与えない                                                                                                           |

|                              | 復帰   | R: VDSL2_OV を保持。<br>その後、クリアコマンド VDS2_OV_ci=1 とすることで、VDSHS2_OV =0, VDSL2_OV =0 となる。<br>G: 影響を与えない<br>C: 影響を与えない                                                       |

| “010”                        | -    | Reserved 注 2                                                                                                                                                         |

| “011”                        | 検出   | R: ステータスレジスターVDSL2_OV を 1 にする。<br>G: ・ハーフブリッジモード時、GDCH2 のゲートドライブをオフにする。<br>・H ブリッジモード時、全てのゲートドライブを停止する。<br>C: 影響を与えない                                                |

|                              | 復帰   | R: VDSL2_OV を保持。<br>その後、クリアコマンド VDS2_OV_ci=1 とすることで、VDSHS2_OV =0, VDSL2_OV =0 となる。<br>G: ゲートドライブ停止を保持。その後 VDS2_OV_ci=1 で再開。<br>C: 影響を与えない                            |

| “100”                        | -    | Reserved 注 2                                                                                                                                                         |

| “101”                        | 検出   | R: ステータスレジスターVDSL2_OV を 1 にする。<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                                            |

|                              | 復帰   | R: VDSL2_OV を保持。<br>その後、クリアコマンド VDS2_OV_ci=1 とすることで、VDSHS2_OV =0, VDSL2_OV =0 となる。<br>G: ゲートドライブ停止を保持。その後 VDS2_OV_ci=1 で再開。<br>C: チャージポンプ停止を保持。その後 VDS2_OV_ci=1 で再開。 |

| “110”                        | -    | Reserved 指定すると、SPI エラーになります。                                                                                                                                         |

| “111”                        | -    | Reserved 指定すると、SPI エラーになります。                                                                                                                                         |

注 1: “Reserved”としてある設定は使用しないでください。

注 2: VDS2L\_OV\_op に“010”, “100”を設定すると、異常検出時にゲートドライブを停止しますが、ド

レイン、ソース間の電圧が正常に復帰したと判断して動作を再開してしまう現象が見られます。

この現象が発生する環境では、停止と再開を繰り返してしまいます。そのため、これらの設定を薦めません。

表 7.13.8 LS2 Vdson 高電圧検出時の動作設定（詳細）

| 動作設定<br>コマンド<br>VDS2L_OV<br>_op[2:0]<br>7.18.24 | 検出<br>推移  | IN21,IN22   | Charge<br>Pump | CPDO<br>端子 | RPPO<br>端子 | GH2 - SH2,<br>GL2 - SL                   | VDSLS2_OV<br>レジスター |

|-------------------------------------------------|-----------|-------------|----------------|------------|------------|------------------------------------------|--------------------|

| “000”                                           | 検出、<br>復帰 | 指示(H,L)     | 動作             | 動作         | VCP        | 動作、動作                                    | 0                  |

| “001”                                           | 検出        | 指示(H,L)     | 動作             | 動作         | VCP        | 動作、動作                                    | 1                  |

|                                                 | 復帰        | 指示(H,L)     | 動作             | 動作         | VCP        | 動作、動作                                    | クリア後 0             |

| “011”                                           | 検出        | Do not care | 動作             | 動作         | VCP        | L, L<br>H ブリッジモード時は<br>GH1,GL1 も<br>L, L | 1                  |

|                                                 | 復帰        | 指示(H,L)     | 動作             | 動作         | VCP        | クリア後<br>動作再開                             | クリア後 0             |

| “101”                                           | 検出        | Do not care | 停止             | Z          | VCP        | 全ゲートドライブを RL<br>とする                      | 1                  |

|                                                 | 復帰        | 指示(H,L)     | クリア後<br>再開     | クリア後<br>再開 | VCP        | クリア後<br>動作再開                             | クリア後 0             |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

| HS1                  | LS1                  | HS2                  | LS2                  |

|----------------------|----------------------|----------------------|----------------------|

| VDS1H_OV_op[2:0] cmd | VDS1L_OV_op[2:0] cmd | VDS2H_OV_op[2:0] cmd | VDS2L_OV_op[2:0] cmd |

| DH-SH1               | SH1-SL               | DH-SH2               | SH2-SL               |

| VDS1Hth[2:0] cmd     | VDS1Lth[2:0] cmd     | VDS2Hth[2:0] cmd     | VDS2Lth[2:0] cmd     |

| VDSHS1_OV sts        | VDSLs1_OV sts        | VDSHS2_OV sts        | VDSLs2_OV sts        |

| VDS1_OV_cl cmd       |                      | VDS2_OV_cl cmd       |                      |

| GH1-SH1              | GL1-SL               | GH2-SH2              | GL2-SL               |

Note cmd = Command, sts = Status

図 7.13.1 HS1 Vdson 高電圧検出時の動作

図 7.13.1 に外部 n 型 MOSFET "HS1" のドレイン、ソース間の電圧異常検出と、動作設定ごとの復帰の様子を示します。"LS1", "HS2", "LS2" については表にある端子名、コマンド名、ステータス名に置き換えて参照してください。

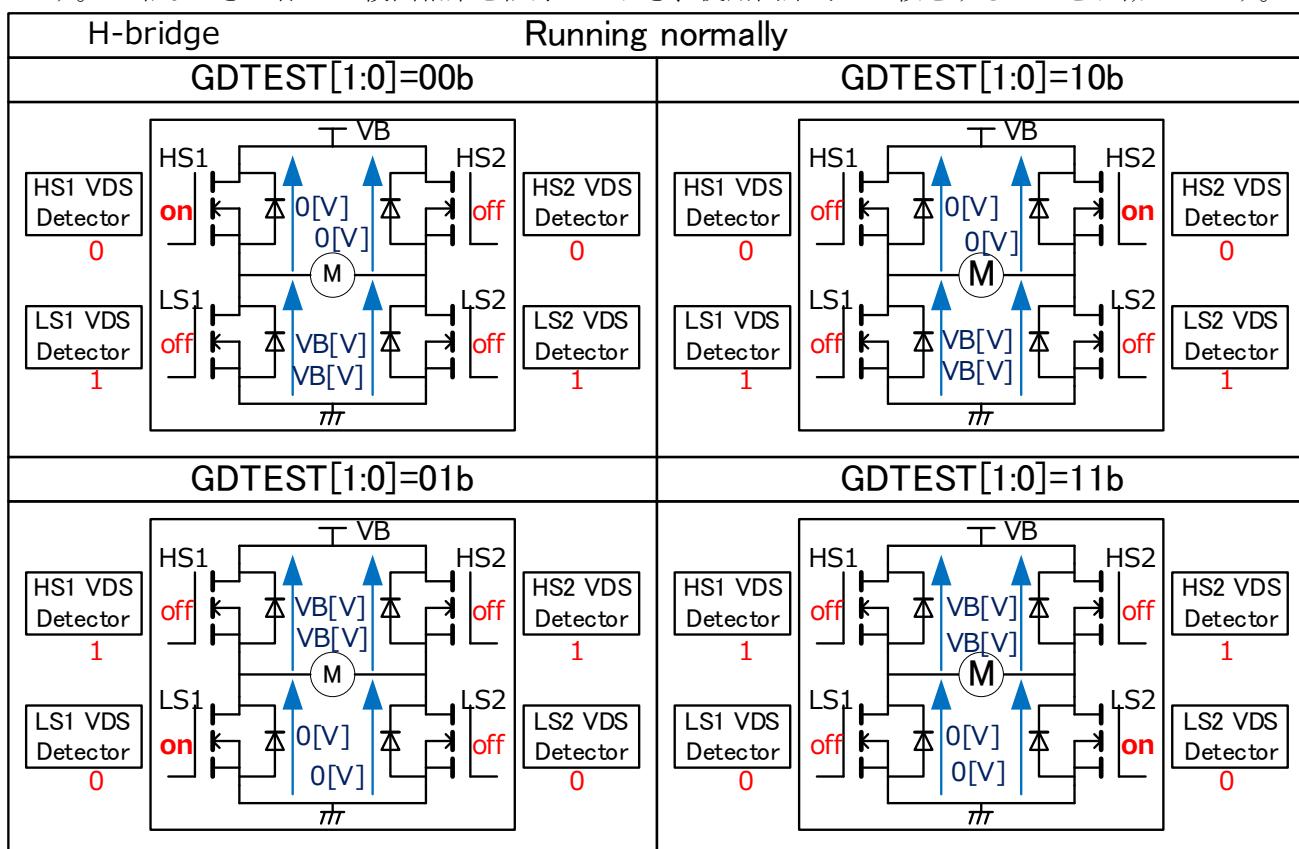

## 7.14. SH1,SH2 状態検出

TB9104FTG は、GDTESTen コマンドによって、SH1 端子、SH2 端子間に接続されるモーターや配線の断線を検出できる機能を備えています。

本テスト中(GDTESTen=1)も、Vds オン時の過電圧検出機能は動作をします。事前に動作設定コマンド VDS1H\_OV\_op, VDS1L\_OV\_op, VDS2H\_OV\_op, VDS2L\_OV\_op を"011"など過電圧時にゲートドライブを停止させる設定にし、VDS1Hth, VDS1Lth, VDS2Hth, VDS2Lth, t\_VDS1fil, t\_VDS2fil, tVDS1mask, tVDS2mask も適切に設定してください。

次に GDTESTen コマンドを 1 にすると、ゲートドライバーは GDTEST[1:0] コマンドの指示に従って外部 n 型 MOSFET を 1 つオンにします。

正常なら SH1,SH2 は図 7.14.1 に示すとおりオンした外部 n 型 MOSFET によって、バッテリー電圧 VB やグラウンド電圧 (0V) に変化します。このときの SH1 端子、SH2 端子の電圧を Vds 検出コンパレーターで測定します。測定した結果は、VDS1Hsts, VDS1Lsts, VDS2Hsts, VDS2Lsts レジスターで見ることができます。断線など何らかの異常がある場合、図 7.14.1 のようにはならない可能性があります。

本テスト時に限らず通常動作の開始時にも、外部 n 型 MOSFET 周辺で天絡地絡があった場合、大電流が流れ、破損や焼損の恐れがあります。TB9104FTG は天絡地絡を検出する機能を備えていません。別途外部に対策が必要か検討ください。

また、外部 n 型 MOSFET 全オフ時の各 Vds 検出結果は、TB9104FTG の外部回路や部品により異なります。正常なときの各 Vds 検出結果を記録しておき、使用開始時に比較をすることをお勧めします。

図 7.14.1 SH1,SH2 状態検出

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

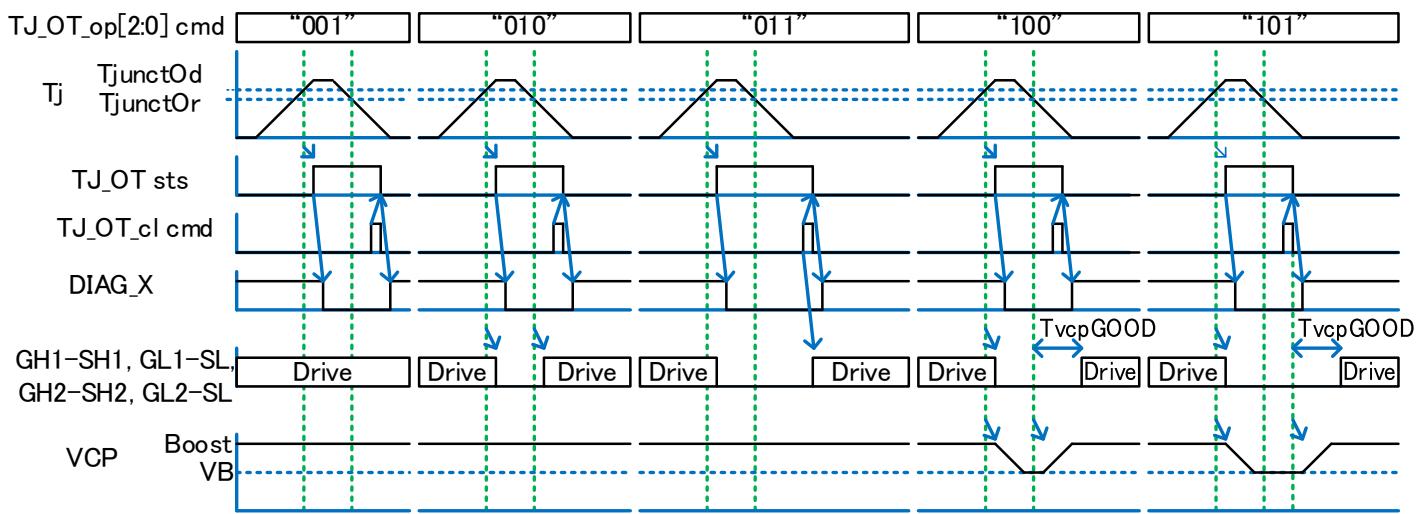

## 7.15. 過熱検出回路

過熱検出センサーは、チップの温度を監視し、温度上昇を検出します。チップの温度が過熱検出温度  $T_{junctOd}$  を超えていると、TB9104FTG は異常と判定します。チップの温度が  $T_{junctOr}$  よりも低いと、TB9104FTG は正常と判定します。

過熱検出回路は、ヒステリシス  $T_{junctOhy}$  を備えています。さらに後段に LPF を備え、 $T_{junctOpw}$  を超えた幅の信号だけを利用します。過熱を検出したときの動作は、動作設定コマンド  $TJ\_OT\_op[2:0]$ によって、選択することができます。

図 7.15.1 過熱検出

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

表 7.15.1 過熱検出時の動作設定（概要）

| 動作設定コマンド<br>TJ_OT_op[2:0] | 検出推移 | 動作概要<br>R=レジスター、G=ゲートドライブ、C=チャージポンプ                                                                                    |

|---------------------------|------|------------------------------------------------------------------------------------------------------------------------|

| “000”                     | -    | R: 影響を与えない<br>G: 影響を与えない<br>C: 影響を与えない                                                                                 |

| “001”                     | 検出   | R: ステータスレジスターTJ_OT を 1 にする。<br>G: 影響を与えない<br>C: 影響を与えない                                                                |

|                           | 復帰   | R: TJ_OT=1 を保持。<br>その後、クリアコマンド TJ_OT_cl=1 とすることで、TJ_OT=0 となる。<br>G: 影響を与えない<br>C: 影響を与えない                              |

| “010”                     | 検出   | R: TJ_OT=1<br>G: 全てのゲートドライブを停止する。<br>C: 影響を与えない                                                                        |

|                           | 復帰   | R: TJ_OT=1 を保持。その後 TJ_OT_cl=1 で TJ_OT=0。<br>G: 速やかにゲートドライブを再開する。<br>C: 影響を与えない                                         |

| “011”                     | 検出   | R: TJ_OT=1<br>G: 全てのゲートドライブを停止する。<br>C: 影響を与えない                                                                        |

|                           | 復帰   | R: TJ_OT=1 を保持。その後 TJ_OT_cl=1 で TJ_OT=0。<br>G: ゲートドライブ停止を保持。その後 TJ_OT_cl=1 で再開。<br>C: 影響を与えない                          |

| “100”                     | 検出   | R: TJ_OT=1<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                  |

|                           | 復帰   | R: TJ_OT=1 を保持。その後 TJ_OT_cl=1 で TJ_OT=0。<br>G: 速やかにゲートドライブを再開する。<br>C: 速やかにチャージポンプを動作させる。                              |

| “101”                     | 検出   | R: TJ_OT=1<br>G: 全てのゲートドライブを停止する。<br>C: チャージポンプを停止する。                                                                  |

|                           | 復帰   | R: TJ_OT=1 を保持。その後 TJ_OT_cl=1 で TJ_OT=0。<br>G: ゲートドライブ停止を保持。その後 TJ_OT_cl=1 で再開。<br>C: チャージポンプ停止を保持。その後 TJ_OT_cl=1 で再開。 |

| “110”                     | -    | Reserved 指定すると、SPI エラーになります。                                                                                           |

| “111”                     | -    | Reserved 指定すると、SPI エラーになります。                                                                                           |

注: “Reserved”としてある設定は使用しないでください。

表 7.15.2 過熱検出時の動作設定（詳細）

| 動作設定コマンド<br>TJ_OT_op<br>[2:0]<br>7.18.16 | 検出<br>推移  | IN11,IN12,<br>IN21,IN22 | Charge<br>Pump | CPDO<br>端子 | RPPO<br>端子 | GH1-SH1,<br>GL1-SL,<br>GH2-SH2,<br>GL2-SL | TJ_OT<br>レジスター |

|------------------------------------------|-----------|-------------------------|----------------|------------|------------|-------------------------------------------|----------------|

| “000”                                    | 検出、<br>復帰 | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | 0              |

| “001”                                    | 検出        | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | 1              |

|                                          | 復帰        | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作                                        | クリア後<br>0      |

| “010”                                    | 検出        | Do not care             | 動作             | 動作         | VCP        | L, L, L, L                                | 1              |

|                                          | 復帰        | 指示(H,L)                 | 動作             | 動作         | VCP        | 動作再開                                      | クリア後<br>0      |

| “011”                                    | 検出        | Do not care             | 動作             | 動作         | VCP        | L, L, L, L                                | 1              |

|                                          | 復帰        | 指示(H,L)                 | 動作             | 動作         | VCP        | クリア後<br>再開                                | クリア後<br>0      |

| “100”                                    | 検出        | Do not care             | 停止             | Z          | VCP        | RL, RL, RL, RL                            | 1              |

|                                          | 復帰        | 指示(H,L)                 | 再開             | 再開         | VCP        | 動作再開                                      | クリア後<br>0      |

| “101”                                    | 検出        | Do not care             | 停止             | Z          | VCP        | RL, RL, RL, RL                            | 1              |

|                                          | 復帰        | 指示(H,L)                 | クリア後<br>再開     | クリア後<br>再開 | VCP        | クリア後<br>再開                                | クリア後<br>0      |

記号の説明 : RL = Resistive low H = High L = Low Z = High-impedance

Note cmd = Command , sts = Status

図 7.15.2 過熱検出時の動作

## 7.16. 電流センス回路

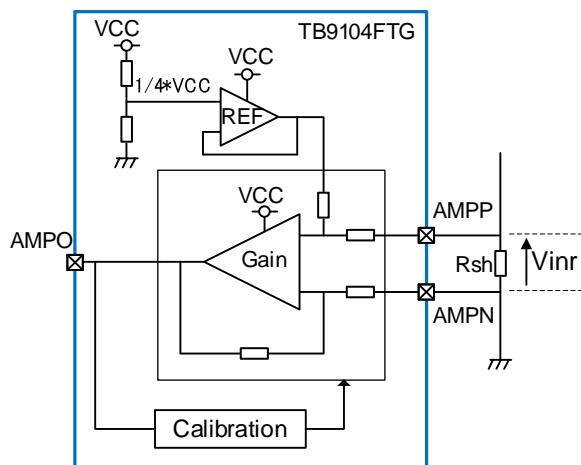

### 7.16.1. 構成

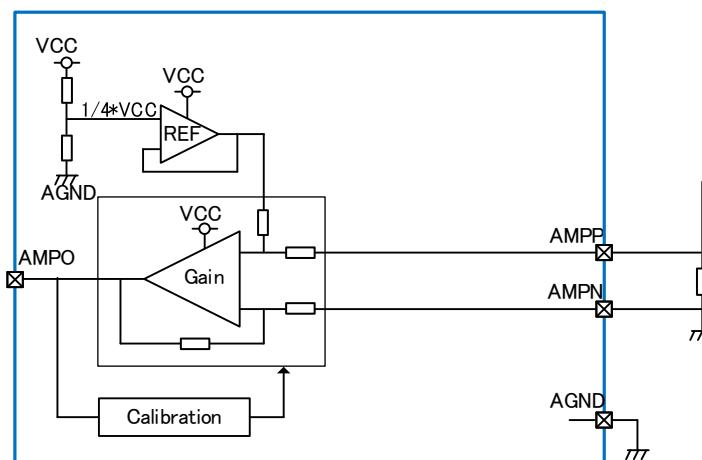

TB9104FTG はリファレンス電圧生成用アンプとモーター電流センス用アンプを内蔵しています。リファレンス電圧生成用アンプは、VCC 端子の電圧をもとにリファレンス電圧を生成します。モーター電流センス用アンプは、外部のモーター駆動部の GND 側に接続されているシャント抵抗を流れる電流により生じる差電圧を増幅します。この増幅電圧は、リファレンス電圧から VCC 方向に出力されます。なお、センス可能なモーター電流は電源から GND の方向だけです。ゲインは SPI 通信で設定可能です。増幅した電圧は、AMPO 端子から出力します。AMPO 端子には、ノイズ除去のためローパスフィルターを接続することをお勧めします。

モーターに電流が流れない状態で、キャリブレーションを実行し個体でのオフセットばらつきを補正することで、出力電圧の精度が向上します。なお、この精度向上が期待できる入力電圧の範囲は、通常時のシャント抵抗の電圧動作点を考慮したものです。入力端子に抵抗を接続する場合は、新たなゲイン誤差の要因になります。また、VCC 電源のノイズおよびシャント抵抗周辺のノイズに対し、規定の耐性を備えています。

図 7.16.1.1 電流センス回路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

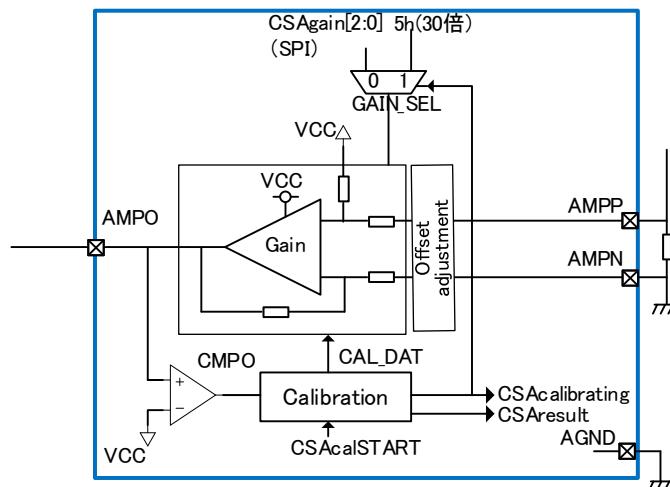

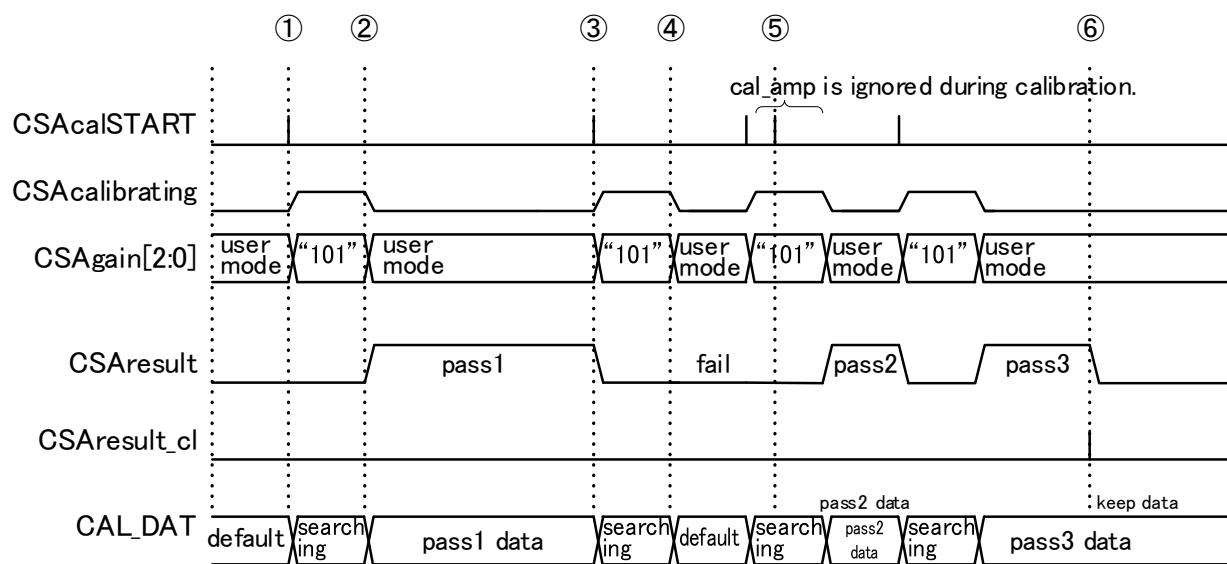

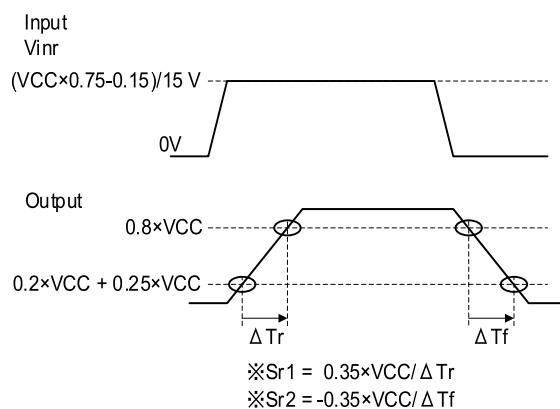

### 7.16.2. オフセットキャリブレーション

TB9104FTG の電流センス回路を使用する前にオフセットキャリブレーションを実施してください。なお、正しくキャリブレーションするため、オフセットキャリブレーションを実行するときは、AMPP 端子とAMPN 端子の間の、入力差電圧を 0[V]にしてください。なお、TB9104FTG は自動で AMPP 端子とAMPN 端子を接続する機能はありません。

キャリブレーションの実行は、SPI から CSACalSTART コマンドを"1"に設定することで始まります。CSACalSTART コマンドは自動的に"0"に戻ります。このとき CSACalibrating ステータスが"1"に、CSAresult ステータスは"0"になります。また、ゲインを 30 倍に固定します。キャリブレーション中はオフセット補正值 CAL\_DAT を変化させながらアンプ出力と VCC 端子の電圧の 8 分の 1 を比較することにより、最適な値を探査します。

キャリブレーションが完了すると CSACalibrating ステータスを 0 にし、キャリブレーション結果を CSAresult ステータスにセットします。CSAresult ステータスが"1"の場合、CAL\_DAT はそのまま保持し調整値として使用します。CSAresult ステータスが"0"の場合、CAL\_DAT は破棄し初期値に戻します。

CSAresult\_cl コマンドを"1"に設定すると CSAresult ステータスを任意のタイミングで"0"にすることができますが、CAL\_DAT は保持します。CSACalibrating ステータスが"1"の期間は、キャリブレーション中であるため、この期間に CSACalSTART コマンドを"1"に設定しても無効になります。

図 7.16.2.1 電流センスアンプ オフセットキャリブレーション回路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

図 7.16.2.2 電流センスアンプ オフセットキャリブレーション波形

注: TB9104FTG には AMPP, AMPN 両端子を自動的に AGND に接続する機能はありません。

## 7.17. 制御回路 Control Logic

### 7.17.1. ハーフブリッジモード

#### 7.17.1.1. 動作説明

TB9104FTG は、ハーフブリッジモード時、独立した 2 チャネルとして動作します。

第 1 のハーフブリッジ用ゲートドライバー GDCH1 は、IN11,IN12 端子の信号で制御されます。ハーフブリッジモードでは、外部ハイサイド n 型 MOSFET HS1 とローサイド n 型 MOSFET LS1 が同時にオンしないよう、IN11,IN12 端子による駆動指示が変更された際には、自動的に両 FET をオフにするデッドタイム  $T_{dead}(T_{dead0\sim7})$  が挿入されます。HS1 や LS1 が過電流になっていないことを確認するため、オンさせている FET はドレイン・ソース間電圧を監視マスク時間を除いて監視します。

第 2 のハーフブリッジ用ゲートドライバー GDCH2 は、IN21,IN22 端子の信号で制御されます。ハーフブリッジモードでは、外部ハイサイド n 型 MOSFET HS2 とローサイド n 型 MOSFET LS2 が同時にオンしないよう、IN21,IN22 端子による駆動指示が変更された際には、自動的に両 FET をオフにするデッドタイム  $T_{dead}(T_{dead0\sim7})$  が挿入されます。HS2 や LS2 が過電流になっていないことを確認するため、オンさせている FET はドレイン・ソース間電圧を監視マスク時間を除いて監視します。

未使用のチャネルは IN 端子を **Low** としてください。ゲートドライバーへオンの指示を出す前に、設定を済ませてください。オンしている間でも設定レジスターへライトすることができますが、その場合思わぬ動作となる可能性があります。

## 7.17.1.2. 真理値表

ハーフブリッジモードにおける動作状態を表 7.17.1.2.1、表 7.17.1.2.2 に示します。

- GH1,SH1 間が RL か Low だと、外部 n 型 MOSFET "HS1" はオフになり、High だとオンになります。

- GL1,SL 間が RL か Low だと、外部 n 型 MOSFET "LS1" はオフになり、High だとオンになります。

- GH2,SH2 間が RL か Low だと、外部 n 型 MOSFET "HS2" はオフになり、High だとオンになります。

- GL2,SL 間が RL か Low だと、外部 n 型 MOSFET "LS2" はオフになり、High だとオンになります。

表 7.17.1.2.1 第 1 のハーフブリッジ用ゲートドライバー GDCH1 真理値表

| IC 内部 | Inputs |        |      | Outputs |          | 説明                                |

|-------|--------|--------|------|---------|----------|-----------------------------------|

|       | 動作状態   | STBY_X | IN11 | IN12    | GH1- SH1 | GL1- SL                           |

| スタンバイ | Low    | X      | X    | RL      | RL       | TB9104FTG はスタンバイモーターの相入力は"High-Z" |

| リセット  | High   | X      | X    | RL      | RL       | TB9104FTG はリセットモーターの相入力は"High-Z"  |

| 通常動作  | High   | Low    | Low  | Low     | Low      | モーターの相入力は"High-Z"                 |

| 通常動作  | High   | High   | Low  | High    | Low      | モーターの相入力は"High"                   |

| 通常動作  | High   | Low    | High | Low     | High     | モーターの相入力は"Low"                    |

| 通常動作  | High   | High   | High | Low     | Low      | モーターの相入力は"High-Z"                 |

記号の説明 :

X = Do not care    RL = Resistive low    H = High    L = Low    High-Z = High-impedance

表 7.17.1.2.2 第 2 のハーフブリッジ用ゲートドライバー GDCH2 真理値表

| IC 内部 | Inputs |        |      | Outputs |          | 説明                                |

|-------|--------|--------|------|---------|----------|-----------------------------------|

|       | 動作状態   | STBY_X | IN21 | IN22    | GH2- SH2 | GL2- SL                           |

| スタンバイ | Low    | X      | X    | RL      | RL       | TB9104FTG はスタンバイモーターの相入力は"High-Z" |

| リセット  | High   | X      | X    | RL      | RL       | TB9104FTG はリセットモーターの相入力は"High-Z"  |

| 通常動作  | High   | Low    | Low  | Low     | Low      | モーターの相入力は"High-Z"                 |

| 通常動作  | High   | High   | Low  | High    | Low      | モーターの相入力は"High"                   |

| 通常動作  | High   | Low    | High | Low     | High     | モーターの相入力は"Low"                    |

| 通常動作  | High   | High   | High | High    | Low      | モーターの相入力は"High-Z"                 |

記号の説明 :

X = Do not care    RL = Resistive low    H = High    L = Low    High-Z = High-impedance

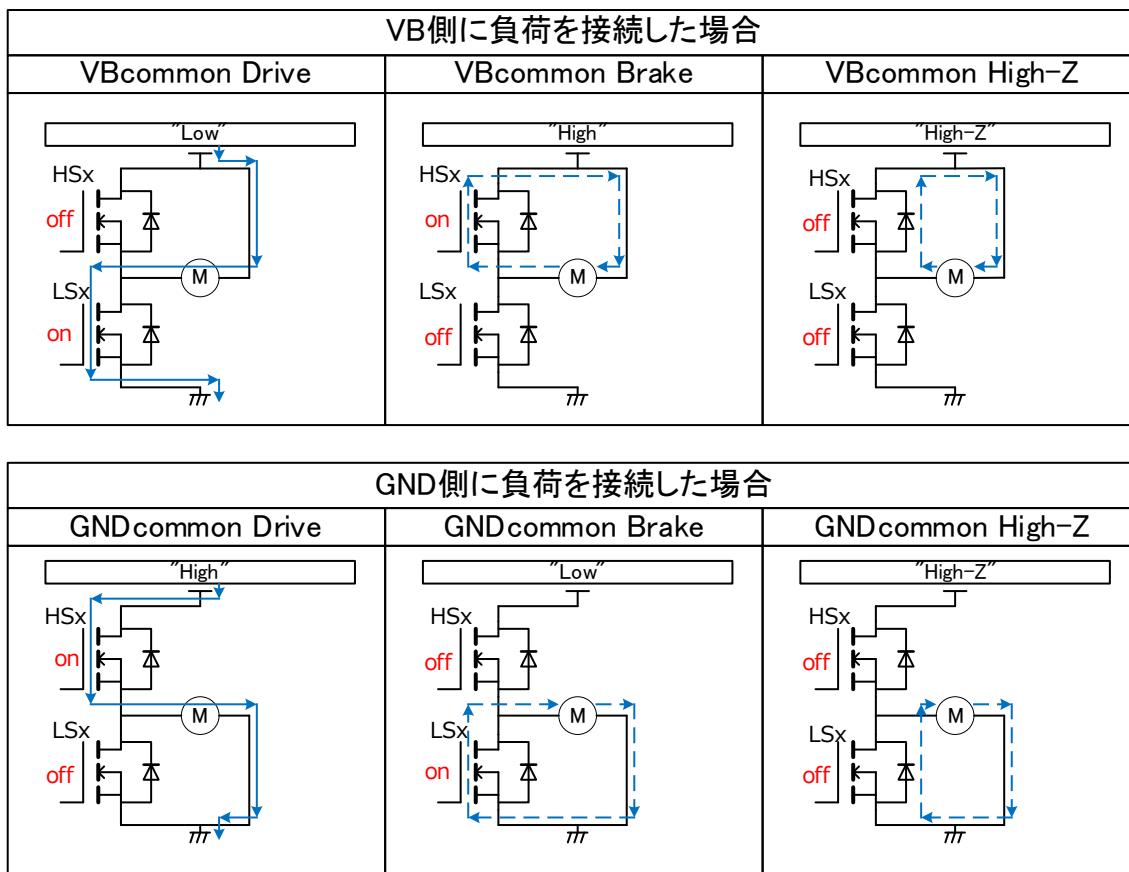

### 7.17.1.3. 電流経路

ハーフブリッジモード時、TB9104FTG で使用する外部 n 型 MOSFET の電流経路を図 7.17.1.3.1 に示します。実線は駆動時の電流経路を示します。点線は回生電流の経路を示します。

図 7.17.1.3.1 ハーフブリッジモードの電流経路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

## 7.17.1.4. 駆動制御フローチャート

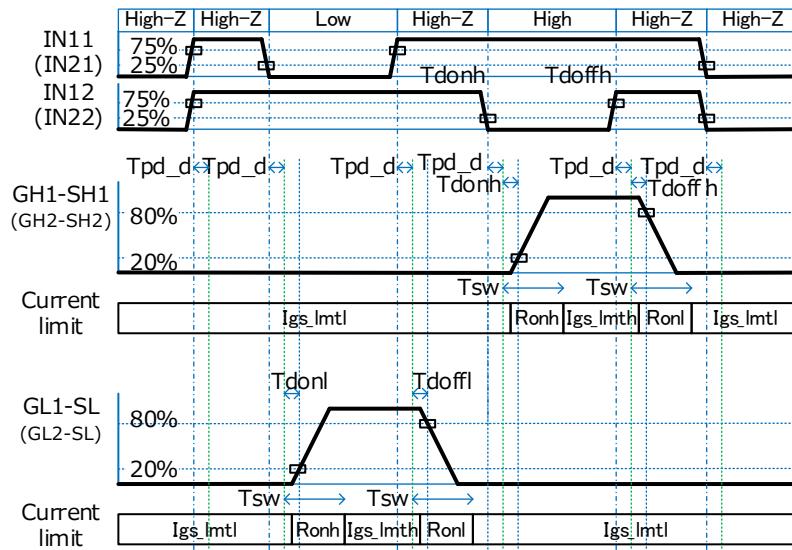

ハーフブリッジモードにおける駆動制御フローチャートを図 7.17.1.4.1 に示します。

また、図 7.17.1.4.1 に記載していない駆動制御の組み合わせを、図 7.17.1.4.2 に示します。

図 7.17.1.4.1 ハーフブリッジ フローチャート 1 (チャネルごと)

図 7.17.1.4.2 ハーフブリッジ フローチャート 2 その他の駆動制御組み合わせ

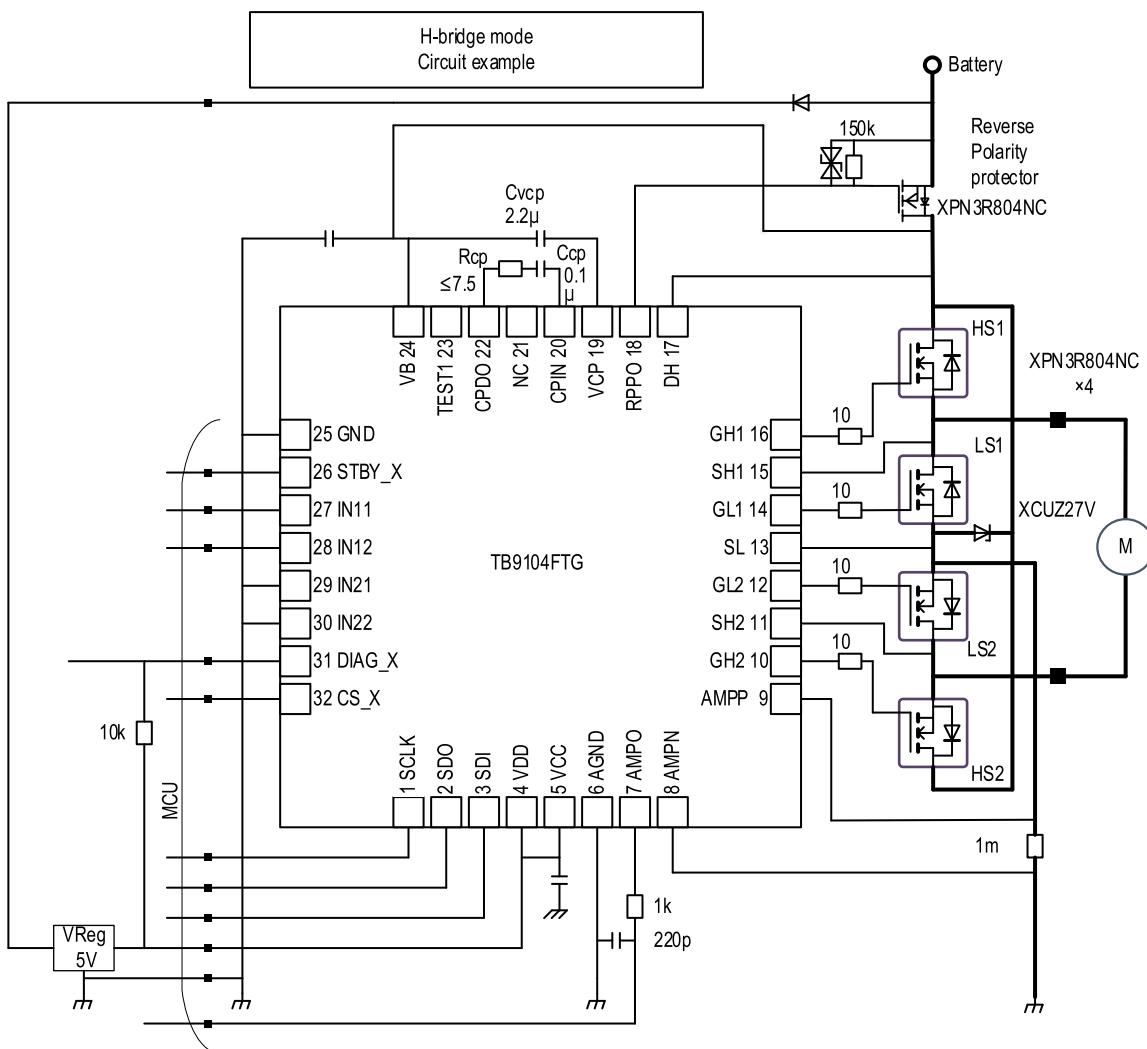

## 7.17.2. H ブリッジモード

### 7.17.2.1. 動作説明

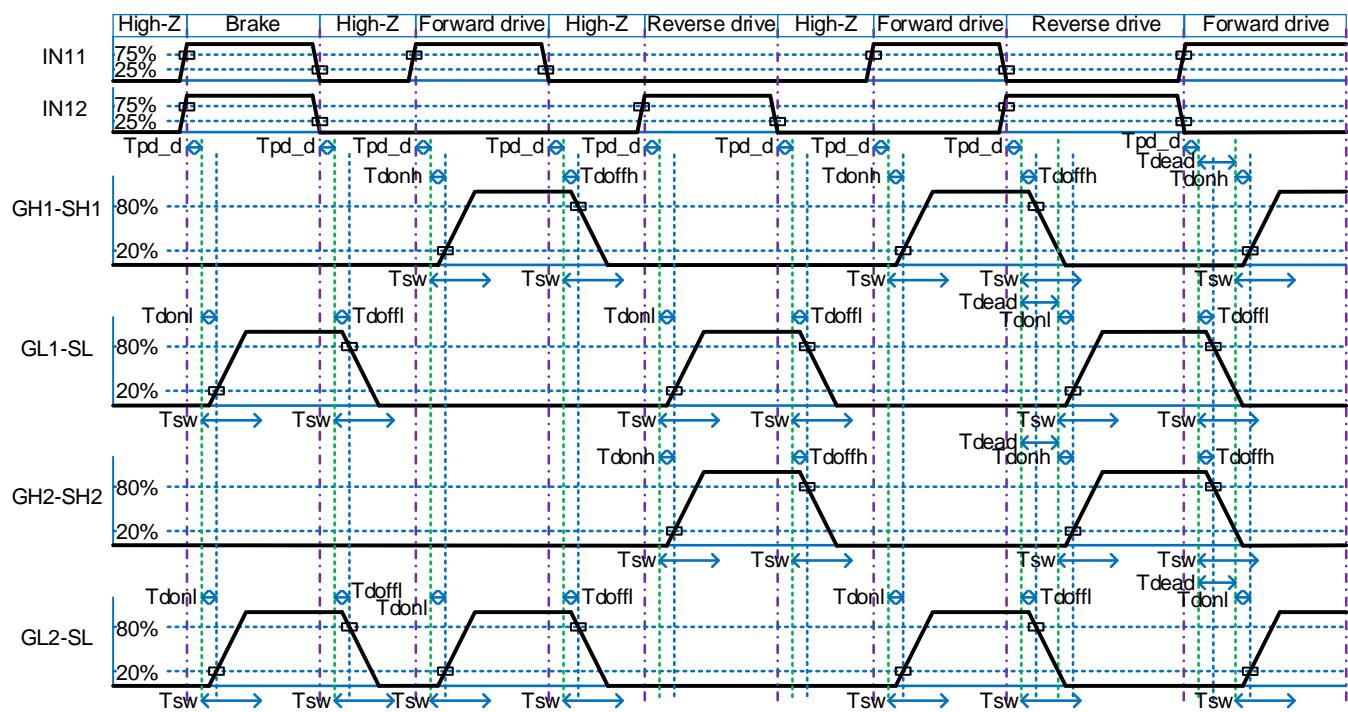

TB9104FTG は、H ブリッジモード時、1 チャネルの H ブリッジとして動作します。制御は、IN11,IN12 端子で行います。IN21,IN22 端子は、GND に接続するようにしてください。H ブリッジモードでは、HS1 と LS1、HS2 と LS2 がそれぞれ同時にオンして貫通電流が流れないよう、IN11,IN12 端子による駆動指示が変更された際には自動的にデッドタイムが挿入されます。

HS1 や LS1 が過電流になっていないことを確認するため、オンさせている FET はドレイン・ソース間電圧を監視マスク時間を除いて監視します。

ゲートドライバーへオンの指示を出す前に、設定を済ませてください。オンしている間でも設定レジスターへライトすることができますが、その場合思わぬ動作となる可能性があります。

### 7.17.2.2. 真理値表

H ブリッジモードにおける動作状態を表 7.17.2.2.1 に示します。GH1,SH1 間が RL か Low だと、外部 n 型 MOSFET "HS1" はオフになります。High だとオンになります。GL1,SL 間が RL か Low だと、外部 n 型 MOSFET "LS1" はオフになります。High だとオンになります。GH2,SH2 間が RL か Low だと、外部 n 型 MOSFET "HS2" はオフになります。High だとオンになります。GL2,SL 間が RL か Low だと、外部 n 型 MOSFET "LS2" はオフになります。High だとオンになります。

表 7.17.2.2.1 H ブリッジモード 真理値表

| IC 内部 | Inputs |      |      | Outputs   |          |           |          | 説明                                |

|-------|--------|------|------|-----------|----------|-----------|----------|-----------------------------------|

| 動作状態  | STBY_X | IN11 | IN12 | GH1 - SH1 | GL1 - SL | GH2 - SH2 | GL2 - SL |                                   |

| スタンバイ | Low    | X    | X    | RL        | RL       | RL        | RL       | TB9104FTG はスタンバイモーターの相入力は"High-Z" |

| リセット  | High   | X    | X    | RL        | RL       | RL        | RL       | TB9104FTG はリセットモーターの相入力は"High-Z"  |

| 通常動作  | High   | Low  | Low  | Low       | Low      | Low       | Low      | モーターの相入力は"High-Z"                 |

| 通常動作  | High   | High | Low  | High      | Low      | Low       | High     | モーターの相入力"Forward drive(SH1→SH2)"  |

| 通常動作  | High   | Low  | High | Low       | High     | High      | Low      | モーターの相入力"Reverse drive(SH2→SH1)"  |

| 通常動作  | High   | High | High | Low       | High     | Low       | High     | モーターの相入力は"Brake"                  |

記号の説明 :

X = Do not care    RL = Resistive low    H = High    L = Low    High-Z = High-impedance

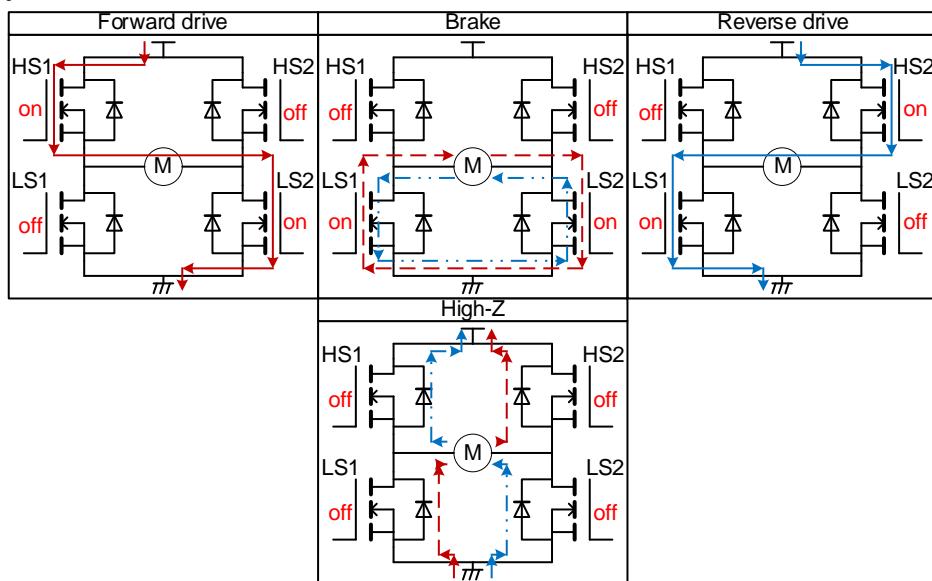

### 7.17.2.3. 電流経路

H ブリッジモード時、TB9104FTG で使用する外部 n 型 MOSFET の電流経路を図 7.17.2.3.1 に示します。赤色の実線は Forward drive 中の電流経路を示し、青色の実線は Reverse drive 中の電流経路を示します。また、点線は Forward drive 中の回生電流の経路を示し、2 点鎖線は Reverse drive 中の電流の経路を示します。

図 7.17.2.3.1 H ブリッジモードの電流経路

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

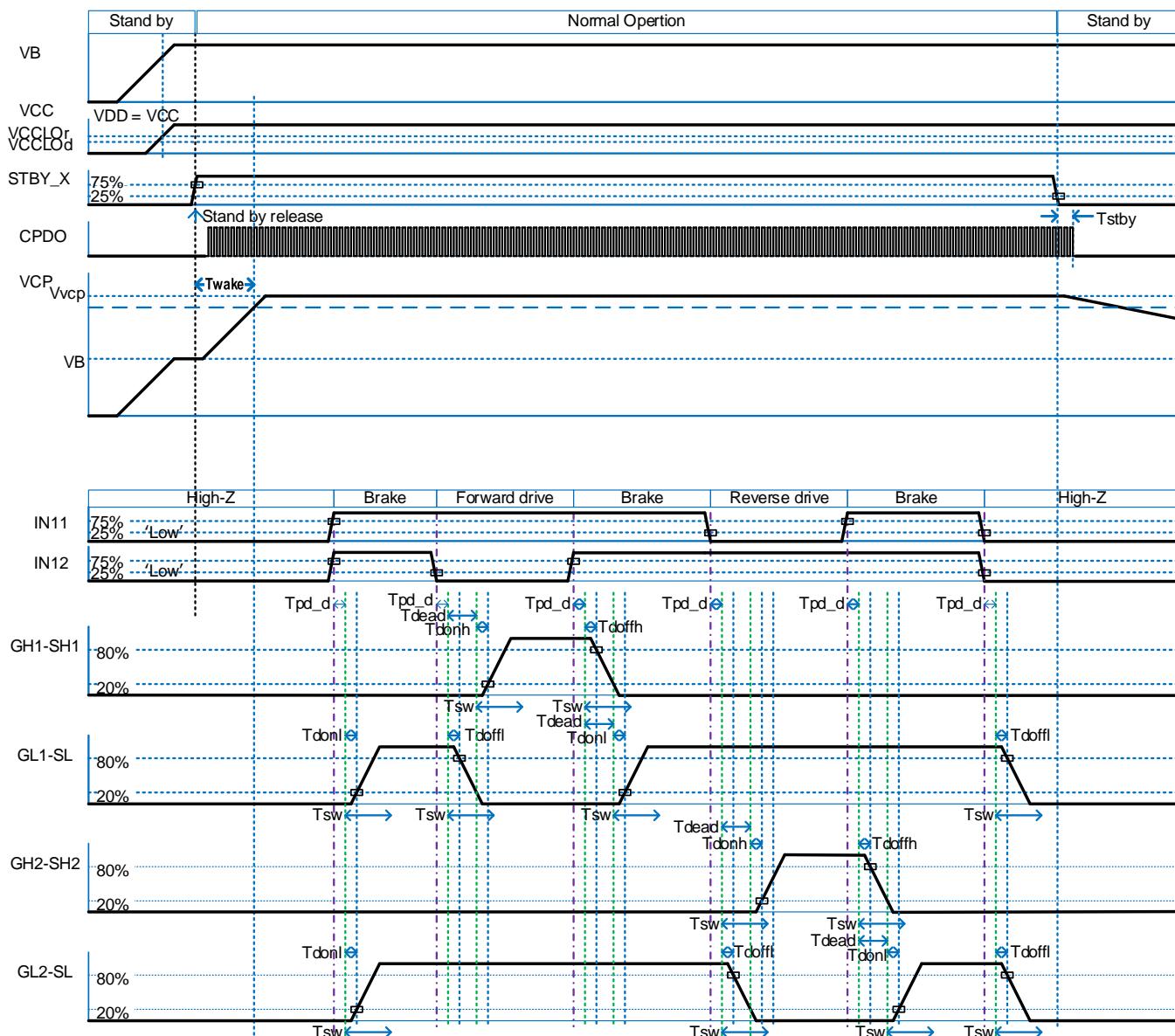

## 7.17.2.4. 駆動制御フローチャート

図 7.17.2.4.1 H ブリッジ フローチャート 1

図 7.17.2.4.2 H ブリッジ フローチャート 2

### 7.17.3. 異常処理

TB9104FTG は各種の異常検出機能を備えています。

異常を検出した際の処理方法として“検出しない”以外を選択すると、異常が発生したとき **DIAG\_X** 端子を **Low** にします。

**DIAG\_X** 端子が **Low** になるのは、異常検出フラグレジスターのうち、1つでも **1(High)** があったときです。

また、各異常検出時の動作設定コマンドに応じて、ゲートドライブ停止、チャージポンプ停止を処理します。

図 7.17.3.1 異常状態の処理と表示

注： 上図は IC について機能・動作などの説明をするため、省略や簡略化をしています。

## 7.18. SPI レジスターマップ

表 7.18.1 レジスターマップ

|               | Bit 15 | Bit 14      | Bit 13           | Bit 12      | Bit 11       | Bit 10              | Bit 9        | Bit 8           | Bit 7          | Bit 6    | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0  |

|---------------|--------|-------------|------------------|-------------|--------------|---------------------|--------------|-----------------|----------------|----------|-------|-------|----------|-------|-------|--------|

| Register name | A [3]  | A [2]       | A [1]            | A [0]       | R D + /W R-  | D[9]                | D[8]         | D[7]            | D[6]           | D[5]     | D[4]  | D[3]  | D[2]     | D [1] | D[0]  | Even P |

| FAULT STATUS  | 0000b  | Wr ite      | GetSt art        | VB_U V_cl   | 0            | VCP_O V_cl          | VCPVB _UV_cl | VCPRPP O_ODV_cl | SPle rrор_cl   | TJ_OT_cl | 0     | 0     |          |       |       | EP     |

|               |        | Re ad       | GetSt art        | VB_U V      | 0            | VCP_O V             | VCPVB _UV    | VCPRPP O_ODV    | SPle rrор      | TJ_OT    | 0     |       | WKUP_sts |       |       | EP     |

|               |        | Init Val ue | 0                | 0           | 0            | 0                   | 0            | 0               | 0              | 0        | 0     | 0     | 0        | 0     | 0     | EP     |

| FAULT VDS     | 0001b  | Wr ite      | VDS1 _OV_ cl     | 0           | VDS2 _OV_ cl | 0                   | 0            | 0               | 0              | 0        | 0     | 0     | 0        | 0     | 0     | EP     |

|               |        | Re ad       | VDSH S1_O V      | VDSL S1_O V | VDSH S2_O V  | VDSL S2_O V         | 0            | 0               | 0              | 0        | 0     | 0     | 0        | 0     | 0     | EP     |

|               |        | Init Val ue | 0                | 0           | 0            | 0                   | 0            | 0               | 0              | 0        | 0     | 0     | 0        | 0     | 0     | EP     |

| SET1          | 0010b  | Wr ite      | VB_UV_op[2:0]    |             |              | 0                   | 0            | 0               | 0              | 0        | 0     | 0     | 0        | 0     | 0     | EP     |

|               |        | Re ad       | VB_UV_op[2:0]    |             |              | 0                   | 0            | 0               | 0              | 0        | 0     | 0     | 0        | 0     | 0     | EP     |

|               |        | Init Val ue | 100b             |             |              | 0                   | 0            | 0               | 0              | 0        | 0     | 0     | 0        | 0     | 0     | EP     |

| SET2          | 0011b  | Wr ite      | VCPVB_UV_op[2:0] |             |              | VCPRPPO_ODV_op[2:0] |              |                 | TJ_OT_op[2:0]  |          |       | 0     |          |       |       | EP     |

|               |        | Re ad       | VCPVB_UV_op[2:0] |             |              | VCPRPPO_ODV_op[2:0] |              |                 | TJ_OT_op[2:0]  |          |       | 0     |          |       |       | EP     |

|               |        | Init Val ue | 010b             |             |              | 101b                |              |                 | 101b           |          |       | 0     |          |       |       | EP     |

| SET VDS1_1    | 0100b  | Wr ite      | VDS1H_OV_op[2:0] |             |              | VDS1L_OV_op[2:0]    |              |                 | tVDS1mask[2:0] |          |       | 0     |          |       |       | EP     |