# DCM340C01

Quad - channel High speed Logic for Automotive equipment, Default Low output

## 1. Description

The DCM340C01 is a 16-pin SOIC Wide package default low-output, quad-channel high-speed digital isolator with the primary and secondary sides insulated and coupled by a magnetic coupling structure.

With a high isolation voltage of  $5000\text{ V}_{\text{rms}}$ , it is suitable for control applications such as in-vehicle communication line insulation.

16pin SOIC Wide body

Weight: 0.426 g (typ.)

## 2. Applications

- Battery Control in Automotive Equipment

- Fuel Battery Control in Automotive Equipment

- Application for Electrical Vehicle

- Data Converter Isolation

(Serial Peripheral Interface (SPI), etc.)

## 3. Features

- Data rate : 50 Mbps (Max)

- Default Output : Low

- Number of channels : 4 channels (Forward 4: Revers 0)

- Suitable operating voltage : 3.3 V or 5 V

- Isolation voltage :  $5000\text{ V}_{\text{rms}}$

- Common-Mode Transient Immunity :  $\pm100\text{ kV}/\mu\text{s}$  (Typ)

- Safety standards

- AEC-Q100 (Grade1 qualified)

- UL : UL1577 , File No. E519997

- cUL: CSA Component Acceptance Service Notice No. E519997

Note: Typical test conditions:  $\text{V}_{\text{DD1}} = \text{V}_{\text{DD2}} = 3.3\text{V}$  or  $5\text{V}$ ,  $\text{T}_a = 25^\circ\text{C}$ ; unless otherwise specified.

## 4. Mechanical Parameters

Table 4.1 Mechanical parameters

| Characteristics                 | Symbol | unit      | Unit          |

|---------------------------------|--------|-----------|---------------|

| Creepage distances              | CPG    | 7.6 (Min) | mm            |

| Clearance distances             | CLR    | 7.6 (Min) | mm            |

| Distance Through the Insulation | DTI    | 17        | $\mu\text{m}$ |

Start of commercial production

2024-12

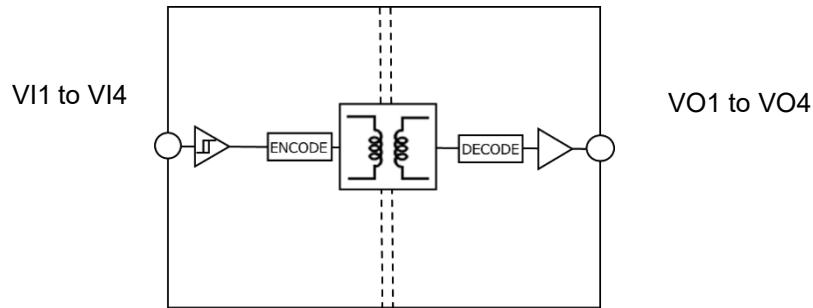

## 5. Block Diagram

DCM340C01

Note: Some of the functional blocks, circuits or constants labels in the block diagram may have been omitted or simplified for clarity.

**Figure 5.1 Block Diagram**

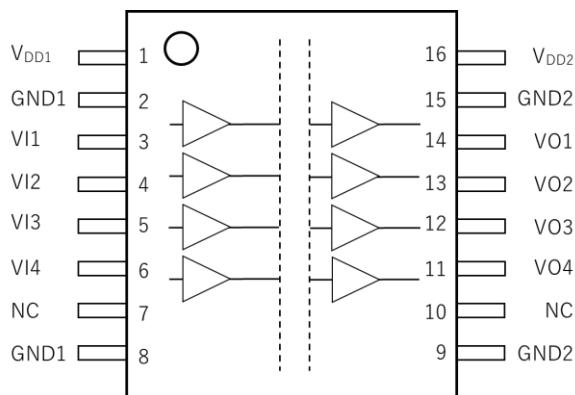

## 6. Pin Assignments

**Figure 6.1 Pin Assignments (top view)**

## 7. Pin Description

**Table 7.1 Pin Description**

| Pin No | Pin name         | I/O | Description                      |

|--------|------------------|-----|----------------------------------|

| 1      | V <sub>DD1</sub> | —   | Power Supply, side 1             |

| 2      | GND1             | —   | GND connection for VDD1 , side 1 |

| 3      | VI1              | IN  | Logic Input, Channel 1           |

| 4      | VI2              | IN  | Logic Input, Channel 2           |

| 5      | VI3              | IN  | Logic Input, Channel 3           |

| 6      | VI4              | IN  | Logic Input, Channel 4           |

| 7      | NC               | NC  | Non – Connection (Note1)         |

| 8      | GND1             | —   | GND connection for VDD1, side 1  |

| 9      | GND2             | —   | GND connection for VDD2, side 2  |

| 10     | NC               | NC  | Non – Connection (Note1)         |

| 11     | VO4              | OUT | Logic Output, Channel 4          |

| 12     | VO3              | OUT | Logic Output, Channel 3          |

| 13     | VO2              | OUT | Logic Output, Channel 2          |

| 14     | VO1              | OUT | Logic Output, Channel 1          |

| 15     | GND2             | —   | GND connection for VDD2, side 2  |

| 16     | V <sub>DD2</sub> | —   | Power Supply, side 2             |

Note 1: Ensure that NC pins are either connected to GND or left unconnected (open).

## 8. Functional Description

### 8.1. Specifications of External Components

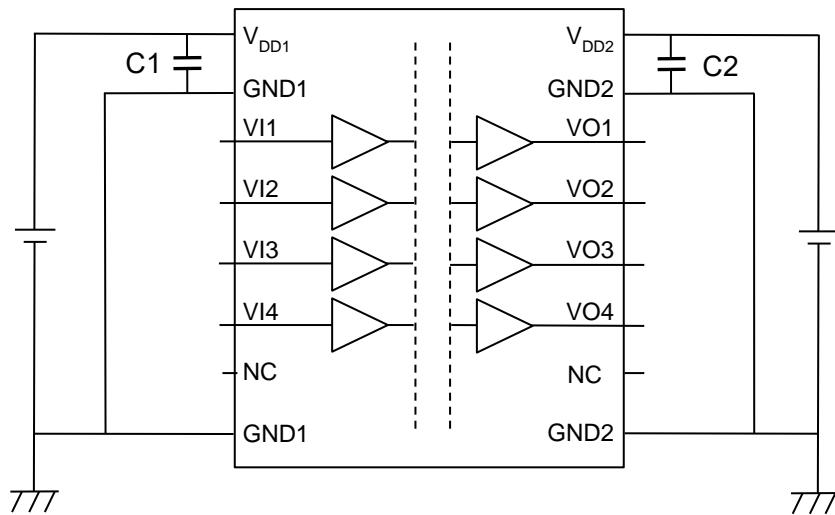

Figure 8.1 Pin Assignments (top view)

Table 8.1 External component specification (Note)

| Component Name | Recommended Value | Pin              | Description |

|----------------|-------------------|------------------|-------------|

| C1             | 0.1 $\mu$ F       | V <sub>DD1</sub> | —           |

| C2             | 0.1 $\mu$ F       | V <sub>DD2</sub> | —           |

Note: Use Ceramic capacitors (C1,C2) with good high frequency characteristics.

Note: Ceramic capacitors (C1,C2) should be connected between pin 1 (V<sub>DD1</sub>) and pin 2 (GND1) for V<sub>DD1</sub> and between pin 16 (V<sub>DD2</sub>) and pin 15 (GND2) for V<sub>DD2</sub>, and should be the layout on the IC as close as possible (less than 10mm). Otherwise, the IC may not switch properly.

## 8.2. Function Description

### 8.2.1. Truth table for each pin

**Table 8.2 Truth table for each pin (Note)**

|   | $V_{DDI}$<br>Input side<br>$V_{DD}$ | $V_{DDO}$<br>Output side<br>$V_{DD}$ | Input<br>(VI1 to VI4) | Output<br>(VO1 to VO4) | State Description                                              |

|---|-------------------------------------|--------------------------------------|-----------------------|------------------------|----------------------------------------------------------------|

| 1 | PU                                  | PU                                   | Low                   | Low                    | Normal Operation                                               |

| 2 |                                     |                                      | High                  | High                   |                                                                |

| 3 |                                     |                                      | OPEN                  | Low                    |                                                                |

| 4 | PU                                  | PD                                   | Undetermined          | Undetermined           | When $V_{DDO}$ is unpowered, a channel output is undetermined. |

| 5 | PD                                  | PU                                   | Undetermined          | Low                    | Default mode                                                   |

| 6 | PD                                  | PD                                   | Undetermined          | Undetermined           | When $V_{DDO}$ is unpowered, a channel output is undetermined. |

Note: PU = Powered Up ( $V_{DD} \geq 2.25$  V) , PD = Powered Down ( $V_{DD} \leq 1.7$  V)

H = High Level , L = Low Level

Note:  $V_{DDI}$  = Input-side  $V_{DD}$ ,  $V_{DDO}$  = Output-side  $V_{DD}$

## 9. Absolute Maximum Ratings (Note)

**Table 9.1 Absolute Maximum Ratings (Note)**

( $T_a = 25^\circ\text{C}$  unless otherwise specified)

| Characteristics                    | Condition                                                                                               | Symbol                           | Rating                                     | Unit             |

|------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------|------------------|

| <b>Junction temperature</b>        | —                                                                                                       | $T_J$                            | -40 to 150                                 | $^\circ\text{C}$ |

| <b>Storage temperature range</b>   | —                                                                                                       | $T_{\text{stg}}$                 | -65 to 150                                 | $^\circ\text{C}$ |

| <b>Operation temperature range</b> | —                                                                                                       | $T_{\text{opr}}$                 | -40 to 125                                 | $^\circ\text{C}$ |

| <b>Soldering temperature</b>       | 10 s                                                                                                    | $T_{\text{sol}}$                 | 260                                        | $^\circ\text{C}$ |

| <b>Supply voltage (DC)</b>         | —                                                                                                       | $V_{\text{DD1}}, V_{\text{DD2}}$ | -0.5 to 6.0                                | V                |

|                                    |                                                                                                         | $V_{\text{I}}(1 \text{ to } 4)$  | -0.5 to $V_{\text{DD1}} + 0.5$<br>(Note 1) | V                |

|                                    |                                                                                                         | $V_{\text{O}}(1 \text{ to } 4)$  | 0.5 to $V_{\text{DDO}} + 0.5$<br>(Note 1)  | V                |

| <b>Output Current</b>              | —                                                                                                       | $I_{\text{O}}$                   | $\pm 15$                                   | mA               |

| <b>Isolation voltage</b>           | 1 min                                                                                                   | $B_{\text{Vs}}$                  | 5000                                       | V <sub>rms</sub> |

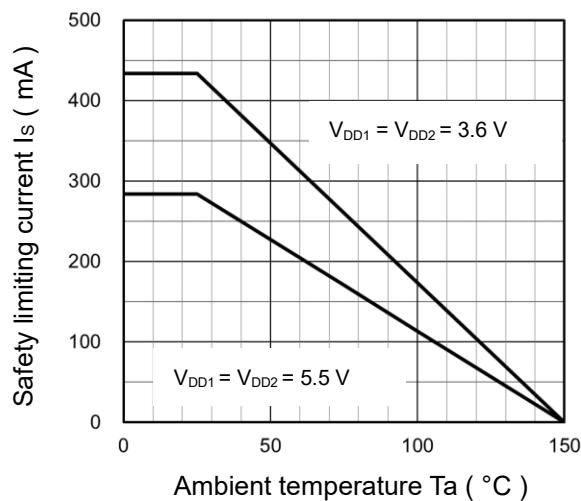

| <b>Output current</b>              | $V_{\text{DD1}} = V_{\text{DD2}} = 5.5 \text{ V},$<br>$T_J = 150^\circ\text{C}, T_a = 25^\circ\text{C}$ | $I_{\text{S1}}$                  | 284                                        | mA               |

|                                    | $V_{\text{DD1}} = V_{\text{DD2}} = 3.6 \text{ V},$<br>$T_J = 150^\circ\text{C}, T_a = 25^\circ\text{C}$ | $I_{\text{S2}}$                  | 434                                        | mA               |

| <b>Power dissipation</b>           | $T_J = 150^\circ\text{C}, T_a = 25^\circ\text{C}$                                                       | $P_{\text{d Max}}$               | 1562                                       | mW               |

**Note:** The absolute maximum ratings of a semiconductor device are a set of specified parameter values, which must not be exceeded during operation, even for an instant.

If any of these rating would be exceeded during operation, the device electrical characteristics may be irreparably altered, and the reliability and lifetime of the device can no longer be guaranteed. Moreover, these operations with exceeded ratings may cause break down, damage, and/or degradation to any other equipment. Applications using the device should be designed such that each maximum rating will never be exceeded in any operating conditions.

Before using, creating, and/or producing designs, refer to and comply with the precautions and conditions set forth in this document.

**Note 1:** Maximum voltage must not exceed 6V.

## 9.1. Power Dissipation

Figure 9.1 Thermal derating curve for safety limiting current

## 10. Recommended operating conditions

Table 10.1 Recommended Operating Ranges (Note)

| Characteristics       | Symbol             | Min | Max | Unit |

|-----------------------|--------------------|-----|-----|------|

| Operation voltage     | $V_{DD1}, V_{DD2}$ | 3.0 | 5.5 | V    |

| Junction temperature  | $T_J$              | -40 | 150 | °C   |

| Operating temperature | $T_{opr}$          | -40 | 125 | °C   |

Note: The recommended operating conditions are given as a design guide necessary to obtain the intended performance of the device. Each parameter is an independent value. When creating a system design using this device, the electrical characteristics specified in this data sheet should also be considered.

## 11. Electrical Characteristics

### 11.1 DC characteristics – 5V Supply

**Table 11.1 DC characteristics – 5V Supply (Note)**

( $V_{DD1} = V_{DD2} = 4.5$  V to 5.5 V over recommended operating conditions unless otherwise noted)

| Characteristics                                  | Symbol       | Test condition                                  | Min                  | Typ             | Max                  | Unit     |

|--------------------------------------------------|--------------|-------------------------------------------------|----------------------|-----------------|----------------------|----------|

| $V_{DD}$ Under Voltage Lockout threshold Voltage | $V_{DDxUV+}$ | Positive $V_{DDx}$ Threshold                    | —                    | 2.1             | 2.25                 | V        |

|                                                  | $V_{DDxUV-}$ | Negative $V_{DDx}$ Threshold                    | 1.7                  | 1.9             | —                    |          |

|                                                  | $V_{DDxUVH}$ | $V_{DDx}$ Hysteresis                            | 0.1                  | 0.2             | —                    |          |

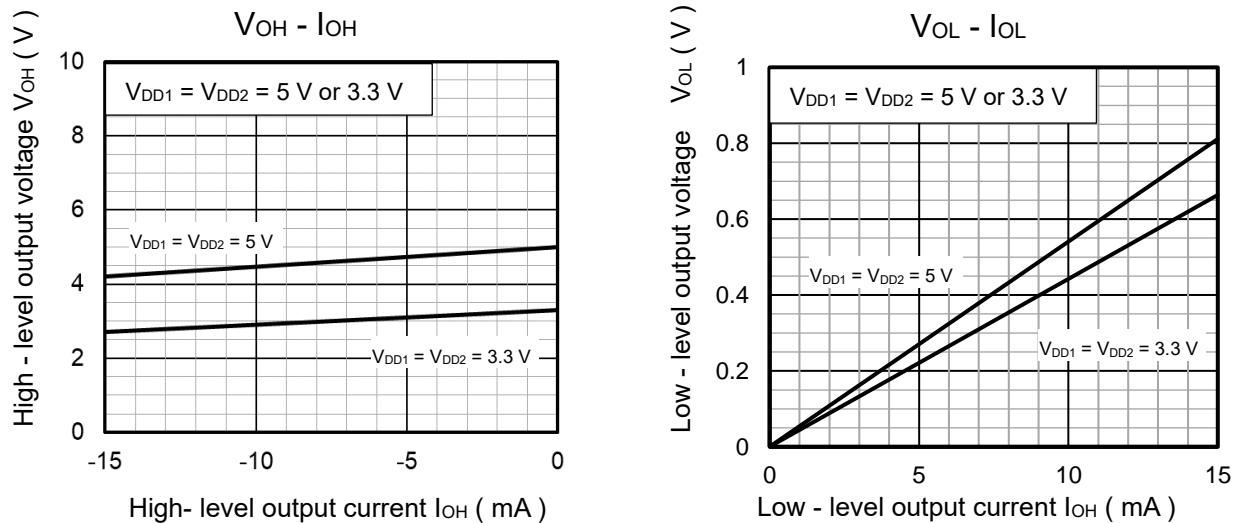

| Logic High-level output voltage                  | $V_{OH}$     | $V_{IX} = \text{High}$ , $I_{OH} = -20$ $\mu$ A | $V_{DDO} - 0.1$      | $V_{DDO}$       | —                    | V        |

|                                                  |              | $V_{IX} = \text{High}$ , $I_{OH} = -4$ mA       | $V_{DDO} - 0.4$      | $V_{DDO} - 0.2$ | —                    |          |

| Logic Low-level output voltage                   | $V_{OL}$     | $V_{IX} = \text{Low}$ , $I_{OL} = 20$ $\mu$ A   | —                    | 0               | 0.1                  | V        |

|                                                  |              | $V_{IX} = \text{Low}$ , $I_{OL} = 4$ mA         | —                    | 0.2             | 0.4                  |          |

| Output Impedance                                 | $Z_O$        | —                                               | —                    | 50              | —                    | $\Omega$ |

| Logic High-level input Threshold voltage         | $V_{IH}$     | —                                               | $0.7 \times V_{DDI}$ | —               | —                    | V        |

| Logic Low-level input Threshold voltage          | $V_{IL}$     | —                                               | —                    | —               | $0.3 \times V_{DDI}$ | V        |

| Logic Input threshold voltage hysteresis         | $V_{HYS}$    | —                                               | —                    | 0.37            | —                    | V        |

| Input current                                    | $I_I$        | $V_I = V_{DDI}$ or 0 V                          | —                    | —               | $\pm 10$             | $\mu$ A  |

Note:  $V_{DDI}$  = Input-side  $V_{DD}$ ,  $V_{DDO}$  = Output-side  $V_{DD}$

## 11.2 Switching Characteristics – 5 V Supply

**Table 11.2 Switching Characteristics – 5 V Supply**

( $V_{DD1} = V_{DD2} = 4.5$  V to 5.5 V over recommended operating conditions unless otherwise noted)

| Characteristics                                       | Symbol               | Test condition                            | Min | Typ  | Max  | Unit  |

|-------------------------------------------------------|----------------------|-------------------------------------------|-----|------|------|-------|

| <b>Data Rate</b>                                      | $t_{bps}$            | —                                         | DC  | —    | 50   | Mbps  |

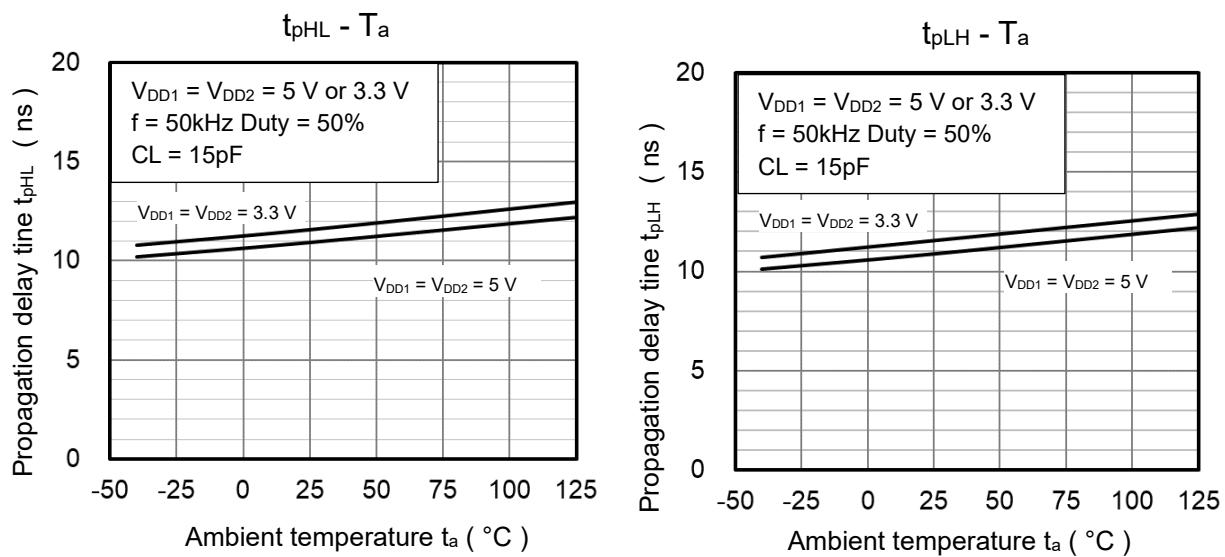

| <b>Propagation Delay</b>                              | $t_{PHL}, t_{PLH}$   | 50 kHz, Duty = 50 %, $C_L = 15$ pF        | —   | 10.9 | 18.4 | ns    |

| <b>Pulse Width Distortion</b>                         | PWD                  | $ t_{PHL} - t_{PLH} $                     | —   | 0.8  | 5.1  | ns    |

| <b>Propagation Delay Skew (Between any two units)</b> | $t_{PSK}$            | (Note1)                                   | —   | —    | 13.0 | ns    |

| <b>Channel Matching</b>                               | <b>Codirectional</b> | $t_{skCD}$                                | —   | —    | 4.4  | ns    |

| <b>Output signal rise time</b>                        | $t_r$                | 10 % to 90 %                              | —   | 0.9  | —    | ns    |

| <b>Output signal fall time</b>                        | $t_f$                | 90 % to 10 %                              | —   | 0.9  | —    | ns    |

| <b>Common-Mode Transient Immunity</b>                 | CMTI                 | $V_I = V_{DD1}$ or 0 V, $V_{CM} = 1500$ V | —   | 100  | —    | kV/μs |

Note1: The Propagation delay skew,  $t_{PSK}$ , is equal to the magnitude of the difference in propagation delay.

That will be seen between units at the same given conditions (supply voltage, input current, temperature, etc.).

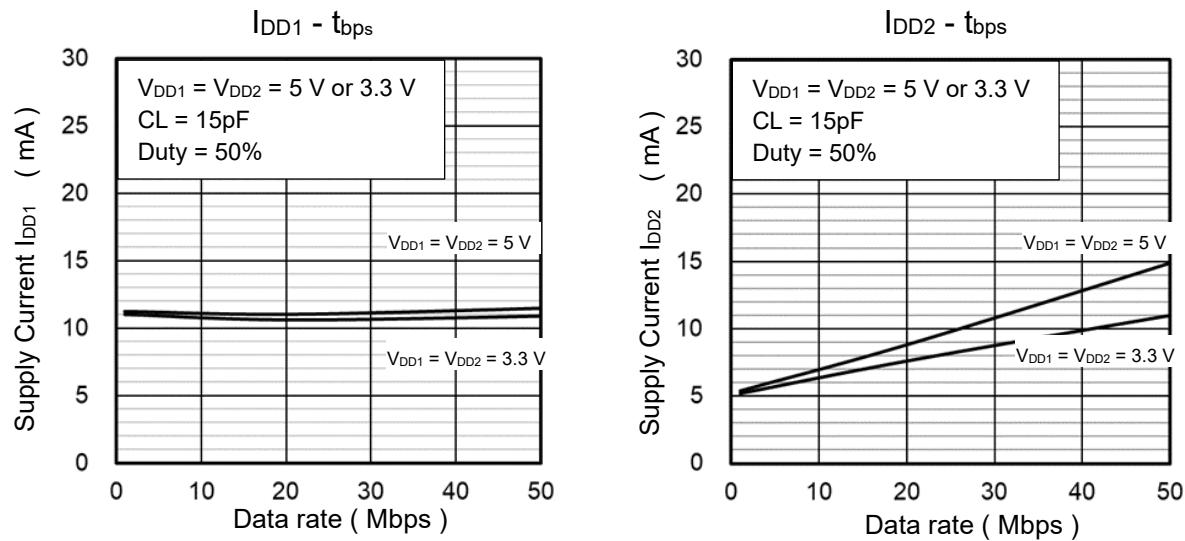

## 11.3 Supply Current Characteristics – 5 V Supply

**Table 11.3 Supply Current Characteristics – 5 V Supply**

( $V_{DD1} = V_{DD2} = 4.5$  V to 5.5 V over recommended operating conditions unless otherwise noted)

| Characteristics                   | Symbol              | Test condition                | Min                                                          | Typ | Max  | Unit |

|-----------------------------------|---------------------|-------------------------------|--------------------------------------------------------------|-----|------|------|

| <b>DC Supply Current</b>          | Primary side        | $I_{DDQ1(0)5}$                | $V_I = \text{Low}$                                           | —   | 2.1  | 3.0  |

|                                   |                     | $I_{DDQ1(1)5}$                | $V_I = \text{High}$                                          | —   | 19.6 | 28.1 |

|                                   | Secondary side      | $I_{DDQ2(0)5}$                | $V_I = \text{Low}$                                           | —   | 5.0  | 7.3  |

|                                   |                     | $I_{DDQ2(1)5}$                | $V_I = \text{High}$                                          | —   | 5.3  | 7.6  |

| <b>Supply Current (AC signal)</b> | $t_{bps} = 1$ Mbps  | Primary side $I_{DD1(1)5}$    | $f_{CLK} = 500$ kHz, Duty = 50 % square wave, $C_L = 15$ pF  | —   | 11.2 | 17.5 |

|                                   |                     | Secondary side $I_{DD2(1)5}$  |                                                              | —   | 5.4  | 8.3  |

|                                   | $t_{bps} = 25$ Mbps | Primary side $I_{DD1(25)5}$   | $f_{CLK} = 12.5$ MHz, Duty = 50 % square wave, $C_L = 15$ pF | —   | 11.0 | 17.1 |

|                                   |                     | Secondary side $I_{DD2(25)5}$ |                                                              | —   | 9.8  | 14.7 |

|                                   | $t_{bps} = 50$ Mbps | Primary side $I_{DD1(50)5}$   | $f_{CLK} = 25$ MHz, Duty = 50 % square wave, $C_L = 15$ pF   | —   | 11.5 | 17.5 |

|                                   |                     | Secondary side $I_{DD2(50)5}$ |                                                              | —   | 14.9 | 22.2 |

## 11.4 DC characteristics – 3.3 V Supply

Table 11.4 DC characteristics – 3.3V Supply (Note)

(V<sub>DD1</sub> = V<sub>DD2</sub> = 3.0 V to 3.6 V over recommended operating conditions unless otherwise noted)

| Characteristics                                         | Symbol              | Test condition                                          | Min                    | Typ                    | Max                    | Unit     |

|---------------------------------------------------------|---------------------|---------------------------------------------------------|------------------------|------------------------|------------------------|----------|

| V <sub>DD</sub> Under Voltage Lockout threshold Voltage | VDD <sub>xUV+</sub> | Positive VDD <sub>x</sub> Threshold                     | —                      | 2.1                    | 2.25                   | V        |

|                                                         | VDD <sub>xUV-</sub> | Negative VDD <sub>x</sub> Threshold                     | 1.7                    | 1.9                    | —                      |          |

|                                                         | VDD <sub>xUVH</sub> | VDD <sub>x</sub> Hysteresis                             | 0.1                    | 0.2                    | —                      |          |

| Logic High-level output voltage                         | V <sub>OH</sub>     | V <sub>I</sub> X = High , I <sub>OH</sub> = -20 $\mu$ A | V <sub>DDO</sub> - 0.1 | V <sub>DDO</sub>       | —                      | V        |

|                                                         |                     | V <sub>I</sub> X = High , I <sub>OH</sub> = -4 mA       | V <sub>DDO</sub> - 0.4 | V <sub>DDO</sub> - 0.2 | —                      |          |

| Logic Low-level output voltage                          | V <sub>OL</sub>     | V <sub>I</sub> X = Low , I <sub>OL</sub> = 20 $\mu$ A   | —                      | 0                      | 0.1                    | V        |

|                                                         |                     | V <sub>I</sub> X = Low , I <sub>OL</sub> = 4 mA         | —                      | 0.2                    | 0.4                    |          |

| Output Impedance                                        | Z <sub>O</sub>      | —                                                       | —                      | 50                     | —                      | $\Omega$ |

| Logic High-level input Threshold voltage                | V <sub>IH</sub>     | —                                                       | 0.7 x V <sub>DDI</sub> | —                      | —                      | V        |

| Logic Low-level input Threshold voltage                 | V <sub>IL</sub>     | —                                                       | —                      | —                      | 0.3 x V <sub>DDI</sub> | V        |

| Logic Input threshold voltage hysteresis                | V <sub>HYS</sub>    | —                                                       | —                      | 0.32                   | —                      | V        |

| Input current                                           | I <sub>I</sub>      | V <sub>I</sub> = V <sub>DDI</sub> or 0 V                | —                      | —                      | $\pm$ 10               | $\mu$ A  |

Note: V<sub>DDI</sub> = Input-side V<sub>DD</sub>, V<sub>DDO</sub> = Output-side V<sub>DD</sub>

## 11.5 Switching Characteristics – 3.3 V Supply

**Table 11.5 Switching Characteristics – 3.3 V Supply**

( $V_{DD1} = V_{DD2} = 3.0$  V to 3.6 V over recommended operating conditions unless otherwise noted)

| Characteristics                                           | Symbol               | Test condition                            | Min | Typ  | Max  | Unit  |

|-----------------------------------------------------------|----------------------|-------------------------------------------|-----|------|------|-------|

| <b>Data Rate</b>                                          | $t_{bps}$            | —                                         | DC  | —    | 50   | Mbps  |

| <b>Propagation Delay</b>                                  | $t_{PHL}, t_{PLH}$   | 50 kHz, Duty = 50 %,<br>$C_L = 15$ pF     | —   | 11.6 | 19.2 | ns    |

| <b>Pulse Width Distortion</b>                             | PWD                  | $ t_{PHL} - t_{PLH} $                     | —   | 0.8  | 5.1  | ns    |

| <b>Propagation Delay Skew<br/>(Between any two units)</b> | $t_{PSK}$            | (Note1)                                   | —   | —    | 13.0 | ns    |

| <b>Channel Matching</b>                                   | <b>Codirectional</b> | $t_{skCD}$                                | —   | —    | 4.4  | ns    |

| <b>Output signal rise time</b>                            | $t_r$                | 10 % to 90 %                              | —   | 0.9  | —    | ns    |

| <b>Output signal fall time</b>                            | $t_f$                | 90 % to 10 %                              | —   | 0.9  | —    | ns    |

| <b>Common-Mode Transient Immunity</b>                     | CMTI                 | $V_I = V_{DD1}$ or 0 V, $V_{CM} = 1500$ V | —   | 100  | —    | kV/μs |

Note1: The Propagation delay skew,  $t_{PSK}$ , is equal to the magnitude of the difference in propagation delay.

That will be seen between units at the same given conditions (supply voltage, input current, temperature, etc.).

## 11.6 Supply Current Characteristics – 3.3 V Supply

**Table 11.6 Supply Current Characteristics – 3.3 V Supply**

( $V_{DD1} = V_{DD2} = 3.0$  V to 3.6 V over recommended operating conditions unless otherwise noted)

| Characteristics                       |                     | Symbol         | Test condition      | Min                                                             | Typ  | Max  | Unit |    |

|---------------------------------------|---------------------|----------------|---------------------|-----------------------------------------------------------------|------|------|------|----|

| <b>DC Supply Current</b>              | Primary side        | $I_{DDQ1(0)3}$ | $V_I = \text{Low}$  | —                                                               | 2.0  | 2.9  | mA   |    |

|                                       |                     | $I_{DDQ1(1)3}$ | $V_I = \text{High}$ | —                                                               | 19.4 | 27.7 |      |    |

|                                       | Secondary side      | $I_{DDQ2(0)3}$ | $V_I = \text{Low}$  | —                                                               | 4.9  | 7.1  | mA   |    |

|                                       |                     | $I_{DDQ2(1)3}$ | $V_I = \text{High}$ | —                                                               | 5.2  | 7.4  |      |    |

| <b>Supply Current<br/>(AC signal)</b> | $t_{bps} = 1$ Mbps  | Primary side   | $I_{DD1(1)3}$       | $f_{CLK} = 500$ kHz, Duty = 50 %<br>square wave, $C_L = 15$ pF  | —    | 11.0 | 16.7 | mA |

|                                       |                     | Secondary side | $I_{DD2(1)3}$       |                                                                 | —    | 5.2  | 7.8  |    |

|                                       | $t_{bps} = 25$ Mbps | Primary side   | $I_{DD1(25)3}$      | $f_{CLK} = 12.5$ MHz, Duty = 50 %<br>square wave, $C_L = 15$ pF | —    | 10.6 | 16.0 | mA |

|                                       |                     | Secondary side | $I_{DD2(25)3}$      |                                                                 | —    | 8.2  | 12.4 |    |

|                                       | $t_{bps} = 50$ Mbps | Primary side   | $I_{DD1(50)3}$      | $f_{CLK} = 25$ MHz, Duty = 50 %<br>square wave, $C_L = 15$ pF   | —    | 10.9 | 16.2 | mA |

|                                       |                     | Secondary side | $I_{DD2(50)3}$      |                                                                 | —    | 11.0 | 18.0 |    |

## 12. Characteristic Chart (Note)

### 12.1 Supply Current vs Data rate

Figure12.1 Supply Current – Data rate

### 12.2 Output Voltage vs Output Current

Figure12.2 Output Voltage – Output Current

Note: The following characteristics curves are presented for reference only and not guaranteed by production test, unless otherwise noted.

## 12.3 Propagation Delay Time vs Ambient Temperature

Figure12.3 Propagation Delay Time vs Ambient Temperature

Figure12.4 Switching Waveforms

Note: The following characteristics curves are presented for reference only and not guaranteed by production test, unless otherwise noted.

## 13. Package Information

**Table 13.1 Insulation Related Specifications (Note)**

| Parameters                   | Symbol | DCM340C01 | Unit |

|------------------------------|--------|-----------|------|

| Minimum clearance            | CLR    | 7.6       | mm   |

| Minimum creepage distance    | CPG    | 7.6       | mm   |

| Minimum insulation thickness | DTI    | 17        | μm   |

| Comparative tracking index   | CTI    | 550       | V    |

Note: If a printed circuit is incorporated, the creepage distance and clearance may be reduced below this value. (e.g., at a standard distance between soldering eye centers of 7.5 mm). If this is not permissible, the user shall take suitable measures.

Note: This photocoupler is suitable for safe electrical isolation only within the safety limit data. Maintenance of the safety data shall be ensured by means of protective circuits.

## 14. Package Information

### 14.1 Package dimensions

16pin SOIC Wide body

( P-SOP16-0811-1.27-002 )

Unit: mm

**Figure 14.1 Package Dimensions**

## 14.2 Land Pattern Dimensions for Reference only

16pin SOIC Wide body

(P-SOP16-0811-1.27-002 )

Unit: mm

Complies with JEITA ET-7501

Level 3 Normal

Creepage distance: 7.6 mm

Isolation option

Creepage distance: ≥ 8mm

**Figure 14.2 Land Pattern Dimensions for Reference only**

### Notes.

- Unless otherwise indicated, dimensions are given in millimeters.

- This document is a reference drawing in accordance with JEITA ET-7501 Level 3. The Company does not guarantee the accuracy or completeness of the diagrams and information.

- The customer should fully evaluate the various conditions (soldering conditions, etc.) and adjust at their own risk.

- The diagrams in this document do not accurately show the actual shape and dimensions. Do not use the dimensions of the actual product as a basis for designing the product.

- When designing and using the product, check the latest information on the product and the operating instructions of the equipment in which the product is to be used, and follow these instructions.

---

## RESTRICTIONS ON PRODUCT USE

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. **TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.**

- **PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE").** Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant. **IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT.** For details, please contact your TOSHIBA sales representative or contact us via our website.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- **ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.**

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. **TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.**

---

**Toshiba Electronic Devices & Storage Corporation**

<https://toshiba.semicon-storage.com/>