# 32-bit RISC Microcontroller Reference Manual

Flash Memory (Code Flash: 256KB/128KB) (FLASH256U2-A)

**Revision 1.1**

2025-01

**Toshiba Electronic Devices & Storage Corporation**

# Contents

| 1.1. Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Contents                                                           | 2  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----|

| Preface         8           Related Documents         8           Conventions         9           Terms and Abbreviation         11           1.0 Utiline         12           1.1. Memory Map         14           2. Configuration         15           2.1. Block Diagram         15           2.2. Configuration of Code Flash         16           2.2.1. Unit of Composition         16           2.2.1. Unit of Composition area Configuration of Code Flash         17           2.2.2. User Information Area Configuration of Code Flash         17           3. Function and Operation Explanation         18           Precautions         18           3.1. Code Flash         19           3.1.1. List of Command Sequence of Code Flash         19           3.1.1. Lommand Sequence of Code Flash         19           3.1.1. 2 Address Bit Configuration in Bus Write Cycle (Code Flash)         21           3.1.1. 4 Protect Bit Assignment (PBA): Code Flash         23           3.1.1. 4 Protect Bit Assignment (MSA)         24           3.1.1. 6 Memory Swap Bit Assignment (MSA)         24           3.2. 1 Nutomatic Programming         25           3.2. 2. Protect Bit         29           3.2. 3. 2. Frotect Bit                         | List of Figures                                                    | 6  |

| Related Documents       8         Conventions       9         Terms and Abbreviation       11         1. Outline       12         1.1. Memory Map       14         2. Configuration       15         2. I. Block Diagram       15         2.2. Configuration of Code Flash       16         2.2.1. Unit of Composition       16         2.2.2. User Information Area Configuration of Code Flash       17         2.2.3. Programming and Erasing Time of Code Flash       17         3. Function and Operation Explanation       18         Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       19         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       23         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Programming       25         3.2.3.                                                  | List of Tables                                                     | 7  |

| Conventions       9         Terms and Abbreviation       11         1. Outline       12         1.1. Memory Map       14         2. Configuration       15         2.1. Block Diagram       15         2.2. Configuration of Code Flash       16         2.2.1. Unit of Composition       16         2.2.2. User information Area Configuration of Code Flash       17         2.2.3. Programming and Erasing Time of Code Flash       17         3. Function and Operation Explanation       18         Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       19         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       23         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.5. Memory Swap       34         4.1. Operation Mode of Flash Memo                                                  | Preface                                                            | 8  |

| Terms and Abbreviation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Related Documents                                                  | 8  |

| 1. Outline       12         1.1. Memory Map       14         2. Configuration       15         2.1. Block Diagram       15         2.2. Configuration of Code Flash       16         2.2.1. Unit of Composition       16         2.2.2. User Information Area Configuration of Code Flash       17         2.2.3. Programming and Erasing Time of Code Flash       17         3. Function and Operation Explanation       18         Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.1. Address Bit Configuration in Bus Write Cycle (Code Flash)       19         3.1.1.1. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1. Protect Bit Assignment (PBA): Code Flash       23         3.1.1. Ib-Read Code (IA, ID): Code Flash       23         3.1.1. Automatic Programming       25         3.2. Automatic Frasing       25         3.2. Automatic Frasing       27         3.2.1. Automatic Programming       25         3.2. Automatic Frasin Memory       36         4.1. Functions       35         4.1. Operation Mode of Flash Memory       36      <                                      | Conventions                                                        | 9  |

| 1.1. Memory Map.       14         2. Configuration.       15         2.1. Block Diagram       15         2.2. Configuration of Code Flash.       16         2.2.1. Unit of Composition       16         2.2.2. User Information Area Configuration of Code Flash.       17         2.2.3. Programming and Erasing Time of Code Flash.       17         3. Function and Operation Explanation.       18         Precautions.       18         3.1. Code Flash.       19         3.1.1. List of Command Sequence of Code Flash.       19         3.1.1.1. List of Command Sequence of Code Flash.       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash).       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash.       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash.       23         3.1.1.6. Memory Swap Bit Assignment (MSA).       24         3.2. Flowchart.       25         3.2.1. Automatic Programming.       25         3.2.2. Automatic Erasing.       27         3.2.3. Protect Bit.       29         3.2.4. Security Bit.       31         3.2.5. Memory Swap.       35         4.1. Operation Mode of Flash Memory.       35         4.1. Functions.       36                             | Terms and Abbreviation                                             | 11 |

| 2. Configuration       15         2.1. Block Diagram       15         2.2. Configuration of Code Flash       16         2.2.1. Unit of Composition       16         2.2.2. User Information Area Configuration of Code Flash       17         2.2.3. Programming and Erasing Time of Code Flash       17         3. Function and Operation Explanation       18         Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       29         3.2.5. Memory Swap       33         4.1. Functions       36         4.1.2. How to Execute Command       36 <td>1. Outline</td> <td>12</td>      | 1. Outline                                                         | 12 |

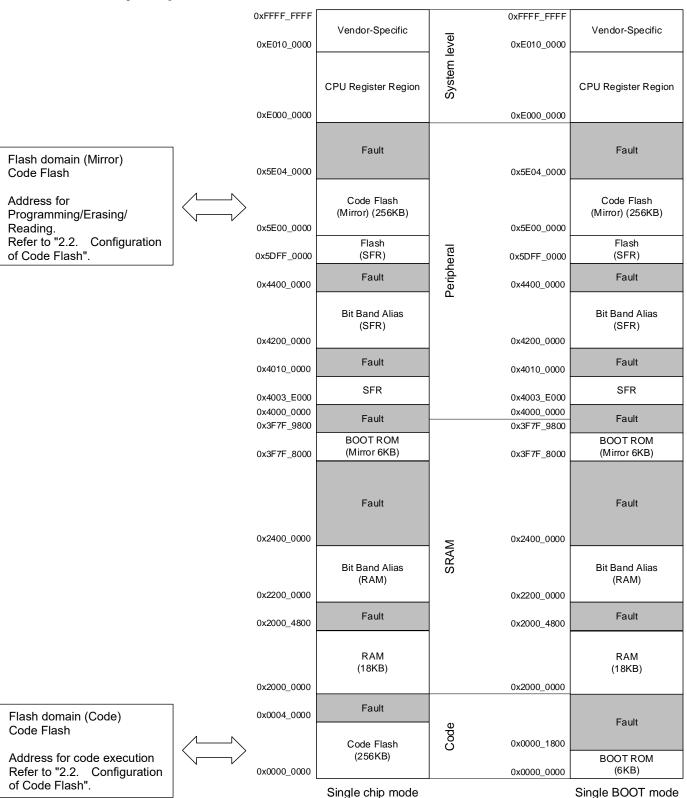

| 2. Configuration       15         2.1. Block Diagram       15         2.2. Configuration of Code Flash       16         2.2.1. Unit of Composition       16         2.2.2. User Information Area Configuration of Code Flash       17         2.2.3. Programming and Erasing Time of Code Flash       17         3. Function and Operation Explanation       18         Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       29         3.2.5. Memory Swap       33         4.1. Functions       36         4.1.2. How to Execute Command       36 <td>1.1. Memory Map</td> <td>14</td> | 1.1. Memory Map                                                    | 14 |

| 2.1. Block Diagram       15         2.2. Configuration of Code Flash       16         2.2.1. Unit of Composition       16         2.2.2. User Information Area Configuration of Code Flash       17         2.2.3. Programming and Erasing Time of Code Flash       17         3.5. Function and Operation Explanation       18         Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       29         3.2.5. Memory Swap       33         4.1. Functions       36         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command                        |                                                                    |    |

| 2.2. Configuration of Code Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |    |

| 2.2.1. Unit of Composition       16         2.2.2. User Information Area Configuration of Code Flash       17         2.2.3. Programming and Erasing Time of Code Flash       17         3. Function and Operation Explanation       18         Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       23         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4.1. Functions       36         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Programming<               | -                                                                  |    |

| 2.2.2. User Information Area Configuration of Code Flash       17         2.2.3. Programming and Erasing Time of Code Flash       17         3. Function and Operation Explanation       18         Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4.1. Functions       35         4.1. Functions       35         4.1. Operation Mode of Flash Memory       36         4.1. Operation Mode of Flash Memory       36         4.1.3. Automatic Programming       38         4.1.3. Automatic Programming       <                    |                                                                    |    |

| 2.2.3. Programming and Erasing Time of Code Flash.       17         3. Function and Operation Explanation       18         Precautions.       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash.       19         3.1.1.1. List of Command Sequence of Code Flash.       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA).       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4.1. Functions       35         4.1. Functions       35         4.1. Function Mode of Flash Memory       36         4.1. Scammand Description       36         4.1. Scammand Description       38         4.1. Scammand Description       38         4.1. Scammand Description       38         4.1                                                  | ·                                                                  |    |

| Precautions       18         3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                   | -                                                                  |    |

| 3.1. Code Flash       19         3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                        | 3. Function and Operation Explanation                              | 18 |

| 3.1.1. Command Sequence of Code Flash       19         3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3. Automatic Programming       38         4.1.3. Automatic Area Erasing       39         4.1.3.4. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                             | Precautions                                                        | 18 |

| 3.1.1.1. List of Command Sequence of Code Flash       19         3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash)       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                | 3.1. Code Flash                                                    | 19 |

| 3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash).       21         3.1.1.3. Area Address (AA), Block Address (BA): Code Flash.       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash.       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash.       24         3.1.1.6. Memory Swap Bit Assignment (MSA).       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing.       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                           | 3.1.1. Command Sequence of Code Flash                              | 19 |

| 3.1.1.3. Area Address (AA), Block Address (BA): Code Flash       23         3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |    |

| 3.1.1.4. Protect Bit Assignment (PBA): Code Flash       23         3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.1.1.2. Address Bit Configuration in Bus Write Cycle (Code Flash) | 21 |

| 3.1.1.5. ID-Read Code (IA, ID): Code Flash       24         3.1.1.6. Memory Swap Bit Assignment (MSA)       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.1.1.3. Area Address (AA), Block Address (BA): Code Flash         | 23 |

| 3.1.1.6. Memory Swap Bit Assignment (MSA).       24         3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |    |

| 3.2. Flowchart       25         3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |    |

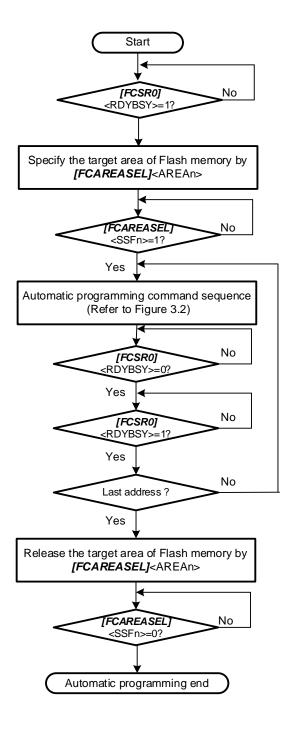

| 3.2.1. Automatic Programming       25         3.2.2. Automatic Erasing       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |    |

| 3.2.2. Automatic Erasing.       27         3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap.       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |    |

| 3.2.3. Protect Bit       29         3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |    |

| 3.2.4. Security Bit       31         3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                                                                  |    |

| 3.2.5. Memory Swap       33         4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |    |

| 4. Details of Flash Memory       35         4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·                                                                  |    |

| 4.1. Functions       35         4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |    |

| 4.1.1. Operation Mode of Flash Memory       36         4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                                                                  |    |

| 4.1.2. How to Execute Command       36         4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |    |

| 4.1.3. Command Description       38         4.1.3.1. Automatic Programming       38         4.1.3.2. Automatic Chip Erasing       39         4.1.3.3. Automatic Area Erasing       39         4.1.3.4. Automatic Block Erasing       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ·                                                                  |    |

| 4.1.3.1. Automatic Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |    |

| 4.1.3.2. Automatic Chip Erasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ·                                                                  |    |

| 4.1.3.3. Automatic Area Erasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |    |

| 4.1.3.4. Automatic Block Erasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.1.3.5. Automatic Page Erasing                                    | 40 |

# **TOSHIBA**

| 4.1.3.6. Automatic Protect Bit Programming              | 40 |

|---------------------------------------------------------|----|

| 4.1.3.7. Automatic Protect Bit Erasing                  | 41 |

| 4.1.3.8. Automatic Security Bit Programming             | 41 |

| 4.1.3.9. Automatic Security Bit Erasing                 | 42 |

| 4.1.3.10. ID-Read                                       | 43 |

| 4.1.3.11. Read/Reset Command                            | 43 |

| 4.1.3.12. Automatic Memory Swap Programming             | 43 |

| 4.1.3.13. Automatic Memory Swap Erasing                 | 44 |

| 4.1.4. Stopping Automatic Chip Erasing Operation        | 44 |

| 4.1.5. Completion Detection of Automatic Operation      | 45 |

| 4.1.5.1. Procedure                                      | 45 |

| 4.1.6. Protection Function                              | 45 |

| 4.1.6.1. How to Enable Protection Function              | 46 |

| 4.1.6.2. How to Disable Protection Function             | 46 |

| 4.1.6.3. Protection Function Temporary Disable Function | 46 |

| 4.1.7. Security Function                                | 47 |

| 4.1.7.1. How to Enable Security Function                | 47 |

| 4.1.7.2. How to Disable Security Function               | 47 |

| 4.1.7.3. Operation                                      | 47 |

| 4.1.8. Memory Swap Function                             | 48 |

| 4.1.8.1. How to Enable Memory Swap Function             | 48 |

| 4.1.8.2. How to Set                                     | 49 |

| 4.1.8.3. Erasing Memory Swap Information                | 50 |

| 4.1.9. User Information Area                            | 51 |

| 4.1.9.1. Switching Procedure of User Information Area   | 51 |

| 4.1.9.2. How to Program Data to User Information Area   | 51 |

| 4.1.9.3. How to Erase User Information Area             | 51 |

| 4.1.10. Read Buffer                                     | 52 |

| 4.1.10.1. Read Buffer Operation                         | 53 |

| 5. Registers                                            | 54 |

| 5.1. Register List                                      | 54 |

| 5.2. Detail of Register                                 | 55 |

| 5.2.1. [FCSBMR] (Flash Security Bit Mask Register)      |    |

| 5.2.2. [FCSSR] (Flash Security Status Register)         |    |

| 5.2.3. [FCKCR] (Flash Key Code Register)                |    |

| 5.2.4. [FCSR0] (Flash Status Register 0)                |    |

| 5.2.5. [FCPSR0] (Flash Protection Status Register 0)    |    |

| 5.2.6. [FCPSR1] (Flash Protect Status Register 1)       |    |

| 5.2.7. [FCPMR0] (Flash Protect Mask Register 0)         |    |

| 5.2.8. [FCPMR1] (Flash Protect Mask Register 1)         |    |

| 5.2.9. [FCSR1] (Flash Status Register 1)                |    |

| 5.2.10. [FCSWPSR] (Flash Memory SWAP Status Register)   |    |

| 5.2.11. [FCAREASEL] (Flash Area Selection Register)     |    |

| 5.2.12. [FCCR] (Flash Control Register)                 |    |

| 5.2.13. [FCSTSCLR] (Flash Status Clear Register)        |    |

| J.Z. 10. [1 COTOOLA] (Flash Status Cleal Register)      | 01 |

# **TOSHIBA**

| 5.2.14. [FCBNKCR] (Flash Bank Change Register)                                            | 61 |

|-------------------------------------------------------------------------------------------|----|

| 5.2.15. [FCACCR] (Flash Access Control Register)                                          | 62 |

| 5.2.16. [FCBUFDISCLR] Flash Buffer Disable/Clear Register                                 | 63 |

| 6. Programming Method                                                                     | 64 |

| 6.1. Initialization                                                                       | 64 |

| 6.2. Mode Description                                                                     | 64 |

| 6.3. Mode Determination                                                                   | 65 |

| 6.4. Memory Map in Each Mode                                                              | 65 |

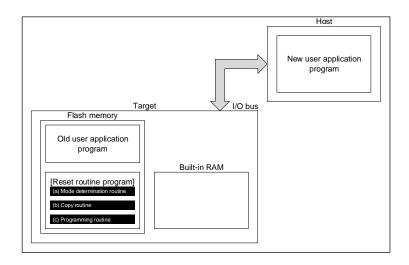

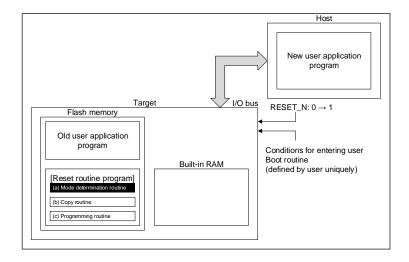

| 6.5. How to Reprogram Flash Memory                                                        | 66 |

| 6.5.1. (1-A) Example Procedure that Reprogramming Routine Stored in Flash Memory          |    |

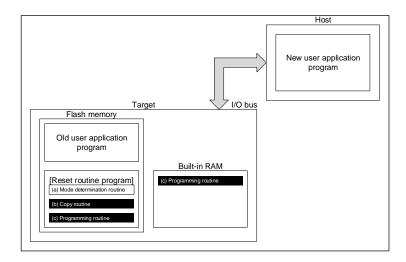

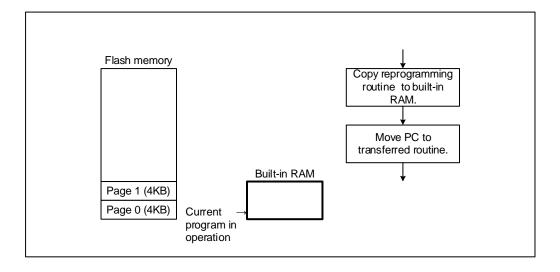

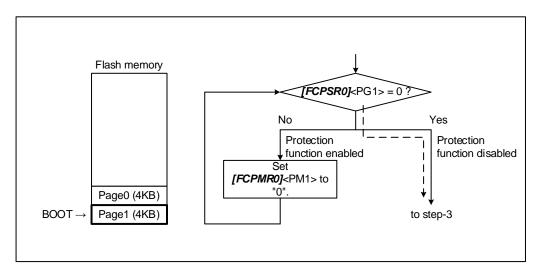

| 6.5.1.1. Step-1                                                                           | 67 |

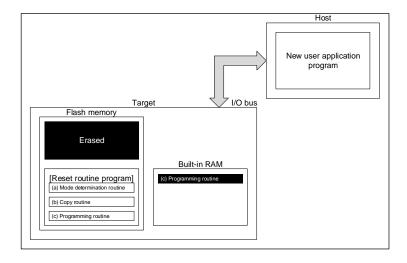

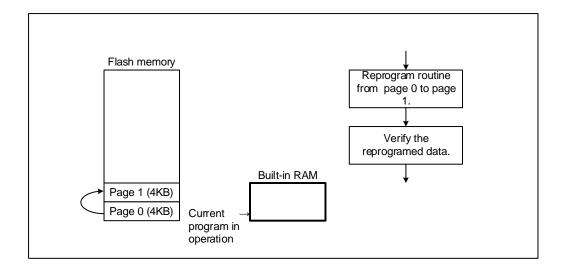

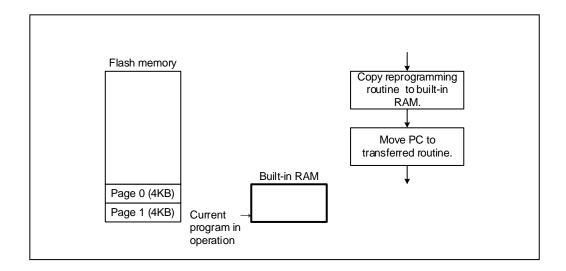

| 6.5.1.2. Step-2                                                                           | 68 |

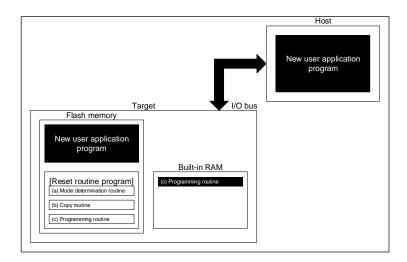

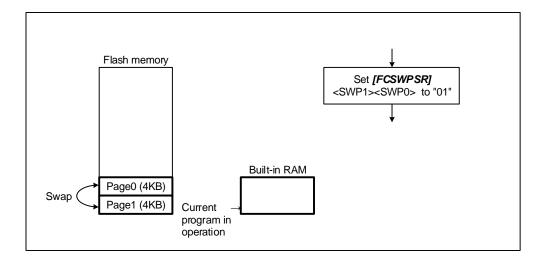

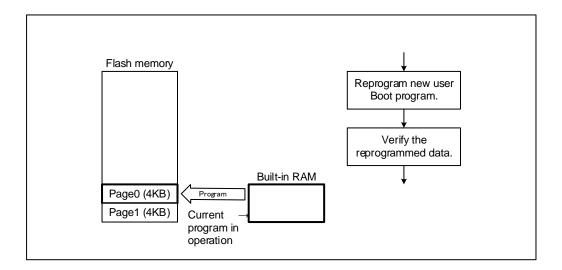

| 6.5.1.3. Step-3                                                                           | 68 |

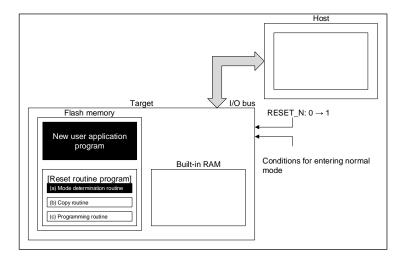

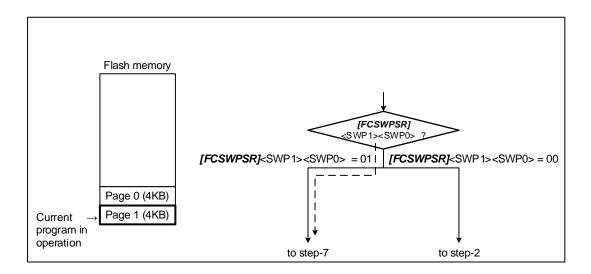

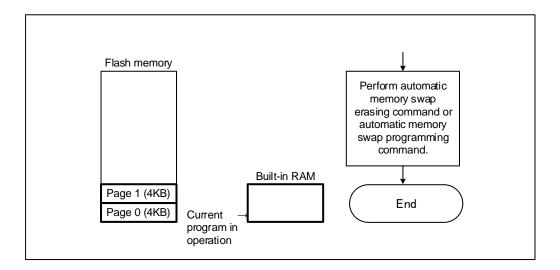

| 6.5.1.4. Step-4                                                                           | 69 |

| 6.5.1.5. Step-5                                                                           | 69 |

| 6.5.1.6. Step-6                                                                           | 70 |

| 6.5.2. (1-B) Example Procedure that Reprogramming Routine is Transferred from Host        | 71 |

| 6.5.2.1. Step-1                                                                           | 71 |

| 6.5.2.2. Step-2                                                                           | 72 |

| 6.5.2.3. Step-3                                                                           | 72 |

| 6.5.2.4. Step-4                                                                           | 73 |

| 6.5.2.5. Step-5                                                                           | 73 |

| 6.5.2.6. Step-6                                                                           | 74 |

| 6.6. How to Reprogram Flash in Single Boot Mode                                           | 75 |

| 6.6.1. Outlines                                                                           | 75 |

| 6.6.2. Mode Setting                                                                       | 76 |

| 6.6.3. Interface Specifications                                                           | 76 |

| 6.6.3.1. Communicate by UART                                                              | 76 |

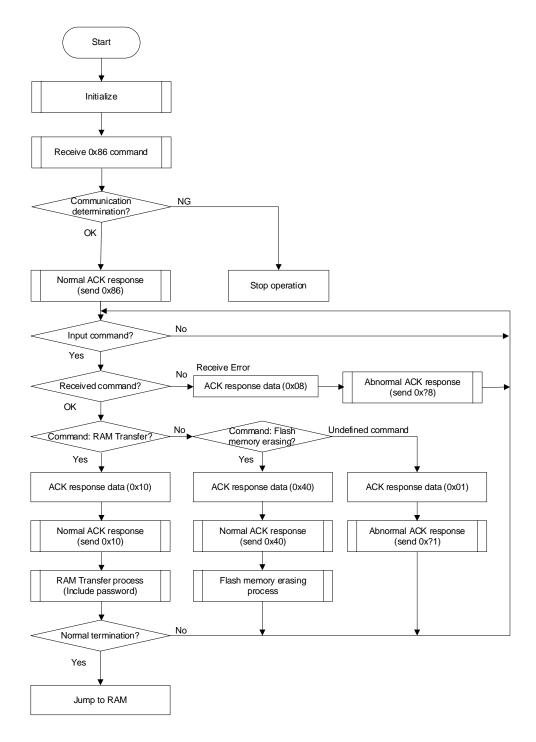

| 6.6.4. General Flowchart of Internal Boot Program                                         | 77 |

| 6.6.5. Restrictions on Memories                                                           | 78 |

| 6.6.6. Operation Command                                                                  | 78 |

| 6.6.6.1. RAM Transfer                                                                     | 78 |

| 6.6.6.2. Flash Memory Erasing                                                             | 78 |

| 6.6.7. Common Operation Regardless of Command                                             | 79 |

| 6.6.7.1. Serial Communication Determination                                               | 79 |

| 6.6.7.2. Acknowledgement Response Data                                                    | 79 |

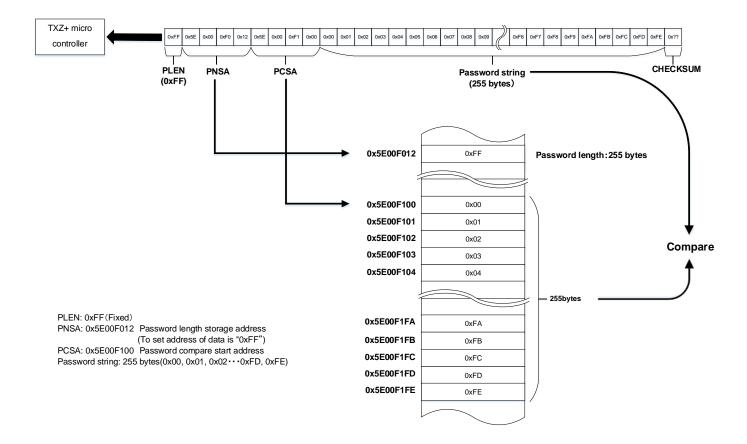

| 6.6.7.3. Password                                                                         | 81 |

| 6.6.7.4. CHECKSUM Calculation                                                             | 83 |

| 6.6.8. Communication Rules of RAM Transfer Command                                        | 84 |

| 6.6.9. Communication Rules of Flash Memory Erasing Command                                | 87 |

| 6.6.10. Reprogramming Procedure of Flash Memory Using Reprogramming Algorithm in BOOT ROM | 88 |

| 6.6.10.1. Step-1                                                                          | 88 |

| 6.6.10.2. Step-2                                                                          | 89 |

| 6.6.10.3. Step-3                                                                          | 89 |

| 6.6.10.4. Step-4                                                                          | 90 |

## Flash Memory

# **TOSHIBA**

|    | 6.6.10.5. Step-5                                       | 90  |

|----|--------------------------------------------------------|-----|

|    | 6.6.10.6. Step-6                                       | 91  |

| 6  | 6.7. How to Reprogram User Boot Program                | 92  |

|    | 6.7.1. Example of Flash Memory Reprogramming Procedure | 92  |

|    | 6.7.1.1. Step-1                                        | 92  |

|    | 6.7.1.2. Step-2                                        | 93  |

|    | 6.7.1.3. Step-3                                        | 93  |

|    | 6.7.1.4. Step-4                                        | 94  |

|    | 6.7.1.5. Step-5                                        | 94  |

|    | 6.7.1.6. Step-6                                        | 95  |

|    | 6.7.1.7. Step-7                                        | 95  |

|    | 6.7.1.8. Step-8                                        |     |

|    | 6.7.1.9. Step-9                                        | 96  |

|    | 6.7.1.10. Step-10                                      | 97  |

| 7. | General Precautions                                    | 98  |

| 8. | Revision History                                       | 99  |

| RE | ESTRICTIONS ON PRODUCT USE                             | 100 |

# List of Figures

| Figure 1.1   | Example of Memory Map (Code: 256KB)                                                   | . 14 |

|--------------|---------------------------------------------------------------------------------------|------|

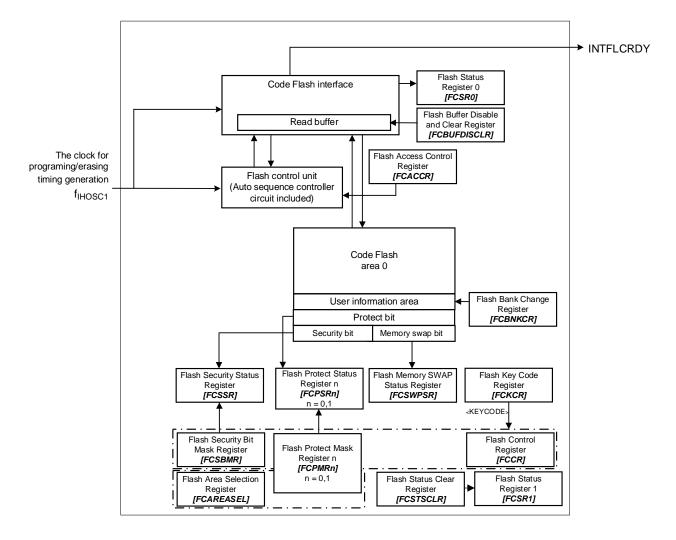

| Figure 2.1   | Block Diagram of Flash Memory                                                         |      |

| Figure 3.1   | Flowchart of Automatic Programming (1)                                                | 25   |

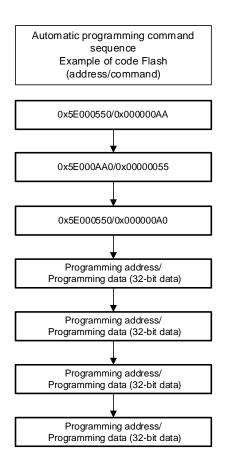

| Figure 3.2   | Flowchart of Automatic Programming (2)                                                | 26   |

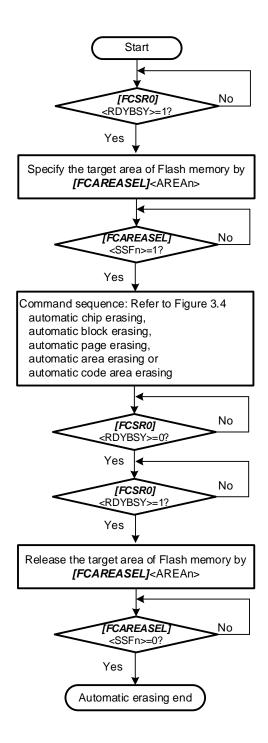

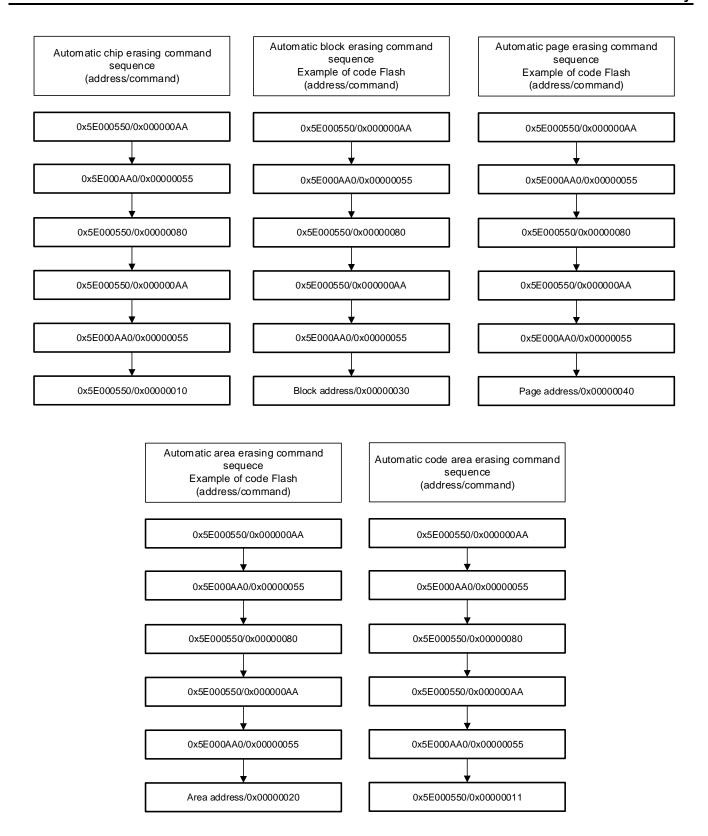

| Figure 3.3   | Flowchart of Automatic Erasing (1)                                                    |      |

| Figure 3.4   | Flowchart of Automatic Erasing (2)                                                    |      |

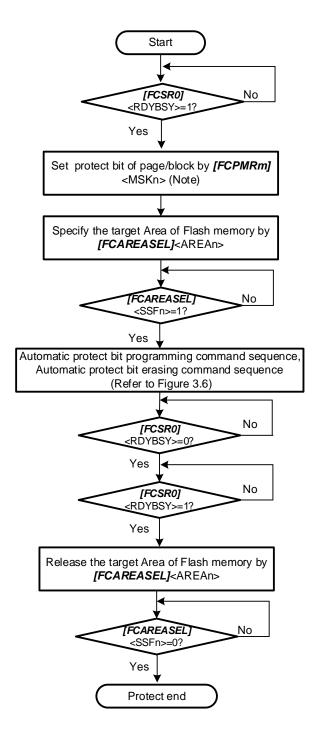

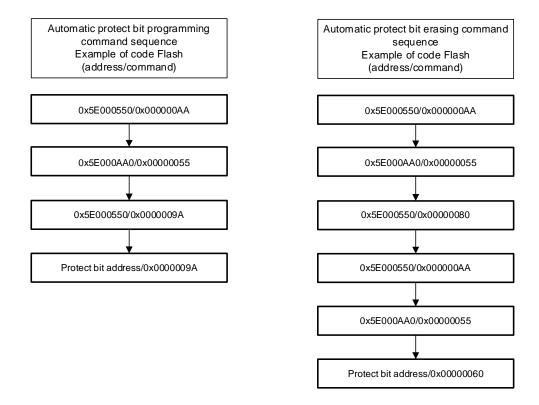

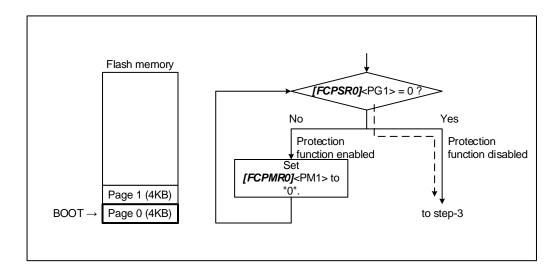

| Figure 3.5   | Flowchart of Protect (1)                                                              |      |

| Figure 3.6   | Flowchart of Protect (2)                                                              |      |

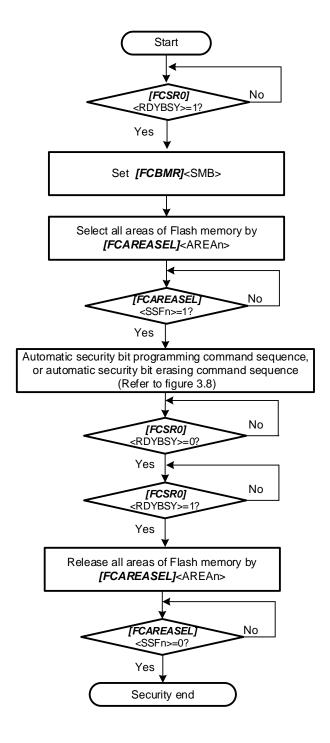

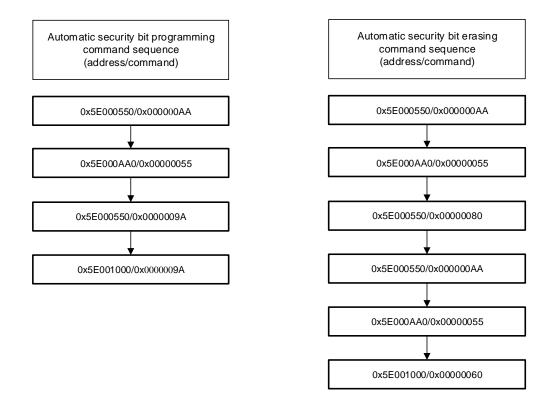

| Figure 3.7   | Flowchart of Security (1)                                                             |      |

| Figure 3.8   | Flowchart of Security (2)                                                             |      |

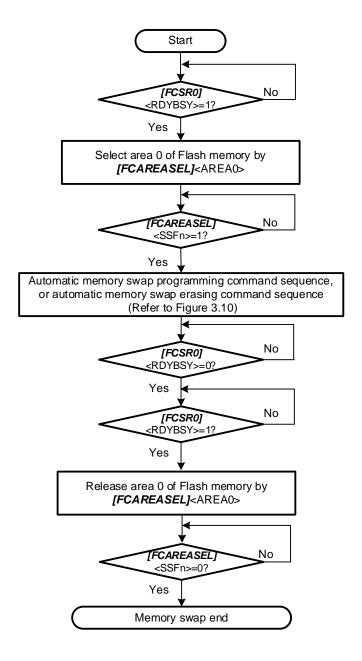

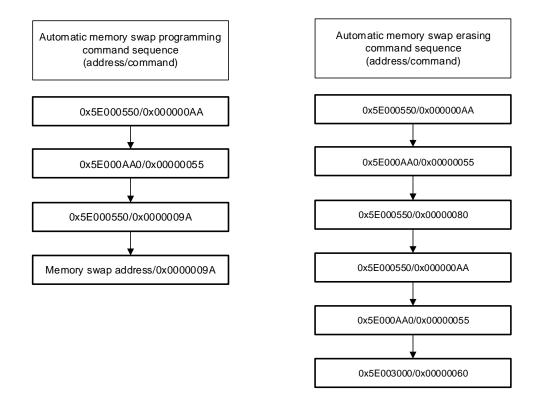

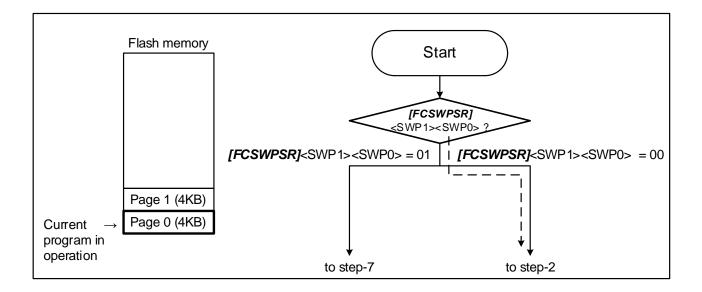

| Figure 3.9   | Flowchart of Memory Swap (1)                                                          |      |

| Figure 3.10  | Flowchart of Memory Swap (2)                                                          | . 34 |

| Figure 4.1   | Example of Memory Śwap Procedure                                                      |      |

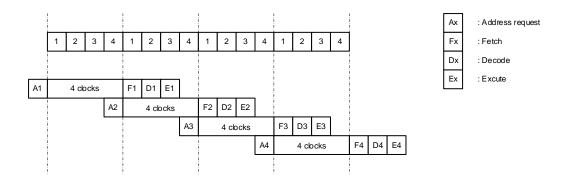

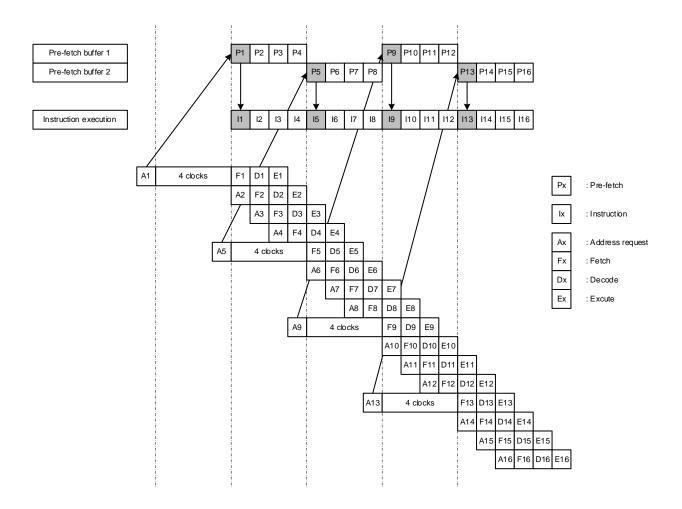

| Figure 4.2   | Example of Read Buffer Operation when Read Buffer is Disabled                         |      |

| Figure 4.3   | Example of Read Buffer Operation when Read Buffer is Enabled                          |      |

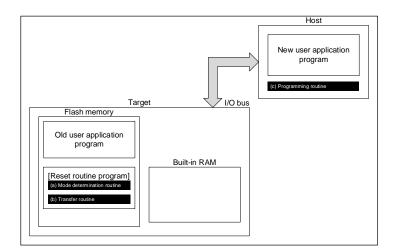

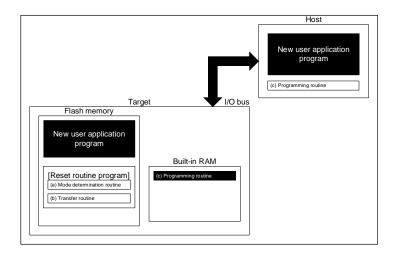

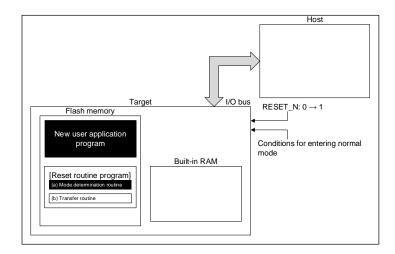

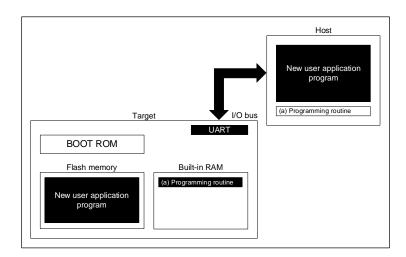

| Figure 6.1   | Procedure that Reprogramming Routine Stored in Flash Memory (1)                       |      |

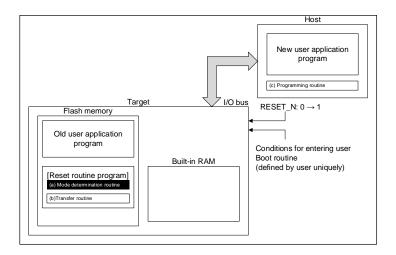

| Figure 6.2   | Procedure that Reprogramming Routine Stored in Flash memory (2)                       |      |

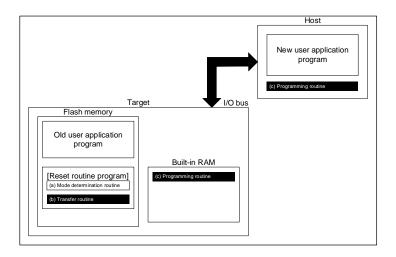

| Figure 6.3   | Procedure that Reprogramming Routine Stored in Flash Memory (3)                       |      |

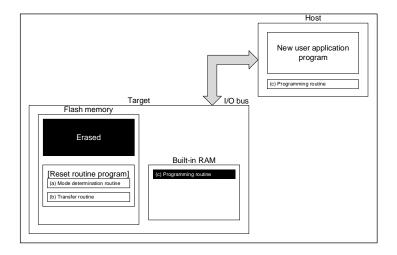

| Figure 6.4   | Procedure that Reprogramming Routine Stored in Flash memory (4)                       |      |

| Figure 6.5   | Procedure that Reprogramming Routine Stored in Flash Memory (5)                       |      |

| Figure 6.6   | Procedure that Reprogramming Routine Stored in Flash Memory (6)                       |      |

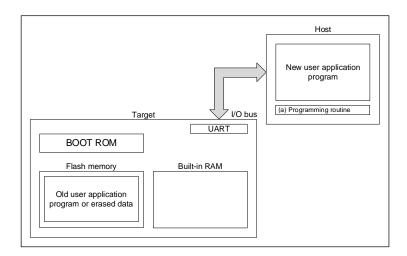

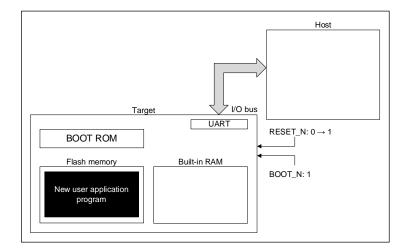

| Figure 6.7   | Procedure that Reprogramming Routine is Transferred from External Host Controller (1) |      |

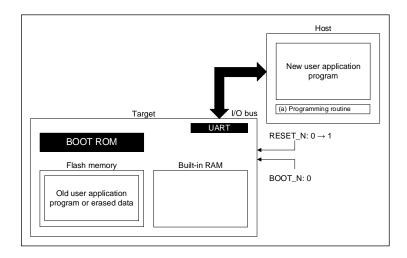

| Figure 6.8   | Procedure that Reprogramming Routine is Transferred from External Host Controller (2) |      |

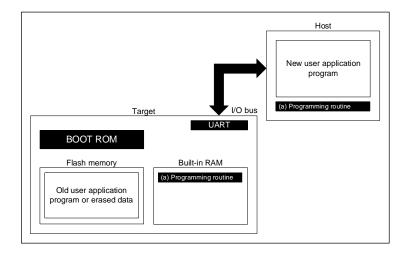

|              | Procedure that Reprogramming Routine is Transferred from External Host Controller (3) |      |

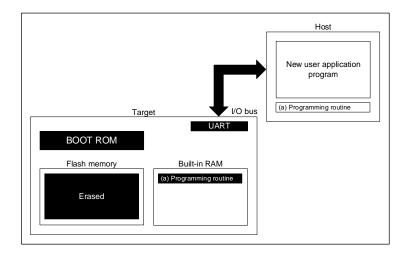

|              | Procedure that Reprogramming Routine is Transferred from External Host Controller     |      |

| rigule 0.10  | 1 Tocedure that Neprogramming Nouthle is Transferred Trom External Flost Controller   |      |

| Figure 6 11  | Procedure that Reprogramming Routine is Transferred from External Host Controller     |      |

| 1 19410 0.11 | Tresedure that Repregramming Reduite to Transferred Hom External Freet Controller     |      |

| Figure 6.12  | Procedure that Reprogramming Routine is Transferred from Host (6)                     | _    |

| Figure 6.13  |                                                                                       |      |

| Figure 6.14  |                                                                                       |      |

| Figure 6.15  |                                                                                       |      |

| •            | ogram (1)                                                                             |      |

| Figure 6.16  |                                                                                       |      |

| •            |                                                                                       | . 89 |

|              | Reprogramming Procedure of Flash Memory Using Reprogramming Algorithm in Inter        |      |

|              | ogram (3)                                                                             |      |

| Figure 6 18  | Reprogramming Procedure of Flash Memory Using Reprogramming Algorithm in Inter        |      |

|              | ogram (4)                                                                             |      |

|              | Reprogramming Procedure of Flash Memory Using Reprogramming Algorithm in Inter        |      |

|              | ogram (5)                                                                             |      |

| Figure 6.20  | Reprogramming Procedure of Flash Memory Using Reprogramming Algorithm in Inter        | mal  |

|              | ogram (6)                                                                             |      |

| Figure 6.21  | Reprogram by User Boot Program (1)                                                    | ือา  |

| 0            |                                                                                       |      |

| Figure 6.22  |                                                                                       |      |

| Figure 6.23  |                                                                                       |      |

| Figure 6.24  |                                                                                       |      |

| Figure 6.25  |                                                                                       |      |

| Figure 6.26  |                                                                                       |      |

| Figure 6.27  |                                                                                       |      |

| Figure 6.28  | Reprogram by User Boot Program (8)                                                    |      |

| Figure 6.29  | Reprogram by User Boot Program (9)                                                    |      |

| Figure 6.30  | Reprogram by User Boot Program (10)                                                   | . 97 |

# List of Tables

| lable 1.1  | Functional Description (Code Flash)                                         |    |

|------------|-----------------------------------------------------------------------------|----|

| Table 1.2  | Functional Description (User Information Area)                              | 13 |

| Table 2.1  | Signal List                                                                 | 15 |

| Table 2.2  | Block Configuration of 256KB Code Flash                                     | 16 |

| Table 2.3  | Block Configuration of 128KB Code Flash                                     | 16 |

| Table 2.4  | User Information Area Configuration of Code Flash                           | 17 |

| Table 2.5  | Programming and Erasing Time of Code Flash                                  | 17 |

| Table 3.1  | JEDEC Compliant Functions                                                   | 18 |

| Table 3.2  | Command Sequence (Code Flash)                                               | 19 |

| Table 3.3  | Address Bit Configuration in Bus Write Cycle (Code Flash)                   |    |

| Table 3.4  | Protect Bit Selection by Programming Address                                |    |

| Table 3.5  | ID-Read Command Code Assignment and Code Contents (Code Flash)              |    |

| Table 3.6  | Setting Values to Memory Swap Address in Memory Swap Programming Command,   |    |

| Table 4.1  | Flash Memory Function                                                       |    |

| Table 4.2  | Detection of Completion of Programming/Erasing Flash                        |    |

| Table 4.3  | Flash Memory Operation and Debug Function When Security Function is Enabled |    |

| Table 6.1  | Mode and Operation                                                          |    |

| Table 6.2  | Operation Mode Setting                                                      |    |

| Table 6.3  | Functions and Commands                                                      |    |

| Table 6.4  | Example of Used Pins (UART)                                                 |    |

| Table 6.5  | Restrictions on Memories in Single Boot Mode                                |    |

| Table 6.6  | Operation Commands in Single Boot Mode                                      |    |

| Table 6.7  | Setting of Baud Rate in Single Boot Mode (fc = 10MHz, without Error)        |    |

| Table 6.8  | ACK Response Data Corresponding to Serial Operation Determination Data      |    |

| Table 6.9  | ACK Response Data Corresponding to Operation Command Data                   |    |

| Table 6.10 | ACK Response Data Corresponding to CHECKSUM Data                            |    |

| Table 6.11 | ACK Response Data Corresponding to Flash Memory Erasing Operation           |    |

| Table 6.12 | Password Setting Values and Setting Ranges                                  |    |

| Table 6.13 | Communication Rules of RAM Transfer Command                                 |    |

| Table 6.14 | Communication Rules of Flash Memory Erasing Command                         | 87 |

| Table 8.1  | Revision History                                                            | 99 |

Rev. 1.1

# **Preface**

#### **Related Documents**

| Document name                             |

|-------------------------------------------|

| Clock Control and Operation Mode          |

| Exception                                 |

| Input/Output Ports                        |

| Product Information                       |

| Asynchronous Serial Communication Circuit |

#### **Conventions**

• Numeric formats follow the rules as shown below:

Hexadecimal: 0xABC

Decimal: 123 or 0d123 - Only when it needs to be explicitly shown that they are decimal

numbers.

Binary: 0b111 - It is possible to omit the "0b" when the number of bits can be

distinctly understood from a sentence.

• "N" is added to the end of signal names to indicate low active signals.

• It is called "assert" that a signal moves to its active level, "deassert" to its inactive level.

• When two or more signal names are referred, they are described like as [m:n]. Example: S[3:0] shows four signal names S3, S2, S1 and S0 together.

• The characters surrounded by [] defines the register.

Example: [ABCD]

• "n" substitutes suffix number of two or more same kind of registers, fields, and bit names.

Example: [XYZ1], [XYZ2],  $[XYZ3] \rightarrow [XYZn]$

- "x" substitutes suffix number or character of units and channels in the register list.

- In case of unit, "x" means A, B, and C, ...

Example: [ADACR0], [ADBCR0],  $[ADCCR0] \rightarrow [ADxCR0]$

• In case of channel, "x" means 0, 1, and 2, ...

Example: [T32A0RUNA], [T32A1RUNA],  $[T32A2RUNA] \rightarrow [T32AxRUNA]$

• The bit range of a register is written like as [m: n].

Example: Bit[3: 0] expresses the range of bit 3 to 0.

- The configuration value of a register is expressed by either the hexadecimal number or the binary number. Example: |ABCD| < EFG > = 0x01 (hexadecimal), |XYZn| < VW > = 1 (binary)

- Word and byte represent the following bit length.

Byte: 8 bits

Half word: 16 bits

Word: 32 bits

Double word: 64 bits

• Properties of each bit in a register are expressed as follows:

R: Read only W: Write only

R/W: Read and write are possible.

- Unless otherwise specified, register access supports only word access.

- The register defined as "Reserved" must not be rewritten. Moreover, do not use the read value.

- The value read from the bit having default value of "-" is unknown.

- When a register containing both of writable bits and read-only bits is written, read-only bits should be written with their default value, In the cases that default is "-", follow the definition of each register.

- Reserved bits of the write-only register should be written with their default value. In the cases that default is "-", follow the definition of each register.

- Do not use read-modified-write processing to the register of a definition which is different by writing and read out.

All other company names, product names, and service names mentioned herein may be trademarks of their respective companies.

10 / 100 2025-01-17

#### **Terms and Abbreviation**

Some of abbreviations used in this document are as follows:

ACK Acknowledgement

Addr Address

Adr Address

BLK Block

KB Kilo Bytes

PG Page

POR Power-on Reset

PORF Power-on Reset for Flash and Debug

SFR Special Function Register

UART Asynchronous Serial Communication Circuit

## 1. Outline

The code Flash which stores a program code is explained.

A code Flash stores an instruction code, and CPU reads and executes it.

There is user information area which can be accessed in a code Flash by switching bank. Since user information area is not erased by a chip erasing command, an unique management number, and etc. can be written to it.

**Table 1.1 Functional Description (Code Flash)**

| Area                | Function                 | Basic function          | Functional description                                                                         | Comments                                    |

|---------------------|--------------------------|-------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------|

|                     |                          | Automatic programming   | Data programming is performed at 4 words (16 bytes).                                           |                                             |

|                     |                          | Automatic chip erasing  | Erasing all area of a Flash memory is performed automatically.                                 | Except user information area in code Flash. |

|                     | Programming and erasing  | Automatic area erasing  | Erasing in an area unit is performed automatically.                                            |                                             |

|                     |                          | Automatic block erasing | Erasing in a block unit is performed automatically.                                            |                                             |

|                     |                          | Automatic page erasing  | performed automatically.                                                                       |                                             |

| Code Flash<br>256KB | Program/erase protection | Protection              | Programming and erasing can be prohibited per block. (Note)                                    |                                             |

| 128KB               | Security                 | Security                | Prohibition of read-out from the Flash memory by a flash writer and of using a debugging tool. |                                             |

|                     | Memory swap              | Automatic memory swap   | Swap /swap release /swap size specification of a code Flash block is performed automatically.  |                                             |

|                     | Execute instruction      | Execute instruction     |                                                                                                |                                             |