CDMOS Linear Integrated Circuits Silicon Monolithic

# TB9032FNG

Automotive CXPI communication driver receiver IC

## **1. INTRODUCTION**

TB9032FNG is a driver receiver IC that is compliant with ISO 20794-4 for the CXPI (Clock Extension Peripheral Interface) communication. It can switch between commander and responder nodes using the external pin. When in Sleep Mode, it enters a standby state with low power consumption. In addition, it is equipped with fault detection functions including overheat detection and low voltage detection, and stops output when an abnormality is detected.

P-SOP8-0405-1.27-002

## 2. APPLICATIONS

- Automotive body system applications such as steering switches, meter cluster switches, light switches, door locks, and door mirror control

- Interfaces of zone ECUs

## **3. FEATURES AND BENEFITS**

- CXPI communication driver receiver IC

- Physical layer interface conforming to CXPI (Clock Extension Peripheral Interface) automotive communication protocol standard

- Operating voltage VBAT: 7 to 18 V

- Microcomputer interface: 4.5 to 5.5 V

- Operating temperature range (Ta): -40 to 125 °C

- Junction temperature (Tj): 150 °C (max)

- Package: SOP8

- Sleep Mode

- Wake-up Transmission Mode

- Dominant timeout detection function

- Overheat detection function

- Undervoltage detection function (BAT, VIO)

- Communication speed: 20 kbps (max)

- To conform to AEC-Q100, AEC-Q006 (planned)

#### This material is for reference only. Do not use this for final equipment design.

**Preliminary**

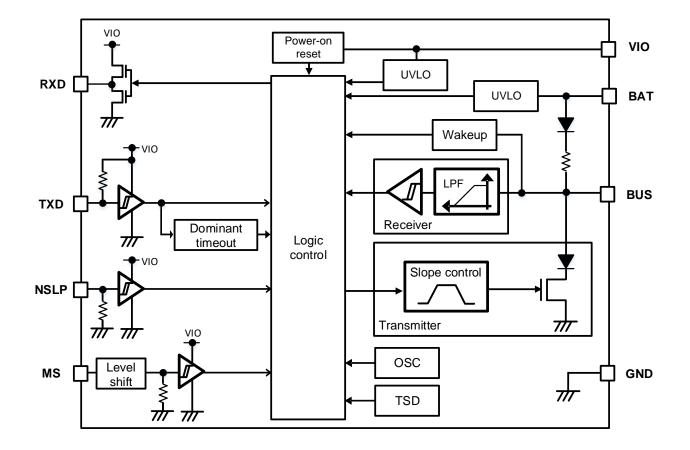

# 4. BLOCK DIAGRAM

Figure 4 Block Diagram

Preliminary

## **5. INFORMATION ON PINS**

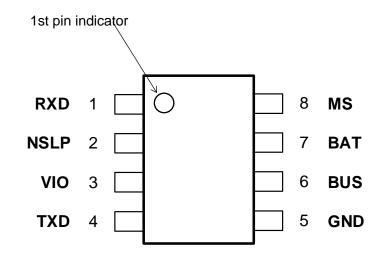

### 5.1. Pin Assignment (Top view)

#### 5.2. Pin Arrangement and Function Description

| Table 5.2 | Pin Arrangement and Function Description |

|-----------|------------------------------------------|

|-----------|------------------------------------------|

| No. | Name | Device<br>Type | Withstand<br>Voltage<br>(V) | I/O             | Pull-up/<br>Pull-down | Description                                                                        |

|-----|------|----------------|-----------------------------|-----------------|-----------------------|------------------------------------------------------------------------------------|

| 1   | RXD  | CMOS           | 6                           | Output          | -                     | Output pin of CXPI signals received from BUS                                       |

| 2   | NSLP | CMOS           | 6                           | Input           | Pull-down             | In Normal Mode: High input<br>In Sleep Mode or Wakeup Transmission Mode: Low input |

| 3   | VIO  | CMOS           | 6                           | Power<br>source | -                     | 5 V Interface                                                                      |

| 4   | TXD  | CMOS           | 6                           | Input           | Pull-up               | Input pin of CXPI signals to be transmitted to BUS                                 |

| 5   | GND  | CMOS           | -                           | -               | -                     | GND                                                                                |

| 6   | BUS  | DMOS           | 40                          | I/O             | -                     | CXPI communication BUS pin                                                         |

| 7   | BAT  | DMOS           | 40                          | Power source    | -                     | Connected to the battery                                                           |

| 8   | MS   | DMOS           | 40                          | Input           | -                     | Commander node: High input<br>Responder node: Low input                            |

All parts should be correctly mounted and electrically connected before using the IC. The IC may experience abnormal operation, operate differently from the settings, or not operate when adjacent pins are short-circuited or a pin is open, though it may work normally even in such cases.

Preliminary

TB9032FNG

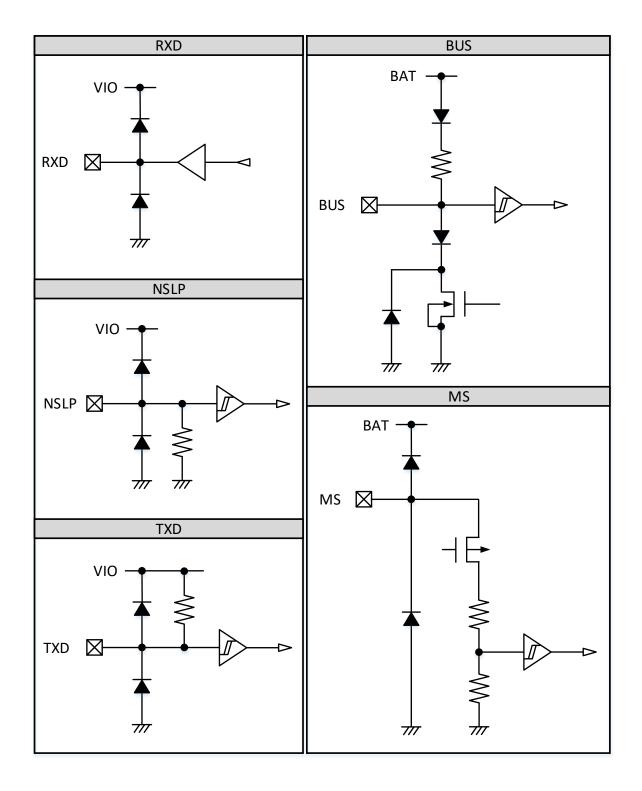

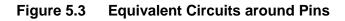

## 5.3. Equivalent Circuits around Pins

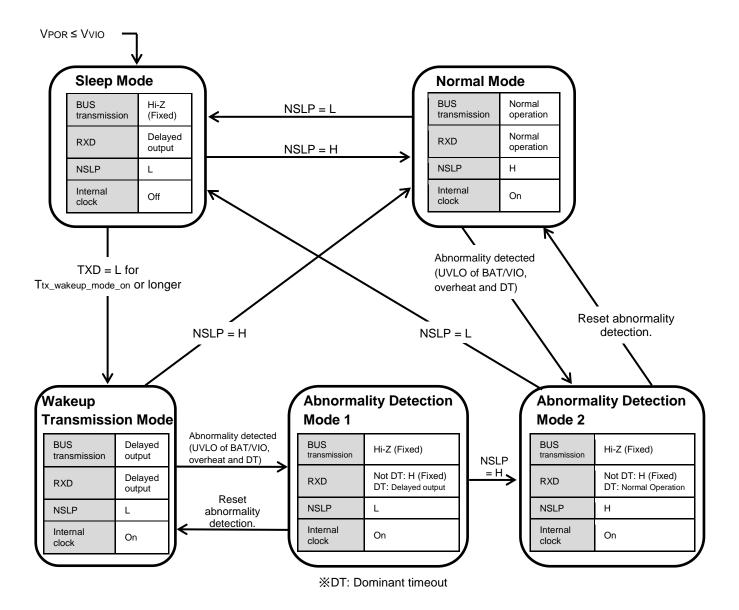

## 6. STATE TRANSITION

State transition of this IC is shown below.

Reset when  $V_{VIO} < V_{POR}$ . This applies to all modes.

### 6.1. Transition to Sleep Mode

When the  $V_{VIO}$  power is turned on, the IC enters Sleep Mode. Additionally, if NSLP = L is input from an MCU during Normal Mode, the IC will transition to Sleep Mode within a certain time period, Tsleep.

#### 6.2. Transition to Wakeup Transmission Mode

The IC will transition to Wakeup Transmission Mode if it receives "TXD = L" from an MCU for a period of Ttx\_wakeup\_mode\_on or longer when in Sleep Mode. In Wakeup Transmission Mode, TXD signal received from an MCU can be transmitted from BUS as a wake-up pulse for the responder node trigger. Please refer to "7.2.3.1 Responder Node" for information on wakeup pulses for the responder node trigger.

According to the CXPI standards, transmission of wakeup pulse in the responder node trigger is part of operational sequence initiated by a responder node. Please refer to "7.2.2.1. Commander Node" for information on wakeup pulses for the commander node trigger.

#### 6.3. Transition to Normal Mode

When this IC is in sleep mode, both commander node and responder node transition to normal mode when NSLP = H has been received from MCU.

When this IC is in wakeup transmission mode, it transmits a wakeup pulse triggered by a responder node and then transitions to normal mode by receiving "NSLP = H" from MCU.

CXPI communication can be conducted normally in normal mode. Also, a commander node transmits a wakeup pulse.

#### 6.4. Transition to Abnormality Detection Mode 1

When the state is wakeup transmission mode and abnormality is detected, the state transitions to abnormality detection mode 1. For types of abnormality detection and conditions for detection and resetting, refer to "7.1 Abnormality Detection Functions." Note that the state transitions to wakeup transmission mode when abnormality detection has been reset. In addition, when NSLP = H is received from MCU, the state transitions to abnormality detection mode 2.

#### 6.5. Transition to Abnormality Detection Mode 2

When the state is normal mode and abnormality is detected, the state transitions to abnormality detection mode 2. For types of abnormality detection and conditions for detection and resetting, refer to "7.1 Abnormality Detection Functions". Note that the state transitions to normal mode when abnormality detection has been reset. In addition, when NSLP = L is received from MCU, the state transitions to sleep mode.

# 7. OPERATIONS

### 7.1. Abnormality Detection Functions

As abnormality detection functions, this IC is equipped with detection functions for TXD dominant timeout, overheat, and undervoltage of BAT and VIO. Each detection function works as follows.

| Abnormality Detection<br>Function | Description                                                                                             | BUS Output    | RXD Output                               |

|-----------------------------------|---------------------------------------------------------------------------------------------------------|---------------|------------------------------------------|

| BAT undervoltage<br>(UVLO of BAT) | Detects by V <sub>BAT</sub> ≤ V <sub>BAT_UV.</sub><br>Resets by V <sub>BAT</sub> ≥ V <sub>BAT_UV.</sub> | Hi-Z(H) Fixed | High Fixed                               |

| VIO undervoltage<br>(UVLO of VIO) | Detects by $V_{VIO} \leq V_{VIO_UV}$ .<br>Resets when $V_{VIO} \geq V_{VIO_UV}$ .                       | Hi-Z(H) Fixed | High Fixed                               |

| VIO undervoltage (POR)            | Detects by $V_{VIO} \leq V_{POR}$ and resets.                                                           | Hi-Z(H) Fixed | High Fixed                               |

| Dominant timeout                  | Detects by TXD = Low for TDTC or longer.<br>Resets when TXD input = High.                               | Hi-Z(H) Fixed | Delayed output<br>or normal<br>operation |

| Overheat (TSD)                    | Detects by $T_{TSD} \le T_J$ .<br>Resets when $T_{HYS}$ is low and $T_J < 150^{\circ}$ C.               | Hi-Z(H) Fixed | High Fixed                               |

### Table 7.1 Abnormality Detection Functions

### 7.1.1. BAT Undervoltage Detection (UVLO of BAT)

When the power source voltage ( $V_{BAT}$ ) is  $V_{BAT_{UV}}$  or lower, undervoltage is detected, and BUS output and RXD output are stopped. When the power source voltage recovers to  $V_{BAT_{UV}}$  or higher, abnormality detection is reset.

### 7.1.2. VIO Undervoltage Detection (UVLO of VIO)

When the power source voltage ( $V_{VIO}$ ) is  $V_{VIO_UV}$  or lower, undervoltage is detected, and BUS output and RXD output are stopped. When the power source voltage is recovered to  $V_{VIO_UV}$  or higher, abnormality detection is reset.

## 7.1.3. VIO Undervoltage Detection (POR)

When the power source voltage ( $V_{VIO}$ ) is  $V_{POR}$  or lower, undervoltage is detected, and the IC is reset. This operation applies to all modes defined in "6. State Transition."

## 7.1.4. Overheat Detection (TSD)

When the IC's Tj temperature has exceeded  $T_{TSD}$ , overheat is detected, and BUS output and RXD output are stopped. After that, when the temperature decreases from the detected overheat temperature by about  $T_{HYS}$  or Tj < 150°C is observed, the abnormality detection is reset. Note that the overheat detection function is not tested at mass production shipment, but an alternative test is conducted.

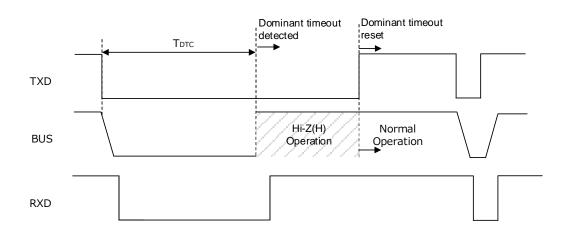

#### 7.1.5. Dominant Timeout

When "Low" time of TXD input from the microcomputer is long and dominant time of BUS output has exceeded  $T_{DTC}$ , this timeout is detected, BUS output is stopped and is set to Hi-Z (H). RXD outputs delayed output in abnormality detection mode 1 and operates normally in abnormality detection mode 2, and when any other abnormality is detected simultaneously, the other abnormality detection is given priority and RXD becomes High (Fixed).

When TXD input becomes High, abnormality detection is reset.

Figure 7.1.5 Sequence of Dominant Timeout

### 7.2. Operation Sequences

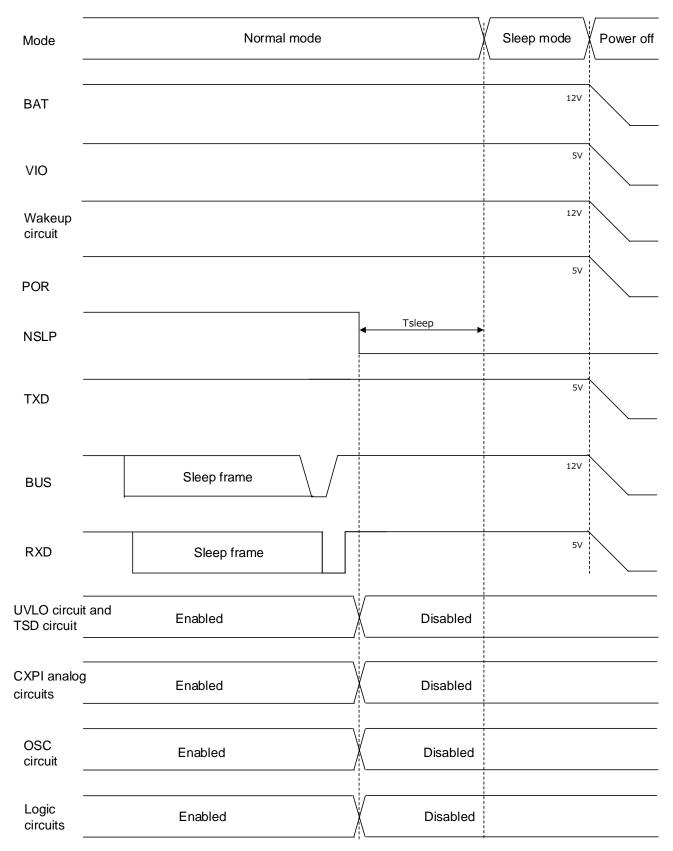

#### 7.2.1. Sleep Mode and Power-off Sequence

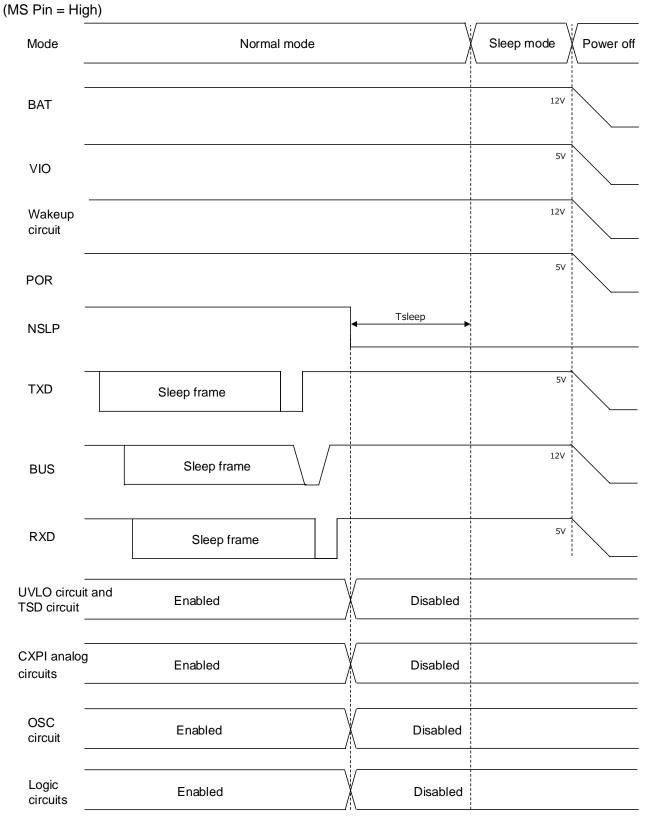

#### 7.2.1.1. Commander Node

When the state transitions to sleep mode and power is turned off, the operation sequence of commander node is as shown below.

Figure 7.2.1.1 Sleep Mode and Power-off Sequence (Commander Node)

- 1. Sleep Frame from MCU is transmitted to BUS.

- 2. NSLP = L is received from MCU, which triggers to turn off UVLO, TSD, OSC, analog circuits (transceiver circuit and receiver circuit).

- 3. When OSC is turned off, the digital logic is also turned off.

- 4. Operations in 2 and 3 above are completed during Tsleep, and the IC then operates in sleep mode.

- 5. When the voltage of BAT and VIO become low, the wakeup circuit is turned off. Also, V<sub>VIO</sub> < V<sub>POR</sub> is observed and power is turned off.

Supplementary information:

Sleep Frame is not directly related to the operation of TB9032FNG. Sleep Frame transmission at a commander node related to sleep mode transition is described as reference information.

# Preliminary

#### 7.2.1.2. Responder Node

When the state transitions to sleep mode and power is turned off, the operation sequence of a responder node is as shown below.

(MS Pin = Low)

#### Figure 7.2.1.2 Sleep Mode and Power-off Sequence (Responder Node)

- 1. Sleep Frame is received from BUS.

- 2. NSLP = L is received from MCU, which triggers to turn off UVLO, TSD, OSC, analog circuits (transceiver circuit and receiver circuit).

- 3. When OSC is turned off, digital logic is also turned off.

- 4. Operations in 2 and 3 are completed during Tsleep, and the IC operates in the sleep mode.

- 5. When the voltage of BAT and VIO become low, the wakeup circuit is turned off. In addition,  $V_{VIO} < V_{POR}$  is observed and power is turned off.

Supplementary information:

Sleep Frame is not directly related to the operation of TB9032. Sleep Frame reception at a responder node related to sleep mode transition is described as reference information.

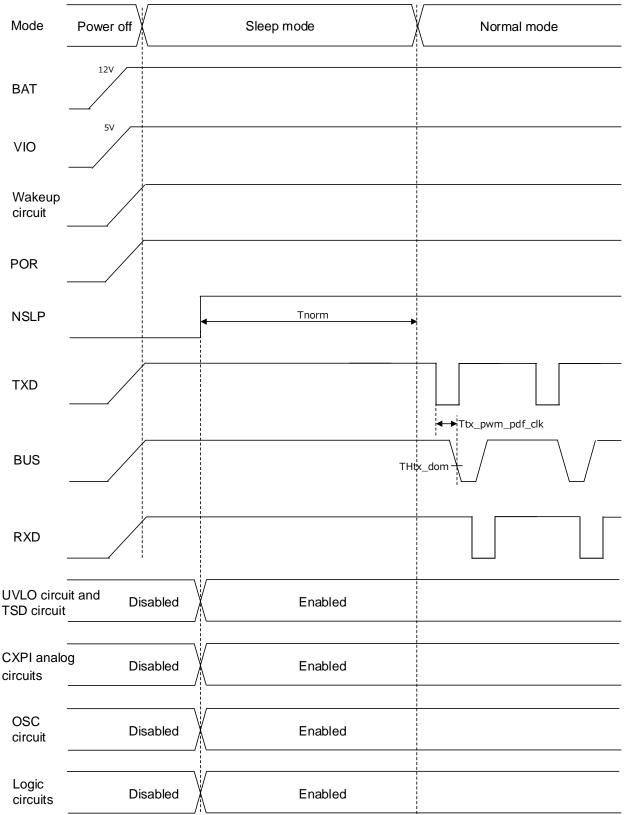

#### 7.2.2. Power-on and Wakeup Sequence (Triggered by a Commander Node)

#### 7.2.2.1. Commander Node

When a wakeup is caused by a commander node, the operation sequence of the commander node is as shown below.

(MS Pin = High)

Figure 7.2.2.1 Wakeup Sequence Triggered by a Commander Node (Commander Node)

- 1. When the power sources of BAT and VIO are turned on, the wakeup circuit and POR circuit are turned on.

- 2. Pins of TXD, BUS and RXD are fixed at High, and the IC operates in this state in sleep mode.

- 3. When NSLP = H is received from MCU, it triggers to turn on UVLO, TSD, OSC and analog circuits (transceiver circuit and receiver circuit).

- 4. OSC starts normal operation.

- 5. The digital logic is turned on triggered by NSLP = H and starts normal operation using OSC as reference.

- 6. Operations in 3 to 5 above are completed during Tnorm, and the IC then starts operation in the normal mode. By receiving TXD = L from MCU and transmitting BUS = L for a certain period or longer, a wakeup pulse triggered by the commander node is transmitted.

Supplementary explanation:

When NSLP = H is input with the power sources of BAT and VIO off, Internal circuitry doesn't work. After that, when the power sources of BAT and VIO are turned on, operations from 3 to 6 above are conducted triggered by NSLP = H, and the state transitions to normal mode.

# Preliminary

## 7.2.2.2. Responder Node

When a wakeup is caused by a commander node, the operation sequence of the responder node is as shown below.

(MS Pin = Low)

Figure 7.2.2.2 Wakeup Sequence Triggered by a Commander Node (Responder Node)

- 1. When the power sources of BAT and VIO are turned on, the wake-up circuit and POR circuit are turned on.

- 2. Pins of TXD, BUS and RXD are fixed at High, and in this state, the IC operates in sleep mode.

- 3. "Low" width (a wake-up pulse triggered by the commander node) for over Trx\_wakeup\_responder is received from BUS, and is output to RXD.

- 4. When NSLP = H is received from MCU, it triggers to turn on UVLO, TSD, OSC and analog circuits (transceiver circuit and receiver circuit).

- 5. OSC starts normal operation.

- 6. The digital logic is turned on triggered by NSLP = H, and starts normal operation using OSC as reference.

- 7. Operations in 4 to 6 above are completed during Thorm, the IC then works in the normal mode.

#### Notes:

1.Request regarding use for microcomputers:

When the state transitions to normal mode, do not make judgment between logic 0 and logic 1 based on RXD value before Tnorm has passed.

When the state changes from sleep mode to normal mode, the delay time of RXD changes as described below.

When RXD is output in the wakeup circuit with NSLP = L, the fall (TF) delay time from BUS to RXD is Trx\_wakeup\_responder: 5  $\mu$ s (max), and the rise time (TR) is also

Trx\_wakeup\_responder\_pdr: 5  $\mu$ s (max). After, when NSLP = H occurs and CXPI analog circuits have been turned on, the fall (TF) delay time from BUS to RXD changes to Trx pwm pdf: 2.1  $\mu$ s (max) and rise time (TR) is also Trx pwm pdr: 2.1  $\mu$ s (max).

In the wakeup sequence, the timing when RXD value becomes valid is 0.5 ms after the power sources of BAT and VIO have been turned on, so it should be taken into consideration.

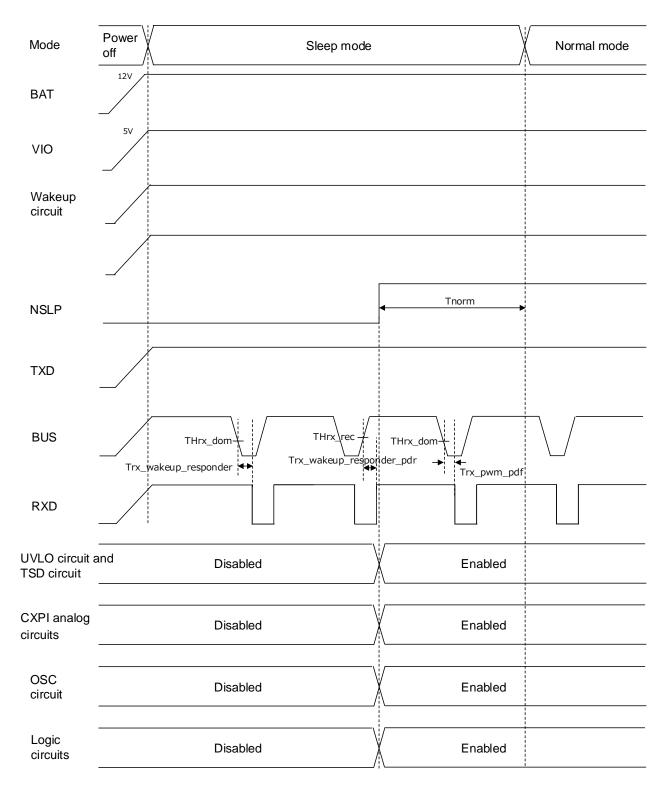

#### 7.2.3. Power-on and Wakeup Sequence (Triggered by a Responder Node)

#### 7.2.3.1. Responder Node

When a wakeup is caused by a responder node, the operation sequence of the responder node is as shown below.

(MS Pin = Low)

### Figure 7.2.3.1 Wakeup Sequence Triggered by a Responder Node (Responder Node)

- 1. When the power sources of BAT and VIO are turned on, the wakeup circuit and POR circuit are turned on.

- 2. Pins of TXD, BUS and RXD are fixed to High (Note 1), and in this state, the IC works in sleep mode.

- 3. When TXD = L is received from MCU for a period (Trx\_wakeup\_mode) or longer, the wakeup internal signal is fixed to High.

- 4. Triggered by the wakeup internal signal, UVLO, TSD and analog circuits (transceiver circuit and receiver circuit) are turned on. (Wakeup transmission mode starts.)

- 5. In addition, OSC and Logic are turned on, and BUS = L is output.

Supplementary explanation 1:

The BUS = L output here works as a wakeup pulse triggered by the responder node. Supplementary explanation 2:

The delay time from TXD = L to BUS = L is Ttx\_wakeup\_responder\_pdf.

- 6. After, when Low width (wakeup pulse from the commander node) for the period of Trx\_wakeup\_responder or longer from BUS is detected, it is output to RXD.

- 7. When NSLP = H is received from MCU, it makes the wakeup internal signal Low.

- 8. OSC starts normal operation.

- 9. The digital logic starts normal operation using OSC as reference.

- 10. Operations 7 to 9 are completed during Thorm, and the IC then works in normal mode.

Supplementary explanation 3:

Even if TXD = H happens before BUS = L is output after the wakeup internal signal becomes High, the wakeup internal signal is fixed at High, and circuits (BGR, UVLO, TSD, analog circuits, OSC and logic) are turned on. However, after that, BUS = L (wakeup pulse triggered by the responder node) is not output.

Note 1:

When TXD = L is externally set while the power sources are being turned on, the state does not transition to sleep mode and wakeup transmission mode starts. In wakeup transmission mode, the consumption current is equivalent to that in normal mode.

# Preliminary

#### 7.2.3.2. Commander Node [RS-OP-01232]

When a wakeup is caused by a responder node, the operation sequence of the commander node is as shown below.

(MS Pin = High)

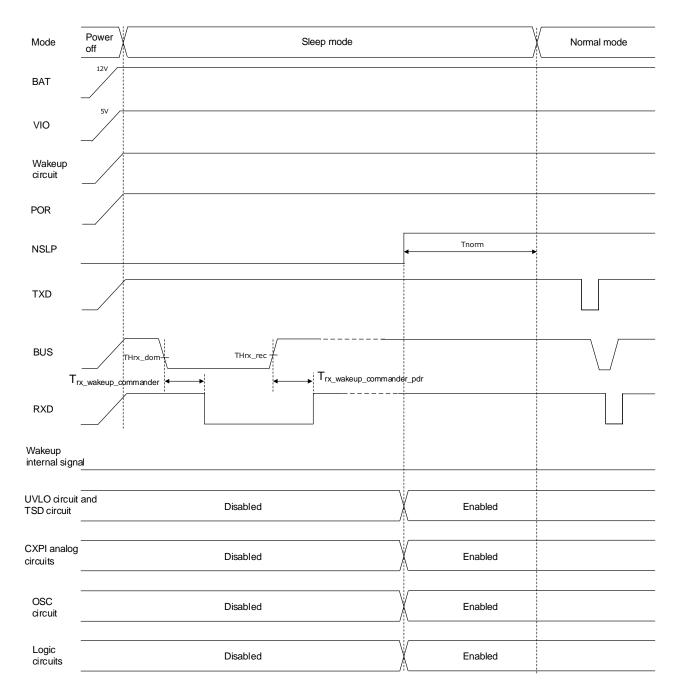

#### Figure 7.2.3.2 Wakeup Sequence Triggered by a Responder Node (Commander Node)

- 1. When the power sources of BAT and VIO are turned on, the wakeup circuit and POR circuit are turned on.

- 2. Pins of TXD, BUS and RXD are fixed to High, and in this state, the IC works in sleep mode.

- 3. When "Low" width (a wakeup pulse triggered by the responder node) for the period of Trx\_wakeup\_commander or longer from BUS is detected, it is output to RXD.

- 4. When NSLP = H is received from MCU, it triggers to turn on UVLO, TSD, OSC and analog circuits (transceiver circuit and receiver circuit).

- 5. OSC starts normal operation.

- 6. The digital logic is turned on triggered by NSLP = H, and starts normal operation using OSC as reference.

- 7. Operations 4 to 6 above are completed during Thorm, and the IC then works in normal mode.

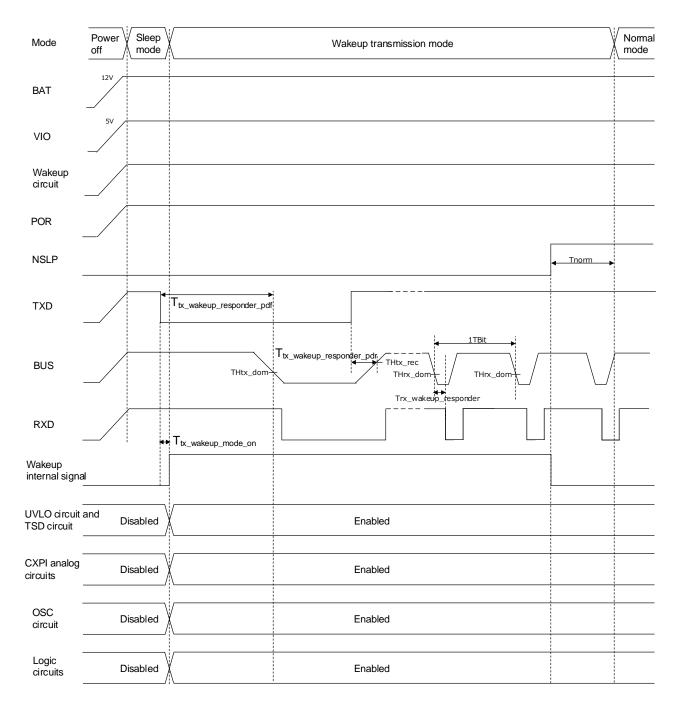

#### 7.2.4. Delay Time in BUS Transmission

When TXD = L is received from MCU and BUS = L is output in normal mode, the delay time differs between a commander node and a responder node.

#### 7.2.4.1. Commander Node

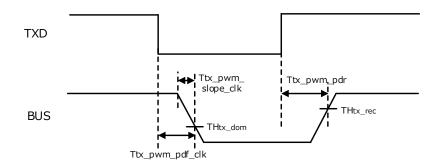

To transmit clock to BUS, a commander node operates with the same delay time from TXD to BUS for both rise and fall (Ttx\_pwm\_pdf\_clk = Ttx\_pwm\_pdr = 16.9  $\mu$ s (max)). The slope of the BUS is 8  $\mu$ s (max) (Ttx\_pwm\_slope\_clk) from the fall of the BUS to the dominant (THtx\_dom = 0.3 × VBAT).

Figure 7.2.4.1 Delay Time in BUS Transmission (Commander Node)

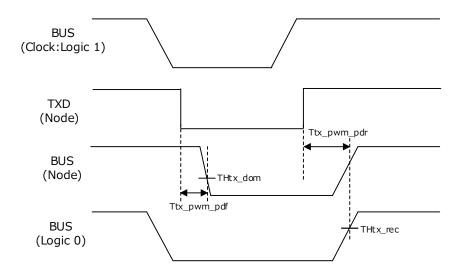

#### 7.2.4.2. Responder Node

As a responder node receives BUS clock from the commander node and transmits a BUS waveform of logic 0, the fall delay time of the BUS is short. The delay time from TXD to BUS fall is 2.9  $\mu$ s (max) (Ttx\_pwm\_pdf). For the BUS rise, however, the delay time is the same as that of a commander node (Ttx\_pwm\_pdr = 16.9  $\mu$ s (max)).

Figure 7.2.4.2 Delay Time in BUS Transmission (Responder Node)

**Preliminary**

TB9032FNG

## 8. ABSOLUTE MAXIMUM RATINGS

| Table 8 | Absolute Maximum Ratings |

|---------|--------------------------|

|---------|--------------------------|

(Ta = -40 to 125 °C unless otherwise specified)

|                                 |                                       |           | (1a = -40  to  125  °C)                              |                                                   | specified |

|---------------------------------|---------------------------------------|-----------|------------------------------------------------------|---------------------------------------------------|-----------|

| Item                            | Symbol                                | Pin       | Test Conditions                                      | Rating                                            | Unit      |

| Power source<br>voltage 1       | VBAT                                  | BAT       | Voltage between BAT and GND pin                      | - 0.3 to 40                                       | V         |

| Power source<br>voltage 2       | Vvio                                  | VIO       | Voltage between VIO and GND pin                      | - 0.3 to 6                                        | V         |

| Input withstand<br>voltage 1    | V <sub>MS</sub>                       | MS        | $V_{MS} \leq V_{BAT}$                                | - 0.3 to V <sub>BAT</sub>                         | V         |

| Input withstand<br>voltage 2    | V <sub>TXD</sub><br>V <sub>NSLP</sub> | TXD, NSLP | -                                                    | - 0.3 to V <sub>VIO</sub> + 0.3<br>and -0.3 to 6  | V         |

| Output withstand voltage        | Vrxd                                  | RXD       | -                                                    | - 0.3 to V <sub>VIO</sub> + 0.3<br>and - 0.3 to 6 | V         |

| I/O withstand<br>voltage        | V <sub>BUS</sub>                      | BUS       | $7 \text{ V} \leq \text{ V}_{BAT} \leq 18 \text{ V}$ | - 27 to 40                                        | V         |

| Output current                  | I <sub>BUS</sub>                      | BUS       | -                                                    | 200                                               | mA        |

| Junction<br>temperature         | Tj                                    | -         | -                                                    | 150                                               | °C        |

| Storage<br>temperature<br>range | Tstg                                  | -         | -                                                    | - 55 to 150                                       | °C        |

The absolute maximum ratings are standard values that must not be exceeded even momentarily. When any absolute maximum rating is exceeded, it may cause destruction, degradation, or damage to the IC and/or other parts. Design systems so that absolute maximum ratings are not exceeded in any operating condition.

Please use this IC within the operating ranges described above.

#### 8.1. Thermal Resistance

- · Thermal resistance values that include the below board

- $\Theta_{JA}$  • Between junction and ambient temperature  $\Theta_{JA} = 147.9$  °C/W

- $\Psi_{JT}$  • Between junction and package upper surface center  $\Psi_{JT}$  = 5.6 °C/W

Board conditions

- 1-layer board

- Board size (FR-4) 114.3 mm × 76.2 mm × 1.57 mm t

- 1st layer Copper foil thickness: 70 µm

- Copper foil area: 1L land pattern area : Cu 50 %, lead wires area : Cu 25 % (Area of land pattern and lead wires is assumed.)

# 9. OPERATING RANGES

| _                                       |           |     |                    |      |                                               |

|-----------------------------------------|-----------|-----|--------------------|------|-----------------------------------------------|

| Item                                    | Symbol    | Pin | Operating<br>Range | Unit | Remark                                        |

| BAT normal operation<br>range           | $V_{BAT}$ | BAT | 7 to 18            | V    | -                                             |

| Function operation (BAT high voltage)   | Vbat      | BAT | 18 to 27           | V    | Function operation only (Note 1), (Note 2)    |

| Function operation<br>(BAT low voltage) | Vbat      | BAT | VBAT_UV to 7       | V    | Function operation only (Note 1), (Note 2)    |

| VIO normal operation<br>range           | Vvio      | VIO | 4.5 to 5.5         | V    | Supports 5 V power source<br>of microcomputer |

| Function operation (VIO low voltage)    | Vvio      | VIO | Vvio_uv to 4.5     | V    | Function operation only (Note 1), (Note 2)    |

| Operating temperature<br>range          | Та        | -   | - 40 to 125        | °C   | -                                             |

#### Table 9Operating Ranges

Note 1) Details of the function operation are as shown below.

- 1. Receives BUS recessive and maintains RXD = H.

- 2. Transmits RXD = L when TXD = L is received. Load condition: RL = 500  $\Omega$

- 3. Maintains the state without being shut down.

- 4. Electrical characteristics during function operation follow "10.2. Characteristics of RXD and TXD".

- 5. During BAT function operation, VIO is assumed to be within the normal operation range.

- 6. During VIO function operation, BAT is assumed to be within the normal operation range.

- 7. Except the function operation following 1 to 6 above, each item in the electrical characteristics table is not guaranteed.

- Note 2) The operating ranges and operating conditions are design guidelines to obtain expected performance. As each item is an independent guideline, specified values in the electrical characteristics table and so on must also be checked when designing.

# Preliminary

## **10. ELECTRICAL CHARACTERISTICS**

## 10.1. IC Overall

| Table 10.1IC Characteristics |

|------------------------------|

|------------------------------|

| 1                                        |                               | = 7 to 18 V, Ta = -                                                            |                             |                             |                        | 1    |

|------------------------------------------|-------------------------------|--------------------------------------------------------------------------------|-----------------------------|-----------------------------|------------------------|------|

| Characteristics                          | Symbol                        | Test Conditions                                                                | Min                         | Тур.                        | Max                    | Unit |

| BAT<br>Consumption current (Sleep)       | IBAT_SLP                      | NSLP = L, TXD = H,<br>$BUS = V_{BAT}$                                          | -                           | 5                           | -                      | μA   |

| Consumption current (Normal)             | BAT_NORM                      | NSLP = H                                                                       | -                           | -                           | 2                      | mA   |

| BAT undervoltage detection               | VBAT_UV                       | Function operation only during $V_{BAT_UV}$ detection by VBAT < 7 V (Note 1)   | 5.0                         | -                           | 6.7                    | V    |

| BAT undervoltage detection hysteresis    | Vbat_hys                      | -                                                                              | -                           | 0.5                         | -                      | V    |

| BAT slew rate while power source rising  | TBAT_SLPO<br>E                | -                                                                              | 0.01                        | -                           | 2                      | V/µs |

| VIO                                      |                               |                                                                                |                             |                             |                        |      |

| Consumption current (Sleep)              |                               | NSLP = L                                                                       | -                           | 3                           | -                      | μA   |

| Consumption current (Normal)             | I <sub>VIO_NORM</sub>         | NSLP = H                                                                       | -                           | -                           | 10                     | mA   |

| VIO undervoltage detection               | Vvio_uv                       | Function operation only during $V_{VIO_UV}$ detection by VVIO < 4.5 V (Note 1) | 3.7                         | -                           | 4.5                    | V    |

| VIO undervoltage detection<br>hysteresis | V <sub>VIO_HYS</sub>          | -                                                                              | -                           | 0.5                         | -                      | V    |

| POR detection                            | VPOR                          | -                                                                              | 1.5                         | 2.5                         | 3.5                    | V    |

| POR detection hysteresis                 | $V_{\text{POR}\_\text{HYS}}$  | -                                                                              | -                           | 0.2                         | -                      | V    |

| VIO slew rate while power source rising  | TVIO_SLPOE                    | -                                                                              | 0.01                        | -                           | 0.5                    | V/µs |

| NSLP                                     |                               |                                                                                |                             |                             |                        |      |

| Input High voltage                       | VIH_NSLP                      | -                                                                              | 0.8 × V <sub>VIO</sub>      | -                           | -                      | V    |

| Input Low voltage                        | $V_{\text{IL}_{\text{NSLP}}}$ | -                                                                              | -                           | -                           | 0.2 × V <sub>VIO</sub> | V    |

| Input hysteresis                         | VNSLP_HYS                     | -                                                                              | 0.032<br>× V <sub>VIO</sub> | 0.065<br>× V <sub>VIO</sub> | 0.13<br>× Vvio         | V    |

| Pull-down resistance                     | R <sub>NSLP</sub>             | NSLP = 5 V                                                                     | 50                          | 100                         | 200                    | kΩ   |

| MS                                       |                               |                                                                                |                             |                             |                        |      |

| Input High voltage                       | V <sub>IH_MS</sub>            | -                                                                              | 3.0                         | -                           | -                      | V    |

| Input Low voltage                        | VIL_MS                        | -                                                                              | -                           | -                           | 2.0                    | V    |

| Input hysteresis                         | $V_{MS_HYS}$                  | -                                                                              | -                           | 0.5                         | -                      | V    |

| Input High current                       | I <sub>IH_MS</sub>            | $MS = V_{BAT} = 12 V$                                                          | -                           | 3                           | -                      | μA   |

| Input Low current                        | I <sub>IL_MS</sub>            | MS = 0 V                                                                       | -                           | 0                           | -                      | μA   |

| Oscillator                               |                               |                                                                                |                             |                             |                        |      |

| Frequency                                | OSC                           | -                                                                              | -                           | 8                           | -                      | MHz  |

Note 1: Not included in the shipping inspection items.

### 10.2. Characteristics of RXD and TXD

#### Table 10.2Characteristics of RXD and TXD

| (V <sub>VIO</sub> = 4.5 to 5.5 V, VBAT = 7 to 18 V, Ta = -40 to 125 °C unless otherwise specified) |                      |                                                                    |                             |                             |                            |      |  |  |  |

|----------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------|-----------------------------|-----------------------------|----------------------------|------|--|--|--|

| Characteristics                                                                                    | Symbol               | Test Conditions                                                    | Min                         | Тур.                        | Max                        | Unit |  |  |  |

| RXD                                                                                                |                      |                                                                    |                             |                             |                            |      |  |  |  |

| Output High voltage                                                                                | V <sub>OH_RXD</sub>  | Load Current =-1 mA<br>Function operation period supported as well | V <sub>VIO</sub> -0.5       | -                           | -                          | V    |  |  |  |

| Output Low voltage                                                                                 | Vol_rxd              | Load Current = 1 mA<br>Function operation period supported as well | -                           | -                           | 0.5                        | V    |  |  |  |

| TXD                                                                                                | ·                    |                                                                    |                             |                             |                            |      |  |  |  |

| Input High voltage                                                                                 | VIH_TXD              | Function operation period supported as well                        | 0.8 × V <sub>VIO</sub>      | -                           | -                          | V    |  |  |  |

| Input Low voltage                                                                                  | VIL_TXD              | Function operation period supported as well                        | -                           | -                           | $0.2 \times V_{VIO}$       | V    |  |  |  |

| Hysteresis                                                                                         | V <sub>HYS_TXD</sub> |                                                                    | 0.032<br>× V <sub>VIO</sub> | 0.065<br>× V <sub>VIO</sub> | 0.13<br>× V <sub>VIO</sub> | V    |  |  |  |

| Pull-up resistance                                                                                 | R <sub>TXL</sub>     | TXD = 0 V                                                          | 50                          | 100                         | 200                        | kΩ   |  |  |  |

| Loop characteristics                                                                               | Loop characteristics |                                                                    |                             |                             |                            |      |  |  |  |

| Loop delay time during function operation                                                          | TLOOP_FUNC_PDF       | Time between TXD = L input and RXD = L output                      | -                           | -                           | 100                        | μs   |  |  |  |

## **10.3. BUS (DC Characteristics)**

#### Table 10.3BUS (DC Characteristics)

$(V_{VIO} = 4.5 \text{ to } 5.5 \text{ V}, \text{ VBAT} = 7 \text{ to } 18 \text{ V}, \text{ Ta} = -40 \text{ to } 125 \text{ }^{\circ}\text{C} \text{ unless otherwise specified})$

| Characteristics                            | Symbol                      | $\frac{10}{18} \sqrt{18} \sqrt{12} = -40 \ 10 \ 125 \sqrt{125}$     | Min                         | Тур.                      | Max                         | Unit |

|--------------------------------------------|-----------------------------|---------------------------------------------------------------------|-----------------------------|---------------------------|-----------------------------|------|

|                                            |                             | $V_{TXD} = 0 V, R_L(Note 1) = 500 \Omega$ $V_{BAT} = 7.3 V$         | -                           | -                         | 1.2                         | V    |

| BUS dominant output voltage                | $V_{\text{OL}\_\text{BUS}}$ | $V_{TxD} = 0 V, R_L = 500 \Omega$<br>7.3 V $\leq V_{BAT} \leq 10 V$ | -                           | -                         | 0.2<br>× V <sub>BAT</sub>   | V    |

|                                            |                             | $V_{TxD} = 0 V, R_L = 500 \Omega$<br>10 V $\leq V_{BAT} \leq 18 V$  | -                           | -                         | 2.0                         | V    |

| BUS recessive output voltage               | Voh_bus                     | TXD = H                                                             | 0.8<br>× V <sub>BAT</sub>   | -                         | $V_{\text{BAT}}$            | V    |

| Current when BUS is short-circuited (DC)   | IBUS_LIM                    | V <sub>BUS</sub> = V <sub>BAT</sub> = 18 V                          | 40                          | -                         | 200                         | mA   |

| Leak current when BUS dominant             | BUS_PAS_dom                 | $V_{BUS} = 0 V$ , $V_{BAT} = 12 V$                                  | -1                          | -                         | -                           | mA   |

| Leak current when BUS recessive            | BUS_PAS_rec                 | 8 V < VBAT < 18 V, 8 V < VBUS <<br>18 V, VBAT < VBUS                | -                           | -                         | 20                          | μA   |

| Leak current when ground disconnected      | I <sub>BUS_NO_GND</sub>     | $\begin{array}{llllllllllllllllllllllllllllllllllll$                | -1                          | -                         | 1                           | mA   |

| Leak current when power is off             | IBUS_NO_BAT                 | $V_{BAT} = 0 \ V_{,} \ 0 \ V < V_{BUS} < 18 \ V$                    | -                           | -                         | 100                         | μA   |

| Dominant threshold voltage when receiving  | $V_{BUSdom}$                | Voltage by which receiving node judged as L level                   | -                           | -                         | 0.423<br>× V <sub>BAT</sub> | V    |

| Recessive threshold voltage when receiving | V <sub>BUSrec</sub>         | Voltage by which receiving node judged as H level                   | 0.556<br>× V <sub>BAT</sub> | -                         | -                           | V    |

| Center voltage when receiving              | VBUSCNT                     | -                                                                   | 0.475<br>× V <sub>BAT</sub> | 0.5<br>× V <sub>BAT</sub> | 0.525<br>× V <sub>BAT</sub> | V    |

| Hysteresis                                 | $V_{BUShys}$                | -                                                                   | -                           | -                         | 0.133<br>× V <sub>BAT</sub> | V    |

Note1: RL is a pull-up resistance between BAT and BUS externally connected to the IC.

### 10.4. BUS (AC Characteristics)

#### Table 10.4 BUS (AC Characteristics)

|  | $(V_{VIO} = 4.5 \text{ to } 5.5 \text{ V}, V_{BAT} = 7 \text{ to } 18 \text{ V}, \text{ Ta} = -40 \text{ to } 125 \text{ °C}, 1 \text{ Tbit} = 50 \ \mu\text{s}$ unless otherwise specific |

|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristics                                                        | Symbol                                | Test conditions                                                                                                                                           | Min  | Тур. | Max  | Unit |

|------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Dominant detection time<br>when receiving wake-up<br>(commander node)  | Trx_wakeup_commander                  | TH <sub>rx_dom</sub> = 0.423 × V <sub>BAT</sub><br>(Figure 7.2.3.2.)                                                                                      | 30   | 90   | 150  | μs   |

| Shutoff pulse width at wakeup (commander node)                         | Trx_wakeup_commander                  | All pulses with dominant 30 µs or less are shut off (Note 1).                                                                                             | -    | -    | 30   | μs   |

| Pass-through (recognized)<br>pulse width at wakeup<br>(commander node) | Trx_wakeup_commander                  | All pulses with dominant 100 to<br>2600 µs are passed through<br>(recognized) (Note 1).                                                                   | 100  | 200  | 2600 | μs   |

| Rise delay when receiving wakeup (commander node)                      | Trx_wakeup_commander_pdr              | $TH_{rx\_rec} = 0.6 \times V_{BAT}$ (Figure 7.2.3.2.)                                                                                                     | 30   | 90   | 150  | μs   |

| Dominant detection time<br>when receiving wake-up<br>(responder node)  | Trx_wakeup_responder                  | TH <sub>rx_dom</sub> = 0.423 × V <sub>BAT</sub><br>(Figure 7.2.2.2.)                                                                                      | 0.5  | 2.75 | 5    | μs   |

| Shut-out pulse width at wakeup (responder node)                        | Trx_wakeup_responder                  | All pulses with dominant 0.5<br>µs or less are shut out<br>(Note 1).                                                                                      | -    | -    | 0.5  | μs   |

| Pass-through (recognized)<br>pulse width at wakeup<br>(responder node) | Trx_wakeup_responder                  | All pulses with dominant<br>3~2600 µs are passed through<br>(recognized) (Note 1).                                                                        | 3    | 6    | 2600 | μs   |

| Rise delay when receiving wakeup (responder node)                      | Trx_wakeup_responder_pdr              | $TH_{rx\_rec} = 0.6 \times V_{BAT}$ (Figure 7.2.2.2.)                                                                                                     | 0.5  | 2.75 | 5    | μs   |

| Fall delay when transmitting<br>wakeup (responder node)<br>TXD⇒BUS     | Ttx_wakeup_responder_pdf              | $C_{BUS}$ = 10 nF, $R_{BUS}$ = 500 $\Omega$                                                                                                               | -    | -    | 195  | μs   |

| Rise delay when transmitting<br>wake-up (responder node)<br>TXD⇒BUS    | T <sub>tx_wakeup_</sub> responder_pdr | $C_{BUS}$ = 10 nF, $R_{BUS}$ = 500 $\Omega$                                                                                                               | -    | -    | 26.6 | μs   |

| Rise delay of wakeup<br>internal signal (responder<br>node)            | Ttx_wakeup_mode_on                    | Pulses of min. or less are ignored.                                                                                                                       | 3    | -    | 10   | μs   |

| Transition time to normal mode                                         | T <sub>norm</sub>                     | -                                                                                                                                                         | -    | -    | 1    | ms   |

| Transition time to sleep mode                                          | T <sub>sleep</sub>                    | -                                                                                                                                                         | -    | -    | 1    | ms   |

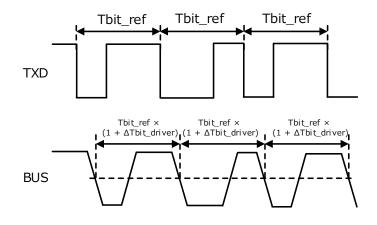

| Difference in bit widths<br>(Figure 10.4.1)                            | $\Delta T_{bit\_driver}$              | Difference from Tbit_ref, bit<br>width of reference<br>communication speed, TH =<br>50 %                                                                  | -0.5 | -    | +0.5 | %    |

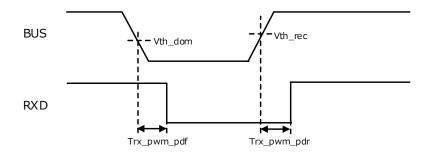

| Fall delay when receiving BUS (Figure 10.4.2) BUS $\Rightarrow$ RXD    | Trx_pwm_pdf                           | $\begin{array}{l} C_{\text{BUS}} = 1 \text{ nF, } R_{\text{BUS}} = 1 \text{ k}\Omega \\ V_{\text{th}\_dom} = 0.423 \times V_{\text{BAT}} \end{array}$     | -    | -    | 2.1  | μs   |

| Rise delay when receiving BUS (Figure 10.4.2) BUS $\Rightarrow$ RXD    | Trx_pwm_pdr                           | $\begin{array}{l} C_{\text{BUS}} = 1 \text{ nF},  R_{\text{BUS}} = 1  k\Omega \\ V_{\text{th}\_\text{rec}} = 0.556 \text{ x } V_{\text{BAT}} \end{array}$ | -    | -    | 2.1  | μs   |

| RXD delay time difference<br>when receiving BUS<br>(Figure 10.4.2)     | Trx_sym                               | (T <sub>rx_sym</sub> = T <sub>rx_pwm_pdf</sub> -T <sub>rx</sub><br>_ <sub>pwm_pdr</sub> )<br>C <sub>BUS</sub> = 1 nF, R <sub>BUS</sub> = 1 kΩ             | -2   | -    | 2    | μs   |

Note 1: Not included in shipping inspection items.

## TB9032FNG

| ( $V_{VIO} = 4.5$ to 5.5 V, $V_{BAT} = 7$ to 18 V, Ta = -40 to 125 °C, 1 Tbit = 50 µs unless otherwise specified) |                               |                                                                                                                                                                                                                          |     |      |      |      |  |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|--|

| Characteristics                                                                                                   | Symbol                        | Test conditions                                                                                                                                                                                                          | Min | Тур. | Max  | Unit |  |

| Slope in BUS transmission<br>(commander node) (Figure<br>7.2.4.1)                                                 | T <sub>tx_pwm_slope_clk</sub> |                                                                                                                                                                                                                          | -   | -    | 8    | μs   |  |

| Fall delay in BUS transmission<br>(commander node) TXD⇒<br>BUS (Figure 7.2.4.1)                                   | Ttx_pwm_pdf_clk               | $\begin{array}{l} C_{\text{BUS}} = 10 \text{ nF}, \text{ R}_{\text{BUS}} = 500 \ \Omega \\ TH_{\text{tx\_dom}} = 0.3 \text{ x } V_{\text{BAT}} \end{array}$                                                              | -   | -    | 16.9 | μs   |  |

| Rise delay in BUS<br>transmission TXD⇒BUS<br>(Figure 7.2.4.1, Figure 7.2.4.2)                                     | Ttx_pwm_pdr                   | $\begin{array}{l} C_{\text{BUS}} = 10 \text{ nF}, \text{ R}_{\text{BUS}} = 500 \ \Omega \\ TH_{\text{tx\_rec}} = 0.7 \text{ x } \text{ V}_{\text{BAT}} \end{array}$                                                      | -   | -    | 16.9 | μs   |  |

| Fall delay in BUS transmission<br>(responder node) TXD⇒BUS<br>(Figure 7.2.4.2)                                    | T <sub>tx_pwm_pdf</sub>       | $\begin{array}{l} C_{\text{BUS}} = 10 \text{ nF}, \text{ R}_{\text{BUS}} = 500 \ \Omega \\ TH_{\text{tx\_dom}} = 0.3 \text{ x } V_{\text{BAT}} \end{array}$                                                              | -   | -    | 2.9  | μs   |  |

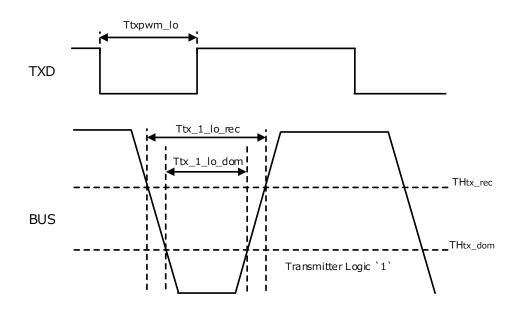

| BUS dominant time for Logic 1<br>(Figure 10.4.3)                                                                  | Ttx_1_lo_dom                  | $\begin{array}{l} C_{\text{BUS}} = 1 \text{ nF, } R_{\text{BUS}} = 1 \text{ k}\Omega \\ TH_{\text{tx\_dom}} = 0.3 \times V_{\text{BAT}} \\ T\text{txpwm\_lo} = 13.75 \ \mu\text{s} \end{array}$                          | 5.5 | -    | -    | μs   |  |

| BUS recessive time for Logic 1<br>(Figure 10.4.3)                                                                 | T <sub>tx_1_lo_rec</sub>      | $\begin{array}{l} C_{\text{BUS}} = 10 \text{ nF},  \text{R}_{\text{BUS}} = 500 \ \Omega \\ \text{TH}_{\text{tx\_rec}} = 0.7 \ \textbf{x} \ \text{V}_{\text{BAT}} \\ \text{Ttxpwm\_lo} = 11.25 \ \mu\text{s} \end{array}$ | -   | -    | 22.5 | μs   |  |

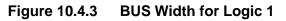

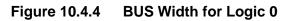

| BUS dominant time for Logic 0<br>(Figure 10.4.4)                                                                  | Ttx_0_lo_dom                  | $\begin{array}{l} C_{\text{BUS}} = 1 \ \text{nF}, \ R_{\text{BUS}} = 1 \ \text{k}\Omega \\ TH_{\text{tx\_dom}} = 0.3 \times V_{\text{BAT}} \\ Ttxpwm\_lo = 16.75 \ \mu\text{s} \end{array}$                              | 8.5 | -    | -    | μs   |  |

| BUS dominant time difference between Logic 1 and Logic 0                                                          | $T_{TX\_dif}$                 | $\begin{array}{l} T_{tx\_0\_lo\_dom} - T_{tx\_1\_lo\_dom} \\ C_{BUS} = 10 nF, \ R_{BUS} = 500 \ \Omega \\ Ttxpwm\_lo = 12.5 \ \mu s \ (Logic \ 1) \\ Ttxpwm\_lo = 35 \ \mu s \ (Logic \ 0) \end{array}$                  | 3   | -    | -    | μs   |  |

Figure 10.4.1 Difference in Bit Widths

Figure 10.4.2 Delay Time when Receiving BUS

Preliminary

TB9032FNG

#### 10.5. Others

#### Table 10.5Other Characteristics

(VBAT = 7 to 18 V, Ta = -40 to 125 °C unless otherwise specified)

| Characteristics                                 | Symbol           | Test conditions                                                   | Min | Тур. | Max  | Unit |

|-------------------------------------------------|------------------|-------------------------------------------------------------------|-----|------|------|------|

| Others                                          |                  |                                                                   |     |      |      |      |

| BUS external resistance<br>(commander node)     | R∟               | External resistance between<br>BAT and BUS of a commander<br>node | 900 | 1000 | 1100 | Ω    |

| BUS internal resistance (responder node)        | Rresponder       | Internal specification                                            | 20  | 30   | 60   | kΩ   |

| BUS external diode voltage drop                 | V <sub>F</sub>   | External diode between BAT and BUS                                | 0.4 | 0.7  | 1.0  | V    |

| MS pin external resistance                      | Rмs              | -                                                                 | -   | 10   | -    | kΩ   |

| Allowable capacitance of<br>commander node side |                  | -                                                                 | -   | 220  | -    | pF   |

| Allowable capacitance of<br>responder side      | Cresponder       | -                                                                 | -   | 220  | 250  | pF   |

| BUS allowable capacitance 1                     | C <sub>BUS</sub> | $R_L = 1 \ k\Omega$                                               | -   | -    | 1    | nF   |

| BUS allowable capacitance 2                     | CBUS             | R <sub>L</sub> = 660 Ω                                            | -   | -    | 4    | nF   |

| BUS allowable capacitance 3                     | CBUS             | R <sub>L</sub> = 500 Ω                                            | -   | -    | 10   | nF   |

| Dominant timeout                                | Тртс             | -                                                                 | 2.6 | 6    | 15   | ms   |

| Overheat detection<br>temperature (TSD)         | T <sub>TSD</sub> | -                                                                 | 150 | 175  | 200  | °C   |

| Hysteresis after overheat detection reset       | T <sub>HYS</sub> | -                                                                 | -   | 10   | -    | °C   |

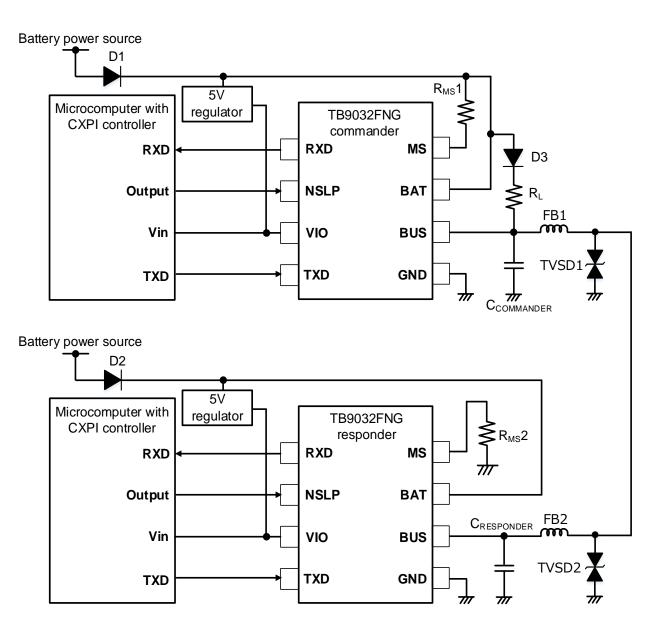

# **11. APPLICATION CIRCUIT EXAMPLE**

## 11.1. Application Circuit Diagram

The above is just one example of application circuits, therefore, it can't be guaranteed as a design for a mass-produced product.

External parts are examples. Other external part other than those shown in the above figure can also be chosen."

Preliminary

#### 11.2. Reference value for parts

| Symbol            | Reference part and<br>reference value | Remarks             |  |

|-------------------|---------------------------------------|---------------------|--|

| D1                | CRG09A                                | -                   |  |

| D2                | CRG09A                                | -                   |  |

| D3                | LL4148 V <sub>F</sub> ≤ 1.0V          | Refer to Table 10.5 |  |

| R <sub>MS</sub> 1 | 10kΩ                                  | Refer to Table 10.5 |  |

| R <sub>MS</sub> 2 | 10kΩ                                  | Refer to Table 10.5 |  |

| R∟                | 1kΩ                                   | Refer to Table 10.5 |  |

| CCOMMANDER        | 220pF                                 | Refer to Table 10.5 |  |

|                   | 220pF                                 | Refer to Table 10.5 |  |

| FB1               | BLM18AG601SH1                         | -                   |  |

| FB2               | BLM18AG601SH1                         | -                   |  |

| TVSD1             | DF2B29FU                              | -                   |  |

| TVSD2             | DF2B29FU                              | -                   |  |

#### Table 11.2Reference value for parts

External parts values are examples. External part values other than those listed above can also be chosen.

# **12. NOTES ON CONTENTS**

### 12.1. Notes on Contents

- (1) Some of the functional blocks, circuits, or constants in the block diagrams may be omitted or simplified for explanatory purposes.

- (2) The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

- (3) Timing charts may be simplified or partially omitted for explanatory purposes.

- (4) The application circuits shown in this document are provided for reference purposes only. Components in the application circuit examples are not guaranteed to prevent malfunction or failure in the application circuits. Thorough evaluation of the application is required in selecting your components, especially at mass production design stage. Toshiba does not grant any license to any industrial property rights by providing these examples of application circuits.

- (5) Components in the test circuits and test conditions are used only to obtain and confirm device characteristics. They are not guaranteed to prevent malfunction or failure in application equipment.

# Preliminary

TB9032FNG

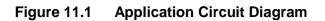

(Unit: mm)

# **13. OUTLINE DRAWING**

## **13.1. External Dimensions**

### P-SOP8-0405-1.27-002

Mass: 0.08 g (typ.)

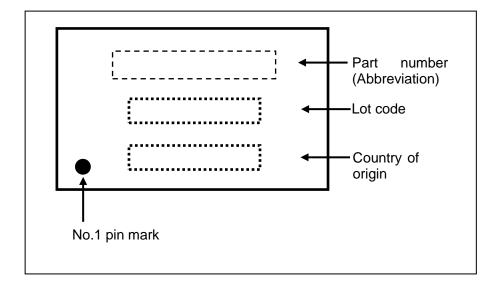

#### 13.2. Labeling Diagram

Preliminary

TB9032FNG

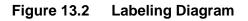

### 13.3. Land Pattern Dimensions (for reference only)

Unit : mm

#### Notes

- All linear dimensions are given in millimeters unless otherwise specified.

- This drawing is based on JEITA ET-7501 Level3 and should be treated as a reference only.

- TOSHIBA is not responsible for any incorrect or incomplete drawings and information.

- You are solely responsible for all aspects of your own land pattern, including but not limited to soldering processes.

- The drawing shown may not accurately represent the actual shape or dimensions.

- Before creating and producing designs and using, customers must also refer to and comply with the latest versions of all relevant TOSHIBA information and the instructions for the application that Product will be used with or for.

#### Figure 13. 3 Land Pattern Dimensions (for reference only)

# 14. IC USAGE CONSIDERATIONS

### 14.1. Notes on Handling of ICs

(1) The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even momentarily.

Do not exceed any of these ratings.

Exceeding rating(s) may cause device breakdown, damage, or deterioration, and may result in injury by explosion or combustion. In your design, make sure that absolute maximum ratings are not exceeded in any operating conditions. Use the product within described operating ranges.

- (2) Use an appropriate power supply fuse to ensure that a large current does not continuously flow in case of over-current and/or IC failure. The IC may fully break down when used under conditions exceeding absolute maximum ratings, when wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and breakdown can lead smoke or combustion. To minimize effects of the flow of a large current in case of breakdown, appropriate settings, such as fuse capacity, fusing time and insertion circuit location, are required.

- (3) Do not insert devices in the wrong orientation or incorrectly. Ensure that positive and negative pins of power supplies are connected properly. Otherwise, current or power consumption may exceed the absolute maximum rating and exceeding the rating(s) may cause the device breakdown, damage, or deterioration, and may result in injury by explosion or combustion. Also, do not ever use any device that was applied the current with inserting in the wrong orientation or incorrectly.

### 14.2. Reminders on Handling of ICs

- (1) Thermal shutdown circuits do not necessarily protect ICs under all circumstances. If thermal shutdown circuits operate against over temperature, clear the heat generation status immediately. Depending on the method of use and usage conditions, exceeding absolute maximum ratings can cause the thermal shutdown circuit to not operate properly or IC breakdown before operation. Thermal shutdown circuits temporarily detect or avoid abnormality and are not guaranteed to prevent ICs from breaking down. In addition, when the IC is not working within the guaranteed operating ranges, such functions may not work, leading to IC breakdown.

- (2) Design the board so that heat is appropriately radiated, not to exceed specified junction temperature (Tj) at any time or condition. ICs generate heat even during normal use. An inadequate IC heat radiation design can lead to decrease in IC life, deterioration of IC characteristics or IC breakdown. In addition, design the device taking into consideration the effect of IC heat radiation on components used around the IC.

## **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's

written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative or contact us via our website.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please

use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including

without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT

OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

# **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

https://toshiba.semicon-storage.com/