# Full-Bridge DC-DC Power Supply Basic Simulation Circuit Reference Guide

RD154-RGUIDE-01

**TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

# Table of Contents

| 1.  | Introduction                              | 3    |

|-----|-------------------------------------------|------|

| 2.  | Outline of Full-Bridge DC-DC Power Supply | 6    |

| 2.1 | Power Supply Specifications               | 6    |

| 2.2 | Circuit Configuration                     | 7    |

| 3.  | Simulation Result                         | 10   |

| 4.  | Product Overview                          | 17   |

| 4.1 | TPN11006PL                                | . 17 |

| 4.2 | TPH1R204PL                                | . 17 |

| 5.  | Using the Simulation Circuit              | 18   |

# 1. Introduction

Most electrical equipment such as including information and telecommunications equipment and home appliances operates with DC voltage.

Therefore, it is not possible to operate directly with commercial power supplied by AC voltage so it is necessary to convert from AC voltage to DC voltage.

Conversion from AC voltage to DC voltage is performed by AC-DC power supply. Depending on the power supply specifications of each load in the equipment, the DC voltage supplied by AC-DC power supply must be further converted to a DC voltage corresponding to that specification.

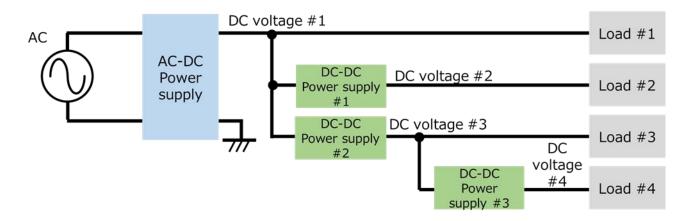

Fig. 1.1 shows an example of the configuration of the power supply line in the equipment. There are several power supply lines depending on the load, and the load may be connected directly to the output voltage supplied from AC-DC power supply, or the output voltage may be further converted to a different DC voltage by DC-DC power supply for connection. DC-DC power supply converts the DC voltage to a different DC voltage in this way.

Fig. 1.1 Example of the Configulation of the power supply Line

There are two types of conversion methods from DC voltage to DC voltage: the series regulating method and the switch regulating method (hereinafter referred to as "series-base" or "switch-base").

This document deals with switch-base, which are the mainstream in DC-DC power supplies. The switch-base regulates the on/off of the switching MOSFET to generate the desired voltage. The control circuit is more complicated than the series-base, but in general, the loss can be reduced than the series-base.

There are two ways of switch-base: one is isolated DC-DC power supply, in which the input side and the output side are isolated by a transformer, and the other is non-isolated DC-DC power supply, in which the input side and the output side are not isolated. This document handles isolated DC-DC power supplies.

The isolated DC-DC power supply switches the input DC voltage at frequencies of several tens to several hundred kHz with a switching MOSFET, transmits the power to the secondary side through a transformer, rectifies, and smoothes to output the DC voltage. The final stage DC voltage is controlled by adjusting the switching MOSFET on/off period.

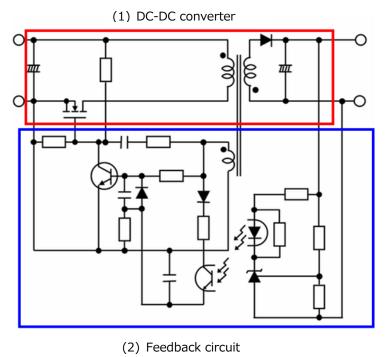

Fig. 1.2 shows examples of circuit blocks for isolated switch-base DC-DC power supply. It consists of two blocks: (1) DC-DC converters and (2) feedback circuits, as shown in the illustration.

The functions of each block are shown below.

Fig. 1.2 Circuit Block for Isolated Switch-base DC-DC Power Supply

- (1) DC-DC converters Converts the input DC voltage to any DC voltage.

- (2) Feedback circuit

The switching MOSFET is controlled so that the output voltage becomes a desired value.

There are a variety of topologies for DC-DC converters. Table 1.1 shows typical topologies and characteristics of DC-DC converters.

Circuitry of DC-DC converter section Power level Disadvantages Advantages Reduction in efficiency Small part count **Flyback** < 200 W at high power Large transformer Higher efficiency · Transformer reset Forward 50 W~500 W than a flyback circuit required circuit Active clamp Higher Efficiency · There are many parts 50 W~500 W forward than a forward · Be difficult to control · Specially designed High efficiency Half-bridge 100 W~1 kW transformer is required. · Low noise · Be difficult to control Resonant High efficiency · Specially designed half bridge 100 W∼1 kW than a half bridge transformer is required. 4 (LLC resonance) · Low noise · Be difficult to control High efficiency · Capable of · There are many parts Full-bridge > 200 W · Be difficult to control increasing the

Table 1.1 Typical Topologies and Characteristics of DC-DC Converters

Regarding the basic operation of the full-bridge method, we are distributing it on our web. Please also refer to the video below.

The Video of the full-bridge DC-DC converter are shown here  $\rightarrow$

Click Here

power capacity

The full-bridge method described in this document is widely used in power supplies requiring high efficiency and high power density, because the power supply input voltage applies the primary side of the transformer directly due to cross coupled two switching elements of four switching elements located on the primary side of the transformer turn on/off at the same timing.

Toshiba provide basic simulation circuits (RD154-SPICE-01) on our web to understand full-bridge DC-DC converter circuit operation in switch-base DC-DC power supplies.

This document provides an overview of this basic simulation circuit and explains how to use it. The Cadence's Capture and PSpice <sup>®</sup> A/D tools are required to operate the simulator circuits from OrCAD. Simulation circuits and documentation have been prepared in accordance with OrCAD 17.2.

# 2. Outline of Full-Bridge DC-DC Power Supply

The basic simulation circuit (RD154-SPICE-01) is a 200 W full-bridge DC-DC power supply.

# 2.1 Power Supply Specifications

The full-bridge DC-DC power supply specifications described in this document are as follows:

- Input voltage (V<sub>in</sub>): 24 V

- Output voltage (Vout): 5 V

- Output current ( $I_{out}$ ) : 0 $\sim$ 40 A

- Secondary MOSFET operating frequency: 65 kHz (twice the primary operating frequency)

- Winding ratio: n1:n2:n3= 5:2:2

- Allowable ripple current width on the secondary side ( $\Delta I_{ripple}$ ): 20 %

# 2.2 Circuit Configuration

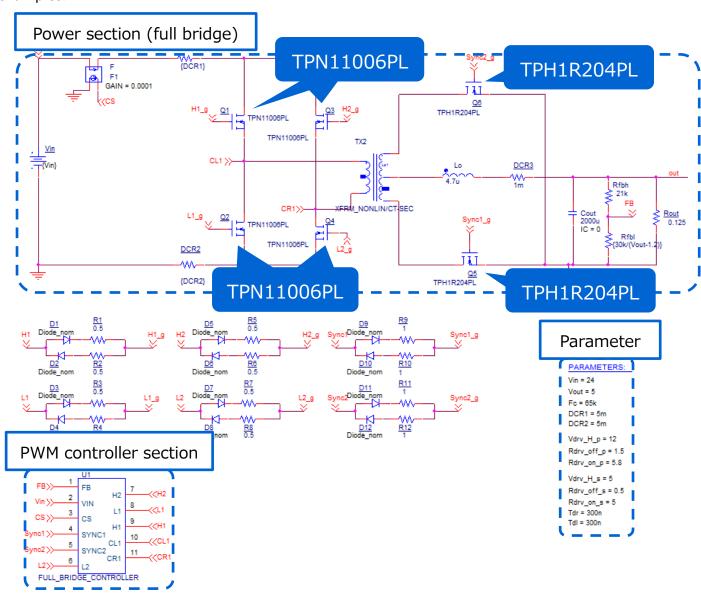

Fig. 2.1 shows the simulation circuit for OrCAD<sup>®</sup>. This is a full-bridge type DC-DC converter power supply, which mainly consists of a power section (full-bridge) and a PWM controller section. The secondary side of the power section is a synchronous rectification circuit using MOSFETs. The PWM controller section is a general-purpose controller with a built-in MOSFET gate driver, which is provided to realize PWM circuit. The switching MOSFETs are "TPN11006PL" and "TPH1R204PL" as examples.

Fig. 2.1 Simulation circuit of 200 W Full-Bridge (DC-DC Converter) Power Supply

# **Selection of primary side MOSFET**

Primary side MOSFET(TPN11006PL: V<sub>DSS</sub>=60 V, I<sub>D</sub>=26 A) is selected from the following viewpoints.

# (1) Breakdown-voltage

The voltage applied to the MOSFET at static state is the input voltage (=24 V). Select a MOSFET with a breakdown-voltage of 60 V or higher, considerating the surge voltage at the time of switching and other factors.

# (2) Current rating

When the input current is maximum, it is at the maximum output power. If the conversion efficiency at the maximum output power (=200W) is 90%, the maximum average input current is 9.3 A. Select a MOSFET with a current rating of 19 A or more.

Here, we selected a 26 A current MOSFET from our product lineup.

# **Selection of secondary side MOSFET**

Secondary side MOSFET(TPH1R204PL: $V_{DSS}$ =40 V,  $I_{D}$ =150 A) is selected from the following viewpoints.

# (1) Breakdown-voltage

Since the winding ratio is 5:2, the voltage between the middle point and both ends of the secondary winding at static state is 9.6 V, which is 2/5 of the input voltage, and 19.2 V, which is twice the voltage, is applied to each MOSFET on the secondary side.

A surge voltage is generated when the transformer current is switched. Select a MOSFET with a breakdown-voltage of 40 V or more.

# (2) Current rating

When the output current is maximum, it is at the maximum output power. The maximum output current of 40 A at maximum output power (=200 W) is shared by MOSFET of the two current paths on the secondary side, a current of 20 A flows per path. Therefore, a MOSFET with a current rating of 40 A or more is required. In addition, select a MOSFET with as low an on-resistance as possible with emphasis on suppressing conduction loss.

# **Selection of output inductor**

This section explains how to select the output inductor on the secondary side. The inductance value of the output inductor in this simulation circuit can be calculated using the following items, which are power supply specifications.

- Input voltage: V<sub>in</sub> (V) = 24

- Transformer winding ratio:  $n_2/n_1=n_3/n_1=2/5$

- · Output Voltage: Vout (V) = 5

- Switching frequency: F<sub>c</sub> (Hz) = 65k

- Max. output current:  $I_{out\ max}(A) = 40$

- Allowable ripple current range:  $\Delta I_{ripple}$  (%) = 20

The inductance value (L<sub>o</sub>) of the output inductor is calculated by the following formula.

$$L_{o} = \frac{\left(\frac{n_{2}}{n_{1}} \times V_{in} - V_{out}\right) \times V_{out}}{\frac{n_{2}}{n_{1}} \times V_{in} \times F_{c} \times I_{out\_max} \times \Delta I_{ripple} \times 0.01}$$

The inductance value (Lo) of the output inductor is calculated as 4.61 µH from the above equation, and 4.7 µH is selected as the setting value from the power supply specifications of this model. In the actual design, the inductance value of the inductor changes due to the DC superposition characteristic. Select a component that can secure the calculated value in a state where the inductance value is lowered due to the DC superposition characteristic.

# 3. Simulation Result

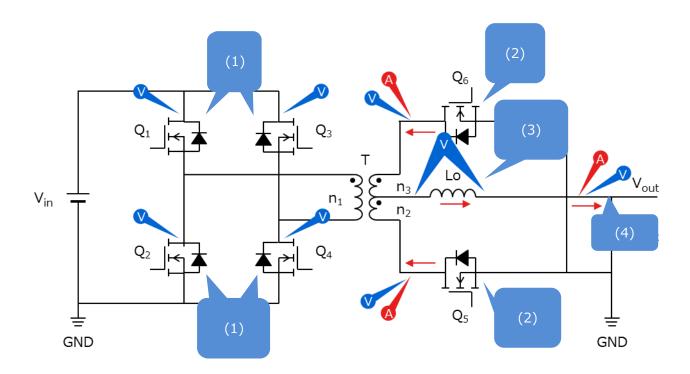

The operation simulation waveforms of each part in the simulation circuit are shown by the points in Fig. 3.1 ((1) to (4)).

- (1) Full-bridge basic operation ("Primary MOSFET Drain-Source Voltage")

- (2) Secondary-side synchronous rectification operation ("Secondary-side MOSFET drain/source voltage/current")

- (3) Output inductor voltage and current at both ends

- (4) "Output voltage and current" as a power supply

When actually using the circuit model, it is possible to display the waveform at any point other than those shown in Fig. 3.1. The waveform display method is described in Chapter 5.

Fig. 3.1 Simulation Waveform Measurement Point List

# (1) Full-bridge basic operation

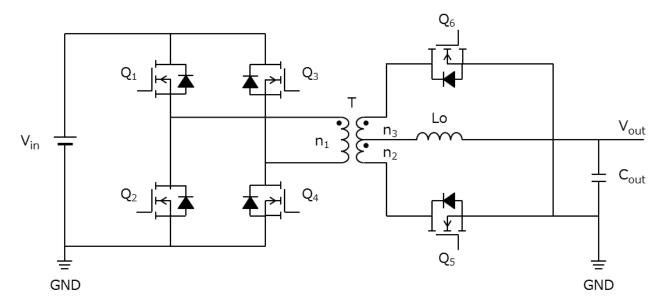

The basic operation of the full-bridge method is described in Fig. 3.2, which shows the full-bridge circuit.

$Q_1 \sim Q_4$ : Primary MOSFET  $Q_5, Q_6$ : Secondary MOSFET

L<sub>0</sub>: Output inductor

Fig. 3.2 Full-Bridge Circuit

In the full-bridge method,  $Q_1$  and  $Q_4$ ,  $Q_3$  and  $Q_2$  are alternately turned on and off in pairs, respectively, and the output voltage is controlled using PWM (pulse-width modulation) control.

For the output-voltage Vout, it can be calculated by:

$$V_{out} = 2 \times \frac{n_2}{n_1} \times V_{in} \times \frac{T_{on}}{T}$$

T: Period of the primary side

Ton: On-time

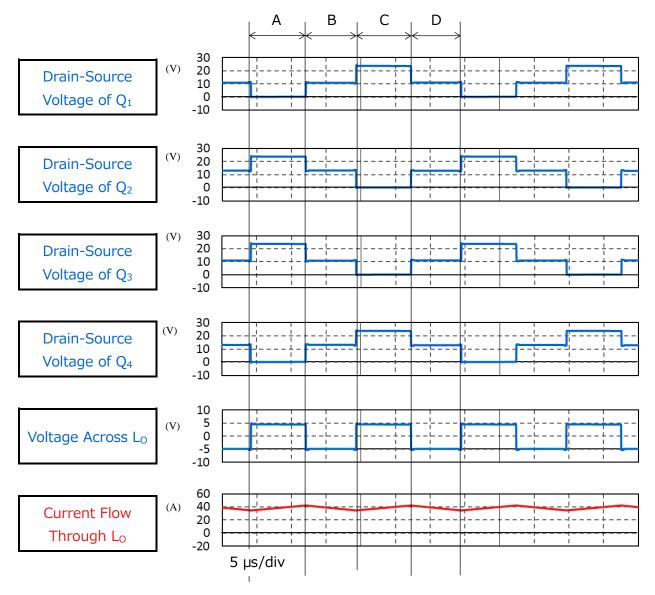

# A. $Q_1$ and $Q_4$ are on, $Q_3$ and $Q_2$ are off

This is the period during power is transferred from the primary side to the secondary side. The primary winding voltage at this time is the input voltage ( $V_{in}$ ). For the secondary winding, the voltages corresponding to the winding ratios are given with the polarity symbol of the  $n_2$  as positive.

$$\frac{n_2}{n_1} \times V_{in}$$

The voltage is applied to the  $L_0$  via the  $Q_5$ ,

$$\Delta i_{Lo(Q1,Q4\_on)} = \frac{1}{L_o} \left( \frac{n_2}{n_1} \times V_{in} - V_{out} \right) \times T_{on}$$

The current determined by the equation increases linearly to charge the Cout and provide the output current Iout. At this time, magnetic energy is stored in the Lo.

# B. $Q_1$ , $Q_2$ , $Q_3$ and $Q_4$ are off

The energy stored in the  $L_0$  flows into the  $Q_5$  and  $Q_6$ . To the  $L_0$  at this time, the current decrease lineally as follows.

$$\Delta i_{Lo(all_{off})} = \frac{-V_{out}}{L_O} \times \left(\frac{T}{2} - T_{on}\right)$$

# C. $Q_1$ and $Q_4$ are off, $Q_2$ and $Q_3$ are on

This is the period during power is transferred from the primary side to the secondary side. During this period, the primary winding voltage becomes -Vin. For the secondary winding, the voltage corresponding to the winding ratio is applied with the polarity symbol side of the n₃ taken as a minus.

$$\frac{n_3}{n_1} \times V_{in}$$

This voltage is applied to the L<sub>0</sub> via the Q<sub>B</sub>, the current flows as follow:

$$\Delta i_{Lo(Q3,Q2\_on)} = \frac{1}{L_o} \times \left(\frac{n_3}{n_1} \times V_{in} - V_{out}\right) \times T_{on}$$

# D. $Q_1$ , $Q_2$ , $Q_3$ and $Q_4$ are off

The energy stored in the  $L_0$  flows into  $Q_5$  and  $Q_6$ , the current flows as follow:

$$\Delta i_{Lo(all_{off})} = \frac{-V_{out}}{L_o} \times \left(\frac{T}{2} - T_{on}\right)$$

Fig. 3.3 shows the primary-side MOSFET drain-source voltage and output inductor voltage/current waveforms.

© 2020 12 / 23 Toshiba Electronic Devices & Storage Corporation

Fig. 3.3 Primary MOSFET Drain-Source Voltage/Current, Output Inductor Voltage/Current

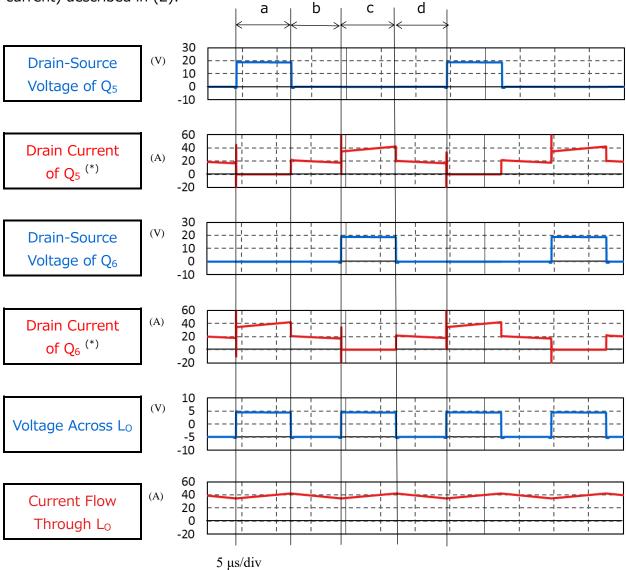

# (2) Secondary side synchronous rectification operation

This simulation model uses a synchronous rectifier circuit that uses MOSFET instead of diodes for the secondary rectifier. Generally, the conduction loss due to the on-resistance of the MOSFET is smaller than that of the diode so the synchronous rectifier circuit can reduce the conduction loss. The larger output current, the greater loss reduction effect of the synchronous rectifier circuit, and is often used in applications where high efficiency and large capacity are required.

The operation of the secondary MOSFET in the respective periods are as follows.

a. Q<sub>5</sub> is off, Q<sub>6</sub> is on

Voltage corresponding to the winding ratio with the polarity symbol side of the secondary side winding  $n_2$  as plus voltage,

$$\frac{n_2}{n_1} \times V_{in}$$

is applied and current flows through  $Q_5$  to  $L_0$ .

b. Q<sub>A</sub> is on, Q<sub>B</sub> is on

Electric power stored in the L<sub>0</sub> recirculates through the Q<sub>5</sub> and Q<sub>6</sub>.

c.  $Q_5$  is on,  $Q_6$  is off

Voltage corresponding to the winding ratio with the polarity symbol side of the secondary side winding  $n_3$  as a minus voltage

$$\frac{n_3}{n_1} \times V_{in}$$

is applied and current flows through Q<sub>6</sub> to L<sub>0</sub>.

d.  $Q_5$  is on,  $Q_6$  is on

Electric power stored in the  $L_0$  recirculates through the  $Q_5$  and  $Q_6$ .

# (3) Output inductor voltage and current at both ends

Fig. 3.4 shows the output inductor voltage and current waveforms in conjunction with the secondary-side synchronous rectification operation (secondary-side MOSFET drain-source voltage and current) described in (2).

<sup>\*:</sup> Drain current is positively directed from MOSFET to the transformer secondary winding.

Fig. 3.4 Secondary-Side MOSFET Drains/Source Voltage/Current Output Inductor Voltage/Current Waveforms

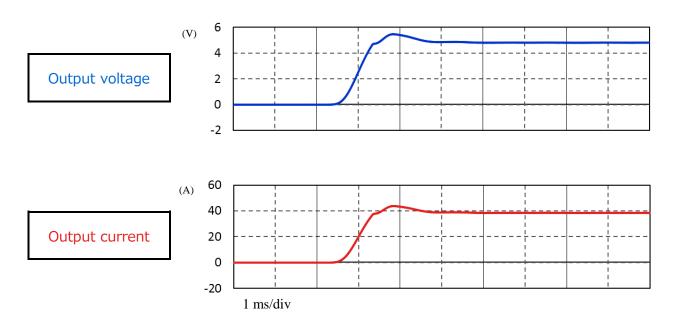

# (4) "output voltage and current" as a power supply

Fig. 3.5 shows the output voltage and current waveforms of this power supply circuit. It can be seen that it is stable at the set voltage and current.

Fig. 3.5 Output Voltage and Current Waveforms

# 4. Product Overview

This section provides an overview of our products that have been tested by incorporating PSpice<sup>®</sup> models into the circuits.

# 4.1 TPN11006PL

# **Features**

- V<sub>DSS</sub>=60 V, I<sub>D</sub>=26 A

- High speed switching

- Small gate-input charge: Q<sub>SW</sub> = 5.8 nC (Typ.)

- Small power charge: Qoss = 14.4 nC (Typ.)

- Low on-resistance: R  $_{DS(ON)}=8.8 \text{ m}\Omega$  (Typ.) ( $V_{GS}=10 \text{ V}$ )

- Lower leakage current:  $I_{DSS} = 10 \mu A (Max.) (V_{DS} = 60 V)$

- Easy-to-handle enhancement type:  $V_{th} = 1.5$  to 2.5 V ( $V_{DS}=10$  V,  $I_D=0.2$  mA)

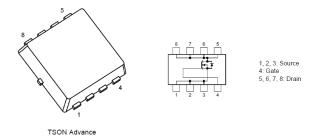

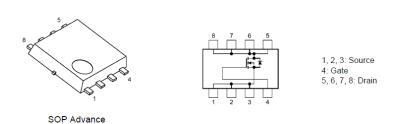

# **Appearance and terminal arrangement**

Width  $3.3 \times \text{Length } 3.3 \times \text{Height } 0.85 \text{ (mm)}$

# 4.2 TPH1R204PL

# **Features**

- V<sub>DSS</sub>=40 V, I<sub>D</sub>=150 A

- High speed switching

- Small gate-input charge: Q<sub>SW</sub> = 17 nC (Typ.)

- Small power charge: Qoss = 56 nC (Typ.)

- Low on-resistance: R  $_{DS(ON)}=1.0 \text{ m}\Omega$  (Typ.) (V<sub>GS</sub>=10 V)

- Lower leakage current:  $I_{DSS} = 10 \mu A (Max.) (V_{DS} = 40 V)$

- Easy-to-handle enhancement type:  $V_{th} = 1.4$  to 2.4 V ( $V_{DS}=10$  V,  $I_D=0.5$  mA)

# Appearance and terminal arrangement

Width 5.0  $\times$  Length 6.0  $\times$  Height 0.95 (mm)

# 5. Using the Simulation Circuit

In order to verify the operation according to actual specifications and the changes according to circuit constants, the simulator can freely change various parameters and analyze the operation of the simulator on OrCAD's Capture. This section describes how to set parameters and how to analyze the operation when actually performing a simulation.

# **How to set parameters**

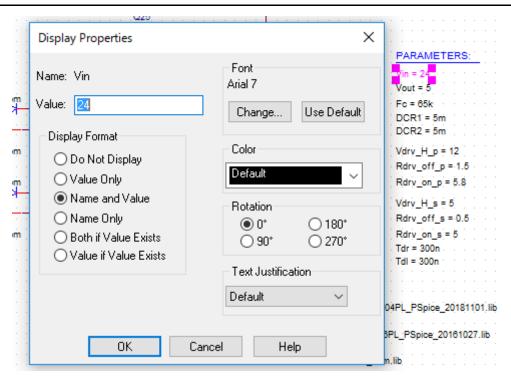

Table 5.1 lists the parameters that can be set by the simulation circuit. Double-clicking a variable in the parameter setting section displays the "Display Properties" window shown in Fig. 5.1. Change the "Value" value in that window.

Table 5.1 List of Variables Settable in Parameter Setting Section

| Variable name | Unit | Description                                   |

|---------------|------|-----------------------------------------------|

| Vin           | V    | Input voltage                                 |

| Vout          | >    | Output voltage                                |

| Fc            | Hz   | Switching frequencies of the secondary        |

| 1 C           |      | MOSFET                                        |

| DCR1          | Ω    | Primary power plane parasitic resistance      |

| DCR2          | Ω    | GND plane parasitic resistance value on the   |

| DCRZ          |      | primary side                                  |

| Vdn/ H n      | V    | Power supply voltage of the primary gate      |

| Vdrv_H_p      |      | driver                                        |

| Rdrv_off_p    | Ω    | Primary MOSFET                                |

| Kui v_oii_p   |      | Internal resistance of gate driver (off side) |

| Rdrv_on_p     | Ω    | Primary MOSFET                                |

| Kui v_oii_p   |      | Internal resistance of gate driver (on side)  |

| Vdrv_H_s      | V    | Power supply voltage of the secondary gate    |

| Vui V_11_5    |      | driver                                        |

| Rdrv_off_s    | Ω    | Secondary MOSFET                              |

| Kui v_oii_s   |      | Internal resistance of gate driver (off side) |

| Pdry on s     | Ω    | Secondary MOSFET                              |

| Rdrv_on_s     |      | Internal resistance of gate driver (on side)  |

| Tdr           | Sec  | Dead time in Q3 and Q4                        |

| Tdl           | Sec  | Dead time of the legs of Q1 and Q2            |

Fig. 5.1 Parameter setting screen

# How to set analysis

The procedure for executing the simulation of this simulation circuit is described below.

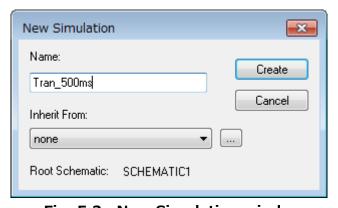

(1) The "New Simulation" window shown in Fig. 5.2 is displayed by clicking "PSpice"-"New Simulation Profile" on OrCAD's Capture menu bar. Specify any profile names and click "Create".

Fig. 5.2 New Simulation window

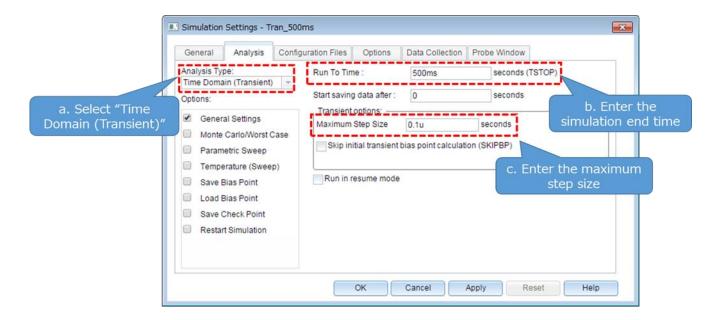

(2) After the steps in 1., the "Simulation Settings" window shown in Fig. 5.3 is displayed, allowing various analysis settings to be made. First, set the analysis method in Analysis tab. Specify "Time Domain(Transient" for "Analysis Type". Specify the duration of the analysis in "Run To Time" and the largest step length in the analysis in "Maximum Step Size".

Fig. 5.3 Simulation Settings"-"Analysis window

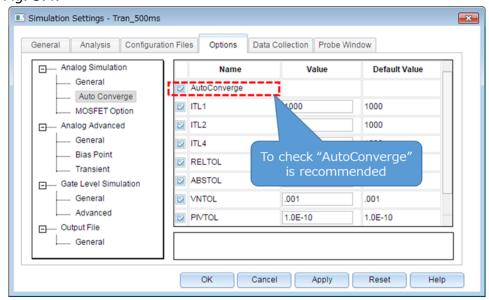

(3) Set analysis options in Options tabs It is recommended to activate the auto-convergence function by checking the "Analog Simulation"-"Auto Converge"-"AutoConverge" checkbox as shown in Fig. 5.4.

Fig. 5.4 Simulation Settings"-"Options window

- (4) When the above settings are completed, click "OK" and close the "Simulation Settings" window.

- (5) Execute simulations at "PSpice"-"Run" on OrCAD "Capture" menu bar. PSpice A/D starts automatically and the simulations are executed.

© 2020

Toshiba Electronic Devices & Storage Corporation

**20** / **23** 2020-05-18

# How to check the results

This section describes how to check the results after completion of simulation. There are two methods for displaying the result waveforms on PSpice A/D window. The procedures for each method are described below.

# Method 1. Result display with net name specified

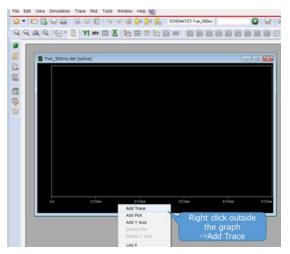

- (1) Right-click outside the graph frame in the graph window, and then select "Add Trace". (Fig. 5.5)

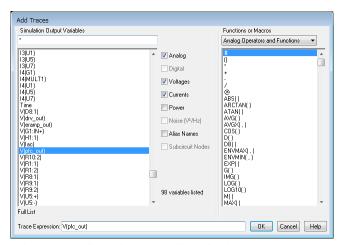

- (2) Select the waveforms to be displayed from the "Add Traces" window. Select V (net name) for the voltage waveform and I (element name) for the current waveform. (Fig. 5.6)

- (3) After selecting, click "OK" to display the result waveform. (Fig. 5.7)

Fig. 5.5 Graph Window

Fig. 5.6 "Add Traces" Window

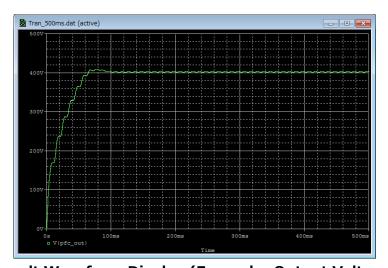

Fig. 5.7 Result Waveform Display (Example: Output Voltage Waveform)

# Method 2. Displaying the result using Marker function

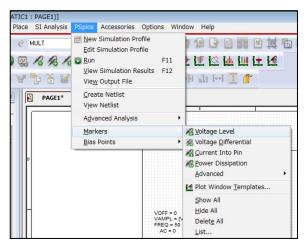

- (1) Select Marker type according to the waveform to be displayed from "PSpice"-"Markers" on OrCAD's Capture menu bar. (Fig. 5.8)

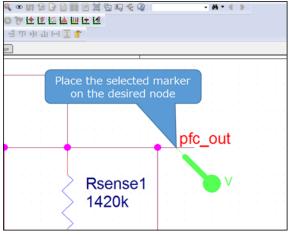

- (2) Place Marker at the waveform measuring points on the simulator. (Fig. 5.9)

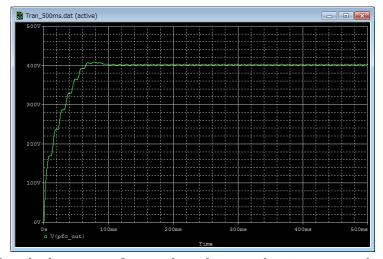

- (3) The result waveforms are displayed in the graph window of PSpice A/D. (Fig. 5.10)

Fig. 5.8 Selecting a Marker type

Fig. 5.9 Placing a Marker in the circuits

Fig. 5.10 Simulation Waveform View (Example: Output Voltage Waveform)

\*\* Cadence, Cadence logo, OrCAD, PSpice and OrCAD logo are trademarks or registered trademarks of Cadence Design Systems, Inc. in the United States or in other countries.

# **Terms of Use**

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and customers who use documents and data that are consulted to design electronics applications on which our semiconductor devices are mounted ("this Reference Design"). Customers shall comply with this terms of use. Please note that it is assumed that customers agree to any and all this terms of use if customers download this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and for any reason. Upon termination of this terms of use, customers shall destroy this Reference Design. In the event of any breach thereof by customers, customers shall destroy this Reference Design, and furnish us a written confirmation to prove such destruction.

### 1. Restrictions on usage

- 1. This Reference Design is provided solely as reference data for designing electronics applications. Customers shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

- 2. This Reference Design is for customer's own use and not for sale, lease or other transfer.

- 3. Customers shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

- 4. This Reference Design shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

### 2. Limitations

- 1. We reserve the right to make changes to this Reference Design without notice.

- 2. This Reference Design should be treated as a reference only. We are not responsible for any incorrect or incomplete data and information.

- 3. Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customers must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

- 4. When designing electronics applications by referring to this Reference Design, customers must evaluate the whole system adequately. Customers are solely responsible for all aspects of their own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- 5. No responsibility is assumed by us for any infringement of patents or any other intellectual property rights of third parties that may result from the use of this Reference Design. No license to any intellectual property right is granted by this terms of use, whether express or implied, by estoppel or otherwise.

- 6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

### 3. Export Control

Customers shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of this Reference Design are strictly prohibited except in compliance with all applicable export laws and regulations.

### 4. Governing Laws

This terms of use shall be governed and construed by laws of Japan.