## 48V バス電圧対応 1.2V/100A 出力 DC-DC コンバータ

# デザインガイド

RD040-DGUIDE-03

東芝デバイス&ストレージ株式会社

1 / 23

2019-05-13

## 目次

| 1.    | はじめに                          | 3    |

|-------|-------------------------------|------|

|       | 搭載パワーMOSFET                   |      |

| 2.    | 回路設計                          | 5    |

| 2.1.  | ハーフブリッジについて                   | 5    |

| 2.2.  | ハーフブリッジ回路設計                   | 6    |

| 3.    | PCB 設計                        | . 18 |

| 3.1.  | PCB パターン設計                    | . 18 |

| 3.2.  | ハーフブリッジ回路パターン設計               | . 19 |

| 3.2.1 | 1. コントローラ周辺パターン設計の注意点         | . 19 |

| 3.2.2 | 2. 入力側 MOSFET 周辺パターン設計の注意点    | . 21 |

| 3 2 3 | 3 出力側同期整流 MOSFFT 周辺パターン設計の注意占 | 22   |

## 1. はじめに

近年の著しい情報処理や通信技術の進歩により、日常的に処理される情報量が飛躍的に増加しデータセンターの増設・新設が繰り返されています。それに伴い全データセンターが消費する電力も増大し、その電力削減が喫緊の課題となっています。近年データセンター内サーバへの電力供給効率を向上させる一方策としてサーバラック内のバス電圧を 48V 化することが検討されていて、OCP (Open Compute Project) からも提案されています。これは、商用 AC 電源から AC-DC 電源を介して生成された DC12V をサーバラック内に供給する従来の方式 (12V バス方式) に対し、AC-DC 電源で DC48V を生成しサーバラック内に供給する方式 (48V バス方式) です。

電源ラインによる電力損失は抵抗成分 (R) と通電電流 (I) で決まる損失 (I<sup>2</sup>R) であり、電流が小さい程損失は低くなります。ここで、12V バス方式と 48V バス方式で同じ電力をサーバラック内に供給する際の電力損失を考えます。48V バス方式の通電電流は 12V 方式の 1/4 であるので、電源ラインの抵抗成分が同等とすると電力損失は 1/16 となり、48V バス方式は大幅に損失低減が可能です。バス電圧が高い程通電電流が減り電源ラインの損失は減りますが、DC60V を超えると安全規格上の危険電圧となり、超低電圧 (ELV: Extra-Low Voltage) や SELV (Safety Extra-Low Voltage) である従来の DC12V と異なる安全規格上の対策が必要となります。そのため、OCP では DC12V と同様の安全規格が適用可能な DC40V~DC59.5V を 48V バス対応電源の入力電圧範囲としています。

一方、48V バス方式化には課題も存在します。 ラックからサーバマザーボードに 48V が印加され、その 48V を CPU、GPU やメモリの電源電圧である 1V 程度の電圧に降圧する必要があります。 一般に降圧 DC-DC コンバータは入力電圧が高い程効率は悪化しますので、 1V を生成する DC-DC コンバータにとって入力が 48V となることは損失増大をもたらします。 48V バス方式により電源ライン損失を低減しても、トータル損失では 12V バス方式と同等、 若しくは劣る恐れもあります。

当社では、この課題を解決するために、48V バス電圧から 1.2V を高効率に生成する DC-DC コンバータのリファンレンスデザインを提案し、トータル効率の向上に貢献します。トランスを介した絶縁型構成を採用し、48V から 1.2V という高い入出力電圧比でも高効率を実現しました。

本デザインガイドはこの DC-DC コンバータ (以下、本電源) の各種回路、レイアウトの設計方法を記載したドキュメントです。本電源の仕様、使用方法、特性データはリファレンスガイドを参照してください。

なお、回路図に部品番号を記載していても、部品表で「Not Mounted」となっているものは PCB に実装しておりません。回路設計時の定数値調整用として PCB に実装場所を設けています。

#### 1.1. 搭載パワーMOSFET

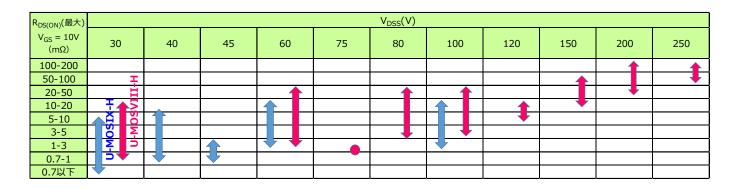

当社では、DC-DC コンバータの一次側(メインスイッチ)や、二次側(同期整流部)に適した低耐圧系 U-MOSVIII/IX シリーズを製品化しています。30Vから250Vまでの広い耐圧展開と、同一耐圧系における豊富なオン抵抗ラインアップを用意しています。DC-DC コンバータの回路トポロジー、入出力電圧、出力仕様、搭載部位(一次側か二次側か)等の設計仕様に応じて最適な製品を選択頂けます。図 1.1 に U-MOSVIII/IX シリーズ製品のラインアップ範囲を示します。

図 1.1 U-MOSVIII/IX 製品ラインアップ範囲

次に、本電源に搭載している MOSFET を紹介します。入力電圧範囲(40~59.5V)、出力電圧(1.2V)、回路トポロジー(ハーフブリッジ)より、一次側に 100V 耐圧系素子、二次側に 30V 耐圧系素子を選択しました。一次側は 100V 耐圧系ラインアップから駆動損失と導通損失のバランスに優れた TPN1200APL を、二次側は 30V 耐圧系ラインアップから 導通損失削減を重視しオン抵抗が小さい TPHR6503PL を選択し搭載しています。

#### TPN1200APL

一次側メインスイッチ部に搭載

$V_{DSS}=100V$ 、 $R_{DS(ON)}$  (最大) = 11.5m $\Omega$  @  $V_{GS}=10V$ 、TSON Advance パッケージ 最新の U-MOSIX-H プロセス品であり、導通損失と駆動損失のバランスを実現。

#### TPHR6503PL

二次側同期整流部に搭載

$V_{DSS} = 30V$ 、 $R_{DS(ON)}$  (最大) = 0.65m $\Omega$ @ $V_{GS} = 10V$ 、SOP Advance パッケージ 最新の U-MOSIX-H プロセス品であり、同期整流動作における損失低減を実現。

Rev.3

## 2. 回路設計

本電源の回路設計のポイントを記載します。

#### 2.1. ハーフブリッジについて

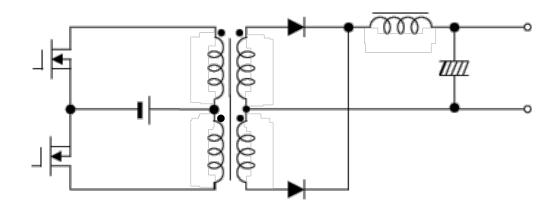

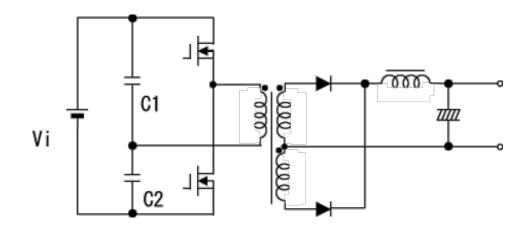

本電源では、ハーフブリッジ回路で 1.2V 出力を生成しています。ハーフブリッジ回路方式はプッシュプル回路方式を基本としています。プッシュプル回路方式は、スイッチング素子を二つ使用し、それらを交互に ON させる方式で、トランスも交互に駆動します。ハーフブリッジ回路方式は、動作はプッシュプル方式と同様ですが、トランスにかかる電圧が Vi の 1/2 となるので耐圧の低いトランジスタを使用することができます。トランスの利用効率は良くなりますが、ブリッジの片側を担うコンデンサに流れるスイッチング電流による発熱に注意が必要です。

図 2.1 プッシュプル回路方式

図 2.2 ハーフブリッジ回路方式

#### 2.2. ハーフブリッジ回路設計

本電源では Texas Instruments 社製コントローラ LM5035 (以下、ハーフブリッジ PWM コントローラ) を用い、ハーフ ブリッジ回路を構成しています。以下に、本電源のハーフブリッジ回路の基本的な設計項目に関して説明します。なお、コントロ ーラ周辺の詳細設計に関しては、Texas Instruments 社製 LM5035 のデータシート、並びに関連文書類を参照してくだ さい。また、本電源の詳細仕様に関してはリファレンスガイド (RD040-RGUIDE-02) を、回路図は RD040-SCHEMATIC-01 を、部品表は RD040-BOM-01 ならびに表 2.1 を参照してください。

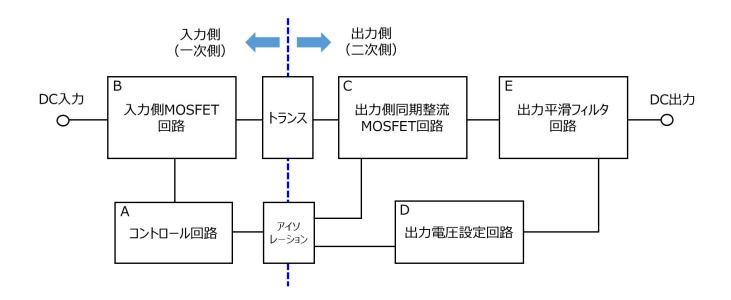

ハーフブリッジ回路のブロック図を図 2.3 に示します。また、各ブロックのパートは以下の通りになっています。

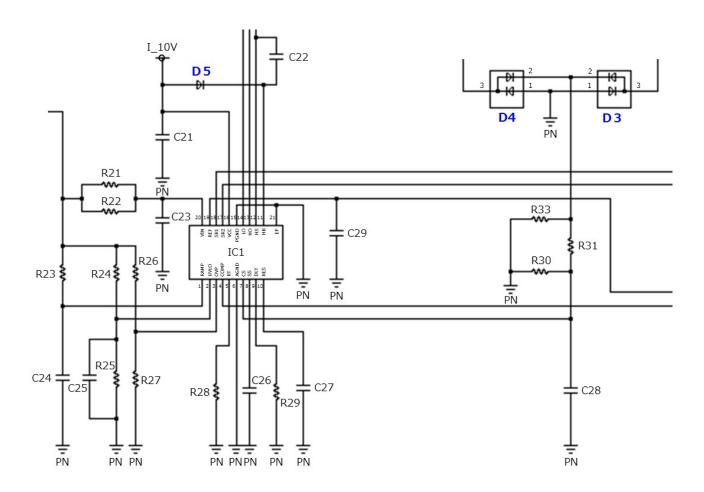

A: コントローラ周辺 (図 2.4)

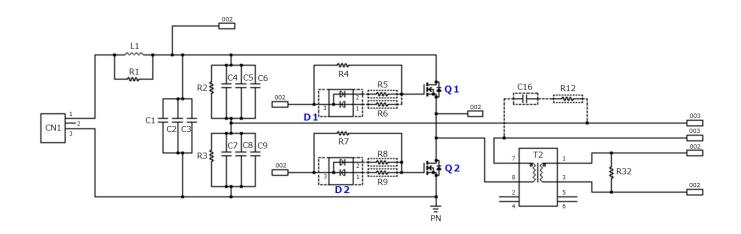

B:入力側 MOSFET 周辺 (図 2.5)

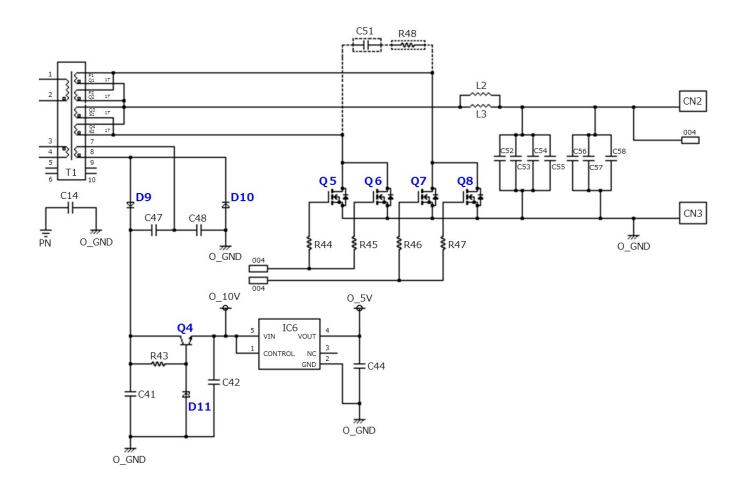

C: 出力側同期整流 MOSFET 周辺 (図 2.6)

D: 出力電圧設定回路 (図 2.11) E: 出力平滑フィルタ回路 (図 2.15)

ハーフブリッジ回路ブロック図 図 2.3

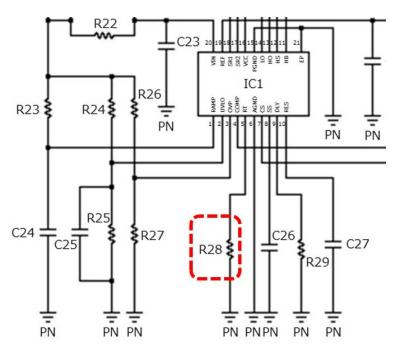

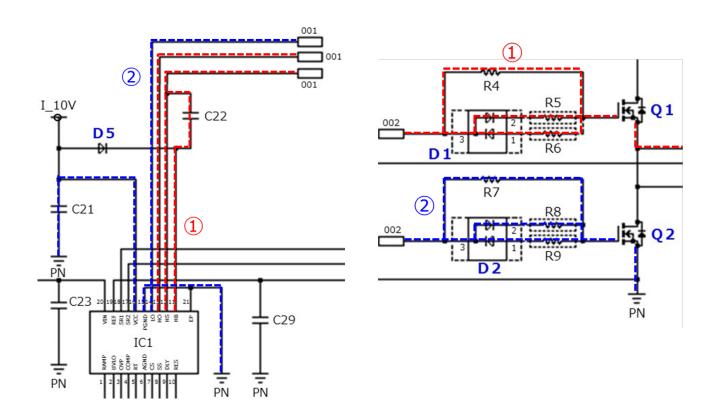

図 2.4 ハーフブリッジ回路 1 (コントローラ周辺)

図 2.5 ハーフブリッジ回路 2 (入力側 MOSFET 周辺)

図 2.6 ハーフブリッジ回路 3 (出力側同期整流 MOSFET 周辺)

2019-05-13

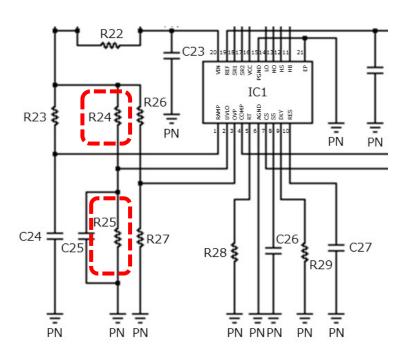

#### 入力電圧動作範囲(下限)の設定

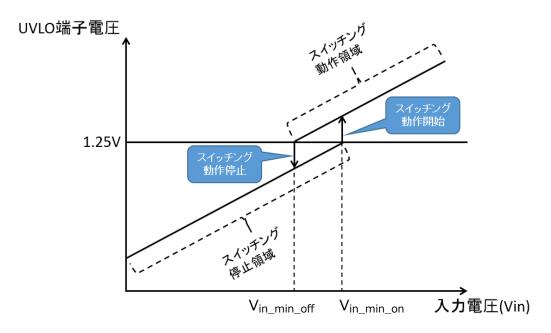

本電源が動作する入力電圧範囲を外付け抵抗 (R24、R25) の抵抗値で設定します (図 2.7)。入力電圧  $V_{in}$  を抵抗 (R24、R25) で分割し、ハーフブリッジ PWM コントローラ の UVLO 端子に入力することで動作電圧下限値 ( $V_{in\_min\_on}$ 、  $V_{in\_min\_off}$ ) を設定します。

図 2.7 UVLO 入力電圧範囲の設定

ハーフブリッジ PWM コントローラは、これらの抵抗分割と内部ヒステリシス電流(23µA)によって発生する UVLO 端子電圧が 1.25V を超えるとスイッチング動作を開始します。 ハーフブリッジ PWM コントローラは、動作開始後は内部ヒステリシス電流を停止し、 UVLO 端子電圧が 1.25V を下回るとスイッチング動作を停止します。 以下の式で動作電圧下限値(V<sub>in\_min\_on</sub>、 V<sub>in\_min\_off</sub>)を算出します。

$$V_{in\_min\_on}(V) = 1.25(V) \times \frac{(R24 + R25)}{(R25)} + 23(\mu A) \times R24$$

$$V_{in\_min\_off}(V) = 1.25(V) \times \frac{(R24 + R25)}{(R25)}$$

$V_{in\_min\_on}$  の設定値は 16.05V、 $V_{in\_min\_off}$  の設定値は 13.75V で、その場合の抵抗値 (R24) が  $100k\Omega$ 、抵抗値 (R25) が  $10~k\Omega$ です。図 2.8 に入力電圧 ( $V_{in}$ ) と UVLO 端子電圧、スイッチング動作状況の関係を示します。

図 2.8 入力電圧 vs UVLO 端子電圧、スイッチング動作状況

#### 入力電圧動作範囲 (上限) の設定

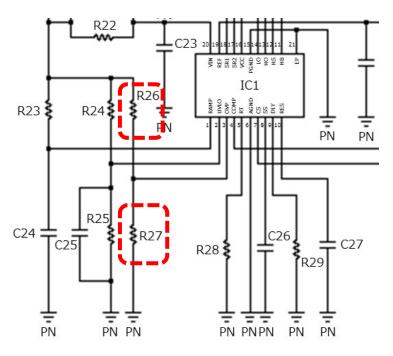

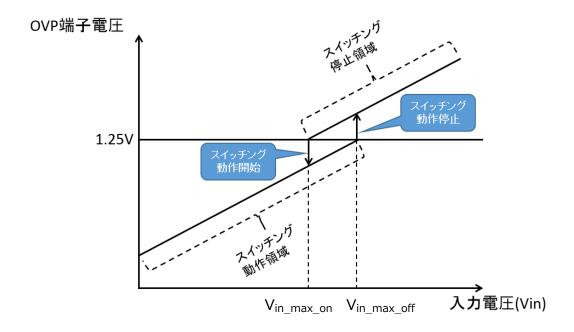

本電源が動作する入力電圧範囲を外付け抵抗 (R26、R27) の抵抗値で設定します (図 2.9)。入力電圧  $V_{in}$  を抵抗 (R26、R27) で分割し、ハーフブリッジ PWM コントローラの OVP 端子に入力することで動作電圧上限値 ( $V_{in\_max\_off}$ 、 $V_{in\_max\_on}$ ) を設定します。

図 2.9 OVP 入力電圧範囲の設定

ハーフブリッジ PWM コントローラは、これらの抵抗分割によって発生する OVP 端子電圧が 1.25V を超えるとスイッチング動 作を停止します。ハーフブリッジ PWM コントローラは、動作停止後は内部ヒステリシス電流の動作を開始し、OVP 端子電圧 が 1.25V を下回るとスイッチング動作を開始します。以下の式で動作電圧下限値 (Vin min on 、Vin min off) を算出します。

$$V_{in\_max\_off}(V) = 1.25(V) \times \frac{(R26 + R27)}{(R27)}$$

$$V_{in\_max\_on}(V) = 1.25(V) \times \frac{(R26 + R27)}{(R27)} - 23(\mu A) \times (R26)$$

V<sub>in\_max\_off</sub> の設定値は 63.75V、V<sub>in\_max\_on</sub> の設定値は 61.45V で、その場合の抵抗値 (R26) が 100kΩ、抵抗値 (R27) が  $2.0k\Omega$  です。図 2.10 に入力電圧  $(V_{in})$  と OVP 端子電圧、スイッチング動作状況の関係を示します。

図 2.10 入力電圧 vs OVP 端子電圧、スイッチング動作状況

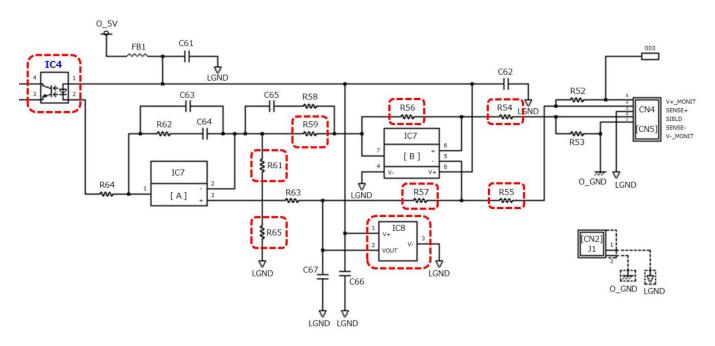

#### 出力電圧の設定

ハーフブリッジ回路の出力電圧 (V<sub>out</sub>) を外付け抵抗 (R54、R55、R56、R57、R59、R61、R65) の抵抗値、電圧リファレンス (IC8) で設定します。LM5035 は出力電圧を抵抗 (R59、R61、R65) で分割した電圧がリファレンス電圧 (V<sub>REF</sub>) と一致するようにフォトカプラ (IC4) の電流を制御します。

図 2.11 出力電圧の設定

ハーフブリッジ PWM コントローラはフォトカプラ (IC4) からフィードバックされる電流量に応じて MOSFET (Q1、Q2、Q5、Q6、Q7、Q8) を制御して出力電圧 ( $V_{out}$ ) を一定に保ちます。R54、R55、R56、R57 を全て  $22k\Omega$ の同一抵抗値とすると、以下の式で出力電圧 ( $V_{out}$ ) を算出します。

$$V_{out} (V) = \frac{V_{REF}(V) \times R59}{(R61 + R65)}$$

出力電圧  $(V_{out})$  の設定値は 1.2V でリファレンス電圧  $(V_{REF})$  は 1.2V であり、その場合の抵抗値 (R59) が  $22k\Omega$ 、抵抗値 (R61) が  $20k\Omega$ 、抵抗値 (R65) が  $2k\Omega$ です。

#### スイッチング周波数の設定

ハーフブリッジ回路のスイッチング周波数 (fpwm) を外付け抵抗 (R28) の抵抗値で設定します。

図 2.12 スイッチング周波数の設定

以下の式でスイッチング周波数 (fpwm) を算出します。

$$f_{PWM}(Hz) = \frac{1}{(R28(\Omega)) \div (6.25 \times 10^9) + 110 \times 10^{-9}}$$

スイッチング周波数  $(f_{PWM})$  の設定値は 302kHz で、その場合の抵抗値 (R28) が  $20k\Omega$ です。ハーフブリッジ PWM コントローラは入力側の MOSFET (Q1 及び Q2) をスイッチング周波数  $(f_{PWM})$  の 1/2 の周波数でスイッチングします。結果として出力にはスイッチング周波数  $(f_{PWM})$  のリップル電圧が発生します。

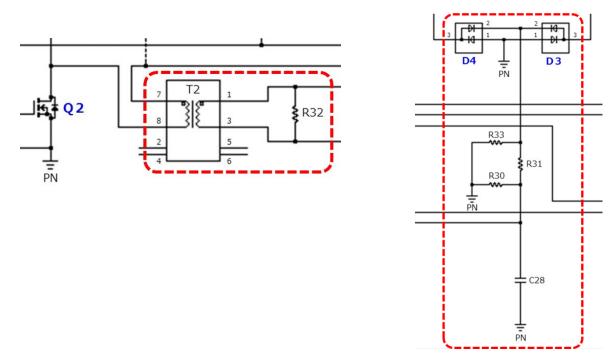

#### カレントリミッタ

ハーフブリッジ PWM コントローラの CS 端子の電圧が電流制限しきい値 (0.25V) に到達すると、ハーフブリッジ PWM コントローラが入力側ブリッジ MOSFET を制御して電流制限をかけます。図 2.5 にハーフブリッジ回路 2 (入力側 MOSFET 周辺) を示します。カレントリミッタレベル (I\_limit) を電流制限しきい値 (0.25V) と電流検出抵抗の抵抗値 (R33) と分割抵抗の抵抗値 (R30、R31) とカレントトランス (T2) の巻線比 (transformer turns ratio) で設定します。

図 2.13 カレントリミッタ

以下の式でカレントリミッタレベルを算出します。

$$I\_limit = \frac{0.25}{R33 \times (transformer\ turns\ ratio)} \times \frac{R30}{(R30 + R31)}$$

カレントリミッタレベルの設定値は 22.7A で、その場合の抵抗値 (R33) が  $2.2\Omega$ 、抵抗値 (R30、R31) が  $1k\Omega$ 、 カレントトランス (T2) の巻線比が 1:100 です。 カレントリミットは実機での合わせ込みが必要となります。

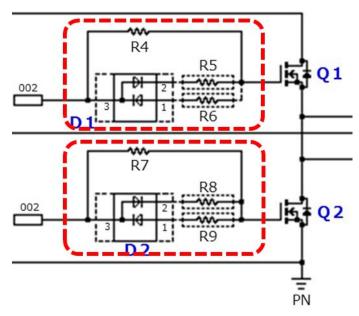

#### ゲート駆動回路

ゲート駆動回路の設計が電源効率と EMI に影響を与えます。一般に電源効率と EMI はトレードオフの関係にあり、両者のバランスを取った設計が必要です。スイッチングノイズが EMI の原因と思われる場合は、MOSFET (Q1、Q2) のゲート直列抵抗の抵抗値 (R5、R6、R8、R9) を大きくし、EMI を確認してください (図 2.14)。

図 2.14 ゲート駆動回路

MOSFET のターンオンスピードとターンオフスピードの個別調整が可能です。もし、個別調整が不要な場合は D1、D2、R5、R6、R8、R9 を未実装に、R4、R7 を実装に変更し、R4、R7 でスイッチングスピードを調整します。初期設定として R4、R7 を  $0\Omega$  に、D1、D2、R5、R6、R8、R9 を未実装にしています。

#### トランス

ハーフブリッジ回路の定常状態における同期整流側の On Duty を 35%に設定すると、出力電圧が 1.2V なので、2 次側には 3.4V 程度の矩形波が必要となります。本電源の入力電圧(標準)54.5V の半分である 27.25V が 1 次側巻線両端に印加されるため、トランス(T1)の巻線比は、8:1 を選択します。これにより、2 次側には 27.25V の巻線比倍の 3.4V の矩形波が発生することになります。また、補助巻線によって入力側のコントローラ用電源(I\_10V)、及び出力側のドライバ電源(O\_10V)、及びその他フォトカプラの電源(O\_5V)を生成するため、トランス(T1)の巻線比は 8:1:1:3:3(センタータップ方式、補助巻線付)を選択します。1 次-2 次間絶縁耐圧、巻線温度上昇、磁束飽和、コアロス等を十分に考慮する必要があります。本電源で使用しているトランスの仕様は、部品表(RD040-BOM-01)を参照してください。

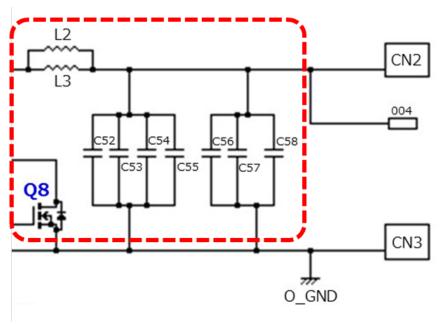

#### 出力平滑フィルタ

出力コンデンサの静電容量値 (Cout) で出力電圧リップル (Vripple) が要求仕様に入るように設定します。トランス (T1) の出力側に現れる矩形波を同期整流用コイル (L2、L3) と出力のコンデンサ (Cout) で構成される LC フィルタで平滑化します。

図 2.15 出力平滑フィルタ回路

トランス (T1) に現れる矩形波の最大電圧 V<sub>node</sub> は入力が最大電圧時 59.5V 時の 3.7V となります。このとき、出力の コンデンサ (C<sub>out</sub>) の総容量を 1900 μF とすると、スイッチング周波数 302kHz 成分の減衰量は約-70dB となるため、出力 のリップル電圧は 1.1mV となります。 実際は出力コンデンサの ESR や ESL 等によるリップル成分もあるため、 実機での確認が 必要です。 また、以下についても確認してください。

- 1. 負荷急変時に発生する出力端アンダーシュート・オーバーシュートが規定電圧範囲に入っていること

- 2. 出力コンデンサの許容リップル電流が確保できていること

- 3. 出力コンデンサの公差や経年劣化を考慮すること

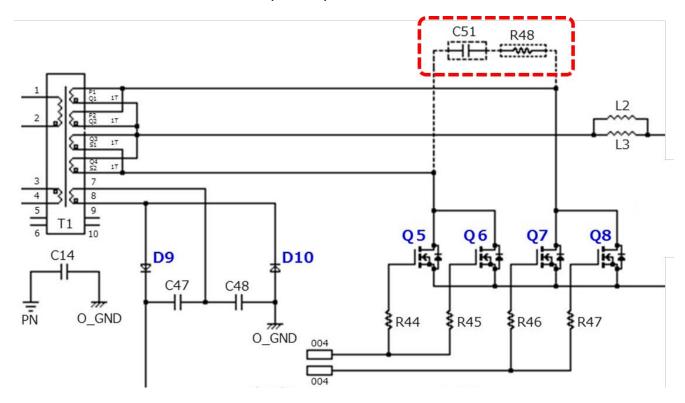

#### 同期整流 MOSFET サージ電圧低減回路

入力から出力に電力を伝達する際にトランス T1 出力端子両端に発生するサージ電圧が問題となる場合は、サージ電圧 を低減するために Snubber 回路を設置します (図 2.16)。

図 2.16 Snubber 回路

Snubber 回路を R48、C51 で実現します。 Snubber 回路では T1 の 7 ピン-10 ピン間に発生したサージ電圧  $(V_{srg})$  を吸収します。 このとき、抵抗 R48 で発生するロス  $P_{d\_Rsnb}$  は以下のとおりとなります。

$$P_{d\_Rsnb} = C51 \times (V_{srg})^2 \times (\frac{f_{PWM}}{2})$$

本電源においては、Snubber 回路は未実装としています。実機でサージ電圧を確認し、必要に応じて実装してください。

## 3. PCB 設計

本電源の PCB 設計時の注意点を記載します。

#### 3.1. PCB パターン設計

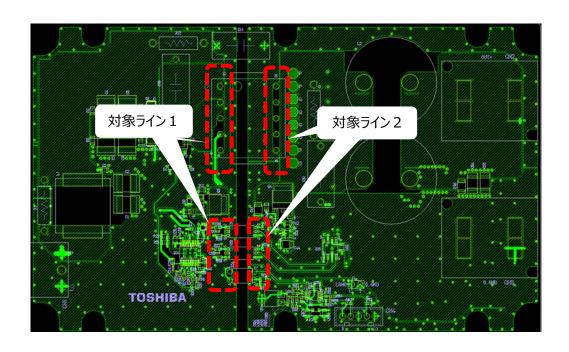

#### 沿面距離

要求仕様の安全規格に応じて適切な空間距離・沿面距離を確保してください。表 3.1 に本電源で用いた沿面距離を示 します。なお、設置する環境、材料、材料の汚損度、湿度、高度 (気圧) 等によって必要な空間距離・沿面距離が変わる ため、十分に考慮してください。

表 3.1 設計最小沿面距離

| 対象ライン 1    | 対象ライン 2    | 対象ライン1と対象ライン2の沿面距離 |

|------------|------------|--------------------|

| 入力 (カプラ部)  | 出力 (カプラ部)  | 1.4mm              |

| 入力 (トランス部) | 出力 (トランス部) | 1.4mm              |

#### 電流容量

基板上の各パターンは、各パターンにおける最大電流を流した際に、温度上昇、あるいはパターンによる IR ドロップのいずれ による問題も発生させないパターン幅を確保する必要があります。

© 2019 18 / 23 2019-05-13 Toshiba Electronic Devices & Storage Corporation Rev.3

#### 3.2. ハーフブリッジ回路パターン設計

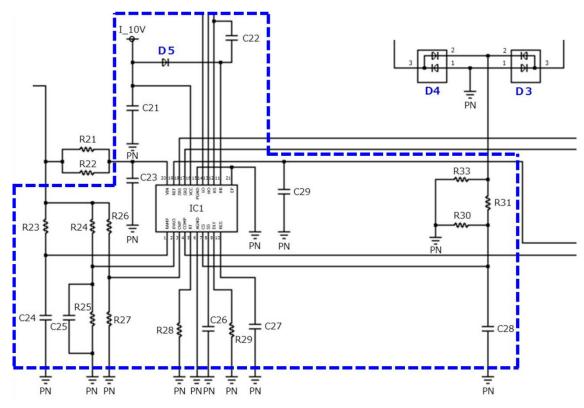

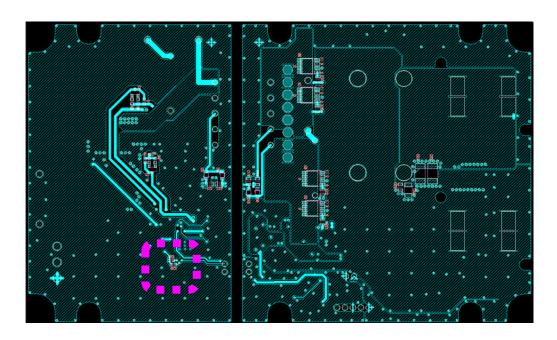

ハーフブリッジ回路周辺の PCB 設計の注意点を説明します。図 3.1 にハーフブリッジ回路 (コントローラ周辺)、図 3.4 に ハーフブリッジ回路パターン設計注意点 1、図 3.5 にハーフブリッジ回路パターン設計注意点 2 を示します。コントローラ周辺の レイアウトはハーフブリッジ PWM コントローラのデータシート、関連書類などを参照してください。

#### 3.2.1. コントローラ周辺パターン設計の注意点

- 1. ハーフブリッジ PWM コントローラ (IC1) は2次側の大電流スイッチング回路、トランス、リアクトルから離して配置します。

- 2. 図 3.1 に記載している青色点線内部の部品は、図 3.2 のようにハーフブリッジ PWM コントローラの近傍に配置します。

- 3. GND プレーン (回路図中 PN) は図 3.3 のように 1 点にまとめ、ハーフブリッジ PWM コントローラの AGND ピンに接続 します。

図 3.1 ハーフブリッジ回路 (コントローラ周辺)

図 3.2 基板レイアウト1

図 3.3 基板レイアウト2

### 3.2.2. 入力側 MOSFET 周辺パターン設計の注意点

- 1. 電圧変動大のスイッチングノード周辺 (図中①および①と同電位の電圧変動を持つライン) の面積が極小となるよう部品を配置します。

- 2. ドライバ出力ライン (図中①、②) を可能な限り短くするために IC1 と Q1、Q2 を近傍に配置し、ドライブ電流最大値を流せるパターン幅を確保します。

- 3. Q1 のドライブ電流のリターン経路をソース端子直近から分離します。

- 4. Q2 のドライブ電流のリターン経路を GND プレーン (PN) から分離する場合は、Q2 のソース端子直近から分離します。

図 3.4 ハーフブリッジ回路パターン設計注意点 1

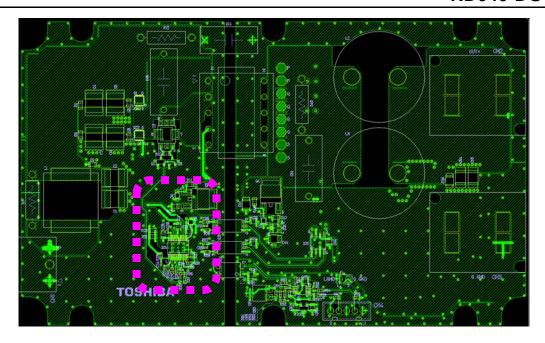

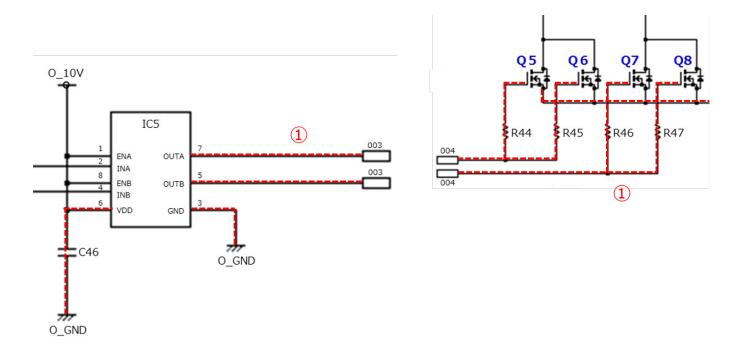

#### 3.2.3. 出力側同期整流 MOSFET 周辺パターン設計の注意点

- 1. ドライバ出力ライン (図中①) は可能な限り短くするために IC5 と Q5、Q6、Q7、Q8 を近傍配置し、ドライブ電流最大値を流すことのできるパターン幅を確保します。

- 2. ドライブ電流のリターン経路を GND (O\_GND) プレーン以外にする場合は、Q5、Q6、Q7、Q8 のソース端子直近から分離します。

- 3. Snubber 回路 C51、R48 を Q5、Q6、Q7、Q8 ドレイン-ソース間直近に配置できるよう場所を確保します。

- 4. トランスと同期整流 MOSFET のループを最小にするため T1 と Q5、Q6、Q7、Q8 を直近に配置します。

図 3.5 ハーフブリッジ回路パターン設計注意点 2

22 / 23

2019-05-13

### ご利用規約

本規約は、お客様と東芝デバイス&ストレージ株式会社(以下「当社」といいます)との間で、当社半導体製品を搭載した機器を設計する際に参考となるドキュメント及びデータ(以下「本リファレンスデザイン」といいます)の使用に関する条件を定めるものです。お客様は本規約を遵守しなければなりません。本リファレンスデザインをダウンロードすることをもって、お客様は本規約に同意したものとみなされます。なお、本規約は変更される場合があります。当社は、理由の如何を問わずいつでも本規約を解除することができます。本規約が解除された場合は、お客様は、本リファレンスデザインを破棄しなければなりません。またお客様が本規約に違反した場合は、お客様は、本リファレンスデザインを破棄し、その破棄したことを証する書面を当社に提出しなければなりません。

#### 第1条 禁止事項

お客様の禁止事項は、以下の通りです。

- 1. 本リファレンスデザインは、機器設計の参考データとして使用されることを意図しています。信頼性検証など、それ以外の目的には使用しないでください。

- 2. 本リファレンスデザインを販売、譲渡、貸与等しないでください。

- 3. 本リファレンスデザインは、高低温・多湿・強電磁界などの対環境評価には使用できません。

- 4. 本リファレンスデザインを、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用しないでください。

#### 第2条 保証制限等

- 1. 本リファレンスデザインは、技術の進歩などにより予告なしに変更されることがあります。

- 2. 本リファレンスデザインは参考用のデータです。当社は、データおよび情報の正確性、完全性に関して一切の保証をいたしません。

- 3. 半導体素子は誤作動したり故障したりすることがあります。本リファレンスデザインを参考に機器設計を行う場合は、誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うことをお願いします。また、使用されている半導体素子に関する最新の情報(半導体信頼性ハンドブック、仕様書、データシート、アプリケーションノートなど)をご確認の上、これに従ってください。

- 4. 本リファレンスデザインを参考に機器設計を行う場合は、システム全体で十分に評価し、お客様の責任において適用可否を判断して下さい。当社は、適用可否に対する責任は負いません。

- 5. 本リファレンスデザインは、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 6. 当社は、本リファレンスデザインに関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をせず、また当社は、本リファレンスデザインに関する一切の損害(間接損害、結果的損害、特別損害、付随的損害、逸失利益、機会損失、休業損、データ喪失等を含むがこれに限らない。)につき一切の責任を負いません。

#### 第3条 輸出管理

お客様は本リファレンスデザインを、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用してはなりません。また、お客様は「外国為替及び外国貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守しなければなりません。

#### 第4条 準拠法

本規約の準拠法は日本法とします。