# インターリーブ方式 PFC 電源 基本シミュレーション回路 リフアレンスガイド

RD032-RGUIDE-02

東芝デバイス&ストレージ株式会社

## 目次

| 1.   | はじめに           | 3  |

|------|----------------|----|

|      |                |    |

| 2.   | PFC 回路概要       | 5  |

| 2.1. | 電源仕様           | 5  |

| 2 2  | 回路構成           | _  |

| 2.2. | 凹近伸双           | 3  |

| 3.   | 動作検証結果         | 7  |

| 4.   | 使用素子概要         | 11 |

| 4.1. | TK20N60W       | 11 |

|      | TRS6E65F       |    |

| 4.2. | TRS6E65F       | 11 |

| 5.   | シミュレーション回路使用方法 | 12 |

## 1. はじめに

交流電力は理想状態では、電圧、電流ともに完全な正弦波状であり両者の位相も揃っています。しかしながら各種機器が接続されると位相がずれたり、波形が正弦波状でなくなったりすることがあります。力率 (Power Factor) とは、理想状態と実際とのずれを定義したものであり、以下の式で表されます。

力率 = 有効電力 ÷ 皮相電力

有効電力は瞬時電圧と瞬時電流を掛け合わせた瞬時電力を交流周期で積分した値であり、実際に負荷で消費される電力を表します。皮相電力は入力電圧の実効値と入力電流の実効値を掛け合わせた値を表します。

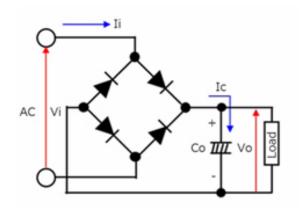

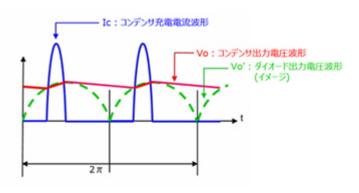

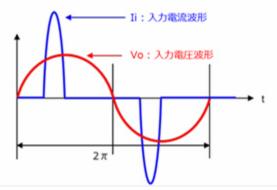

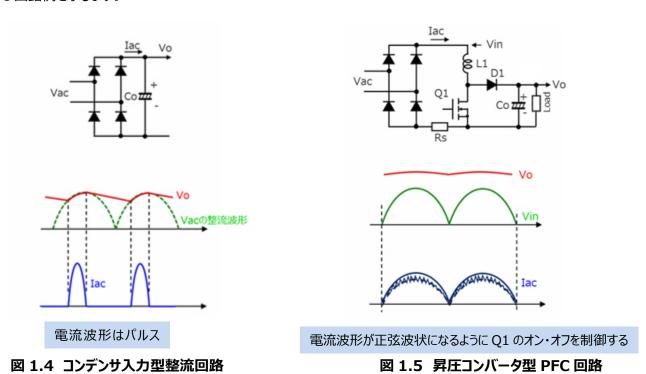

力率は 0 から 1 の間の値をとり、力率=1 が理想状態で皮相電力=有効電力の時、力率=0 は皮相電力=無効電力の時を表します。力率が低くなると同じ有効電力を伝送する際に、より大きな皮相電力が必要となり、他の機器や送配電設備へ影響を与えるため、望ましくありません。旧来の AC-DC 電源では、AC 入力をダイオードブリッジとコンデンサで整流するコンデンサ入力型整流回路で DC 化した後に所望の電圧へ変換していました。この方式は、コンデンサ出力電圧がダイオードブリッジ出力電圧を下回った時のみコンデンサへ充電電流が流れるため、入力電流はパルス状となり力率は低い値でした。図 1.1、図 1.2、図 1.3 にコンデンサ入力型整流回路の回路例、各部波形イメージを示します。

図 1.1 コンデンサ入力型整流回路

図 1.2 各部波形イメージ

図 1.3 入力電流、電圧波形イメージ

PFC (Power Factor Correction) 回路とは、AC 入力を DC へ変換する際に力率を改善するための回路です。現在は PFC 回路を内蔵し力率を改善した AC-DC 電源が主流となっています。AC-DC 電源における PFC 回路は AC 入力をダイオードブリッジの後に配置する昇圧コンバータが一般的です。図 1.4 にコンデンサ入力型整流回路、図 1.5 に昇圧コンバータ型 PFC 回路例を示します。

AC-DC 電源における力率や PFC 回路に関しては当社 Web 上で配信しております下記動画もご参照願います。

単相 PFC 回路に対し、インダクタ、ダイオード、MOSFET を並列に 2 相配置し、各相の位相を半周期 (180 度) ずらして動作させるインターリーブ方式 PFC 回路があります。2 相で電力分担を行うので、同出力の単相 PFC 回路に比べ定格の小さな素子を使用することが可能になります。また、動作位相が 180 度ずれているので合成後のリップル電流は、各相単独の物より小さくなります。そのため、インターリーブ方式 PFC 回路は出力の比較的大きな AC-DC 電源で採用されています。このインターリーブ方式 PFC 電源の動作を理解頂くために、基本シミュレーション回路 (RD032-SPICE-02) を当社 Web 上で提供しています。

本ドキュメントでは、このシミュレーション回路の概要、使用方法等を解説していきます。シミュレーション回路を動作させるためには、Cadence<sup>®</sup>社の OrCAD<sup>®</sup> Capture 及び PSpice<sup>®</sup> A/D ツールが必要となります。また、本シミュレーション回路及びドキュメントは OrCAD<sup>®</sup> 17.2 に基づき作成されています。

## 2. PFC 回路概要

RD032-SPICE-02 は、1200W 出力のインターリーブ方式 PFC 電源を構成しています。

## 2.1. 電源仕様

本ドキュメントでは、以下の仕様でインターリーブ方式 PFC 電源を規定しています。

·入力電圧: 90~264 V<sub>rms</sub>

・出力電圧: 400 V・出力電流: 0~3.0 A・動作周波数: 50 kHz

・許容リップル電流幅: 50%(ピーク入力電流比)

・インダクタ設定値:180 μH

## 2.2. 回路構成

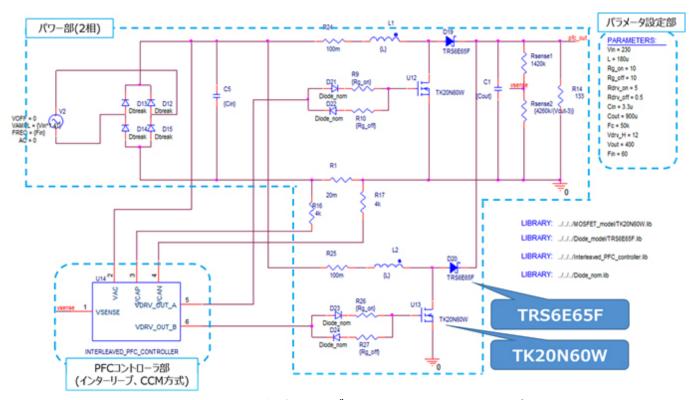

図2.1にOrCAD<sup>®</sup>上で動作するシミュレーション回路を示します。電流連続モード(以下 CCM: Continuous Current Mode)方式のインターリーブ PFC 電源であり、主に、2 相のスイッチング回路で構成されたパワー部、PFC コントローラ部、パラメータ設定部で構成されています。PFC コントローラは本基本回路を実現する為に用意した MOSFET ゲートドライバ内蔵の汎用コントローラです。また、スイッチング用 MOSFET およびダイオードは、「TK20N60X」・「TRS6E65F」を例として使用しています。

図 2.1 1200W インターリーブ PFC 電源シミュレーション回路

## 搭載 MOSFET、ダイオード選定

搭載する MOSFET とダイオードは以下の観点にて選定しました。

(1) 素子耐圧

定常的に MOSFET、ダイオードに印加される電圧は出力電圧と同じ 400V であるので、耐圧 600V 以上の素子を選定。

(2) 電流定格

入力電流が最大となるのは、最大出力電力時で入力電圧が最小の時となります。最大出力電力=1200W 時の変換効率を94%、力率を1とすると、最小入力電圧=90V<sub>rms</sub> 時の最大入力電流は約14.1A<sub>rms</sub> となります。これを2相で分担し、デューテイを50%と仮定すると、各素子に印加される電流は約3.6Arms であるので、電流定格5A以上の素子を選定。

MOSFET: TK20N60W (V<sub>DS</sub>=600V / I<sub>D</sub>=20A / R<sub>DS(ON)</sub>=155mΩ (最大))

ダイオード: TRS6E65F (650V/6A)

## インダクタ選定

インダクタの選定法について説明します。本シミュレーション回路におけるインダクタンス値は、電源仕様である下記項目を用いて計算により求めることができます。

最大出力電力: Pout (W)

AC ライン最小入力電圧: V<sub>in min</sub> (V<sub>rms</sub>)

PFC 電力変換効率:η(%)

・ PFC 出力電圧: Vout (V)

・ スイッチング周波数:Fc(Hz)

許容リップル電流幅: ΔI<sub>ripple</sub> (%)

以下の式でインダクタンス値を算出します。

$$L = \frac{\left(V_{out} - \sqrt{2} \times V_{in\_min}\right) \times \eta \times 0.01 \times V_{in\_min}^{2}}{F_{c} \times 0.01 \times \Delta I_{ripple} \times P_{out} \times V_{out}}$$

ここで最大出力電力( $P_{out}$ )が 1200W、AC ライン最小入力電圧( $V_{in\_min}$ )が 90V、PFC 出力電圧( $V_{out}$ )が 400V、スイッチング周波数( $F_c$ )が 50kHz であり、PFC 電力変換効率( $\eta$ )を 94%とすると、上記式よりインダクタンス 値(L)は 173 $\mu$ H と算出されるため、設定値は 180 $\mu$ H としています。

実際の設計においては、インダクタは直流重畳特性によりインダクタンス値が変動します。直流重畳特性によりインダクタンス値が低下した状態で、上記計算値の値を確保できる部品を選定する必要があります。

インターリーブ PFC では、合成された電流のリップルは各相のインダクタに流れる電流リップルより小さくなります。単相 PFC と同じ電流リップルを実現する場合、より小さなインダクタンス値を採用することが可能です。しかしながらリップル抑制率は実動作条件に応じて変動しますので、インダクタンス値を下げる際は充分な検証が必要です。

## 3. 動作検証結果

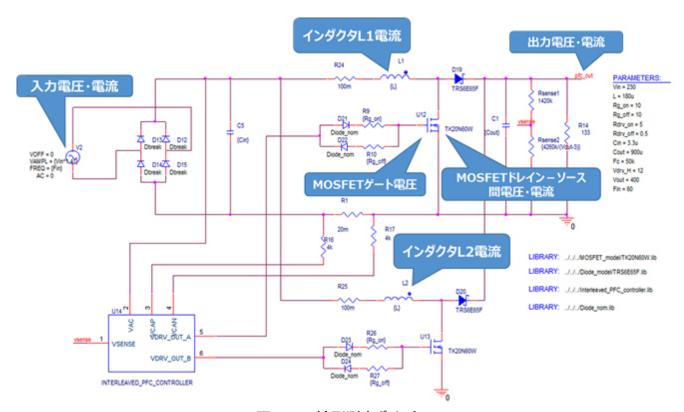

本シミュレーション回路における各部の動作結果について説明します。本ドキュメントでは、図 3.1 の「入力電圧・電流」、「インダクタ電流」、「出力電圧・電流」、「MOSFET ゲート電圧」、「MOSFET ドレイン・ソース間電圧・電流」の波形を示します。実際にシミュレーション回路を使用する際には、図 3.1 以外の部分についても波形を表示することが可能です。波形表示方法については第5章で記述します。

図 3.1 波形測定ポイント

## 入力電圧・電流, 出力電圧・電流, インダクタ電流波形

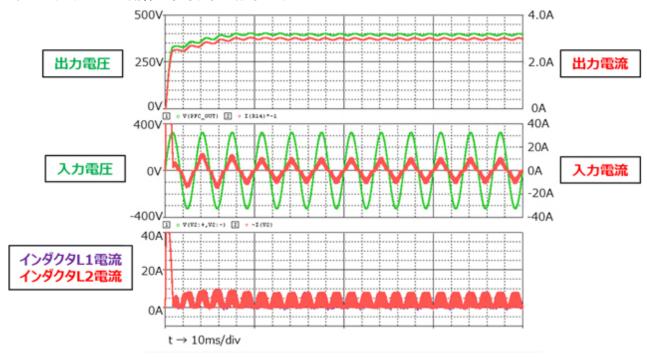

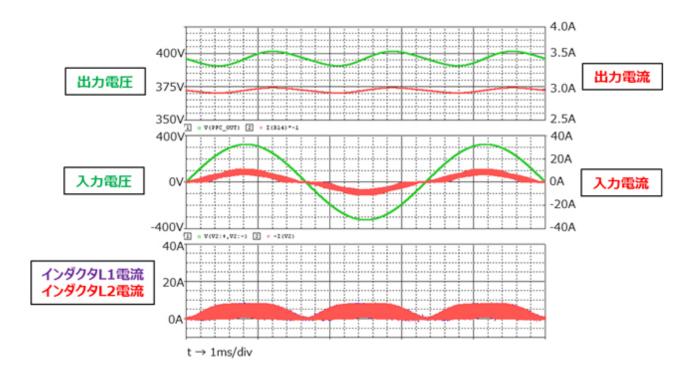

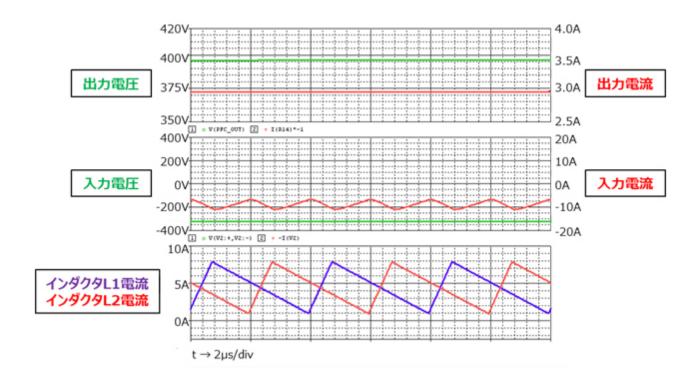

図 3.2~図 3.4 に電源回路の AC 入力部の電流・電圧、PFC 出力電圧・電流およびインダクタ電流波形を示します。 PFC 出力電圧波形(図 3.2~図 3.4 上段)より、PFC 回路の出力が電源仕様である 400V で安定していることが確認できます。 また、AC 入力の電流波形(図 3.2~図 3.4 中段)より、電流波形が CCM 方式で正弦波に補正され、力率が改善されていることが確認できます。 各相のインダクタ電流(図 3.4 下段)より、インダクタ L1・L2 のそれぞれで位相が 180° ずれたインターリーブ PFC の動作を確認することができます。

図 3.2 入力電圧・電流、出力電圧・電流、インダクタ電流波形

図 3.3 入力電圧・電流、出力電圧・電流、インダクタ電流波形 拡大 1

図 3.4 入力電圧・電流、出力電圧・電流、インダクタ電流波形\_拡大 2

## MOSFET ゲート電圧, MOSFET ドレインソース間電圧・電流

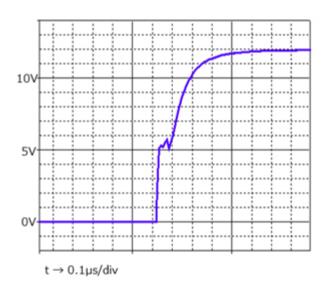

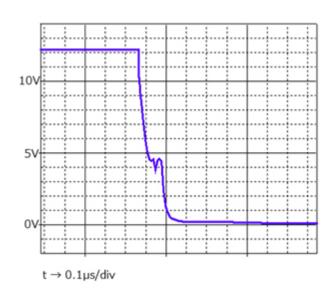

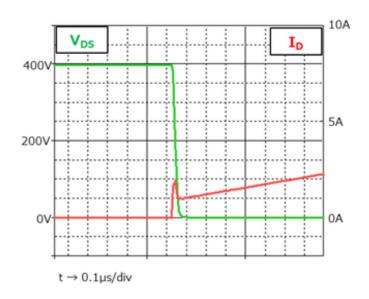

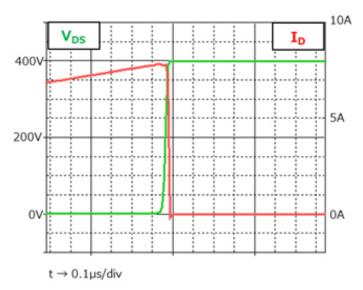

本シミュレーション回路でスイッチング用 MOSFET として使用されている「TK20N60W」について、図 3.5 に MOSFET ゲート電圧波形、図 3.6 に MOSFET ドレイン・ソース間電圧(V<sub>DS</sub>)・電流(I<sub>D</sub>)波形を示します。 MOSFET を PWM 制御し、正弦半波状のインダクタ電流を形成していますが、インダクタ電流がピークとなった時の波形を表示しています。

本シミュレーション回路では、ゲートに接続される外付け抵抗の定数を「Rg\_on」「Rg\_off」という変数名でパラメータ化しており、これら値を変更することで、ゲート抵抗を変更した場合の MOSFET の挙動を検証することができます。

(a) ターンオン時

(b) ターンオフ時

図 3.5 MOSFET ゲート電圧波形

a. ターンオン時

b. ターンオフ時

図 3.6 MOSFET ドレイン-ソース間電圧・電流波形

Rev.2

## 4. 使用素子概要

本回路に PSpice®モデルを組み込んで検証している当社製品の概要を紹介します。

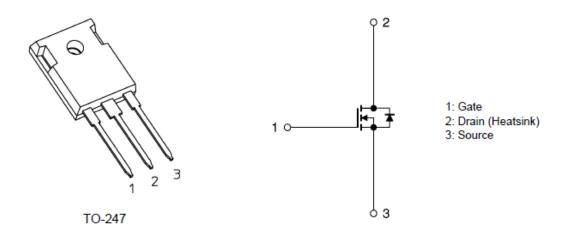

## 4.1. TK20N60W

## 特徴

- $\bullet$  スーパージャンクション構造DTMOSの採用によりオン抵抗が低い:  $R_{DS(ON)} = 0.13 \Omega$  (標準)

- ゲートスイッチングスピードの最適化

- ullet 取り扱いが簡単なエンハンスメントタイプ:  $V_{th}=2.7{\sim}3.7~V~(V_{DS}=10~V,~I_D=1~mA)$

## 外観と端子配置

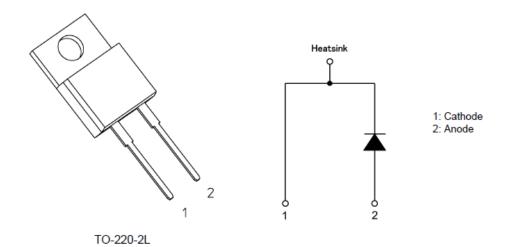

## 4.2. TRS6E65F

## 特徴

大電流サージ耐量: I<sub>FSM</sub> = 55 A (最大)

接合容量が小さい: C<sub>j</sub> = 22 pF (標準)

リーク電流が小さい: I<sub>R</sub> = 0.3 μA (標準)

## 外観と端子配置

© 2019

## 5. シミュレーション回路使用方法

本シミュレーション回路では、実際の仕様に沿った動作や、回路定数に応じた変化を検証する為に、OrCAD® Capture 上で各種パラメータを自由に変更し、動作解析をすることが可能です。本章ではパラメータ設定方法、動作解析方法に関し説明します。本シミュレーション回路は、「RD032-SPICE-02」をダウンロードしフォルダ内の OPJ ファイル (.opj) を開くことで立ち上がります。

## パラメータ設定

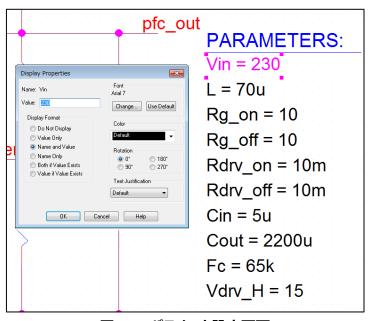

シミュレーション回路で設定可能なパラメータの一覧を表 5.1 に示します。設定の手順としては、パラメータ設定部の変数を ダブルクリックすると、図 5.1 の「Display Properties」ウインドウが表示されますので、その中の「Value」値を変更してください。

| _,       |           |                 |

|----------|-----------|-----------------|

| 変数名      | 単位        | 説明              |

| Vin      | $V_{rms}$ | AC 入力電圧         |

| Fin      | Hz        | AC 入力周波数        |

| Vout     | V         | PFC 出力電圧        |

| L        | Η         | ブーストインダクタの部品定数  |

| DCR      | Ω         | インダクタの寄生抵抗値     |

| Cin      | F         | 入力コンデンサの部品定数    |

| Cout     | F         | 出力コンデンサの部品定数    |

| Fc       | Hz        | スイッチング周波数       |

| Rg_on    | Ω         | ターンオン側外付けゲート抵抗値 |

| Rg_off   | Ω         | ターンオフ時外付けゲート抵抗値 |

| Rdrv_on  | Ω         | ゲートドライバのオン側抵抗値  |

| Rdrv_off | Ω         | ゲートドライバのオフ側抵抗値  |

| Vdrv_H   | V         | ゲートドライバの電源電圧    |

表 5.1 パラメータ設定部で設定可能な変数一覧

図 5.1 パラメータ設定画面

## 解析設定方法

本シミュレーション回路のシミュレーション実行の手順を下記に説明します。

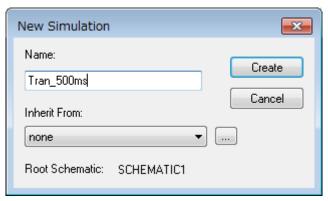

(1) メニューバー上の「PSpice」-「New Simulation Profile」をクリックすると、図 5.2 の「New Simulation」ウインドウが表示されます。任意のプロファイル名を指定し、「Create」をクリックしてください。

図 5.2 「New Simulation」画面

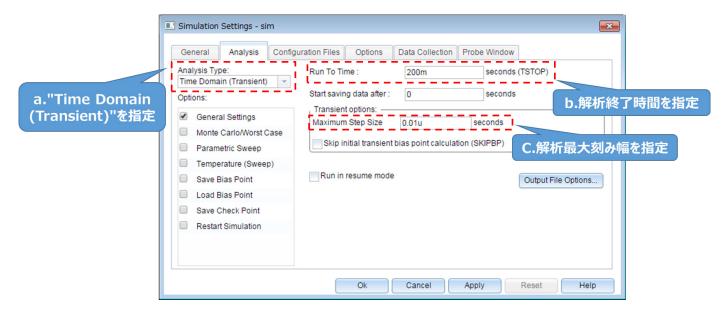

(2) (1)の手順後、図 5.3 の「Simulation Settings」ウインドウが表示され、各種解析設定が可能になります。まずは「Analysis」タブにて解析方法の設定を行います。「Analysis Type」は「Time Domain (Transient)」を指定してください。「Run To Time」で解析終了時間を指定し、「Maximum Step Size」にて解析における最大刻み幅を指定してください。

図 5.3 「Simulation Settings」-「Analysis」画面

Rev.2

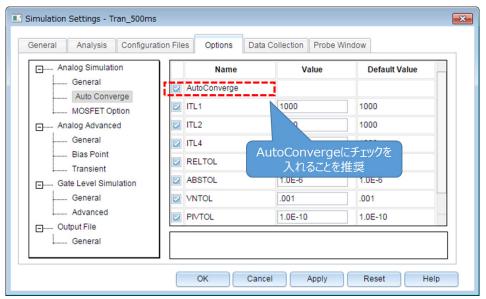

(3) 「Options」タブにて解析オプションの設定を行います。本モデルでのシミュレーションにおいては、「Analog Simulation」 -「Auto Converge」-「AutoConverge」にチェックをいれ、自動収束機能を有効にすることを推奨します。 (図 5.4)

図 5.4 「Simulation Settings」-「Options」画面

- (4) 上記設定が完了したら、「OK」をクリックし、「Simulation Settings」ウインドウを閉じてください。

- (5) メニューバーの「PSpice」-「Run」でシミュレーションを実行します。PSpice® A/D が自動で起動し、シミュレーションが実行されます。

## 結果確認方法

シミュレーション完了後の結果確認方法について説明します。PSpice® A/D 画面上に結果波形を表示する方法として、2 通りの方法があります。下記に各方法の手順について説明します。

## 方法1. ネット名を指定した結果表示

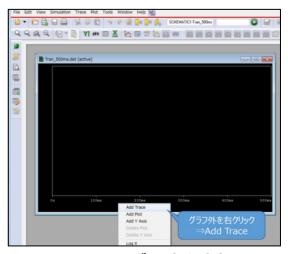

- (1) グラフウインドウのグラフ枠外を右クリック後、「Add Traces」を選択してください。(図 5.5)

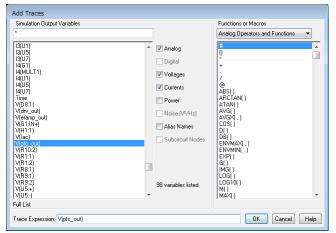

- (2) 「Add Traces」画面から表示する波形を選択します。電圧波形の場合には V(ネット名)、電流波形の場合には I(素子名)を選択してください。(図 5.6)

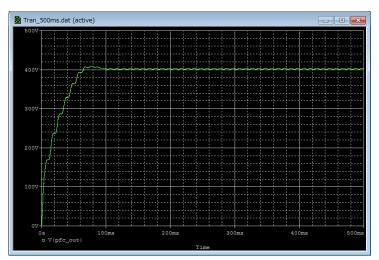

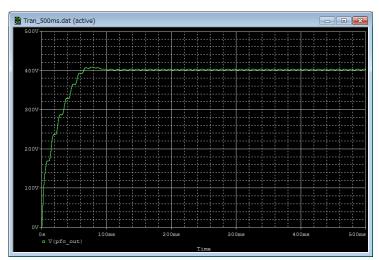

- (3) 選択後、「OK」をクリックすることで結果波形が表示されます。 (図 5.7)

図 5.5 グラフウインドウ

図 5.6 「Add Traces」画面

図 5.7 結果波形表示 (例: PFC 出力電圧波形)

## 方法 2. Marker 機能を使用した結果表示

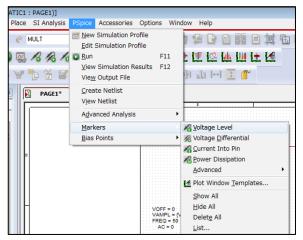

- (1) OrCAD<sup>®</sup> Capture メニューバーの「PSpice」-「Markers」から、表示させる波形に応じて Marker 種類を選択します。 (図 5.8)

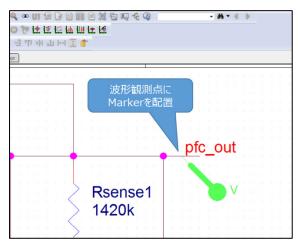

- (2) シミュレーション回路上の波形観測ポイントに Marker を配置します。 (図 5.9)

- (3) PSpice® A/D のグラフウインドウに結果波形が表示されます。 (図 5.10)

図 5.8 Marker 種類選択画面

図 5.9 回路上への Marker 配置

図 5.10 結果波形表示 (例: PFC 出力電圧波形)

※Cadence、Cadence ロゴ、OrCAD、PSpice および OrCAD ロゴは Cadence Design Systems, Inc.の米国 またはその他の国における商標または登録商標です。

© 2019

## ご利用規約

本規約は、お客様と東芝デバイス&ストレージ株式会社(以下「当社」といいます)との間で、当社半導体製品を搭載した機器を設計する際に参考となるドキュメント及びデータ(以下「本リファレンスデザイン」といいます)の使用に関する条件を定めるものです。お客様は本規約を遵守しなければなりません。本リファレンスデザインをダウンロードすることをもって、お客様は本規約に同意したものとみなされます。なお、本規約は変更される場合があります。当社は、理由の如何を問わずいつでも本規約を解除することができます。本規約が解除された場合は、お客様は、本リファレンスデザインを破棄しなければなりません。またお客様が本規約に違反した場合は、お客様は、本リファレンスデザインを破棄したことを証する書面を当社に提出しなければなりません。

#### 第1条 禁止事項

お客様の禁止事項は、以下の通りです。

- 1. 本リファレンスデザインは、機器設計の参考データとして使用されることを意図しています。信頼性検証など、それ以外の目的には使用しないでください。

- 2. 本リファレンスデザインを販売、譲渡、貸与等しないでください。

- 3. 本リファレンスデザインは、高低温・多湿・強電磁界などの対環境評価には使用できません。

- 4. 本リファレンスデザインを、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用しないでください。

#### 第2条 保証制限等

- 1. 本リファレンスデザインは、技術の進歩などにより予告なしに変更されることがあります。

- 2. 本リファレンスデザインは参考用のデータです。当社は、データおよび情報の正確性、完全性に関して一切の保証をいたしません。

- 3. 半導体素子は誤作動したり故障したりすることがあります。本リファレンスデザインを参考に機器設計を行う場合は、誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うことをお願いします。また、使用されている半導体素子に関する最新の情報(半導体信頼性ハンドブック、仕様書、データシート、アプリケーションノートなど)をご確認の上、これに従ってください。

- 4. 本リファレンスデザインを参考に機器設計を行う場合は、システム全体で十分に評価し、お客様の責任において適用可否を判断して下さい。当社は、適用可否に対する責任は負いません。

- 5. 本リファレンスデザインは、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 6. 当社は、本リファレンスデザインに関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をせず、また当社は、本リファレンスデザインに関する一切の損害(間接損害、結果的損害、特別損害、付随的損害、逸失利益、機会損失、休業損、データ喪失等を含むがこれに限らない。)につき一切の責任を負いません。

#### 第3条 輸出管理

お客様は本リファレンスデザインを、大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他軍事用途の目的で使用してはなりません。また、お客様は「外国為替及び外国貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守しなければなりません。

#### 第4条 準拠法

本規約の準拠法は日本法とします。