# TPD7104AF Application note

# **Description**

TPD7104AF is a high-side gate driver IC for N-channel MOSFETs with 12 V power supply. The MOSFET is driven by an internal charge pump circuit. By selecting the optimum MOSFET for the operating condition, a high-side switch with suitable specifications can be configured for systems handling a wide range of currents. This IC is equipped with a power reverse connection protection function in addition to a load short protection function and a diagnostic function, all of which contribute to improved system safety. Additionally, it is available in a compact PS-8 surface-mount package (2.9 mm \* 2.8 mm), enabling system miniaturization.

# **Table of Contents**

| Description                                                                                          | 1  |

|------------------------------------------------------------------------------------------------------|----|

| Table of Contents                                                                                    | 2  |

| 1. Product overview                                                                                  | 5  |

| 2. Application circuit example                                                                       | 5  |

| 2.1. Application example of load switch circuit (disable reverse polarity protection)                | 5  |

| 2.2. Application example of reverse polarity protection circuit (enable reverse polarity protection) | 6  |

| 3. Terminal equivalent circuit                                                                       | 7  |

| 4. Normal operation                                                                                  | 8  |

| 5. Description of each function or circuit                                                           | 9  |

| 5.1. Reverse polarity protection function                                                            | 9  |

| 5.2. Load short (overcurrent) protection function                                                    | 10 |

| 5.3. Charge pump circuit                                                                             | 13 |

| 5.4. Charge pump voltage monitor circuit                                                             | 16 |

| 5.5. V <sub>DD</sub> pin overvoltage protection circuit                                              | 16 |

| 6. Electrical characteristics measurement circuit                                                    | 17 |

| 7. Definition and terminology                                                                        | 21 |

| 7.1. Absolute maximum rating                                                                         | 21 |

| 7.2. Electrical characteristics                                                                      | 22 |

| 8. Evaluation board                                                                                  | 24 |

| 8.1. Appearance of evaluation board                                                                  | 24 |

| 8.2. Circuit diagram for evaluation board                                                            | 25 |

| 8.3. Bill of materials                                                                               | 26 |

| 8.4. Board layout                                                                                    | 27 |

| Points to note in the description                                                                    | 28 |

| IC usage consideration                                                                               | 28 |

| Notes on handing of ICs                                                                              | 28 |

| RESTRICTIONS ON PRODUCT USE                                                                          | 29 |

# **List of Figures**

| Fig. 2.1  | Block diagram (load switch circuit)                                                        | 5  |

|-----------|--------------------------------------------------------------------------------------------|----|

| Fig. 2.2  | Block diagram (reverse polarity protection)                                                | 6  |

| Fig. 3.1  | Equivalent circuit of V <sub>DD</sub> pin                                                  | 7  |

| Fig. 3.2  | Equivalent circuit of IS and R <sub>ISref</sub> pins                                       | 7  |

| Fig. 3.3  | Equivalent circuit of OUT pin                                                              | 7  |

| Fig. 3.4  | Equivalent circuit of SUB and GND pins                                                     | 7  |

| Fig. 3.5  | Equivalent circuit of IN pin                                                               | 7  |

| Fig. 3.6  | Equivalent circuit of DIAG pin                                                             | 7  |

| Fig. 4.1  | Timing chart of normal operation                                                           | 8  |

| Fig. 5.1  | Reverse polarity protection                                                                | 9  |

| Fig. 5.2  | Load short detection                                                                       | 10 |

| Fig. 5.3  | V <sub>RISref</sub> - R <sub>IS</sub>                                                      | 11 |

| Fig. 5.4  | Relationship between V <sub>RISref</sub> and V <sub>ISOC</sub>                             | 11 |

| Fig. 5.5  | Timing chart of load short detection operation                                             | 12 |

| Fig. 5.6  | Charge pump equivalent circuit                                                             | 13 |

| Fig. 5.7  | Charge pump circuit operation                                                              | 14 |

| Fig. 5.8  | Operation waveforms of each node in charge pump circuit                                    | 15 |

| Fig. 5.9  | Charge pump voltage monitor circuit                                                        | 16 |

| Fig. 5.10 | V <sub>DD</sub> pin overvoltage protection circuit                                         | 16 |

| Fig. 5.11 | Image of V <sub>DD</sub> pin overvoltage protection operation                              | 16 |

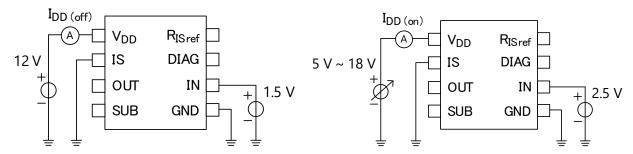

| Fig. 6.1  | Supply current IDD(off) measurement circuit                                                | 17 |

| Fig. 6.2  | Supply current I <sub>DD(on)</sub> measurement circuit                                     | 17 |

| Fig. 6.3  | High-level input voltage V <sub>IH</sub> measurement circuit                               | 17 |

| Fig. 6.4  | Low-level input voltage V <sub>IL</sub> measurement circuit                                | 17 |

| Fig. 6.5  | Input current I <sub>IH</sub> measurement circuit                                          | 17 |

| Fig. 6.6  | Input current I <sub>IL</sub> measurement circuit                                          | 17 |

| Fig. 6.7  | Output voltage V <sub>OUT1,2</sub> measurement circuit                                     | 18 |

| Fig. 6.8  | Output clamp voltage V <sub>clamp</sub> measurement circuit                                | 18 |

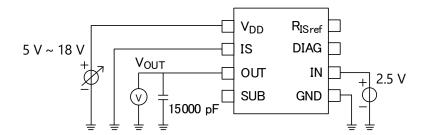

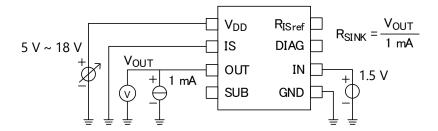

| Fig. 6.9  | Output resistance R <sub>SINK</sub> measurement circuit                                    | 18 |

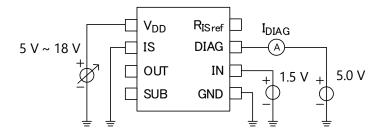

| Fig. 6.10 | Diagnosis output leakage current IDIAGH measurement circuit                                | 18 |

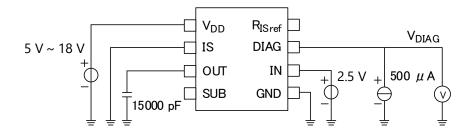

| Fig. 6.11 | Diagnosis output voltage V <sub>DIAGL</sub> measurement circuit                            | 19 |

| Fig. 6.12 | Short circuit detection voltage V <sub>ISOC</sub> measurement circuit                      | 19 |

| Fig. 6.13 | R <sub>ISref</sub> pin output current I <sub>ISref(1),(2),(3)</sub> measurement circuit    | 19 |

| Fig. 6.14 | Switching time ton, toff measurement circuit                                               | 19 |

| Fig. 6.15 | Output current under reverse power connection I <sub>REV(1), (2)</sub> measurement circuit | 20 |

| Fig. 8.1  | TPD7104AF evaluation board                                                                 | 24 |

| Fig. 8.2  | Circuit diagram of TPD7104AF evaluation board                                              | 25 |

| Fig. 8.3  | Layout of TPD7104AF evaluation board                                                       | 27 |

# **List of Tables**

| Table 4.1 Truth table of normal operation               |    |

|---------------------------------------------------------|----|

|                                                         |    |

| Table 5.1 Truth table of load short detection operation | 11 |

| Table 8.1 BOM list                                      | 26 |

#### 1. Product overview

The TPD7104AF is a high-side gate driver IC for N-channel MOSFETs, designed for applications such as semiconductor relays and load switches. By selecting the most suitable MOSFET for the system, the IC can accommodate a wide range of applications. This IC incorporates power reverse connection protection and load short-circuit (overcurrent) detection circuits.

# 2. Application circuit example

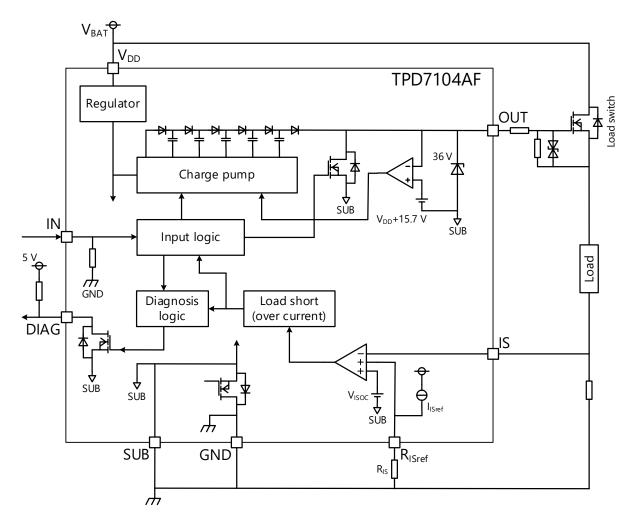

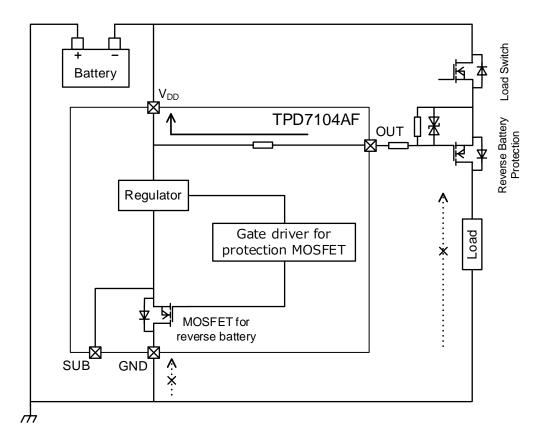

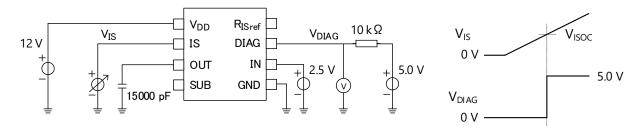

#### 2.1. Application example of load switch circuit (disable reverse polarity protection)

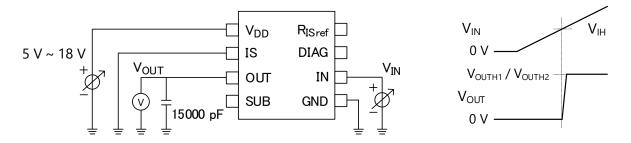

Fig. 2.1 Block diagram (load switch circuit)

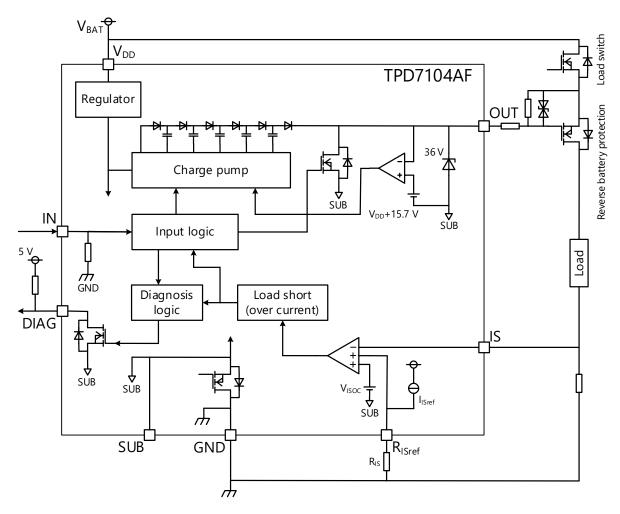

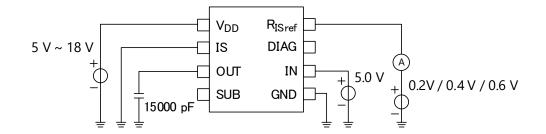

# 2.2. Application example of reverse polarity protection circuit (enable reverse polarity protection)

Fig. 2.2 Block diagram (reverse polarity protection)

# 3. Terminal equivalent circuit

Fig. 3.1 Equivalent circuit of  $V_{DD}$  pin

Fig. 3.2 Equivalent circuit of IS and R<sub>ISref</sub> pins

Fig. 3.3 Equivalent circuit of OUT pin

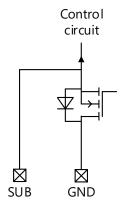

Fig. 3.4 Equivalent circuit of SUB and GND pins

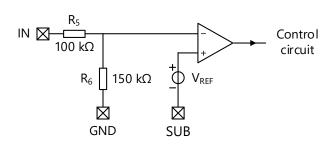

Fig. 3.5 Equivalent circuit of IN pin

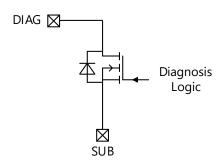

Fig. 3.6 Equivalent circuit of DIAG pin

#### 4. Normal operation

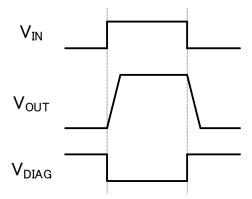

TPD7104AF controls the output voltage at the OUT pin according to the input level at the IN pin, thereby driving an external N-channel MOSFET. When  $V_{IN} = V_{IL}$ , the OUT pin outputs Low, turning off the external N-channel MOSFET, and the DIAG pin outputs High. When  $V_{IN} = V_{IH}$ , the OUT pin outputs High, turning on the external N-channel MOSFET, and the DIAG pin outputs Low. Ensure that the voltage at the  $V_{DD}$  pin remains within the operating range (5 V to 18 V) during operation.

VIN

VOUT

VDIAG

External N-channel MOSFET

L

L

H (Note)

OFF

H

H

L

ON

Table 4.1 Truth table of normal operation

Note: The DIAG output is configured as an N-channel open-drain MOSFET. When  $V_{\text{DIAG}}$  is 'H', the MOSFET is OFF.

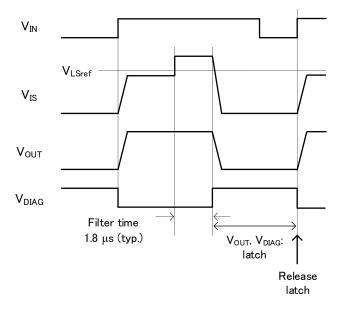

Fig. 4.1 Timing chart of normal operation

#### 5. Description of each function or circuit

#### 5.1. Reverse polarity protection function

TPD7104AF is equipped with a reverse polarity protection function. This function prevents current from flowing into the IC from the GND pin when the power supply is connected in reverse, thereby protecting the IC. In this case, ensure that the voltage at each pin does not exceed the absolute maximum ratings. In addition, since the OUT pin is pulled down to the  $V_{DD}$  pin through an internal resistor, the external N-channel MOSFET remains off. When using this function, leave the SUB pin open. If this function is not used, short the SUB pin and the GND pin externally.

Fig. 5.1 Reverse polarity protection

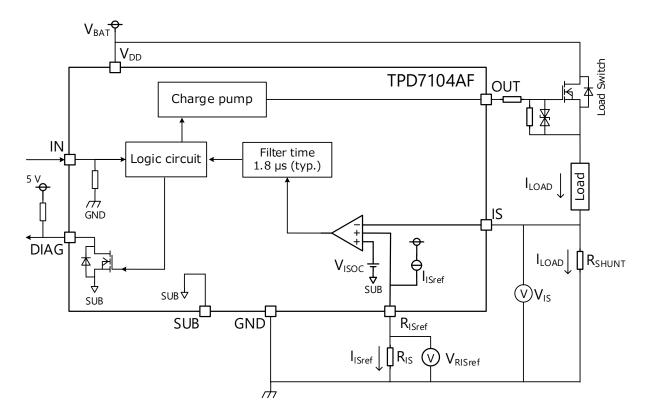

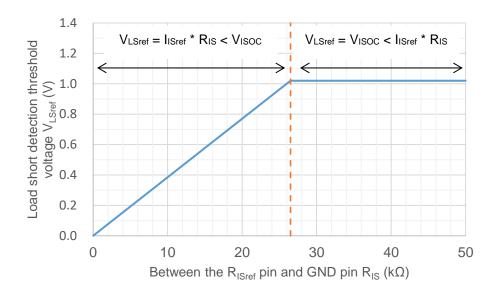

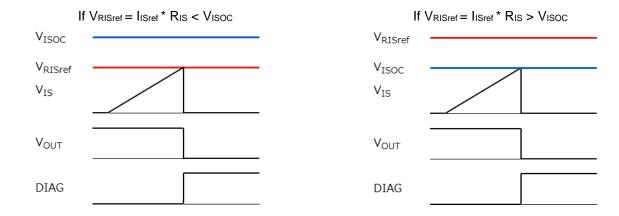

#### 5.2. Load short (overcurrent) protection function

TPD7104AF is equipped with a load short (overcurrent) protection function. This function latches VOUT output to Low, turns off the external N-channel MOSFET, and latches  $V_{DIAG}$  to High if  $V_{IS}$  remains at or above the load short detection voltage threshold  $V_{LSref}$  for the filter time of 1.8  $\mu$ s (typical).  $V_{IS}$  is generated by passing the load current ( $I_{LOAD}$ ) through the shunt resistor ( $R_{SHUNT}$ ) inserted between the IS pin and GND. The threshold value  $V_{LSref}$  is determined as the smaller of the following two values: (1)  $V_{ISOC}$  (1.02  $V_{ISOC}$ ), which is a fixed voltage generated internally in the IC, and (2)  $V_{RISref}$  (the voltage at the  $R_{ISref}$  pin), which is the product of the resistance  $R_{IS}$  (variable) inserted between the  $R_{ISref}$  pin and GND and the internally generated current  $I_{ISref}$  (a fixed value of 38  $\mu$ A (typ.)). If (2) is not used, leave the  $R_{ISref}$  pin open. To release the latch, set  $V_{IN}$  from  $V_{IL}$  to  $V_{IH}$ . In addition, if this function is not used, short the IS pin to GND.

The load short detection current threshold can be calculated using the following (Eq. 5-1) to (Eq. 5-2-2).

(1) When the R<sub>ISref</sub> pin is left open:

Load short detection current threshold =

$$\frac{V_{ISOC}}{R_{SHUNT}}$$

(Eq. 5-1)

(2) When a resistor is connected to the R<sub>ISref</sub> pin:

Load short detection current threshold =

$$\frac{V_{RISref}}{R_{SHIINT}}$$

(Eq. 5-2-1)

(2 - 2) If V<sub>ISOC</sub> < V<sub>RISref</sub> (= I<sub>ISref</sub> \* R<sub>IS</sub>):

Load short detection current threshold =

$$\frac{V_{ISOC}}{R_{SHIINT}}$$

(Eq.5-2-2)

Fig. 5.2 Load short detection

| V <sub>IN</sub> | V <sub>IS</sub>      | V <sub>OUT</sub> | V <sub>DIAG</sub> | External<br>N-channel MOSFET | Notes                          |

|-----------------|----------------------|------------------|-------------------|------------------------------|--------------------------------|

| Н               | < V <sub>LSref</sub> | Н                | L                 | ON                           | Normal operation               |

| Н               | > V <sub>LSref</sub> | L (latch)        | H (latch)         | OFF                          | Load short detection operation |

Fig. 5.3 V<sub>RISref</sub> - R<sub>IS</sub>

Fig. 5.4 Relationship between  $V_{\text{RISref}}$  and  $V_{\text{ISOC}}$

Fig. 5.5 Timing chart of load short detection operation

#### 5.3. Charge pump circuit

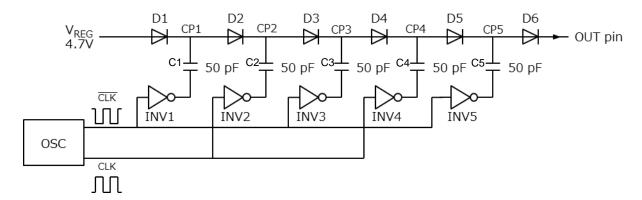

The charge pump circuit is a boost power supply circuit for generating the gate-driving voltage of an external N-channel MOSFET. For high-side switches, when the external N-channel MOSFET is turned on, the source potential becomes nearly equal to the supply voltage. Therefore, to maintain the on-state, it is necessary to apply a voltage plus 10 to 15 V to the gate terminal. The charge pump circuit generates this voltage inside the IC. TPD7104AF incorporates a Dickson-type charge pump circuit, which consists of diodes, capacitors, and inverter circuits as shown in Fig. 5.6. The boosted voltage  $V_{CP(OUT)}$  can be calculated using (Eq. 5-3).

Fig. 5.6 Charge pump equivalent circuit

$$V_{CP(OUT)} = N * (V_{REG} - V_F)$$

(Eq. 5-3)

N : Number of stages

V<sub>REG</sub>: Power supply voltage for control circuit (V)

V<sub>F</sub>: Diode forward voltage (V)

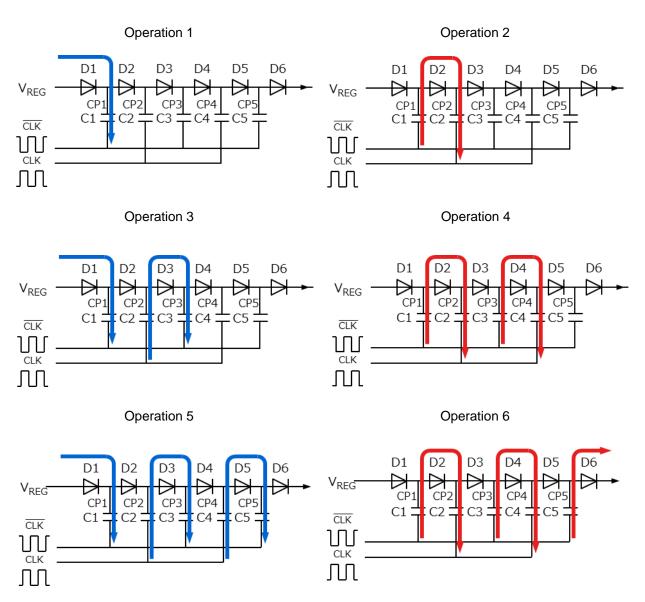

Fig. 5.7 illustrates the operation of the Dickson-type charge pump circuit. Here, it is assumed that the voltage amplitudes of CLK and  $\overline{\text{CLK}}$  are equal to that of  $V_{\text{REG}}$ .

#### Operation 1

When  $\overline{\text{CLK}}$  is at the "L" level, capacitor C1 is charged from  $V_{\text{REG}}$  through diode D1, causing the voltage across C1 to become  $V_{\text{REG}}$  -  $V_{\text{F}}$  and voltage across CP1 swings between  $2V_{\text{REG}}$  -  $V_{\text{F}}$  and  $V_{\text{REG}}$  -  $V_{\text{F}}$ .

#### Operation 2

When  $\overline{\text{CLK}}$  is at the "H" level and CLK is at the "L" level, the charge stored in C1 charges C2 through D2, causing the voltage across C2 to become  $2V_{\text{REG}}$  to  $2V_{\text{F}}$ , and voltage across CP2 swings between  $3V_{\text{REG}}$ - $2V_{\text{F}}$  and  $2V_{\text{REG}}$ - $2V_{\text{F}}$ .

#### Operation 3

When  $\overline{\text{CLK}}$  is at the "L" level and CLK is at the "H" level, the charge stored in C2 charges C3 through D3, causing the voltage across C3 to become  $3V_{\text{REG}}$  to  $3V_{\text{F}}$ , and voltage across CP3 swings between  $4V_{\text{REG}}$  -  $3V_{\text{F}}$  and  $3V_{\text{REG}}$  -  $3V_{\text{F}}$ .

#### Operation 4

When  $\overline{\text{CLK}}$  is at the "H" level and CLK is at the "L" level, the charge stored in C3 charges C4 through D4, causing the voltage across C4 to become  $4V_{REG}$  -  $4V_{F}$ , and voltage across CP4 swings between  $5V_{REG}$  -  $4V_{F}$  and  $4V_{REG}$  -  $4V_{F}$ .

#### Operation 5

When  $\overline{\text{CLK}}$  is at the "L" level and CLK is at the "H" level, the charge stored in C4 charges C5 through D5, causing the voltage across C5 to become  $5V_{REG}$  -  $5V_{F}$ , and voltage across CP5 swings between  $6V_{REG}$  -  $5V_{F}$  and  $5V_{REG}$  -  $5V_{F}$ .

#### Operation 6

The charge stored in C5 drives the gate of the external N-channel MOSFET with the voltage that is eventually boosted to 6 \* (V<sub>REG</sub> - V<sub>F</sub>) through D6.

Fig. 5.7 Charge pump circuit operation

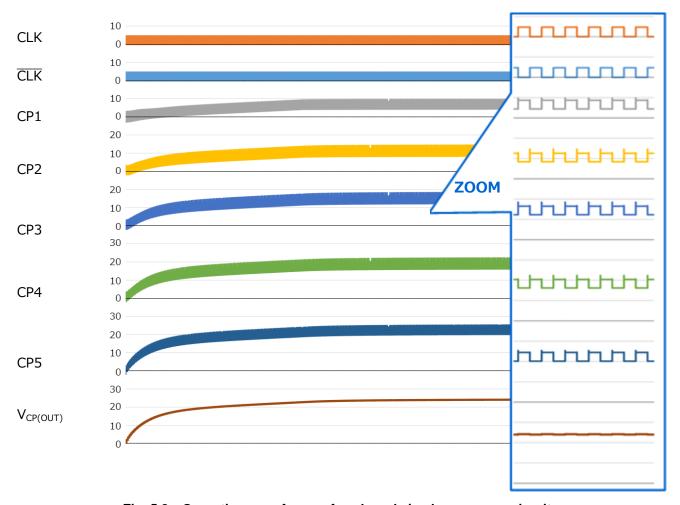

The voltage waveforms at the nodes of the charge pump circuit are as shown in Fig. 5.8. When  $V_{REG} = 4.7 \text{ V}$  and  $V_F = 0.7 \text{ V}$ , the output voltage calculated from (Eq. 5-3) becomes  $V_{CP(OUT)} = 24 \text{ V}$ , which is almost the same as the  $V_{CP(OUT)}$  value shown in Fig. 5.8.

Fig. 5.8 Operation waveforms of each node in charge pump circuit

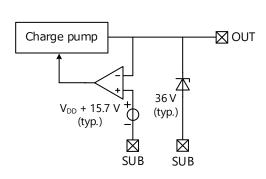

#### 5.4. Charge pump voltage monitor circuit

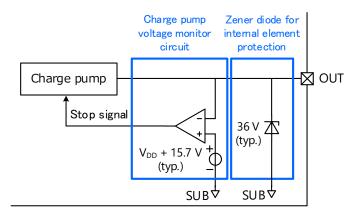

TPD7104AF incorporates a charge pump voltage monitor circuit inside the OUT pin. This circuit stops the charge pump operation to protect the external N-channel MOSFET if the charge pump output voltage rises above  $V_{DD}$  + 15.7 V (typ.) due to external noise or other factors. A 36 V (typ.) Zener diode is also incorporated between the OUT and the SUB pins to protect the internal elements.

Fig. 5.9 Charge pump voltage monitor circuit

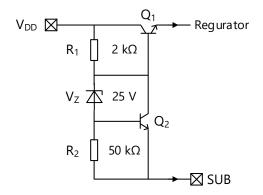

#### 5.5. V<sub>DD</sub> pin overvoltage protection circuit

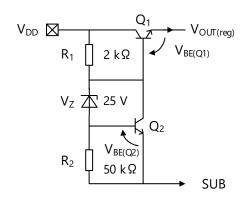

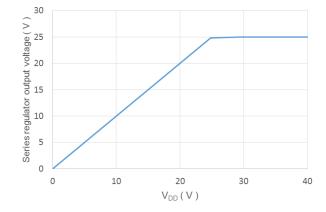

TPD7104AF incorporates a series regulator, as shown in Figure 5.10, inside the  $V_{DD}$  pin to protect the internal elements when an overvoltage is applied to the  $V_{DD}$  pin. The output voltage of this regulator can be calculated using (Eq. 5-4). The power supply voltage for each control circuit is provided from the power supply for the control circuits connected to the subsequent stage through this regulator. When  $V_{DD}$  rises above 25 V, the output voltage of the series regulator is clamped at approximately 25 V, as shown in Figure 5.11.

$$V_{OUT(reg)} \approx V_Z + V_{BE(Q2)} - V_{BE(Q1)}$$

(Eq. 5-4)

Fig. 5.10 V<sub>DD</sub> pin overvoltage protection circuit

Fig. 5.11 Image of V<sub>DD</sub> pin overvoltage protection operation

#### 6. Electrical characteristics measurement circuit

Fig. 6.1 Supply current I<sub>DD(off)</sub> measurement circuit

Fig. 6.2 Supply current I<sub>DD(on)</sub> measurement circuit

Fig. 6.3 High-level input voltage V<sub>IH</sub> measurement circuit

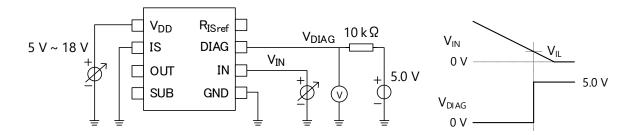

Fig. 6.4 Low-level input voltage  $V_{IL}$  measurement circuit

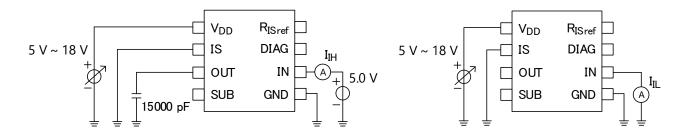

Fig. 6.5 Input current I<sub>IH</sub> measurement circuit

Fig. 6.6 Input current I<sub>IL</sub> measurement circuit

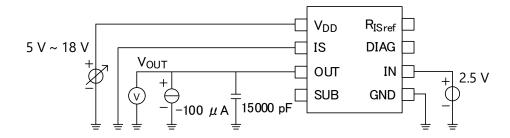

Fig. 6.7 Output voltage V<sub>OUT1,2</sub> measurement circuit

Fig. 6.8 Output clamp voltage V<sub>clamp</sub> measurement circuit

Fig. 6.9 Output resistance R<sub>SINK</sub> measurement circuit

Fig. 6.10 Diagnosis output leakage current IDIAGH measurement circuit

Fig. 6.11 Diagnosis output voltage V<sub>DIAGL</sub> measurement circuit

Fig. 6.12 Short circuit detection voltage V<sub>ISOC</sub> measurement circuit

Fig. 6.13 R<sub>ISref</sub> pin output current I<sub>ISref(1),(2),(3)</sub> measurement circuit

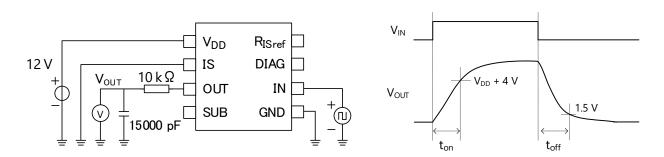

Fig. 6.14 Switching time ton, toff measurement circuit

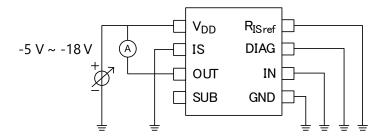

Fig. 6.15 Output current under reverse power connection I<sub>REV(1), (2)</sub> measurement circuit

# 7. Definition and terminology

# 7.1. Absolute maximum rating

| Term                            | Symbol               | Description                                                                                                                                                                                                                                              |

|---------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage (DC)       | V <sub>DD(1)</sub>   | DC voltage rating applied to the $V_{\text{DD}}$ pin ensuring no IC destruction, characteristic degradation, or reliability deterioration.                                                                                                               |

| Power supply voltage (pulse)    | V <sub>DD(2)</sub>   | Pulse voltage rating applied to the $V_{\text{DD}}$ pin ensuring no IC destruction, characteristic degradation, or reliability deterioration.                                                                                                            |

| Power supply reverse connection | - V <sub>DD(3)</sub> | Voltage rating applied to the $V_{DD}$ pin ensuring no IC destruction, characteristic degradation, or reliability deterioration, even when a positive power supply is applied to the GND pin and a negative power supply is applied to the $V_{DD}$ pin. |

| Input voltage                   | VIN                  | Voltage rating applied to the IN pin ensuring no IC destruction, characteristic degradation, or reliability deterioration.                                                                                                                               |

| Output source current           | I <sub>OUT(-)</sub>  | Current rating applied to the OUT pin (source current) ensuring no IC destruction, characteristic degradation, or reliability deterioration.                                                                                                             |

| Output sink current             | I <sub>OUT(+)</sub>  | Current rating applied to the OUT pin (sink current) ensuring no IC destruction, characteristic degradation, or reliability deterioration.                                                                                                               |

| IS pin Voltage                  | Vis                  | Voltage rating applied to the IS pin ensuring no IC destruction, characteristic degradation, or reliability deterioration.                                                                                                                               |

| Diagnosis output voltage        | $V_{DIAG}$           | Voltage rating applied to the DIAG pin ensuring no IC destruction, characteristic degradation, or reliability deterioration.                                                                                                                             |

| Diagnosis pin current           | I <sub>DIAG</sub>    | Current rating applied to the DIAG pin ensuring no IC destruction, characteristic degradation, or reliability deterioration.                                                                                                                             |

| Power dissipation               | $P_D$                | Maximum allowable power dissipation throughout the operating range, ensuring no IC damage.                                                                                                                                                               |

| Operating temperature           | $T_{opr}$            | Ambient temperature range required for proper IC operation.                                                                                                                                                                                              |

| Junction temperature            | Tj                   | Maximum allowable junction temperature during IC operation.                                                                                                                                                                                              |

| Storage temperature             | $T_{stg}$            | Ambient temperature range for storage or transportation without applied voltage applied to IC.                                                                                                                                                           |

#### 7.2. Electrical characteristics

| Term                                  | Symbol               | Description                                                                                                                                                                                |

|---------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating supply voltage              | V <sub>DD(opr)</sub> | The supply voltage range that guarantees the normal operation and electrical characteristics of this IC within the specified junction temperature range.                                   |

| Supply current                        | I <sub>DD(off)</sub> | The current flowing into the $V_{DD}$ pin when the IC is turned off by setting $V_{IN}$ to $V_{IL}$ within the specified junction temperature range.                                       |

| Supply current                        | I <sub>DD(on)</sub>  | The current flowing into the $V_{DD}$ pin when the IC is turned on by setting $V_{IN}$ to $V_{IH}$ within the specified junction temperature range.                                        |

| High level input voltage              | Vıн                  | The voltage at the IN pin that ensures the internal control circuit operates normally and the external N-channel MOSFET turns on within the specified junction temperature range.          |

| Low level input voltage               | VIL                  | The voltage at the IN pin that ensures the internal control circuit operates normally and the external N-channel MOSFET turns off within the specified junction temperature range.         |

| Input current                         | Іін                  | The current flowing into the IN pin when the voltage specified in the measurement condition is applied to the IN pin within the specified junction temperature range.                      |

| Input current                         | Iı∟                  | The current flowing into the IN pin when the voltage specified in the measurement condition is applied to the IN pin within the specified junction temperature range.                      |

| High level output<br>voltage          | Vоитн1<br>Vouth2     | The output voltage at the OUT pin when the voltage and current specified in the measurement conditions are applied within the specified junction temperature range.                        |

| Output clamp voltage                  | $V_{clamp}$          | The clamp voltage at the OUT pin when the voltage specified in the measurement conditions is applied within the specified junction temperature range.                                      |

| Output resistance                     | Rsink                | The resistance value between the OUT pin and the GND pin when the voltage and current specified in the measurement conditions are applied within the specified junction temperature range. |

| Diagnostic output<br>leakage current  | Idiagh               | The leakage current flowing into the DIAG pin when the voltage specified in the measurement conditions is applied within the specified junction temperature range.                         |

| Diagnostic output<br>voltage          | Vdiagl               | The on-voltage at the DIAG pin when the voltage and current specified in the measuring conditions are applied within the specified junction temperature range.                             |

| Short circuit detection voltage       | Visoc                | The reference voltage for load short detection inside the IC when the voltage specified in the measurement conditions is applied within the specified junction temperature range.          |

| R <sub>ISref</sub> pin output current | <b>I</b> ISref       | The current flowing into the R <sub>ISref</sub> pin when the voltage specified in the measurement conditions is applied within the specified junction temperature range.                   |

| Term                                  | Symbol                                     | Description                                                                                                                                                       |  |  |  |

|---------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Switching time                        | ton<br>toff                                | ton: delay time from $V_{IN} = V_{IH}$ (rising) to $V_{OUT} = V_{DD} + 4 V$ toff: delay time from $V_{IN} = V_{IL}$ (falling) to $V_{OUT} = 1.5 V$                |  |  |  |

| Output current for reverse connection | I <sub>REV(1)</sub><br>I <sub>REV(2)</sub> | The value of current flowing into the OUT pin when the voltage specified by the measurement condition is applied within the specified junction temperature range. |  |  |  |

#### 8. Evaluation board

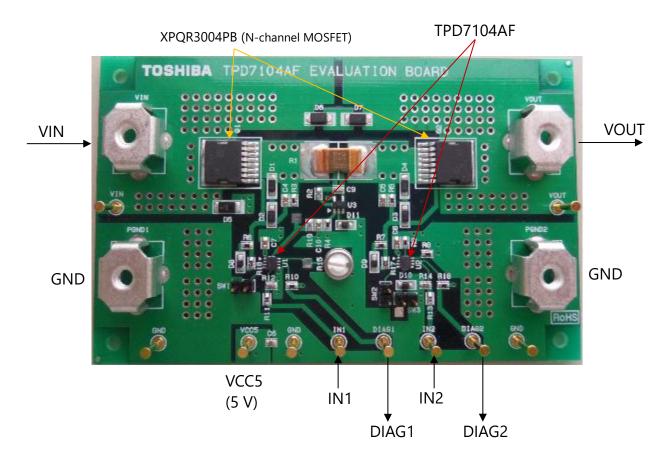

#### 8.1. Appearance of evaluation board

We provide this product along with an evaluation board equipped with peripheral devices. By using this board, you can check the operation and the protection diagnosis function when using an actual load.

Fig. 8.1 TPD7104AF evaluation board

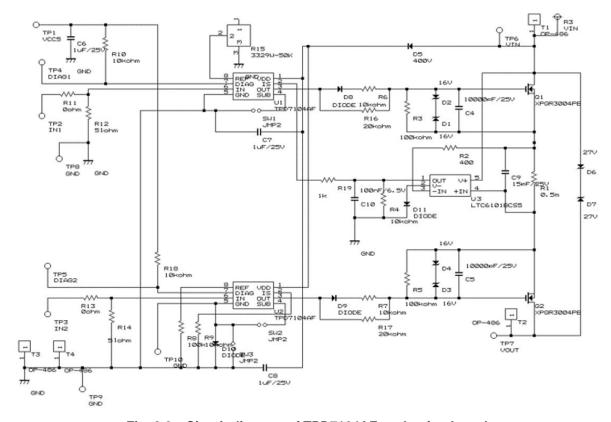

# 8.2. Circuit diagram for evaluation board

Fig. 8.2 Circuit diagram of TPD7104AF evaluation board

#### 8.3. Bill of materials

Table 8.1 BOM list

| No. | item      | p/n                | maker           | spec.                | location                       | PKG     | QTY | Note. |

|-----|-----------|--------------------|-----------------|----------------------|--------------------------------|---------|-----|-------|

| 1   | IC        | TPD7104AF          | Toshiba         | driver IC            | U1, U2                         | PS-8    | 2   |       |

| 2   |           | LTC6101HVACS5      | LT              | sense amp.           | U3                             | TSOT-23 | 1   |       |

| 3   | Power MOS | XPQR3004PB         | Toshiba         | Nch / 40V            | Q1, Q2                         | L-TOGL  | 2   |       |

| 4   | R         | BVS-M-R0005-1.0    | Isabellenhuette | 0.5 mΩ               | R1                             |         | 1   |       |

| 5   |           |                    |                 | 300 Ω                | R2                             | 1608    | 1   |       |

| 6   |           | ERJP03F1003V       | Panasonic       | 100 kΩ               | R3, R5,<br>R8                  | 1608    | 3   |       |

| 7   |           | ERJP03F1002V       | Panasonic       | 10 kΩ                | R4, R6,<br>R7, R9,<br>R10, R18 | 1608    | 5   |       |

| 8   |           | ERJ3GEY0R00V       | Panasonic       | 0 Ω                  | R11, R13                       | 1608    | 2   |       |

| 9   |           | RR0816Q-510-D      | Susumu          | 51 Ω                 | R12, R14                       | 1608    | 2   |       |

| 10  |           | 3329H              | BOURNS          | 0 to 50 kΩ           | R15                            | -       | 1   |       |

| 11  |           | CR0603-FX-2002ELF  | BOURNS          | 20 kΩ                | R16, R17                       | 1608    | 2   |       |

| 12  |           |                    |                 | 1 kΩ                 | R19                            | 1608    | 1   |       |

| 13  | O         | GRM155B11E103KA01D | Murata          | 10000pF /<br>25V     | C4, C5                         | 1005    | 2   |       |

| 14  |           | GRM188B31E105KA    | Murata          | 1 μF / 25V           | C6, C7,<br>C8                  | 1608    | 3   |       |

| 15  |           | C0603CH1E150J      | TDK             | 15pF / 25V           | C9                             | 0603    | 1   |       |

| 16  |           |                    |                 | 100 nF               | C10                            | 1608    | 1   |       |

| 17  | TP        | ST2-2-2            |                 |                      | TP1 to<br>TP10                 |         | 10  |       |

| 18  | D         | CRZ16              | Toshiba         | 16 V Zdi             | D1 to D4                       | S-FLAT  | 4   |       |

| 19  |           | CMG06A             | Toshiba         | 400 V / 1A           | D5                             | M-FLAT  | 1   |       |

| 20  |           | CMZ27              | Toshiba         | 27V / 1W             | D6, D7                         | S-FLAT  | 2   |       |

| 21  |           | 1SS352             | Toshiba         | 80 V / 100<br>mA     | D8 to D11                      | SOD-323 | 4   |       |

| 22  | terminal  | OP-486             | Osada           | 40 A DC max          | T1 to T4                       |         | 4   |       |

| 23  | jumper    | XJ8T               | Omron           | 2 poles / 2.54<br>mm | SW1 to<br>SW3                  |         | 3   |       |

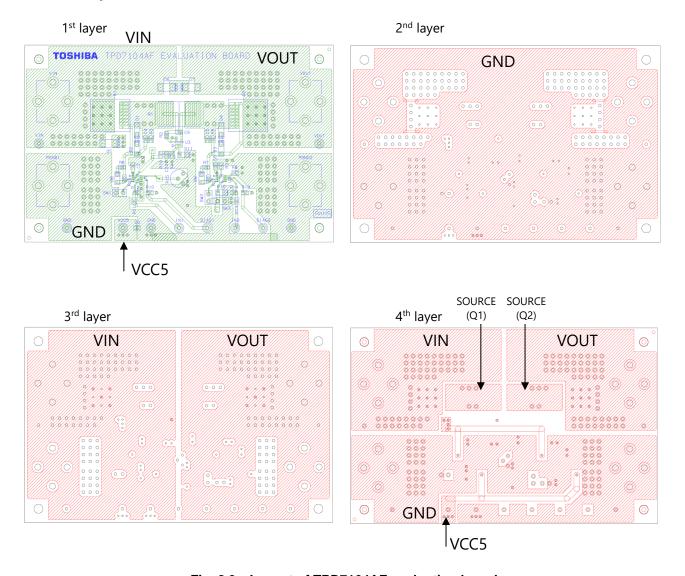

#### 8.4. Board layout

Fig. 8.3 Layout of TPD7104AF evaluation board

#### Points to note in the description

#### 1. Block diagram

Function blocks, circuits, constants, etc. in the block diagram are partially omitted or simplified for explanation of functions.

#### 2. Equivalent circuit

The equivalent circuit may be partially omitted or simplified for explanation of the circuit.

#### 3. Measurement circuit

The measurement circuit may be partially omitted or simplified for explanation of the measurement conditions.

# IC usage consideration

#### Notes on handing of ICs

The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Exceeding the maximum rating may cause destruction, damage, and deterioration, and may result in injury due to explosion or burning.

#### **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE

EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY

CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT

("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation,

equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment,

equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or

explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE,

TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative or contact us via our

website.

- · Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any

infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any

intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR

PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER,

INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING

WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2)

DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR

INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE,

ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for

the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass

destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations

including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export

and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and

regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please

use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including

without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT

OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

# **Toshiba Electronic Devices & Storage Corporation**

https://toshiba.semicon-storage.com/