## **TOSHIBA**

# 32 ビット RISC マイクロコントローラ TX03 シリーズ

TMPM376FDDFG/TMPM376FDFG

株式会社 **東芝** セミコンダクター & ストレージ社

## 改訂履歴

| 日付                 | 版 | 改訂内容             |

|--------------------|---|------------------|

| 2011/12/28         | 1 | First Release    |

| 2013/04/08         | 2 | Contents Revised |

| <b>20</b> 21/10/15 | 3 | Contents Revised |

| <b>20</b> 22/03/31 | 4 | Contents Revised |

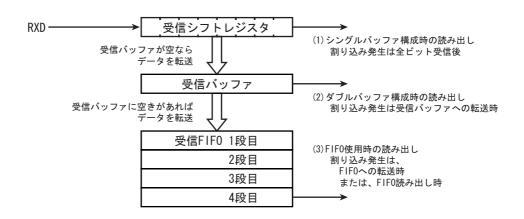

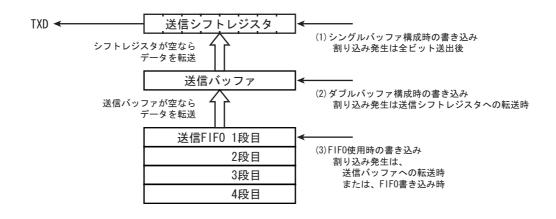

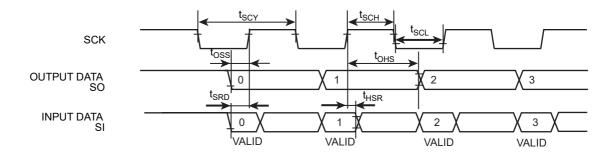

| <b>20</b> 22/06/01 | 5 | Contents Revised |

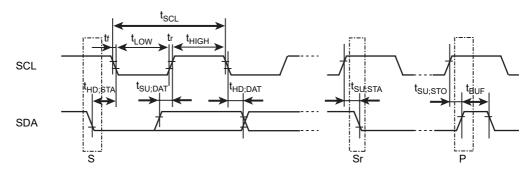

| <b>20</b> 23/07/21 | 6 | Contents Revised |

| <b>20</b> 23/07/31 | 7 | Contents Revised |

ARM, ARM Powered, AMBA, ADK, ARM9TDMI, TDMI, PrimeCell, RealView, Thumb, Cortex, Coresight, ARM9, ARM926EJ-S, Embedded Trace Macrocell, ETM, AHB, APB, and KEIL はARM LimitedのEUおよびその他の国における登録商標または商標です。

## TMPM376FDDFG/FDFG

TMPM376FDDFG/FDFGは、ARM社Cortex™-M3コアを内蔵した32ビットRISCマイクロプロセッサです。

| 製品名          | ROM<br>(FLASH) | RAM      | パッケージ                |

|--------------|----------------|----------|----------------------|

| TMPM376FDDFG | 512 Kbyte      | 32 Kbyte | QFP100-P-1420-0.65Q  |

| TMPM376FDFG  | 512 Kbyte      | 32 Kbyte | LQFP100-P-1414-0.50H |

機能概要と特長は次のとおりです。

### 1.1 機能概要

- 1. ARM 社製 Cortex-M3 コアを使用

- a. Thumb®-2 命令で、コード効率の向上を実現

- ・プログラムフロー改善のための新しい 16 ビット命令

- ・性能とコードサイズ向上のための新しい32ビット命令

- ・32 ビット /16 ビット混在の命令セットでコード効率を向上

- b. 高性能化と低消費電力化を同時に実現

#### 【高性能化】

- ・32 ビット乗算 (32 × 32 = 32 ビット) を 1 クロックで実行

- ・除算を 2~12 クロックで実行

#### 【低消費電力化】

- ・低消費電力ライブラリを使用した最適化設計

- ・プロセッサコアの動作を停止させるスタンバイ機能

- c. リアルタイム制御に向いた高速割り込み応答

- ・実行時間の長い命令は割り込みで中断可能

- ・スタックへの PUSH をハードウエアで自動的に実行

- 2. 内蔵プログラムメモリ/データメモリ

• 内蔵 RAM: 32Kbyte

• 内蔵 FlashROM: 512Kbyte

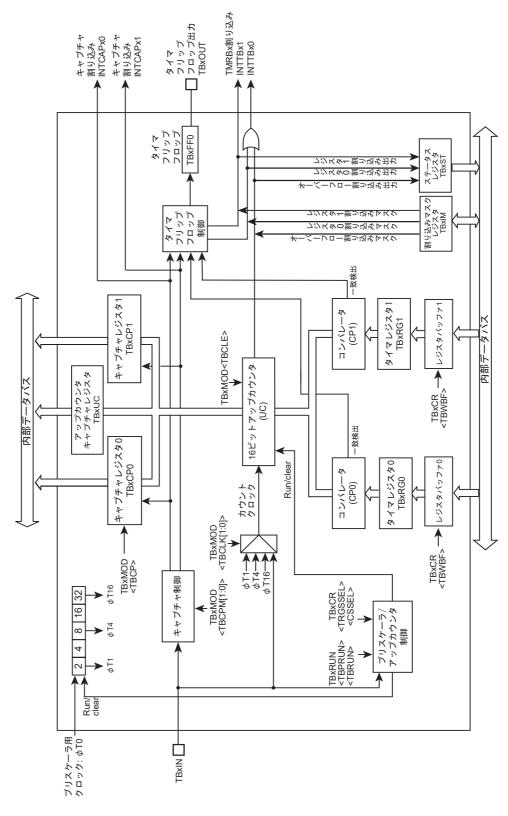

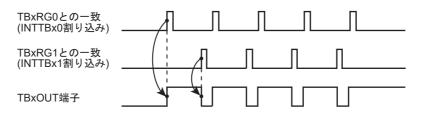

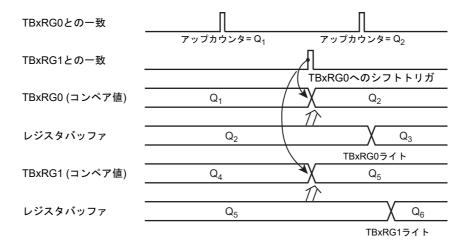

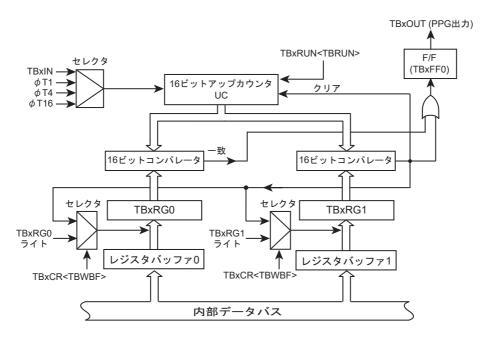

- 3. 16 ビットタイマ (TMRB): 8 チャネル

- 16 ビットインタバルタイマモード

- 16 ビットイベントカウンタモード

- インプットキャプチャ機能

- ・ 外部トリガ PPG 出力

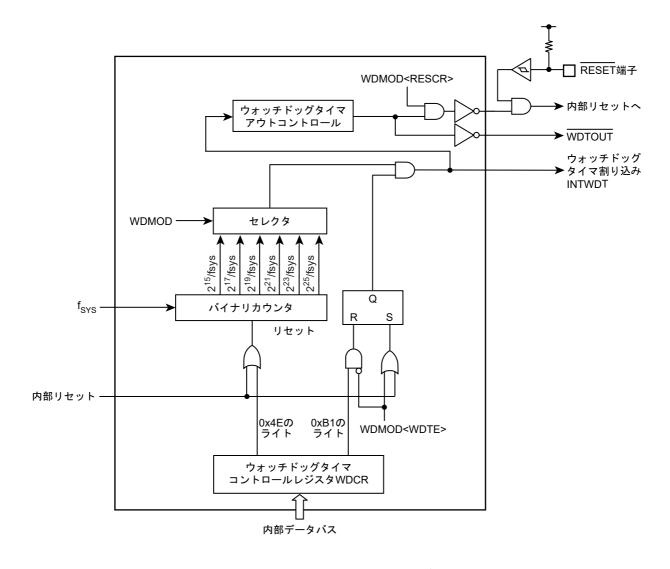

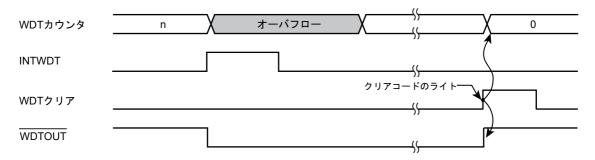

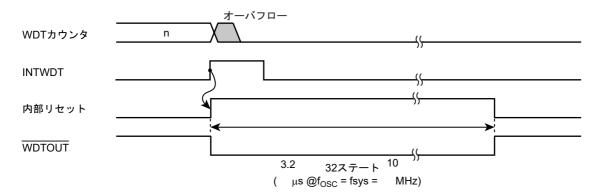

- 4. ウォッチドッグタイマ (WDT): 1 チャネル

Page1 2023/07/31

1.1 機能概要 TMPM376FDDFG/FDFG

#### リセットまたはマスク不能割り込み (NMI) 発生

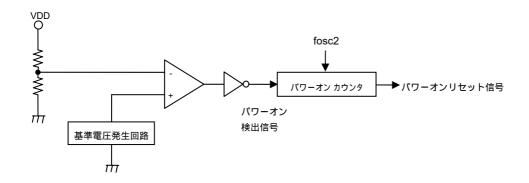

- 5. パワーオンリセット回路 (POR)

- 6. 電圧検出回路 (VLTD)

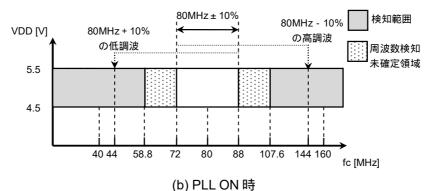

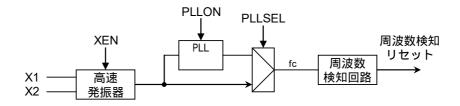

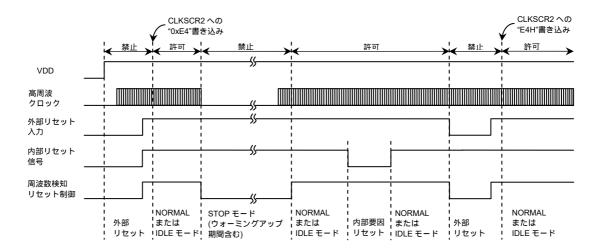

- 7. 周波数検知回路 (OFD)

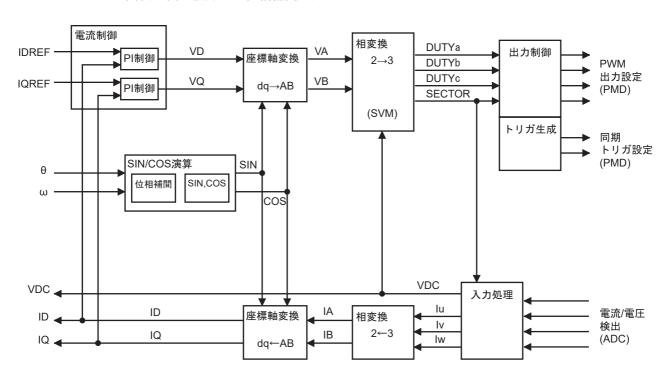

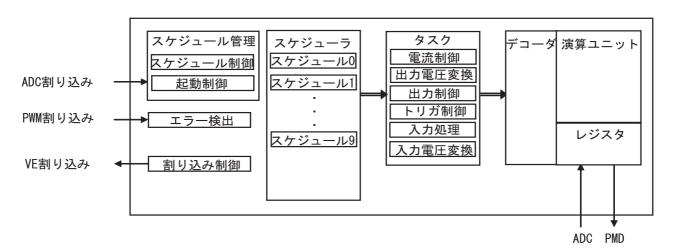

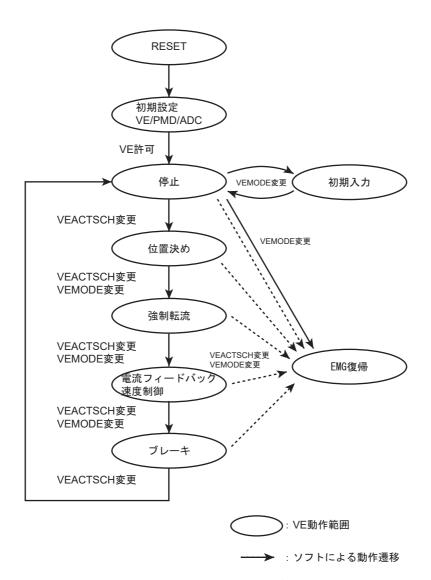

- 8. ベクトルエンジン (VE): 1 ユニット

- モータ制御用演算機能

- 2 モータ対応

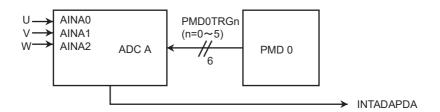

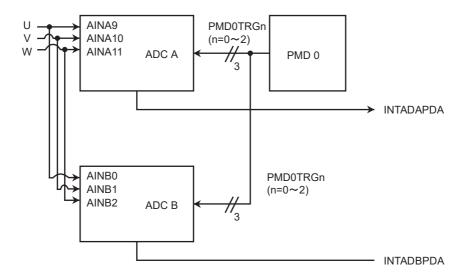

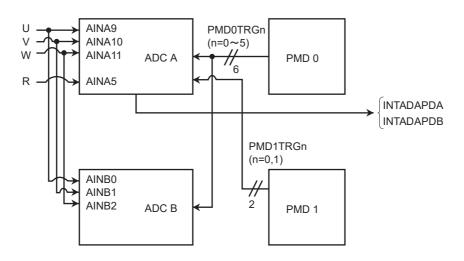

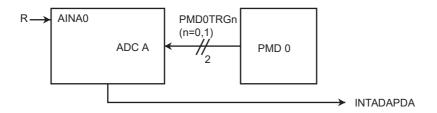

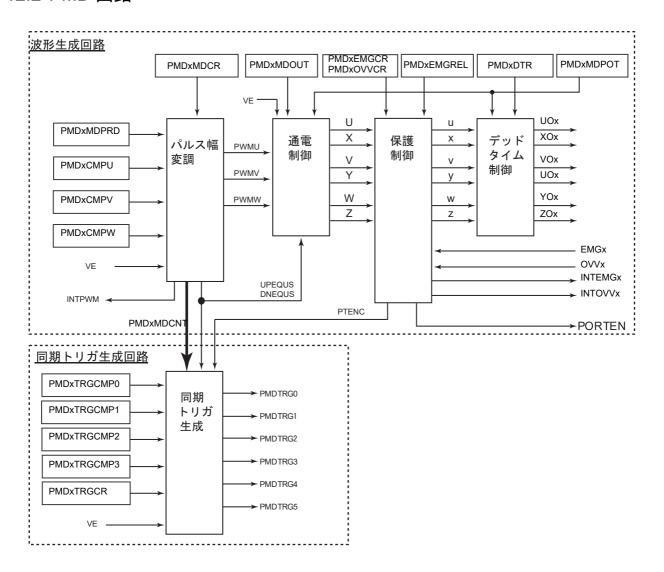

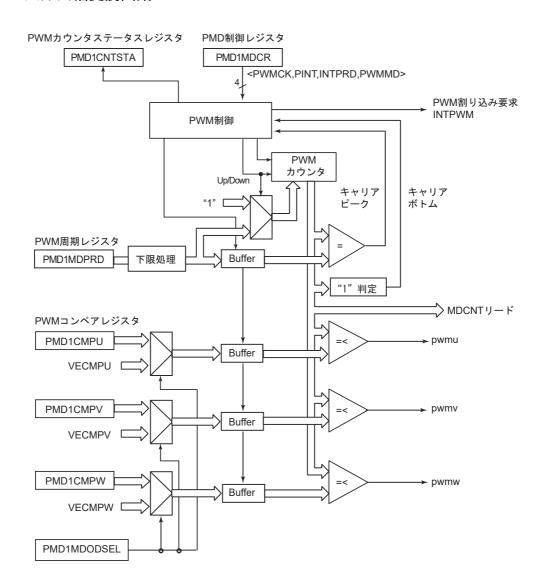

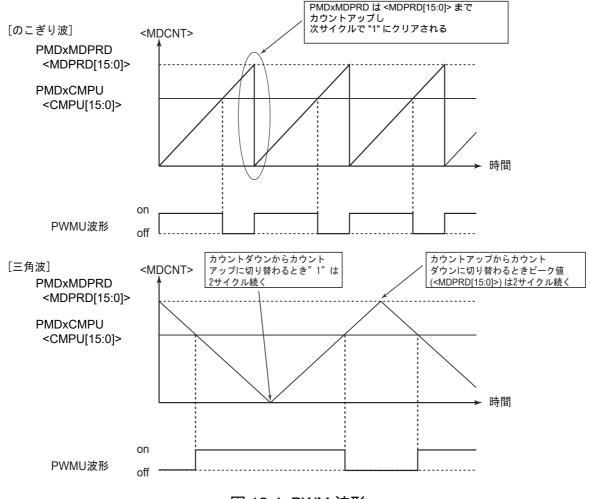

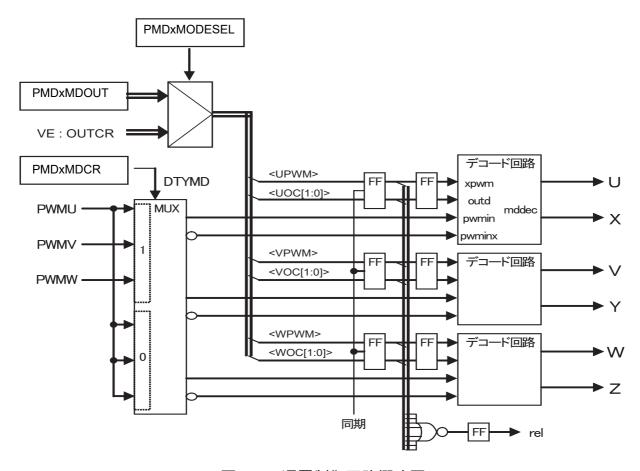

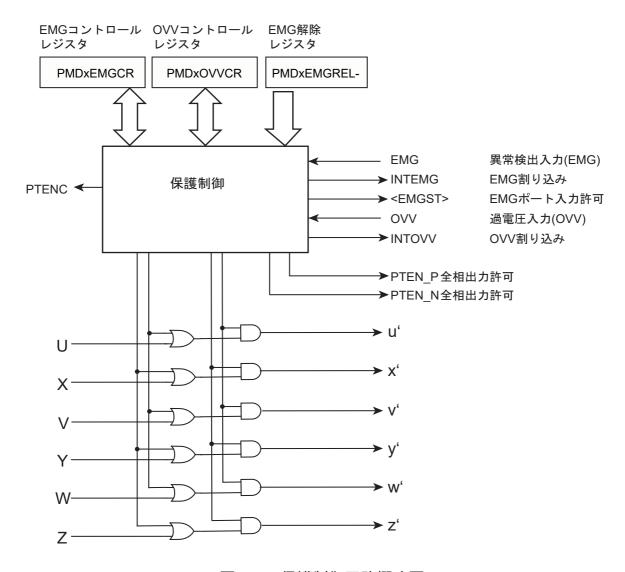

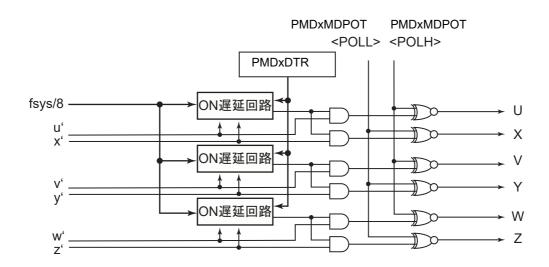

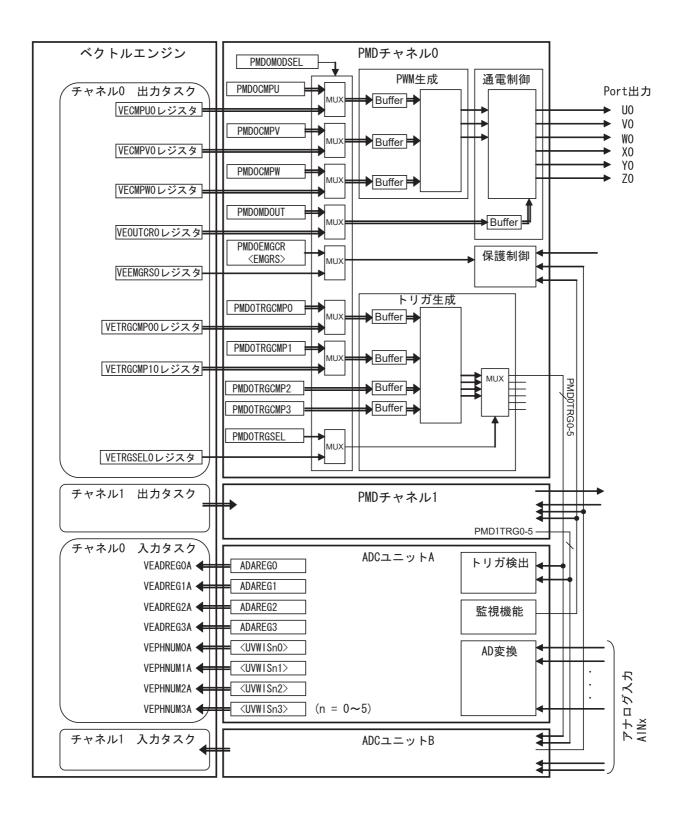

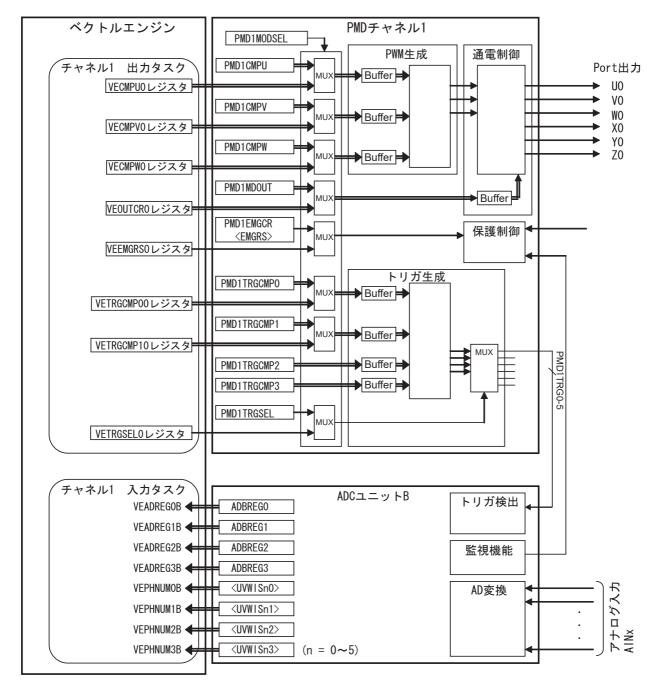

- 9. モータ制御回路 (PMD): 2 チャネル

- 3 相相補 PWM 出力

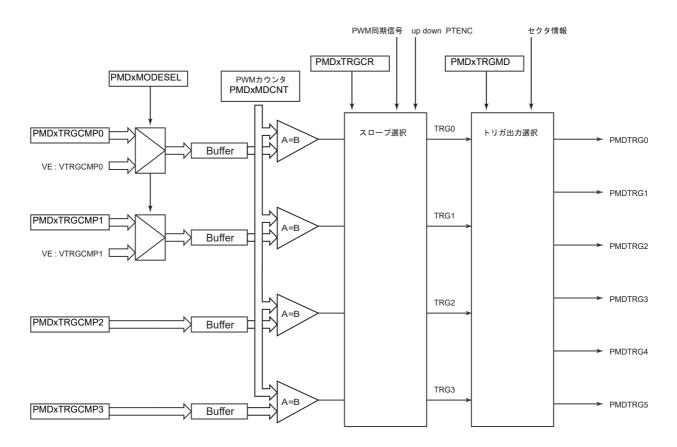

- AD コンバータを連動させる同期トリガ生成

- 緊急停止保護機能 (EMG)

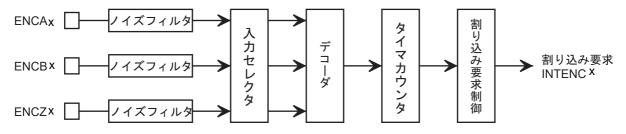

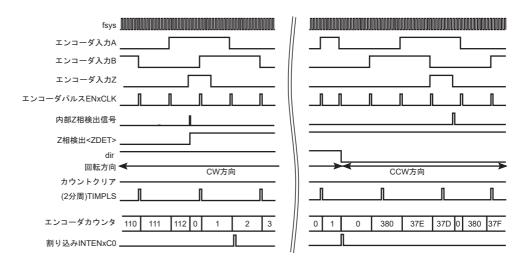

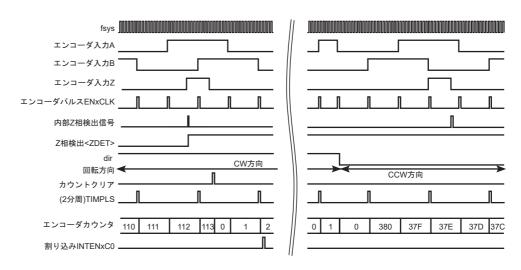

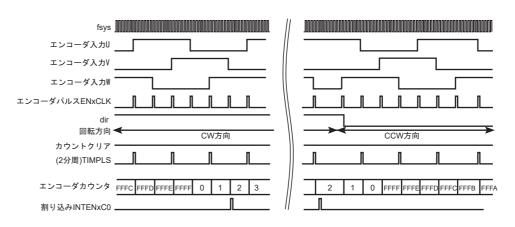

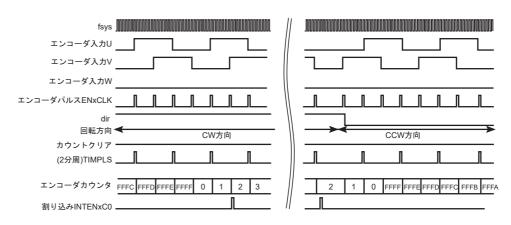

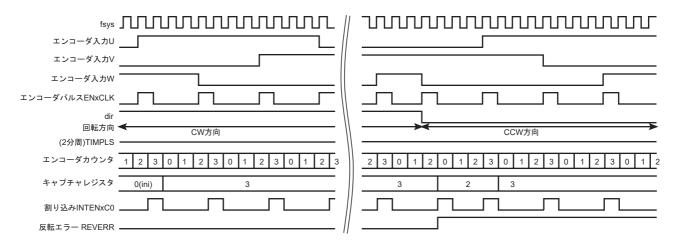

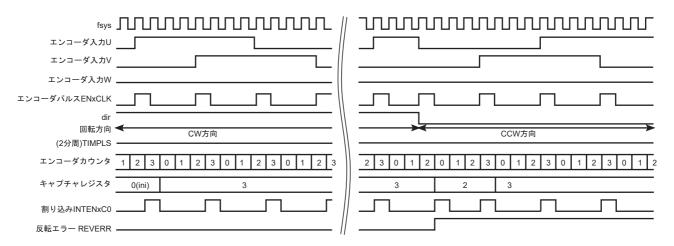

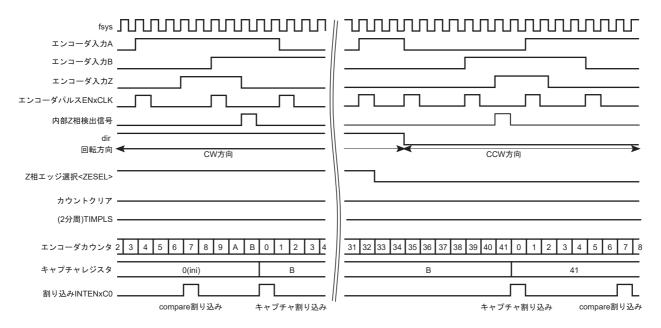

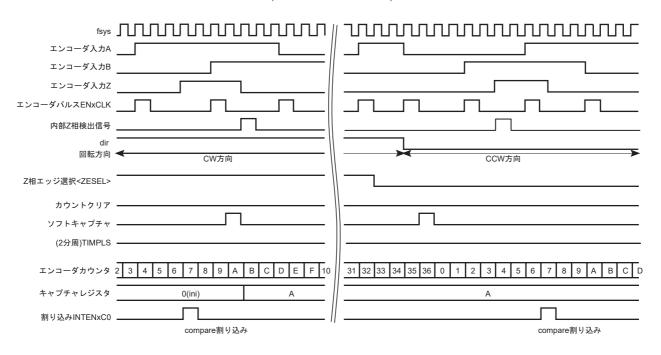

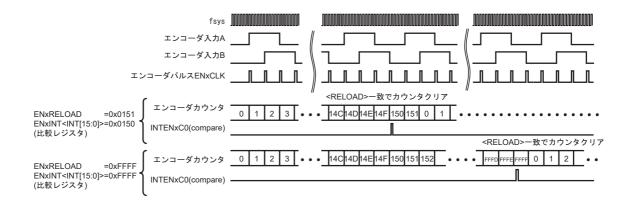

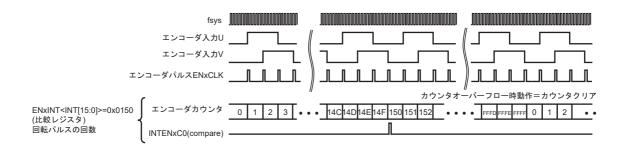

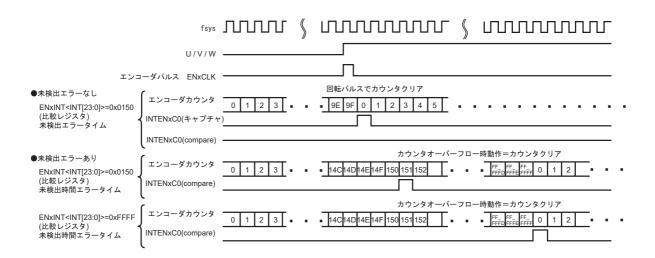

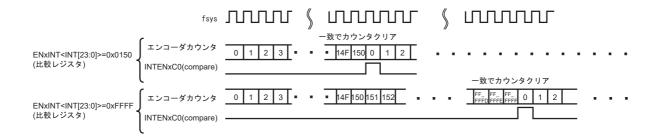

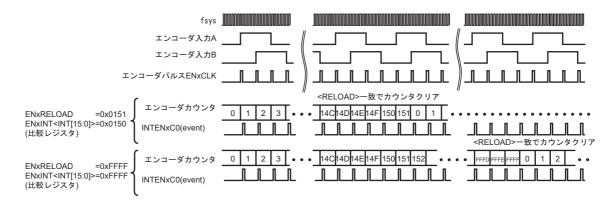

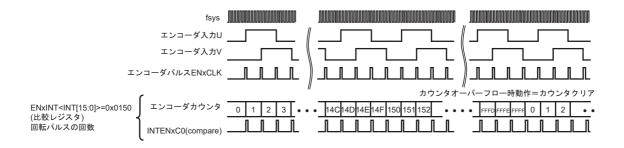

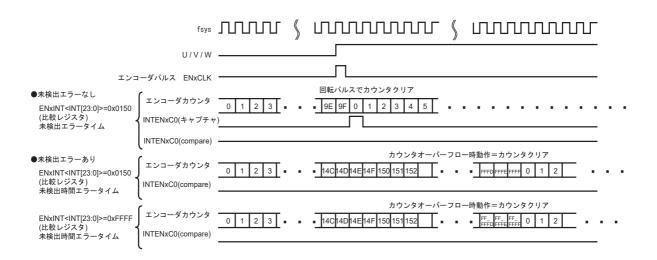

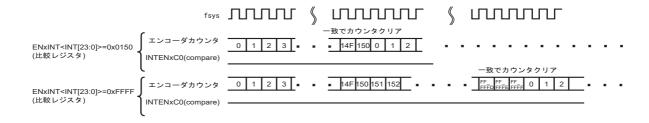

- 10. エンコーダ入力回路 (ENC): 2 チャネル

- インクリメンタル形エンコーダ対応 (AB 信号 / ABZ 信号)

- 回転方向検出回路

- 絶対位置検出カウンタ

- 位置コンペア回路

- ノイズフィルタ内蔵

- ・3相センサ入力対応

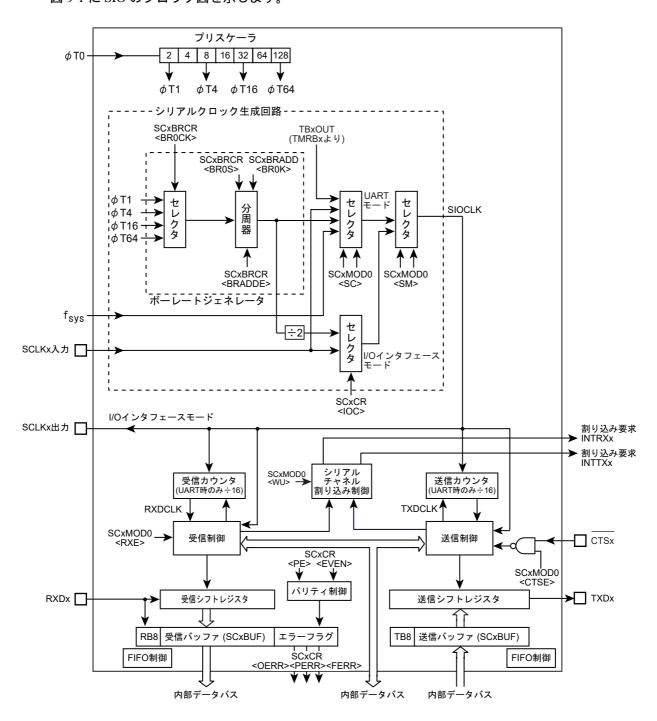

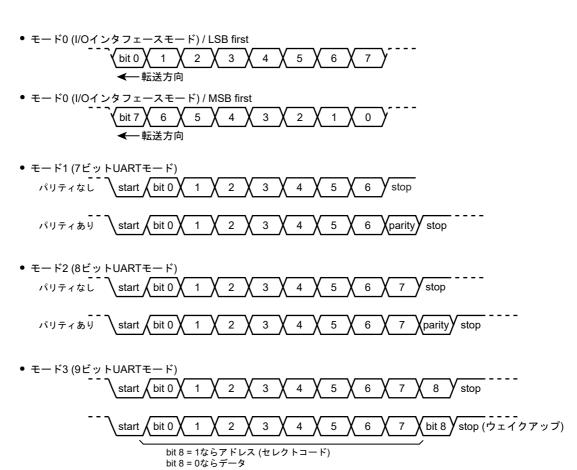

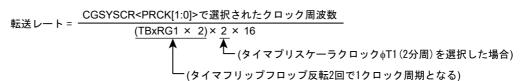

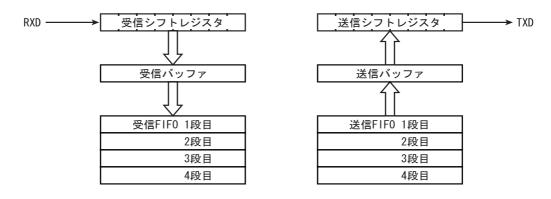

- 11. 汎用シリアルインターフェース (SIO/UART) : 4 チャネル UART/ クロック同期式モード選択可能 (4byte FIFO 内蔵)

- 12. シリアルバスインタフェース (I2C/SIO): 1 チャネル I2C バスモード / クロック同期式モード選択可能

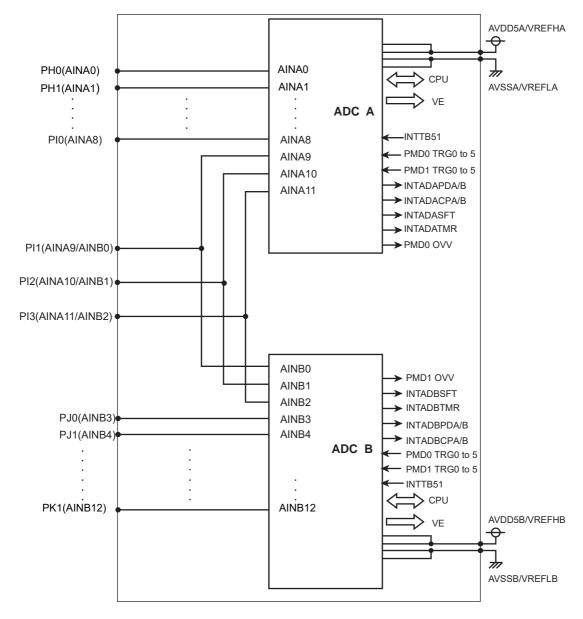

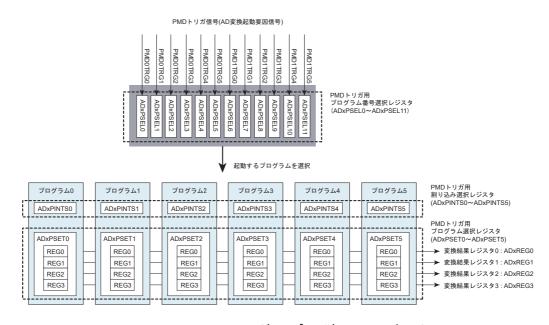

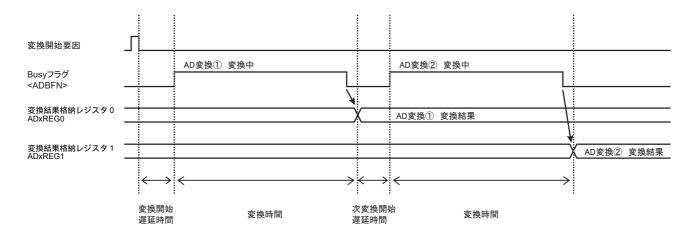

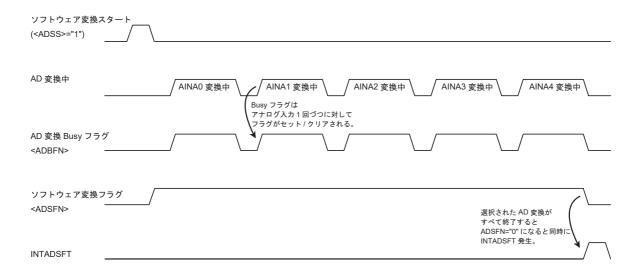

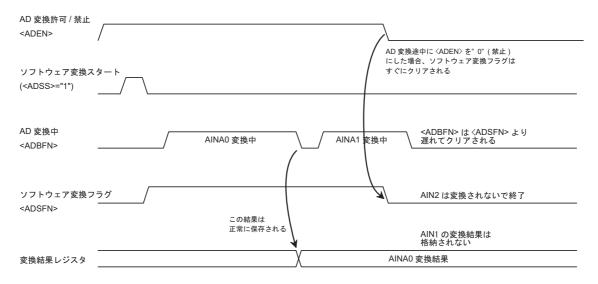

- 13.12 ビット AD コンバータ (ADC): 2 ユニット (アナログ入力: 22 チャネル)

- トリガスタート機能: TMRB 割り込み / PMD トリガによるスタート可能

- 常時変換可能

- AD 監視機能 2ch

- 変換時間 2 μsec (ADC 変換クロック 40 MHz 時 )

- 14. 入出力ポート (PORT): 82 端子

入出力端子:80本 入力端子:2本

- 15. 割り込み機能

- 内部 63 本: 7 レベルの優先順位設定可能(ウォッチドッグタイマ割り込みを除く)

• 外部 16 本: 7 レベルの優先順位設定可能

#### 16. スタンバイ機能

スタンバイモード: IDLE, STOP

- 17. クロックジェネレータ (CG)

- PLL 内蔵 (8 逓倍)

- クロックギア機能: 高速クロックを 1/1, 1/2, 1/4, 1/8,1/16 に分周可能

- 18. エンディアン

リトルエンディアン

- 19. 内蔵高速発振器

- 20. 最大動作周波数: 80 MHz

- 21. 動作電圧範囲

4.5 V~5.5 V (内蔵レギュレータ使用)

- 22. 温度範囲

- -40°C ~ 85°C (Flash W/E およびデバッグ時以外)

- 0°C ~ 70°C (Flash W/E 時)

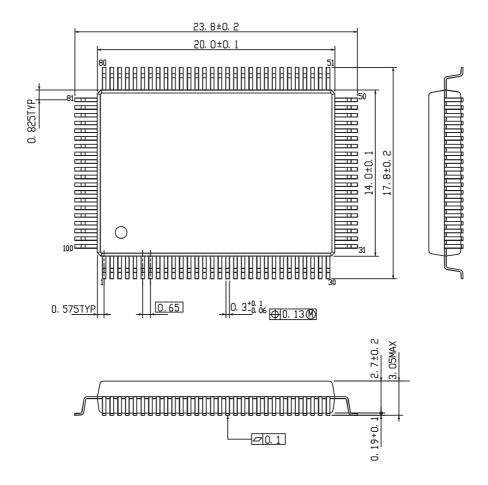

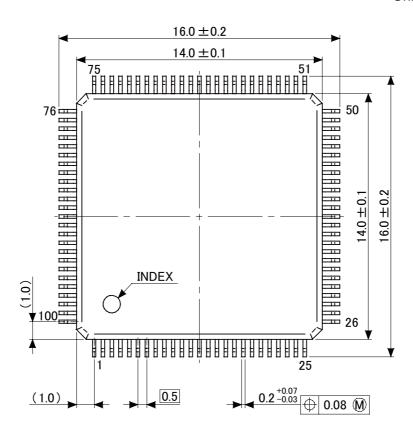

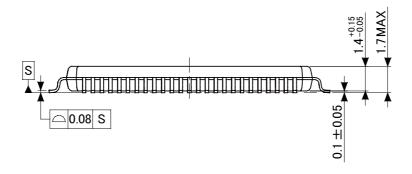

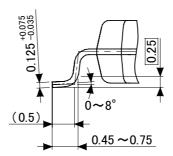

- 23. パッケージ

- QFP100-P-1420-0.65Q (14 mm × 20 mm, 0.65 mm ピッチ)

- LQFP100-P-1414-0.50H (14 mm×14 mm, 0.5 mm ピッチ)

Page3 2023/07/31

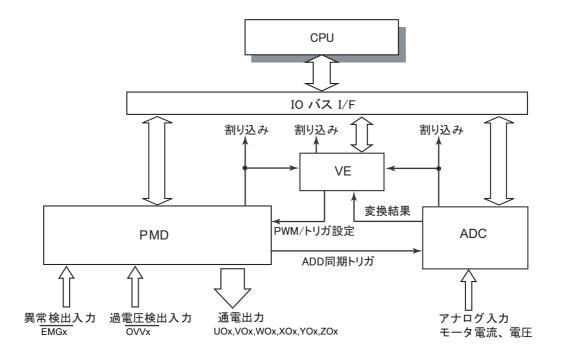

1.2 プロック図 TMPM376FDDFG/FDFG

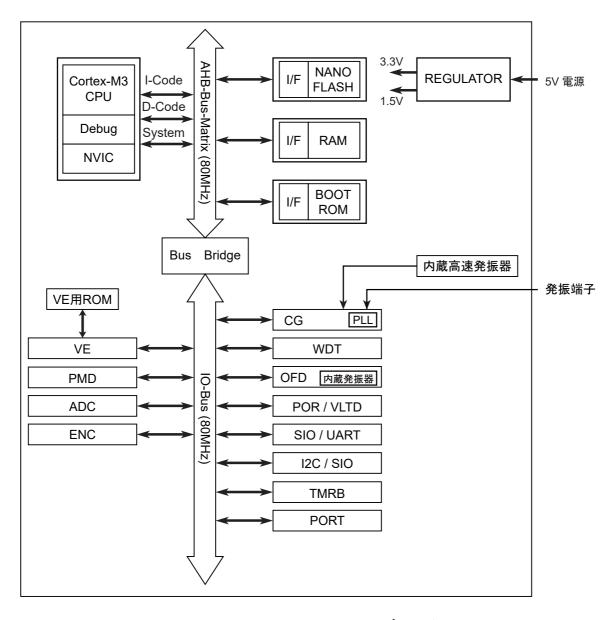

## 1.2 ブロック図

図 1-1 TMPM376FDDFG/FDFG ブロック図

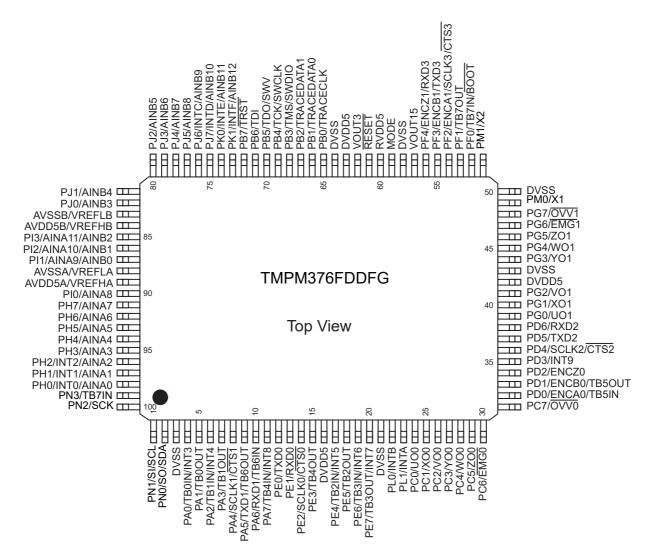

## 1.3 ピン配置図 (Top view)

TMPM376FDDFG/FDFGのピン配置図は、下図のとおりです。

図 1-2 ピン配置図 (QFP100)

Page5 2023/07/31

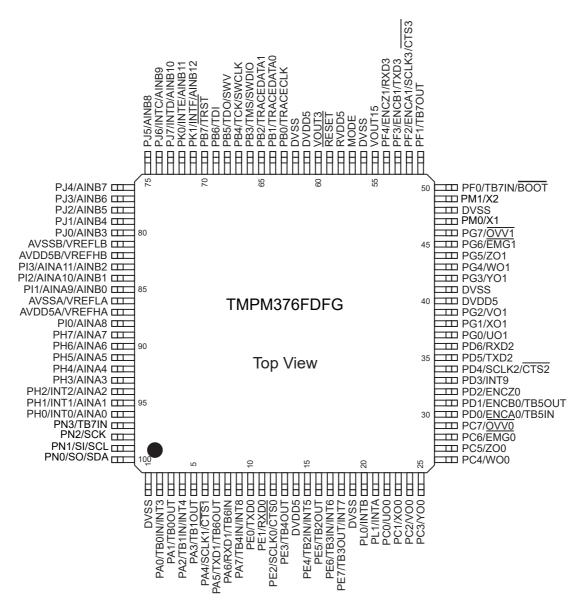

1.3 ピン配置図 (Top view) TMPM376FDDFG/FDFG

図 1-3 ピン配置図 (LQFP100)

## 1.4 ピン名称と機能

TMPM376FDDFG/FDFG の入出力ピン名称と機能は、表 1-1 のとおりです。

### 1.4.1 ポート順

表 1-1 ピン名称と機能 < ポート順 > (1/5)

| PORT   | 分類           | ピン番号<br>(DFG/ FG) | 記号                    | 入出力              | 機能                                       |

|--------|--------------|-------------------|-----------------------|------------------|------------------------------------------|

| PORT A | 機能           | 4/2               | PA0<br>TB0IN<br>INT3  | 入出力<br>入力<br>入力  | 入出力ポート<br>タイマ B インプットキャプチャ端子<br>外部割り込み端子 |

| PORT A | 機能           | 5/3               | PA1<br>TB0OUT         | 入出力<br>出力        | 人出力ポート         タイマ B 出力端子                |

| PORT A | 機能           | 6/4               | PA2<br>TB1IN<br>INT4  | 入出力<br>入力<br>入力  | 入出力ポート<br>タイマ B インプットキャプチャ端子<br>外部割り込み端子 |

| PORT A | 機能           | 7/5               | PA3<br>TB1OUT         | 入出力<br>出力        | 入出力ポート<br>タイマ B 出力端子                     |

| PORT A | 機能           | 8/6               | PA4<br>SCLK1<br>CTS1  | 入出力<br>入出力<br>入力 | 入出力ポート<br>SIO クロック端子<br>SIO ハンドシェイク用端子   |

| PORT A | 機能           | 9/7               | PA5<br>TXD1<br>TB6OUT | 入出力<br>出力<br>出力  | 入出力ポート<br>SIO 送信端子<br>タイマ B 出力端子         |

| PORT A | 機能           | 10 / 8            | PA6<br>RXD1<br>TB6IN  | 入出力<br>入力<br>入力  | 入出力ポート<br>SIO 受信端子<br>タイマ B インプットキャプチャ端子 |

| PORT A | 機能           | 11 / 9            | PA7<br>TB4IN<br>INT8  | 入出力<br>入力<br>入力  | 入出力ポート<br>タイマ B インプットキャプチャ端子<br>外部割り込み端子 |

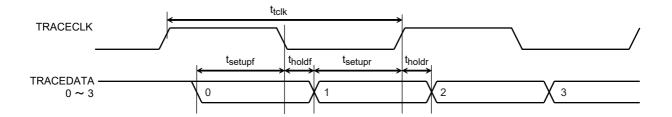

| PORT B | 機能 /<br>デバッグ | 65 / 63           | PB0<br>TRACECLK       | 入出力<br>出力        | 入出力ポート<br>デバッグ用端子                        |

| PORT B | 機能 /<br>デバッグ | 66 / 64           | PB1<br>TRACEDATA0     | 入出力<br>出力        | 入出力ポート<br>デバッグ用端子                        |

| PORT B | 機能 /<br>デバッグ | 67 / 65           | PB2<br>TRACEDATA1     | 入出力<br>出力        | 入出力ポート<br>デバッグ用端子                        |

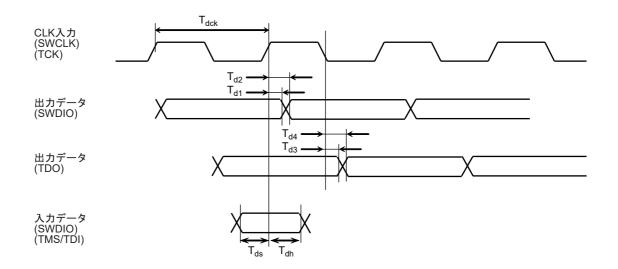

| PORT B | 機能 /<br>デバッグ | 68 / 66           | PB3<br>TMS/SWDIO      | 入出力<br>入出力       | 入出力ポート<br>デバッグ用端子                        |

| PORT B | 機能 /<br>デバッグ | 69 / 67           | PB4<br>TCK/SWCLK      | 入出力<br>入力        | 入出力ポート<br>デバッグ用端子                        |

| PORT B | 機能 /<br>デバッグ | 70 / 68           | PB5<br>TDO/SWV        | 入出力<br>出力        | 入出力ポート<br>デバッグ用端子                        |

| PORT B | 機能 /<br>デバッグ | 71 / 69           | PB6<br>TDI            | 入出力<br>入力        | 入出力ポート<br>デバッグ用端子                        |

| PORT B | 機能 /<br>デバッグ | 72 / 70           | PB7<br>TRST           | 入出力<br>入力        | 入出力ポート<br>デバッグ用端子                        |

| PORT C | 機能           | 24 / 22           | PC0<br>UO0            | 入出力<br>出力        | 入出力ポート<br>U 相出力端子                        |

Page7 2023/07/31

1.4 ピン名称と機能 TMPM376FDDFG/FDFG

## 表 1-1 ピン名称と機能 < ポート順 > (2/5)

| PORT   | 分類 | ピン番号<br>(DFG/ FG) | 記号                     | 入出力              | 機能                                                |

|--------|----|-------------------|------------------------|------------------|---------------------------------------------------|

| PORT C | 機能 | 25 / 23           | PC1<br>XO0             | 入出力<br>出力        | 入出力ポート<br>X 相出力端子                                 |

| PORT C | 機能 | 26 / 24           | PC2<br>VO0             | 入出力<br>出力        | 入出力ポート<br>V 相出力端子                                 |

| PORT C | 機能 | 27 / 25           | PC3<br>YO0             | 入出力<br>出力        | 入出力ポート<br>Y 相出力端子                                 |

| PORT C | 機能 | 28 / 26           | PC4<br>WO0             | 入出力<br>出力        | 入出力ポート<br>W 相出力端子                                 |

| PORT C | 機能 | 29 / 27           | PC5<br>ZO0             | 入出力<br>出力        | 入出力ポート<br>Z 相出力端子                                 |

| PORT C | 機能 | 30 / 28           | PC6<br>EMG0            | 入出力<br>入力        | 入出力ポート<br>異常検出入力                                  |

| PORT C | 機能 | 31 / 29           | PC7<br>OVV0            | 入出力<br>入力        | 入出力ポート<br>過電圧入力                                   |

| PORT D | 機能 | 32 / 30           | PD0<br>ENCA0<br>TB5IN  | 入出力<br>入力<br>入力  | 入出力ポート         A 相入力端子         タイマ B インプットキャプチャ端子 |

| PORT D | 機能 | 33 / 31           | PD1<br>ENCB0<br>TB5OUT | 入出力<br>入力<br>出力  | 入出力ポート         B相入力端子         タイマ B 出力端子          |

| PORT D | 機能 | 34 / 32           | PD2<br>ENCZ0           | 入出力<br>入力        | 入出力ポート<br>Z 相入力端子                                 |

| PORT D | 機能 | 35 / 33           | PD3<br>INT9            | 入出力<br>入力        | 入出力ポート<br>外部割り込み端子                                |

| PORT D | 機能 | 36 / 34           | PD4<br>SCLK2<br>CTS2   | 入出力<br>入出力<br>入力 | 入出力ポート<br>SIO クロック端子<br>SIO ハンドシェイク用端子            |

| PORT D | 機能 | 37 / 35           | PD5<br>TXD2            | 入出力<br>出力        | 入出力ポート<br>SIO 送信端子                                |

| PORT D | 機能 | 38 / 36           | PD6<br>RXD2            | 入出力<br>入力        | 入出力ポート<br>SIO 受信端子                                |

| PORT E | 機能 | 12 / 10           | PE0<br>TXD0            | 入出力<br>出力        | 入出力ポート<br>SIO 送信端子                                |

| PORT E | 機能 | 13 / 11           | PE1<br>RXD0            | 入出力<br>入力        | 入出力ポート<br>SIO 受信端子                                |

| PORT E | 機能 | 14 / 12           | PE2<br>SCLK0<br>CTS0   | 入出力<br>入出力<br>入力 | 入出力ポート<br>SIO クロック端子<br>SIO ハンドシェイク用端子            |

| PORT E | 機能 | 15 / 13           | PE3<br>TB4OUT          | 入出力<br>出力        | 入出力ポート<br>タイマ B 出力端子                              |

| PORT E | 機能 | 17 / 15           | PE4<br>TB2IN<br>INT5   | 入出力<br>入力<br>入力  | 入出力ポート<br>タイマ B インプットキャプチャ端子<br>外部割り込み端子          |

| PORT E | 機能 | 18 / 16           | PE5<br>TB2OUT          | 入出力<br>出力        | 入出力ポート<br>タイマ B 出力端子                              |

## 表 1-1 ピン名称と機能 < ポート順 > (3/5)

| PORT   | 分類         | ピン番号<br>(DFG/ FG) | 記号                            | 入出力                    | 機能                                                                                                       |

|--------|------------|-------------------|-------------------------------|------------------------|----------------------------------------------------------------------------------------------------------|

| PORT E | 機能         | 19 / 17           | PE6<br>TB3IN<br>INT6          | 入出力<br>入力<br>入力        | 入出力ポート<br>タイマ B インプットキャプチャ端子<br>外部割り込み端子                                                                 |

| PORTE  | 機能         | 20 / 18           | PE7<br>TB3OUT<br>INT7         | 入出力<br>出力<br>入力        | 入出力ポート<br>タイマ B 出力端子<br>外部割り込み端子                                                                         |

| PORT F | 機能 /<br>制御 | 52 / 50           | PF0<br>TB7IN<br>BOOT          | 入出力<br>入力<br>入力        | 入出力ポート<br>タイマ B インブットキャプチャ端子 (注 3)<br>BOOT モード端子 (注 )RESET 信号の立ち上がりで "Low" をサンプリングしてシ<br>ングルブートモードになります。 |

| PORT F | 機能         | 53 / 51           | PF1<br>TB7OUT                 | 入出力<br>出力              | 入出力ポート<br>タイマ B 出力端子                                                                                     |

| PORT F | 機能         | 54 / 52           | PF2<br>ENCA1<br>SCLK3<br>CTS3 | 入出力<br>入力<br>入出力<br>入力 | 人出力ポート         エンコーダ入力         SIO クロック端子         SIO ハンドシェイク用端子                                         |

| PORT F | 機能         | 55 / 53           | PF3<br>ENCB1<br>TXD3          | 入出力<br>入力<br>出力        | 人出力ポート         エンコーダ入力         SIO 送信端子                                                                  |

| PORT F | 機能         | 56 / 54           | PF4<br>ENCZ1<br>RXD3          | 入出力<br>入力<br>入力        | 人出力ポート         エンコーダ入力         SIO 受信端子                                                                  |

| PORT G | 機能         | 39 / 37           | PG0<br>UO1                    | 入出力<br>出力              | 入出力ポート<br>U 相出力端子                                                                                        |

| PORT G | 機能         | 40 / 38           | PG1<br>XO1                    | 入出力<br>出力              | 入出力ポート<br>X 相出力端子                                                                                        |

| PORT G | 機能         | 41 / 39           | PG2<br>VO1                    | 入出力<br>出力              | 入出力ポート<br>V 相出力端子                                                                                        |

| PORT G | 機能         | 44 / 42           | PG3<br>YO1                    | 入出力<br>出力              | 入出力ポート<br>Y相出力端子                                                                                         |

| PORT G | 機能         | 45 / 43           | PG4<br>WO1                    | 入出力<br>出力              | 入出力ポート<br>W 相出力端子                                                                                        |

| PORT G | 機能         | 46 / 44           | PG5<br>ZO1                    | 入出力<br>出力              | 入出力ポート<br>Z 相出力端子                                                                                        |

| PORT G | 機能         | 47 / 45           | PG6<br>EMG1                   | 入出力<br>入力              | 入出力ポート<br>異常検出入力                                                                                         |

| PORT G | 機能         | 48 / 46           | PG7<br>OVV1                   | 入出力<br>入力              | 入出力ポート<br>過電圧入力                                                                                          |

| PORT H | 機能         | 98 / 96           | PH0<br>INT0<br>AINA0          | 入出力<br>入力<br>入力        | 入出力ポート<br>外部割り込み端子<br>アナログ入力端子                                                                           |

| PORT H | 機能         | 97 / 95           | PH1<br>INT1<br>AINA1          | 入出力<br>入力<br>入力        | 入出力ポート<br>外部割り込み端子<br>アナログ入力端子                                                                           |

| PORT H | 機能         | 96 / 94           | PH2<br>INT2<br>AINA2          | 入出力<br>入力<br>入力        | 入出力ポート<br>外部割り込み端子<br>アナログ入力端子                                                                           |

| PORT H | 機能         | 95 / 93           | PH3<br>AINA3                  | 入出力<br>入力              | 入出力ポート         アナログ入力端子                                                                                  |

Page9 2023/07/31

1.4 ピン名称と機能 TMPM376FDDFG/FDFG

## 表 1-1 ピン名称と機能 < ポート順 > (4/5)

| PORT   | 分類           | ピン番号<br>(DFG/ FG) | 記号                    | 入出力             | 機能                             |

|--------|--------------|-------------------|-----------------------|-----------------|--------------------------------|

| PORT H | 機能           | 94 / 92           | PH4<br>AINA4          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT H | 機能           | 93 / 91           | PH5<br>AINA5          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT H | 機能           | 92 / 90           | PH6<br>AINA6          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT H | 機能           | 91 / 89           | PH7<br>AINA7          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT I | 機能           | 90 / 88           | PI0<br>AINA8          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT I | 機能           | 87 / 85           | PI1<br>AINA9/AINB0    | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT I | 機能           | 86 / 84           | PI2<br>AINA10/AINB1   | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT I | 機能           | 85 / 83           | PI3<br>AINA11/AINB2   | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT J | 機能           | 82 / 80           | PJ0<br>AINB3          | 入出力<br>入力       | 人出力ポート<br>アナログ入力端子             |

| PORT J | 機能           | 81 / 79           | PJ1<br>AINB4          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT J | 機能           | 80 / 78           | PJ2<br>AINB5          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT J | 機能           | 79 / 77           | PJ3<br>AINB6          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT J | 機能           | 78 / 76           | PJ4<br>AINB7          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT J | 機能           | 77 / 75           | PJ5<br>AINB8          | 入出力<br>入力       | 入出力ポート<br>アナログ入力端子             |

| PORT J | 機能           | 76 / 74           | PJ6<br>INTC<br>AINB9  | 入出力<br>入力<br>入力 | 入出力ポート<br>外部割り込み端子<br>アナログ入力端子 |

| PORT J | 機能           | 75 / 73           | PJ7<br>INTD<br>AINB10 | 入出力<br>入力<br>入力 | 入出力ポート<br>外部割り込み端子<br>アナログ入力端子 |

| PORT K | 機能           | 74 / 72           | PK0<br>INTE<br>AINB11 | 入出力<br>入力<br>入力 | 入出力ポート<br>外部割込み端子<br>アナログ入力端子  |

| PORT K | 機能           | 73 / 71           | PK1<br>INTF<br>AINB12 | 入出力<br>入力<br>入力 | 入出力ポート<br>外部割り込み端子<br>アナログ入力端子 |

| PORT L | 機能           | 22 / 20           | PL0<br>INTB           | 入力<br>入力        | 入力ポート<br>外部割り込み端子              |

| PORT L | 機能           | 23 / 21           | PL1<br>INTA           | 入力<br>入力        | 入力ポート<br>外部割り込み端子              |

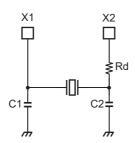

| PORT M | 機能<br>/ クロック | 49 / 47           | PM0<br>X1             | 入出力<br>入力       | 入出力ポート<br>高速発振子接続端子            |

## 表 1-1 ピン名称と機能 < ポート順 > (5/5)

| PORT   | 分類           | ピン番号<br>(DFG/ FG) | 記号               | 入出力        | 機能                                                    |

|--------|--------------|-------------------|------------------|------------|-------------------------------------------------------|

| PORT M | 機能<br>/ クロック | 51 / 49           | PM1<br>X2        | 入出力<br>出力  | 入出力ポート<br>高速発振子接続端子                                   |

| PORT N | 機能           | 2 / 100           | PN0<br>SO / SDA  | 入出力<br>入出力 | 入出力ポート<br>SIO モード送信端子、I2C モード送受信                      |

| PORT N | 機能           | 1 / 99            | PN1<br>SI / SCL  | 入出力<br>入出力 | 入出力ポート<br>SIO モード受信端子、I2C モードクロック                     |

| PORT N | 機能           | 100 / 98          | PN2<br>SCK       | 入出力<br>入出力 | 入出力ポート<br>SIO モードクロック端子                               |

| PORT N | 機能           | 99 / 97           | PN3<br>TB7IN     | 入出力<br>入力  | 入出力ポート<br>タイマ B インプットキャプチャ端子 (注 3)                    |

| -      | 制御           | 59 / 57           | MODE             | 入力         | モード端子<br>(注)必ず GND に接続してください。                         |

| -      | 機能           | 61 / 59           | RESET            | 入力         | リセット入力端子<br>(注)プルアップおよびノイズフィルタ (Typ. 条件で約 30ns) 付きです。 |

| -      | 電源           | 3 / 1             | DVSS             | -          | GND 端子                                                |

| -      | 電源           | 21 / 19           | DVSS             | -          | GND 端子                                                |

| -      | 電源           | 43 / 41           | DVSS             | -          | GND 端子                                                |

| -      | 電源           | 50 / 48           | DVSS             | -          | GND 端子                                                |

| -      | 電源           | 58 / 56           | DVSS             | -          | GND 端子                                                |

| -      | 電源           | 64 / 62           | DVSS             | -          | GND 端子                                                |

| -      | 電源           | 16 / 14           | DVDD5            | -          | 電源端子                                                  |

| -      | 電源           | 42 / 40           | DVDD5            | -          | 電源端子                                                  |

| -      | 電源           | 63 / 61           | DVDD5            | -          | 電源端子                                                  |

| -      | 電源           | 60 / 58           | RVDD5            | -          | 電源端子                                                  |

| -      | 電源           | 57 / 55           | VOUT15           | -          | 電源端子                                                  |

| -      | 電源           | 62 / 60           | VOUT3            | -          | 電源端子                                                  |

| -      | 電源           | 83 / 81           | AVSSB<br>VREFLB  | _          | AD コンバータ用 GND 端子 ( 注 1)<br>AD コンバータ用基準電源端子            |

| -      | 電源           | 84 / 82           | AVDD5B<br>VREFHB | _          | AD コンバータ用電源端子 (注 2)<br>AD コンバータ用基準電源端子                |

| -      | 電源           | 88 / 86           | AVSSA<br>VREFLA  | -          | AD コンパータ用 GND 端子 (注 1)<br>AD コンパータ用基準電源端子             |

| -      | 電源           | 89 / 87           | AVDD5A<br>VREFHA | -          | AD コンバータ用電源端子 (注 2)<br>AD コンバータ用基準電源端子                |

- 注 1) AD コンバータを使用しない場合でも GND に接続してください。

- 注 2) AD コンバータを使用しない場合でも電源に接続してください。

- 注3) TB7IN は同時に使用することはできません。

Page11 2023/07/31

1.5 電源の種類と供給端子 TMPM376FDDFG/FDFG

## 1.5 電源の種類と供給端子

表 1-2 電源の種類と供給端子

| 電源の種類  | 電圧範囲         | ピン番号<br>(DFG / FG)                | 電源供給端子                                                                              |

|--------|--------------|-----------------------------------|-------------------------------------------------------------------------------------|

| DVDD5  |              | 16 / 14 ,<br>42 / 40 ,<br>63 / 61 | PA,PB,PC,PD,PE,PF,PG,PL,PM<br>PN,RESET,MODE                                         |

| AVDD5A | 4.5 ~ 5.5V   | 89 / 87                           | PH, PI                                                                              |

| AVDD5B |              | 84 / 82                           | PJ, PK                                                                              |

| RVDD5  |              | 60 / 58                           | -                                                                                   |

| VOUT15 | 1.35 ~ 1.65V | 57 / 55                           | 内部電源の安定化コンデンサ接続端子です。外部回路への電源供給はできません。<br>DVSS との間にコンデンサ 3.3μF ~ 4.7μF<br>を接続してください。 |

| VOUT3  | 2.7 ~ 3.6V   | 62 / 60                           | 内部電源の安定化コンデンサ接続端子です。外部回路への電源供給はできません。<br>DVSS との間にコンデンサ 3.3μF ~ 4.7μF<br>を接続してください。 |

注) VOUT15,VOUT3 は内蔵レギュレータ出力の安定化のためのコンデンサ接続端子です。

## 第2章 プロセッサコア

TX03 シリーズには、高性能 32 ビットプロセッサコア (ARM 社 Cortex-M3 コア ) が内蔵されています。 プロセッサコアの動作については、ARM 社からリリースされる "Cortex-M3 テクニカルリファレンスマニュアル"を参照してください。ここでは、製品固有の情報について説明します。

## 2.1 コアに関する情報

TMPM376FDDFG/FDFG で使用している Cortex-M3 コアのリビジョンは以下のとおりです。

CPU コア部、アーキテクチャなどの詳細は、ARM 社の下記 URL より "Cortex-M series processors" のマニュアルを参照してください。

http://infocenter.arm.com/help/index.jsp

| 製品名                   | コアリビジョン |

|-----------------------|---------|

| TMPM376FDDFG/<br>FDFG | r2p0    |

## 2.2 構成可能なオプション

Cortex-M3 コアは、一部のブロックについて実装するかどうかを選択することができます。 TMPM376FDDFG/FDFG での構成は以下のとおりです。

| 構成可能なオプション               | 実装                             |

|--------------------------|--------------------------------|

| FPB                      | リテラルコンパレータ:2 本<br>命令コンパレータ:6 本 |

| DWT                      | コンパレータ:4 本                     |

| ITM                      | あり                             |

| MPU                      | なし                             |

| ETM                      | あり                             |

| AHB-AP                   | あり                             |

| AHB トレースマクロセル<br>インタフェース | あり                             |

| TPIU                     | あり                             |

| WIC                      | なし                             |

Page13 2023/07/31

### 2.3 例外/割り込み

例外/割り込みに関連する製品固有の情報をまとめます。

#### 2.3.1 割り込み本数

Cortex-M3 コアは割り込み本数を 1 ~ 240 本の間で任意に構成することができます。

TMPM376FDDFG/FDFG の割り込み本数は 79 本です。割り込み本数は NVIC レジスタの割り込み コントローラタイプレジスタの <INTLINESNUM[4:0]> ビットに反映され、本製品では "0x00" が読み出されます。

#### 2.3.2 割り込み優先度ビット数

Cortex-M3 コアは割り込み優先度ビット数を3~8ビットの間で任意に構成することができます。

TMPM376FDDFG/FDFGの割り込み優先度は3ビットです。このビット数は割り込み優先度レジスタとシステムハンドラ優先度レジスタのビット構成に反映されます。

#### 2.3.3 SysTick

Cortex-M3 コアには SysTick と呼ばれるシステムタイマがあり、SysTick 例外を発生させることができます。

SysTick 例外の詳細については、例外の「SysTick」の章および、「NVIC レジスタ」の SysTick 関連レジスタの章を参照してください。

#### 2.3.4 SYSRESETREQ

Cortex-M3 コアは、アプリケーション割り込みおよびリセット制御レジスタの <SYSRESETREQ>ビットがセットされると SYSRESETREQ 信号を出力します。

TMPM376FDDFG/FDFG では SYSRESETREQ 信号が出力されるとウォームリセットと同様の動作になります。

#### 2.3.5 LOCKUP

回復不能な例外が発生すると Cortex-M3 コアは LOCKUP 信号を出力し、ソフトウエアに重大な誤りのあることを示します。

TMPM376FDDFG/FDFG ではこの信号は未使用です。LOCKUP 状態から復帰する際にはマスク不能割り込み (NMI) またはリセットを使用する必要があります。

#### 2.3.6 補助フォールトステータスレジスタ

Cortex-M3 コアにはソフトウエアに対して追加のシステムフォールト情報を提供するための補助フォールトステータスレジスタが準備されています。

TMPM376FDDFG/FDFG ではこのレジスタに対して機能を定義していません。リードすると常に "0x0000\_0000" が読み出されます。

### 2.4 イベント

Cortex-M3 コアにはイベント出力信号とイベント入力信号があります。イベント出力信号は、SEV 命令実行により出力されます。また、イベントが入力されると WFE 命令による低電力状態から復帰します。

TMPM376FDDFG/FDFG では、イベント出力信号、イベント入力信号とも未使用です。SEV 命令、WFE 命令は使用しないでください。

### 2.5 電力管理

Cortex-M3コアには電力管理のための信号としてSLEEPINGおよびSLEEPDEEPがあります。SLEEPDEEPは、システム制御レジスタの <SLEEPDEEP> ビットがセットされている場合に出力されます。

これらの信号は、割り込み待ち (WFI) 命令の実行、イベント待ち (WFE) 命令の実行または、システム制御レジスタの <SLEEPONEXIT> ビットがセットされている場合の割り込みサービスルーチン (ISR) からの退出時に出力されます。

TMPM376FDDFG/FDFG では、SLEEPDEEP 信号は使用していません。<SLEEPDEEP> ビットはセットしないでください。また、イベント信号も未使用のため、WFE 命令は使用しないでください。

電力管理については、「クロック/モード制御」の章を参照してください。

### 2.6 排他アクセス

Cortex-M3 コアは DCode バスおよびシステムバスの排他アクセスをサポートしていますが、TMPM376FDDFG/FDFG ではこの機能を使用していません。

Page15 2023/07/31

## 第3章 メモリマップ

### 3.1 メモリマップ

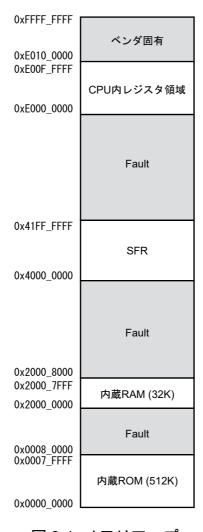

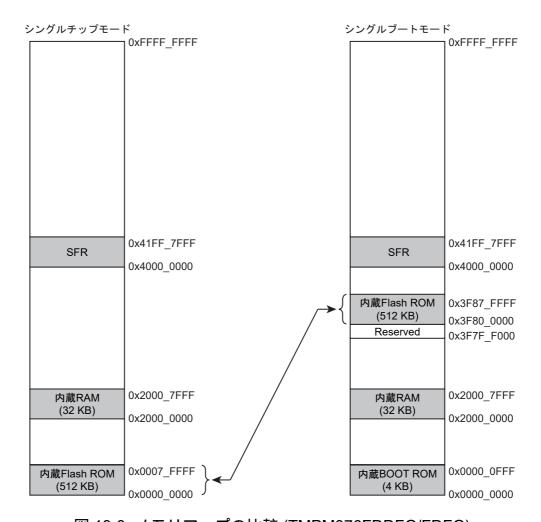

TMPM376FDDFG/FDFG のメモリマップは、ARM Cortex-M3 コアのメモリマップに沿って作られており、内蔵 ROM 領域は Cortex-M3 コアメモリマップの Code 領域、内蔵 RAM 領域は SRAM 領域、特殊機能レジスタ (SFR) 領域は Peripheral 領域に割り付けられています。特殊機能レジスタ (SFR: Special function register) とは、入出力ポートおよび周辺機能のコントロールレジスタを示します。 SRAM 領域、SFR 領域はすべてビットバンド領域に含まれています。

CPU 内レジスタ領域はコア内部のレジスタ領域です。

各領域の詳細については、"Cortex-M3 テクニカルリファレンスマニュアル"を参照してください。

"Fault" と記載された領域では、アクセスするとメモリフォールトが有効な場合にはメモリフォールト、無効な場合にはハードフォールトが発生します。また、ベンダ固有領域にはアクセスしないでください。

#### 3.1.1 TMPM376FDDFG/FDFG メモリマップ

TMPM376FDDFG/FDFG のメモリマップを以下に示します。

図 3-1 メモリマップ

Page17 2023/07/31

## 3.2 SFR 領域詳細

SFR 領域の詳細を表 3-1 に示します。

表 3-1 の Reserved (予約領域)にはアクセスしないでください。また、周辺機能によってはアクセスを制限するアドレスを有する場合があります。詳細は各周辺機能の章を参照してください。

表 3-1 SFR 詳細

| Start Address | End Address   | Peripheral |

|---------------|---------------|------------|

| 0x4000 _ 0000 | 0x4000 _ 037F | PORT       |

| 0x4000 _ 0380 | 0x4000 _ FFFF | Reserved   |

| 0x4001 _ 0000 | 0x4001 _ 01FF | TMRB       |

| 0x4001 _ 0200 | 0x4001 _ 03FF | Reserved   |

| 0x4001 _ 0400 | 0x4001 _ 053F | ENC        |

| 0x4001_0540   | 0x4001 _ FFFF | Reserved   |

| 0x4002 _ 0000 | 0x4002 _ 007F | I2C/SIO    |

| 0x4002 _ 0080 | 0x4002 _ 017F | SIO/UART   |

| 0x4002 _ 0180 | 0x4002 _ FFFF | Reserved   |

| 0x4003 _ 0000 | 0x4003 _ 02FF | ADC        |

| 0x4003 _ 0300 | 0x4003 _ FFFF | Reserved   |

| 0x4004 _ 0000 | 0x4004 _ 003F | WDT        |

| 0x4004 _ 0040 | 0x4004 _ 01FF | Reserved   |

| 0x4004 _ 0200 | 0x4004 _ 023F | CG         |

| 0x4004 _ 0240 | 0x4004 _ 07FF | Reserved   |

| 0x4004 _ 0800 | 0x4004 _ 083F | OFD        |

| 0x4004 _ 0840 | 0x4004_08FF   | Reserved   |

| 0x4004 _ 0900 | 0x4004_093F   | VLTD       |

| 0x4004 _ 0940 | 0x4004 _ FFFF | Reserved   |

| 0x4005 _ 0000 | 0x4005 _ 023F | VE         |

| 0x4005 _ 0240 | 0x4005 _ 03FF | Reserved   |

| 0x4005 _ 0400 | 0x4005 _ 04FF | PMD        |

| 0x4005 _ 0500 | 0x4007 _ FFFF | Reserved   |

| 0x4008 _ 0000 | 0x41FF _ EFFF | Hard fault |

| 0x41FF _ F000 | 0x41FF _ F03F | FLASH      |

| 0x41FF _ F040 | 0x41FF _ FFFF | Reserved   |

## 第4章 リセット動作

### 4.1 リセット入力前状態

電源投入時は、製品の状態は不定です。全ての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの期間、内部回路は不確定であり、レジスタの設定や各端子の状態は不定となります。

### 4.2 リセット期間

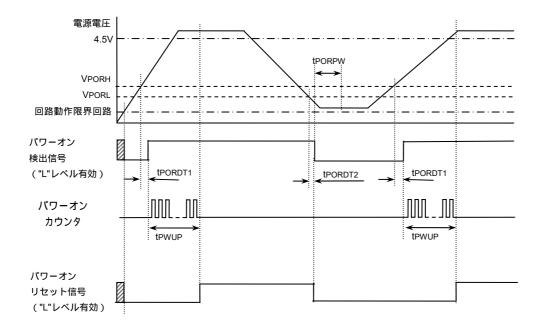

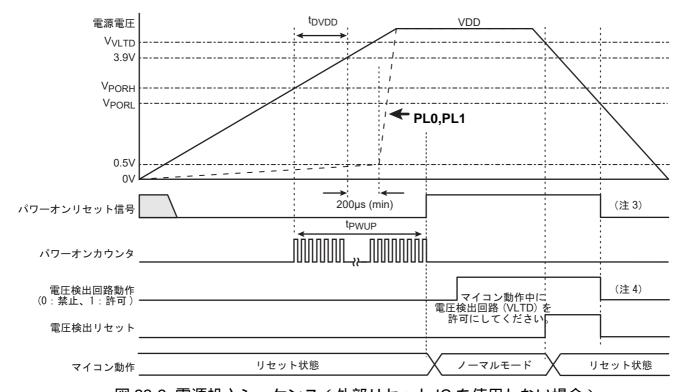

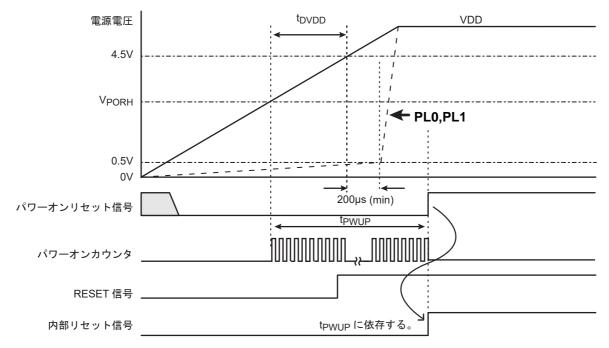

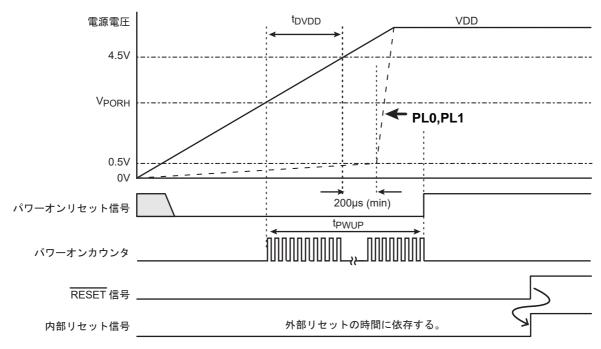

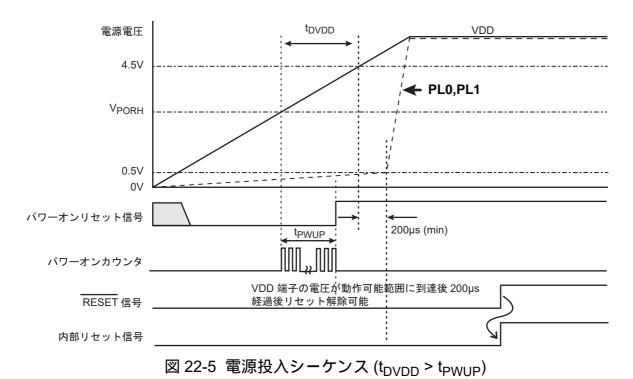

本デバイスはパワーオンリセットを内蔵しており、電源投入時にパワーオンリセット信号を発生します。

また、外部からリセットをかける場合は、電源電圧が動作範囲内であり、かつ、高周波発振器の発振が安定した状態で、RESET 端子入力を少なくとも 12 システムクロック間 (1.2μs@10MHz 発振接続時) ローレベル "L" にしてください。

### 4.3 リセット解除後

リセット解除後は、Cortex-M3 コアの制御レジスタや内蔵 I/O レジスタは初期化されます。なお、リセット解除後は PLL 逓倍回路が停止しているので、PLL 逓倍回路を使用する場合は CGOSCCR および CGPLLSEL にて設定が必要です。

リセット例外処理をおこなった後、プログラムはリセットの割り込みサービスルーチンへ分岐します。 リセットの割り込みサービスルーチン先頭アドレスは、0x0000\_0004番地に格納します。

- 注 1) RESET 端子を "L" にした状態で電源投入することも可能です。

- 注 2) リセット動作により、内蔵 RAM のデータは保証できなくなります。

Page 19 2023/07/31

## 第5章 クロック/モード制御

### 5.1 特長

クロック / モード制御ブロックでは、クロックギアやプリスケーラクロックの選択、PLL( 逓倍回路 ) や発振器のウォーミングアップ等を設定することが可能です。

また、低消費電力モードがあり、モード遷移を行うことで電力の消費を抑えることが可能です。

本章では、クロックの制御および動作モードとモード遷移について説明します。

クロックに関連する機能としては以下のようなものがあります。

- システムクロックの制御

- プリスケーラクロックの制御

- クロック逓倍回路 (PLL) の制御

- ウォーミングアップタイマの制御

また、動作モードとして NORMAL モードと各種低消費電力モードがあり、使用方法に応じて消費電力を抑えることができます。

Page21 2023/07/31

## 5.2 レジスタ説明

## 5.2.1 レジスター覧

CG 関連のレジスタとアドレスを以下に示します。

Base Address = 0x4004 \_ 0200

| レジスタ名           | Address(Base+) |        |

|-----------------|----------------|--------|

| システムコントロールレジスタ  | CGSYSCR        | 0x0000 |

| 発振コントロールレジスタ    | CGOSCCR        | 0x0004 |

| スタンバイコントロールレジスタ | CGSTBYCR       | 0x0008 |

| PLL セレクトレジスタ    | CGPLLSEL       | 0x000C |

| Reserved        | -              | 0x0010 |

## 5.2.2 CGSYSCR(システムコントロールレジスタ)

|            | 31 | 30 | 29 | 28    | 27 | 26   | 25   | 24 |

|------------|----|----|----|-------|----|------|------|----|

| bit symbol | -  | -  | -  | -     | -  | -    | -    | -  |

| リセット後      | 0  | 0  | 0  | 0     | 0  | 0    | 0    | 0  |

|            | 23 | 22 | 21 | 20    | 19 | 18   | 17   | 16 |

| bit symbol | -  | -  | -  | -     | -  | -    | -    | -  |

| リセット後      | 0  | 0  | 0  | 0     | 0  | 0    | 0    | 1  |

|            | 15 | 14 | 13 | 12    | 11 | 10   | 9    | 8  |

| bit symbol | -  | -  | -  | FPSEL | -  |      | PRCK |    |

| リセット後      | 0  | 0  | 0  | 0     | 0  | 0    | 0    | 0  |

|            | 7  | 6  | 5  | 4     | 3  | 2    | 1    | 0  |

| bit symbol | -  | -  | -  | -     | -  | GEAR |      |    |

| リセット後      | 0  | 0  | 0  | 0     | 0  | 0    | 0    | 0  |

| Bit   | Bit Symbol | Type | 機能                                                                                                                                                         |

|-------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-18 | -          | R    | リードすると "0" が読めます。                                                                                                                                          |

| 17-16 | -          | R/W  | "01" をライトしてください。                                                                                                                                           |

| 15-13 | -          | R    | リードすると "0" が読めます。                                                                                                                                          |

| 12    | FPSEL      | R/W  | fperiph 選択<br>0: fgear<br>1: fc<br>fperiph のソースクロックを選択します。                                                                                                 |

| 11    | -          | R    | リードすると "0" が読めます。                                                                                                                                          |

| 10-8  | PRCK[2:0]  | R/W  | プリスケーラクロック選択<br>000: fperiph<br>001: fperiph/2<br>010: fperiph/4<br>011: fperiph/8<br>100: fperiph/16<br>101: fperiph/32<br>110: Reserved<br>111: Reserved |

| 7-3   | -          | R    | リードすると "0" が読めます。                                                                                                                                          |

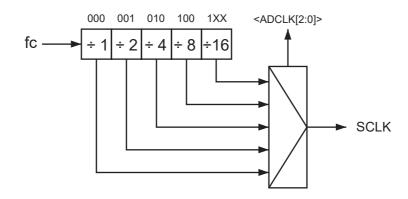

| 2-0   | GEAR[2:0]  | R/W  | 高速クロック (fc) のギア選択<br>000: fc<br>001: Reserved<br>010: Reserved<br>011: Reserved<br>100: fc/2<br>101: fc/4<br>110: fc/8<br>111: fc/16                       |

Page23 2023/07/31

## 5.2.3 CGOSCCR(発振コントロールレジスタ)

|            | 31 | 30 | 29  | 28 | 27      | 26     | 25     | 24    |  |

|------------|----|----|-----|----|---------|--------|--------|-------|--|

| bit symbol |    |    |     | WU | JODR    |        |        |       |  |

| リセット後      | 1  | 0  | 0   | 0  | 0       | 0      | 0      | 0     |  |

|            | 23 | 22 | 21  | 20 | 19      | 18     | 17     | 16    |  |

| bit symbol |    | WU | ODR |    | WUPSEL2 | HOSCON | OSCSEL | XEN2  |  |

| リセット後      | 0  | 0  | 0   | 0  | 0       | 0      | 0      | 1     |  |

|            | 15 | 14 | 13  | 12 | 11      | 10     | 9      | 8     |  |

| bit symbol | -  | -  | -   | -  | -       | -      | -      | XEN1  |  |

| リセット後      | 0  | 0  | 0   | 0  | 0       | 0      | 0      | 0     |  |

|            | 7  | 6  | 5   | 4  | 3       | 2      | 1      | 0     |  |

| bit symbol | -  | -  | -   | -  | WUPSEL1 | PLLON  | WUEF   | WUEON |  |

| リセット後      | 0  | 0  | 0   | 0  | 0       | 0      | 0      | 0     |  |

| Bit   | Bit Symbol  | Type | 機能                                                                                                                                                                                                                                           |

|-------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-20 | WUODR[11:0] | R/W  | 発振器用ウォーミングアップタイマの時間を設定                                                                                                                                                                                                                       |

| 19    | WUPSEL2     | R/W  | ウォーミングアップタイマ (WUP) のクロック<br>0: 内部 (OSC2)<br>1: 外部 (OSC1)<br>ウォーミングアップタイマのクロックソースを選択します。                                                                                                                                                      |

| 18    | HOSCON      | R/W  | ポート M/ 外部高速発振器選択 (注)<br>0: ポート M<br>1: 発振器 (X1 / X2)<br>外部高速発振器 (X1 / X2) とポート M のどちらを使用するか選択します。<br>外部発振器として選択する場合は、ポート M について、PMCR/PMPUP/PMPDN/PMIE=disable に設定して<br>ください ( リセット後は、全て disable)。                                            |

| 17    | OSCSEL      | R/W  | 高速発振器の切り替え<br>0: 内部 (OSC2)<br>1: 外部 (OSC1)<br>高速発振を外部 (OSC1) へ切り替えます。切り替え後は高速発振器が外部 (OSC1) へ切り替わった事<br>( <oscsel>="1") を確認し、内蔵発振器は速やかに停止してください。また、外部発振器に切り替え後は<br/>本ピットの書き替えによる内蔵発振器に切り替えを行わないでください。</oscsel>                                |

| 16    | XEN2        | R/W  | 高速発振器 2 (内部: OSC2)<br>0: 停止<br>1: 発振<br>高速発振器 2(OSC2) の動作を選択します。                                                                                                                                                                             |

| 15-12 | -           | R/W  | "0" をライトしてください。                                                                                                                                                                                                                              |

| 11-10 | _           | R    | リードすると "0" が読めます。                                                                                                                                                                                                                            |

| 9     | -           | R/W  | "0" をライトしてください。                                                                                                                                                                                                                              |

| 8     | XEN1        | R/W  | 高速発振器 1 (外部: OSC1)<br>0: 停止<br>1: 発振<br>高速発振器 1(OSC1) の動作を選択します。                                                                                                                                                                             |

| 7-4   | -           | R    | リードすると "0" が読めます。                                                                                                                                                                                                                            |

| 3     | WUPSEL1     | R/W  | ウォーミングアップタイマ (WUP) のクロック<br>"0" を設定してください。                                                                                                                                                                                                   |

| 2     | PLLON       | R/W  | PLL 動作<br>0: 停止<br>1: 発振<br>PLL( 逓倍回路)の動作を選択します。<br>リセット解除後は停止状態です。PLL を使用する場合はこのビットをセットします。                                                                                                                                                 |

| 1     | WUEF        | R    | ウォーミングアップタイマ (WUP) ステータス<br>0: ウォーミングアップ終了<br>1: ウォーミングアップ中<br>このビットを読むことでウォーミングアップタイマの動作状態を確認できます。                                                                                                                                          |

| 0     | WUEON       | W    | ウォーミングアップタイマ (WUP) 制御 0: don't care 1: ウォーミングアップスタート このビットをセットすることでウォーミングアップタイマがスタートします。  (注)自動ウォーミングアップする低消費電力モード (表 5-6)からの復帰では、本レジスタの設定をする必要はありません。ソフトにて WUP スタートした場合にはウォーミングアップが終了していること ( <wuef> = "0")を確認してから、モード遷移するようにしてください。</wuef> |

注) <HOSCON>="1" 設定時、ポート M のすべてのレジスタにアクセスできなくなります。 (読み出すと常に "0" が読まれます) また、PMDATA,PMOD を除くポート M のレジスタのいずれかが "0" でない場合、 <HOSCON> を "1" に設定することはできません。

Page25 2023/07/31

## 5.2.4 CGSTBYCR(スタンバイコントロールレジスタ)

|            | 31 | 30 | 29 | 28 | 27 | 26 | 25   | 24   |

|------------|----|----|----|----|----|----|------|------|

| bit symbol | -  | -  | -  | -  | -  | -  | -    | -    |

| リセット後      | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    |

|            | 23 | 22 | 21 | 20 | 19 | 18 | 17   | 16   |

| bit symbol | -  | -  | -  | -  | -  | -  | -    | DRVE |

| リセット後      | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    |

|            | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    |

| bit symbol | -  | -  | -  | -  | -  | -  | -    | RXEN |

| リセット後      | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 1    |

|            | 7  | 6  | 5  | 4  | 3  | 2  | 1    | 0    |

| bit symbol | -  | -  | -  | -  | -  |    | STBY | _    |

| リセット後      | 0  | 0  | 0  | 0  | 0  | 0  | 1    | 1    |

| Bit   | Bit Symbol | Туре | 機能                                                                                                                                             |

|-------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-18 | -          | R    | リードすると "0" が読めます。                                                                                                                              |

| 17    | -          | R/W  | "0" をライトしてください。                                                                                                                                |

| 16    | DRVE       | R/W  | STOP モード中の端子状態制御<br>0: STOP モード中端子をドライブしません<br>1: STOP モード中も端子をドライブします                                                                         |

| 15-10 | -          | R    | リードすると "0" が読めます。                                                                                                                              |

| 9     | -          | R/W  | "0" をライトしてください。                                                                                                                                |

| 8     | RXEN       | R/W  | STOP モード解除後の高速発振器の動作選択<br>"1" を設定してください。                                                                                                       |

| 7-3   |            | R    | リードすると "0" が読めます。                                                                                                                              |

| 2-0   | STBY[2:0]  | R/W  | 低消費電力モード選択 000: Reserved 001: STOP 010: Reserved 011: IDLE 100: Reserved 101: Reserved 110: Reserved 110: Reserved 111: Reserved 111: Reserved |

## 5.2.5 CGPLLSEL(PLL セレクトレジスタ)

|            | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24     |

|------------|----|----|----|----|----|----|----|--------|

| bit symbol | -  | -  | -  | -  | -  | -  | -  | -      |

| リセット後      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      |

|            | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

| bit symbol | -  | -  | -  | -  | -  | -  | -  | -      |

| リセット後      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      |

|            | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8      |

| bit symbol | -  | -  | -  | -  | -  | -  | -  | -      |

| リセット後      | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1      |

|            | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

| bit symbol | -  | -  | -  | -  | -  | -  | -  | PLLSEL |

| リセット後      | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 0      |

| Bit   | Bit Symbol | Type | 機能                                                                                                                                                                            |

|-------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-16 | -          | R    | リードすると "0" が読めます。                                                                                                                                                             |

| 15-12 | -          | R/W  | "1010" をライトしてください。                                                                                                                                                            |

| 11    | -          | R    | リードすると "0" が読めます。                                                                                                                                                             |

| 10-1  | -          | R/W  | "00_1001_1111" をライトしてください。                                                                                                                                                    |

| 0     | PLLSEL     | R/W  | PLL 選択         0: fosc         1: PLL 使用         PLL で逓倍されたクロック (f <sub>PLL</sub> ) をシステムクロック: fc へのクロックソースとするか選択します。         リセット解除後は "fosc" が 選択されているので、PLL を使用する場合は設定が必要です |

Page27 2023/07/31

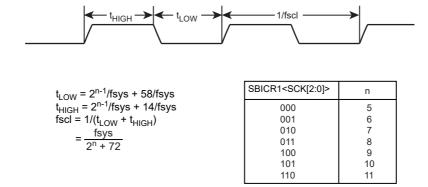

### 5.3 クロック制御

#### 5.3.1 クロックの種類

クロックの一覧を以下に示します。

fosc1 : X1, X2 端子より入力されるクロック

fosc2 : 内蔵発振器より入力されるクロック

fosc : fosc1 または fosc2 どちらか選択されたシステムクロック

f<sub>PLL</sub>: PLL により逓倍 (8 逓倍 ) されたクロック

fc : CGPLLSEL<PLLSEL> で選択されたクロック(高速クロック)

fgear : CGSYSCR<GEAR[2:0]> で選択されたクロック fsys : fgear と同一クロック(システムクロック) fperiph : CGSYSCR<FPSEL> で選択されたクロック

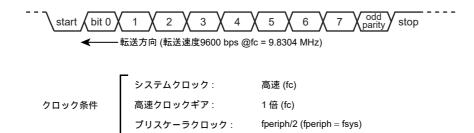

高速クロック fc と、プリスケーラクロック \$T0 は以下のように分周することが可能です。

高速クロック : fc, fc/2, fc/4, fc/8, fc/16

プリスケーラクロック : fperiph, fperiph/2, fperiph/4, fperiph/8, fperiph/16, fperiph/32

### 5.3.2 リセット動作による初期値

リセット動作により、クロックの設定は下記のような状態に初期化されます。

外部高速発振器 (OSC1) : 停止 (X1,X2)

内部高速発振器 (OSC2) : 発振 PLL ( 逓倍回路 ) : 停止

高速クロックギア : fc (分周なし)

リセット動作により、すべてのクロックの設定が fosc2 と同じになります。

```

\begin{split} f_{C} &= f_{OSC2} \\ f_{SYS} &= f_{C} \; (= f_{OSC2} \; ) \\ f_{periph} &= f_{C} \; (= f_{OSC2} \; ) \\ \phi T0 &= f_{periph} \; (= f_{OSC2} \; ) \end{split}

```

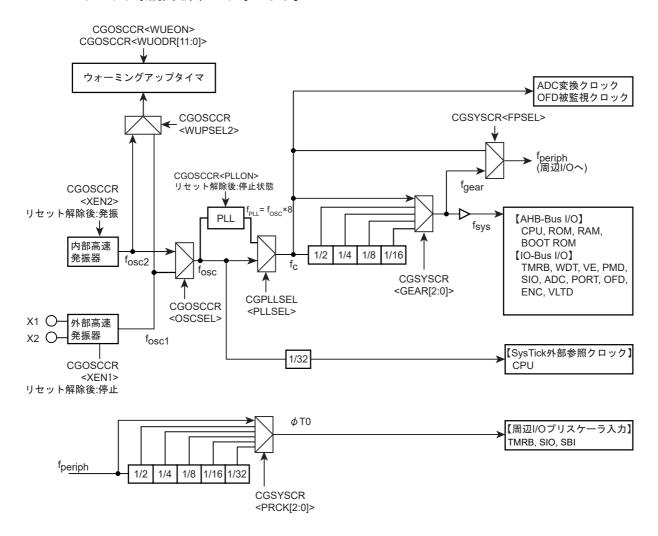

#### 5.3.3 クロック系統図

クロック系統図を図5-1に示します。

図 5-1 クロック系統図

セレクタに入力されるクロックのうち、矢印つきのものがリセット後の初期状態として選択されます。

Page29 2023/07/31

### 5.3.4 クロック逓倍回路 (PLL)

高速発振器の出力クロック fosc を 8 逓倍した  $f_{PLL}$  クロックを出力する回路です。これにより、発振器への入力周波数は低く内部クロックは高速にすることが可能です。

PLL はリセット解除後、ディセーブル状態です。PLL を有効にするためには、CGOSCCR<PLLON>を"1" に設定し、CGPLLSEL<PLLSEL> を "1" に設定することで fosc を 8 逓倍した  $f_{PLL}$  クロックを出力することができます。なお、PLL の動作が安定するまでの時間をウォーミングアップ機能等を用いて確保する必要があります。

注) PLL 動作開始の PLL 安定時間は、約 200 µs です。

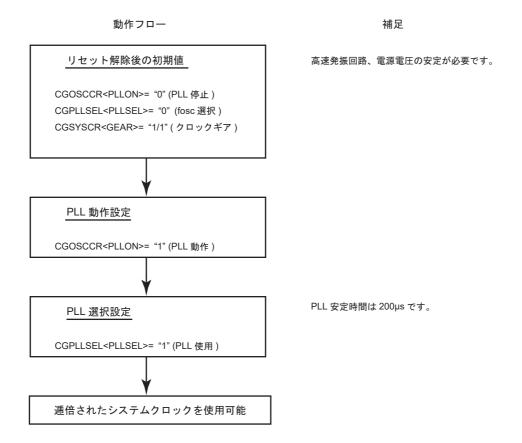

#### 5.3.4.1 PLL 設定シーケンス

以下にリセット解除後の PLL 設定シーケンスを示します。

注) PLL を停止する場合は、CGPLLSEL<PLLSEL>="0" を設定後、CGPLLSEL<PLLSEL> をリードして"0" となっている事を確認した後に CGOSCCR<PLLON>= "0"(PLL 停止)を設定してください。

### 5.3.5 ウォーミングアップ機能

ウォーミングアップ機能は、STOP モード解除時に、ウォーミングアップタイマを用いて発振子の発振安定時間や、PLL の安定時間を確保するための機能です。詳細機能については「5.6.6 ウォーミングアップ」にて説明します。

注) ウォーミングアップタイマ動作中に、低消費電力モードへ遷移しないでください。

ウォーミングアップ機能は、STOP モードからの復帰の際にも使用されます。この場合には、低消費電力モードからの復帰割り込みが発生すると自動的にタイマがカウントを開始し、設定された時間のカウント終了後、システムクロックが出力され CPU が動作を開始します。

STOP モードでは PLL がディセーブルになるため、復帰の際には内部発振器の安定のほかに、PLL の安定時間も考慮してウォーミングアップ時間を設定してください。

ウォーミングアップ機能の設定方法を説明します。

1. クロックの選択

ウォーミングアップカウンタのカウントアップクロックを CGOSCCR<WUPSEL1> および <WUPSEL2> で選択します。(<WUPSEL1> は "0" を、<WUPSEL2> は "0" または "1" を設定してください。)

2. ウォーミングアップカウンタ設定値の算出

ウォーミングアップ時間は CGOSCCR<WUODR[11:0]> により任意の値が設定可能です。

以下にウォーミングアップ時間の計算式と設定例を示します。

< 例 > 高速発振子 8MHz 使用時、ウォーミングアップ時間 5ms を設定する場合

$$\frac{ \text{ウォーミングアップ時間}}{ \text{ウォームアップクロック周期}} = \frac{5\text{ms}}{1/8\text{MHz}} = 40,000サイクル = 0x9C40$$

下位 4 ビットを切り捨て、0x9C4 を CGOSCCR<WUODR[11:0]> に設定

3. ウォーミングアップの開始および終了確認

ウォーミングアップタイマのスタートおよび終了確認は、CGOSCCR<WUEON><WUEF>を使用してソフトウエア(命令)により行います。

注) ウォーミングアップタイマは発振クロックで動作しているため、発振周波数にゆらぎがある場合は誤差を含みます。従って概略時間としてとらえる必要があります。

Page31 2023/07/31

## 以下に、ウォーミングアップ機能の設定例を示します。

#### ウォーミングアップ機能設定例 (外部発振の場合)

CGOSCCR<WUPSEL1> = "0" : ウォーミングアップタイマクロック設定

CGOSCCR<WUPSEL2> = "1" : ウォーミングアップタイマクロック設定 (1: 外部 (OSC1))

CGOSCCR<WUODR[11:0]> = "0x9C4" : ウォーミングアップ時間設定

内部発振器から外部発振器への切り替えは5.3.6を参照してください

CGOSCCR<WUEON>="1" : ウォーミングアップタイマ (WUP) スタート

CGOSCCR<WUEF> リード : "0"(WUP 終了 ) になるまでウエイト

#### 5.3.6 システムクロック

システムクロックは高速クロックのみですが、内部発振器と外部発振器のどちらかを選択して使用します。リセット解除時は内部発振器が有効(発振)となっており、外部発振器は停止しています。高速クロックは分周することができます。

• X1, X2 入力周波数: 8 MHz ~ 10MHz

• 内部発振入力周波数:10MHz

• クロックギア: 1/1, 1/2, 1/4, 1/8, 1/16(リセット後は 1/1 分周)

#### 表 5-1 高速クロック範囲 (単位は MHz)

| 入力周波数 最低動作<br>周波数 |    | 最低動作 最大動作 |                          | リセット後 | クロックギア (CG) PLL = ON 時 |     |     |      | クロックギア (CG) PLL = OFF 時 |     |     |     |      |   |

|-------------------|----|-----------|--------------------------|-------|------------------------|-----|-----|------|-------------------------|-----|-----|-----|------|---|

|                   |    | 周波数       | (PLL = OFF,<br>CG = 1/1) | 1/1   | 1/2                    | 1/4 | 1/8 | 1/16 | 1/1                     | 1/2 | 1/4 | 1/8 | 1/16 |   |

| 0004              | 8  |           |                          | 8     | 64                     | 32  | 16  | 8    | 4                       | 8   | 4   | 2   | 1    | - |

| OSC1              | 10 | 1         | 80                       | 10    | 80                     | 40  | 20  | 10   | 5                       | 10  | 5   | 2.5 | 1.25 | - |

| OSC2              | 10 |           |                          | 10    | 80                     | 40  | 20  | 10   | 5                       | 10  | 5   | 2.5 | 1.25 | - |

注 1) PLL=ON / OFF は CGOSCCR<PLLON> で設定します。

注 2) 高速クロックの分周の切り替えは、CGSYSCR<GEAR[2:0]> へ値を書き込むことにより実行されます。書き込み後、実際に切り替わるまでに若干の時間を要します。

注3) PLL=OFF 時、クロックギアの 1/16 は設定しないでください。

注 4) SysTick 使用時、クロックギアの 1/16 は設定しないでください。

内部発振器から外部発振器への切り替え手順を以下に示します。

1. PMCR / PMPUP / PMPDN / PMIE の該当ビット = "0" :PM0, PM1 について禁止(リセット後は、全て禁止)

2. CGOSCCR<WUODR[11:0]> = " ウォーミングアップ時間 " : ウォーミングアップ時間設定

3. CGOSCCR<HOSCON>="1" : 外部発振使用:PM0,PM1 X1,X2

4. CGOSCCR<XEN1> = "1" : 高速発振器 (OSC) の発振

5. CGOSCCR<WUPSEL2> = "1" : ウォーミングアップタイマクロック設定 (1: 外部 (OSC1))

6. CGOSCCR<WUEON>="1" : ウォーミングアップタイマ (WUP) スタート

CGOSCCR<WUEF> リード : "0" (WUP 終了) になるまでウエイト

7. CGOSCCR<OSCSEL> = "1" : 高速発振器を外部発振器 (OSC1) に切り替え

8. CGOSCCR<OSCSEL> リード : 外部発振選択を確認 (<OSCSEL> = "1")

9. CGOSCCR<XEN2> = "0" : 内部発振停止

なお、CGOSCCR < HOSCON > = "1" と設定したあとはポート M の全てのレジスタのアクセスが禁止されるため、ポート M の設定値を変更する事はできません。

Page33 2023/07/31

## 5.3.7 プリスケーラクロック

周辺機能には、それぞれにクロックを分周するプリスケーラがあります。これらのプリスケーラへ入力するクロック  $\phi$ TO は、CGSYSCR<FPSEL> から選択されたクロック fperiph をさらに CGSYSCR<PRCK[2:0]> にて分周することが可能です。リセット後の  $\phi$ TO は fperiph/1 が選択されます。

注) クロックギアを使用する場合、周辺 I/O の各プロックのプリスケーラ出力  $\phi$ Tn は、 $\phi$ Tn < fsys を満足するように時間設定 ( $\phi$ Tn が fsys よりも遅くなるように)してください。また、タイマカウンタなどの周辺 I/O 動作中にクロックギアを切り替えないようにしてください。

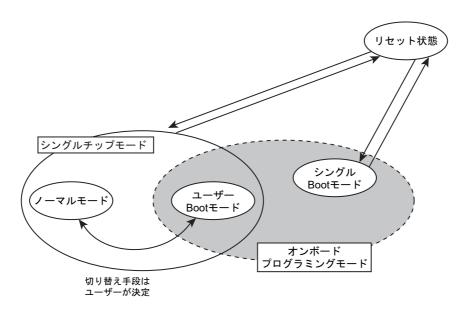

## 5.4 モードとモード遷移

#### 5.4.1 モード状態遷移

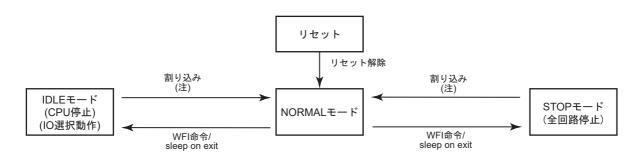

動作モードとしてシステムクロックに高速クロックを使用する NORMAL モードがあります。

プロセッサコアの動作を停止して電力の消費を抑える低消費電力モードとして、IDLE モード、STOP モードがあります。

図 5-2 にモード状態遷移図を示します。

WFI 命令、Sleep-on-exit については、"Cortex-M3 テクニカルリファレンスマニュアル" を参照してください。

図 5-2 モード状態遷移図

注) 復帰時にウォーミングアップが必要となります。ウォーミングアップ時間の設定は STOP モードに入る前のモード (NORMAL) にて設定する必要があります。ウォーミングアップ時間に関しては、「5.6.6 ウォーミングアップ」を参照してください。

## 5.5 動作モード

動作モードには NORMAL モードがあります。NORMAL モードの特長は次のとおりです。

#### 5.5.1 NORMAL モード

CPU コアおよび周辺ハードウエアを高速クロックで動作させるモードです。リセット解除後は、NORMAL モードになります。

Page35 2023/07/31

## 5.6 低消費電力モード

低消費電力モードには、IDLE, STOP モードがあります。低消費電力モードに移行するには、システムコントロールレジスタ CGSTBYCR<STBY[2:0]> にてモードを選択し、WFI(Wait For Interrupt) 命令を実行します。WFI 命令によって低消費電力モードへ移行した場合、低消費電力モードからの復帰はリセットまたは割り込み発生により行われます。割り込みで復帰する場合には、設定を行っておく必要があります。詳細は「例外」の章の「割り込み」を参照してください。

- 注 1) 本製品ではイベントによる復帰はサポートしていないため、WFE (Wait For Event) による低消費電力モードへの 移行は行わないでください。

- 注 2) 本製品は、Cortex-M3 コアの SLEEPDEEP による低消費電力モードはサポートしていません。システム制御レジスタの <SLEEPDEEP> ビットは設定しないでください。

IDLE, STOP モードの特長は次のとおりです。

#### 5.6.1 IDLE モード

CPU のみが停止するモードです。周辺機能は、各モジュールの中のレジスタに IDLE モード時の動作 / 停止設定レジスタを 1 ビット持ち、IDLE モードでの動作設定が可能です。IDLE モード時に動作停止に設定された周辺機能は、IDLE モードへ遷移した時の状態で停止します。

以下に IDLE モードでの動作を設定できる周辺機能の一覧を示します。設定方法は、各機能の章を参照してください。

- 16 ビットタイマ / イベントカウンタ (TMRB)

- シリアルチャネル (SIO/UART)

- シリアルバスインタフェース (I2C/SIO)

- ウォッチドッグタイマ (WDT)

- ベクトルエンジン (VE)

- 注) ウォッチドッグタイマは IDLE モードへ遷移する前に停止してください。

## 5.6.2 STOP モード

STOP モードでは、内部発振器も含めてすべての内部回路が停止します。

STOP モードが解除されると、STOP モードへ移行する直前の動作モードへ復帰し、動作を開始します。

STOP モードでは、CGSTBYCR<DRVE>の設定により端子の状態を設定することができます。STOP モード時の端子状態を表 5-2 に示します。

表 5-2 STOP モード時の端子状態

|           | 機能                                                                                                       | 入出力  | <drve> = 0</drve>             | <drve> = 1</drve>  |  |

|-----------|----------------------------------------------------------------------------------------------------------|------|-------------------------------|--------------------|--|

| ポート<br>以外 | RESET, MODE                                                                                              | 入力専用 | 0                             |                    |  |

|           | X1                                                                                                       | 入力専用 | ×                             |                    |  |

|           | X2                                                                                                       | 出力専用 | "High" レ                      | ベル出力               |  |

|           | TMS TCK TDI TRST                                                                                         | 入力   | o                             |                    |  |

|           | TDO                                                                                                      | 出力   |                               | iはイネーブル<br>はディセーブル |  |

|           | SWCLK                                                                                                    | 入力   |                               | 0                  |  |

|           |                                                                                                          | 入力   | 0                             |                    |  |

|           | SWDIO                                                                                                    | 出力   | データ有効時はイネーブル<br>データ無効時はディセーブル |                    |  |

| ポート       | TRACECLK<br>TRACEDATA0<br>TRACEDATA1<br>SWV                                                              | 出力   | o                             |                    |  |

|           | U00,1<br>V00,1<br>W00,1<br>X00,1<br>Y00,1<br>Z00,1                                                       | 出力   | ×                             | o                  |  |

|           | INT0, INT1, INT2<br>INT3, INT4, INT5<br>INT6, INT7, INT8<br>INT9, INTA, INTB<br>INTC, INTD, INTE<br>INTF | λカ   | o                             |                    |  |

|           | 上記以外の機能端子また                                                                                              | 入力   | ×                             | o                  |  |

|           | は汎用入出力として使用                                                                                              | 出力   | ×                             | o                  |  |

o:入力または出力がイネーブルであることを示します。

Page37 2023/07/31

<sup>×:</sup> 入力または出力がディセーブルであることを示します。

## 5.6.3 低消費電力モードの選択

低消費電力モード選択は、CGSTBYCR<STBY[2:0]> の設定で選択されます。 表 5-3 に <STBY[2:0]> の設定より選択されるモードを示します。

表 5-3 低消費電力モードと設定

| モード  | CGSTBYCR<br><stby[2:0]></stby[2:0]> |

|------|-------------------------------------|

| STOP | 001                                 |

| IDLE | 011                                 |

注)上記以外の設定は行わないでください。

## 5.6.4 各モードにおける動作状態

各モードにおける動作状態を表 5-4 に示します。

IO ポートについては「o」は入出力の有効、「 $\times$ 」は無効を、その他の機能については「o」はクロックが供給されていることを、「 $\times$ 」は供給されていないことを示します。

表 5-4 各動作モードにおける動作状態

| ブロック       | NORMAL | IDLE      | STOP   |

|------------|--------|-----------|--------|

| プロセッサコア    | 0      | ×         | ×      |

| I/O ポート    | o      | o         | * (注1) |

| PMD        | o      | o         | ×      |

| ENC        | o      | o         | ×      |

| OFD        | o      | o         | ×      |

| ADC        | o      | o         | ×      |

| VE         | 0      |           | ×      |

| SIO        | o      | モジュールご    | ×      |

| SBI        | o      | とに動作 / 停止 | ×      |

| TMRB       | o      | 選択可能      | ×      |

| WDT        | o      |           | ×      |

| VLTD       | 0      | 0         | o(注2)  |

| POR        | 0      | o         | o (注2) |

| CG         | 0      | 0         | ×      |

| PLL        | 0      | 0         | ×      |

| 高速発振器 (fc) | o      | o         | ×      |

o:対象のモード中に動作が可能

- 注 1) CGSTBYCR<DRVE> の設定によります。

- 注 2) クロックは供給されていませんが、動作停止しません。

Page39 2023/07/31

<sup>×:</sup>対象のモードに移行すると自動的にモジュールへのクロックが停止

#### 5.6.5 低消費電力モードの解除

低消費電力モードからの解除は、割り込み、リセットによって行うことができます。使用できるスタンバイ解除ソースは、低消費電力モードにより決まります。詳細を表 5-5 に示します。

表 5-5 解除ソースと解除可能なモード

|           | 低消費電力モード     |                                                                              |   | STOP |

|-----------|--------------|------------------------------------------------------------------------------|---|------|

|           |              | INT0~F (注 1)                                                                 | o | 0    |

|           |              | INTRX0~3, INTTX0~3                                                           | o | ×    |

|           |              | INTVCNA, INTVCNB                                                             | o | ×    |

|           |              | INTEMG0~1                                                                    | o | ×    |

|           |              | INTOVV0~1                                                                    | o | ×    |

|           |              | INTADAPDA, INTADBPDA,<br>INTADAPDB, INTADBPDB                                | o | ×    |

| 解除<br>ソース | 割り<br>込み     | INTTB00, 10, 20, 30, 40, 50, 60, 70<br>INTTB01, 11, 21, 31, 41, 51, 61, 71   | o | ×    |

|           |              | INTPMD0, 1                                                                   | o | ×    |

|           |              | INTCAP00, 10, 20, 30, 40, 50, 60, 70<br>INTCAP01, 11, 21, 31, 41, 51, 61, 71 | o | ×    |

|           |              | INTADACPA, INTADBCPA,<br>INTADACPB, INTADBCPB                                | o | ×    |

|           |              | INTADASFT, INTADBSFT                                                         | o | ×    |

|           |              | INTADATMR, INTADBTMR                                                         | o | ×    |

|           |              | INTENC0, INTENC1                                                             | o | ×    |

|           |              | INTSBI                                                                       | o | ×    |

|           | SysTick 割り込み |                                                                              | o | ×    |

|           | マスク不能        | l割り込み (INTWDT)                                                               | o | ×    |

|           | RESET (R     | ESET 端子)                                                                     | o | О    |

- o: 解除後、割り込み処理を開始します (RESET は本製品を初期化します)。

- ×: 解除に使用できません。

- 注 1) レベルモードの割り込みによる解除を行う場合、割り込み処理が開始されるまでレベルを保持してください。それ以前でレベルを変化させた場合は、正しい割り込み処理を開始できません。

- 注 2) 低消費電力モードへ移行する場合は、CPU で復帰要因以外の割り込みを禁止してください。禁止していないと復帰要因以外の割り込みで解除が行われる場合があります。

- 注 3) 各モードからの復帰に必要なウォーミングアップについては「5.6.6 ウォーミングアップ」を参照してください。

### • 割り込み要求による解除

割り込みによって低消費電力モードを解除する場合、CPU で割り込みが検出されるよう 準備しておく必要があります。STOP モードの解除に使用する割り込みは、CPU の設定の ほかにクロックジェネレータで割り込み検出の設定を行う必要があります。

• マスク不能割り込み (NMI) による解除

マスク不能割り込みの要因には、WDT 割り込み (INTWDT) があります。INTWDT は IDLE モードでのみ使用可能です。

• リセットによる解除

RESET 端子によるリセットですべての低消費電力モードからの解除を行うことができます。リセットで解除した場合には通常のリセット動作と同様になり、解除後は NORMAL モードですべてのレジスタが初期化された状態になります。

• SysTick 割り込みによる解除

SysTick 割り込みは IDLE モードでのみ使用可能です。

割り込みの詳細に関しては、「例外」の章の「割り込み」をご参照ください。

Page41 2023/07/31

## 5.6.6 ウォーミングアップ

モード遷移の際には内部発振器 (OSC2) の安定のためウォーミングアップが必要な場合があります。

STOP モードから NORMAL モードへの遷移では、自動的にウォーミングアップ用カウンタが起動され、設定されているウォーミングアップ時間経過後にシステムクロックの出力が開始されます。このため、STOPモードに移行する命令を実行する前に CGOSCCR<WUPSEL1><WUPSEL2>でウォーミングアップする発振器の選択(注1)および、CGOSCCR<WUODR>でウォーミングアップ時間の設定を行ってください。

- 注 1) TMPM376FDDDFG/FDFGでは、常にCGOSCCR<WUPSEL1>=0を設定してください。

- 注 2) STOP モードでは PLL がディセーブルになるため、STOP モード解除の際には内部発振器の安定のほかに、PLL の安定時間も考慮してウォーミングアップ時間を設定してください。PLL の安定時間は、約 200 us です

- 注 3) 自動ウォーミングアップする低消費電力モードからの復帰では、CGOSCCR<WUEON> の設定をする必要 はありません。

各動作モード遷移時におけるウォーミングアップ有無を表 5-6 に示します。

表 5-6 各動作モード遷移時のウォーミングアップ設定

| 動作モード遷移           | ウォーミングアップ設定 |

|-------------------|-------------|

| $NORMAL \to IDLE$ | 不要          |

| $NORMAL \to STOP$ | 不要          |

| $IDLE \to NORMAL$ | 不要          |

| $STOP \to NORMAL$ | 自動ウォーミングアップ |

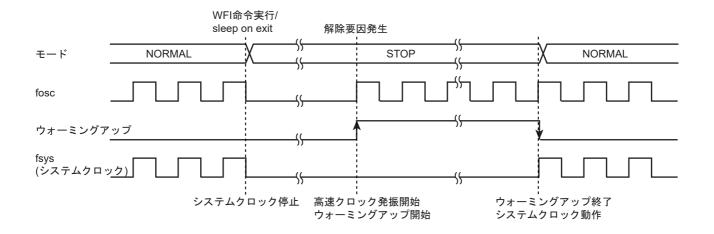

## 5.6.7 モード遷移によるクロック動作

モード遷移の際の、クロック動作について示します。

### 5.6.7.1 NORMAL → STOP → NORMAL 動作モード遷移

STOP モードから NORMAL モードへ復帰する場合、ウォーミングアップは自動的に起動します。STOP モードへ遷移する前にウォーミングアップ時間の設定を行ってください。

リセットで NORMAL モードへ復帰する場合にはウォーミングアップは行われませんので、発振動作が安定するまでリセット信号を有効に保ってください。

Page43 2023/07/31

# 第6章 例外

この章では、例外の特長、種類、処理について概略を説明します。

例外は CPU のアーキテクチャと深くかかわる部分ですので、必要に応じて "Cortex-M3 テクニカルリファレンスマニュアル"もご覧ください。

## 6.1 概要

例外は CPU に対し現在実行中の処理を中断して別の処理に移ることを要求するものです。

例外には、何らかの異常な状態が起こったときや例外を発生する命令を実行したときに発生するものと、外部端子や周辺機能からの割り込み要求信号といった、ハードウエアによる要因で発生する割り込みがあります。

すべての例外は優先度にしたがって CPU 内にあるネスト型ベクタ割り込みコントローラ (NVIC) によって処理されます。例外が発生すると、CPU はそのときの状態をスタックに退避し、割り込み処理ルーチンへ分岐します。割り込み処理ルーチンの実行後、スタックに退避した情報は自動的に復帰されます。

## 6.1.1 種類

例外には以下のようなものがあります。

それぞれの例外の詳細な内容は、"Cortex-M3テクニカルリファレンスマニュアル"をご覧ください。

- ・リセット

- マスク不能割り込み (NMI)

- ハードフォールト

- メモリ管理

- ・バスフォールト

- 用法フォールト

- SVCall (スーパバイザコール)

- デバッグモニタ

- PendSV

- SysTick

- 外部割り込み

Page45 2023/07/31

6.1.2.4 節

# 6.1.2 処理の流れ

例外からの復帰

| ウエアによる                 | みの処理の流れの概略を以下に示します。以下の説明で、<br>処理を、 | <u></u> はハード<br>ます。 |

|------------------------|------------------------------------|---------------------|

| 処理                     | 内容                                 | 説明                  |

| CG/CPU が<br>例外を検出      | CG/CPU が例外要求を検出します。                | 6.1.2.1 節           |

| $\Box$                 |                                    |                     |

| CPU が例外を処理             | CPU が例外処理を行います。                    |                     |

| $\Box$                 |                                    | 6.1.2.2 節           |

| CPU が割り込み<br>処理ルーチンへ分岐 | 検出した例外に応じた割り込み処理ルーチンへ分岐します。        |                     |

| $\Box$                 |                                    |                     |

| 割り込み処理ルーチン<br>実行       | 必要な処理を行います。                        | 6.1.2.3 節           |

| $\Box$                 |                                    |                     |

別の割り込み処理ルーチンまたはもとのプログラムに復帰します。

#### 6.1.2.1 例外要求と検出

#### (1) 例外要求の発生

例外は、CPU の命令実行, メモリアクセス, 外部割り込み端子や周辺機能からの割り込み要求などにより発生します。

CPU の命令実行による例外の要求は、例外を発生する命令の実行や、命令実行中の異常が要因で発生します。

メモリアクセスによる例外の要求は、実行不可領域からの命令フェッチや、フォールト 領域へのアクセスにより発生します。

割り込みの要求は、外部割り込み端子からの信号入力や周辺機能から発生します。スタンバイ解除に使用する割り込みの場合、クロックジェネレータの設定も必要になります。詳細は「6.5割り込み」の節で説明します。

#### (2) 例外の検出

複数の例外が同時に検出された場合には、CPU は優先度にしたがって最も優先度の高い 例外を選択します。

各例外の優先度は以下のとおりです。"構成可能"と記載された例外は、優先度を設定することができます。また、メモリ管理,バスフォールト,用法フォールトは許可/禁止を選択することができます。禁止された例外が発生した場合にはハードフォールトとして扱われます。

| 耒 | 6-1 | 例外 | の種類 | 上 | <b>優先</b> 5 | 查 |

|---|-----|----|-----|---|-------------|---|

|   |     |    |     |   |             |   |

| 番号   | 例外        | 優先度     | 要因                                                                |

|------|-----------|---------|-------------------------------------------------------------------|

| 1    | リセット      | -3 (最高) | リセット端子 , WDT, POR, VLTD, OFD, SYSRESETREQ                         |

| 2    | マスク不能割り込み | -2      | WDT                                                               |

| 3    | ハードフォールト  | -1      | より優先度の高いフォールトの処理中、または禁止されているために<br>発生できないフォールト                    |

| 4    | メモリ管理     | 構成可能    | MPU(メモリ保護ユニット)からの例外(注 1)<br>実行不可 (XN) (Execute Never) 領域からの命令フェッチ |

| 5    | バスフォールト   | 構成可能    | メモリマップのハードフォールト領域に対するアクセス                                         |

| 6    | 用法フォールト   | 構成可能    | 未定義命令の実行や、命令実行によって発生するその他のエラー                                     |

| 7~10 | 予約        | -       |                                                                   |

| 11   | SVCall    | 構成可能    | SVC 命令によるシステムサービスの呼び出し                                            |

| 12   | デバッグモニタ   | 構成可能    | CPU がフォールト中でないときのデバッグモニタ                                          |

| 13   | 予約        | _       |                                                                   |

| 14   | PendSV    | 構成可能    | 保留可能なシステムサービスへの要求                                                 |

| 15   | SysTick   | 構成可能    | システムタイマからの通知                                                      |

| 16~  | 外部割り込み    | 構成可能    | 外部割り込み端子や周辺機能 (注 2)                                               |

- 注 1) 本製品は MPU を搭載していません。

- 注 2) 外部割り込みは、製品により要因と番号が異なります。具体的な要因と番号については、「6.5.1.5 要因一覧」を参照してください。

Page47 2023/07/31

#### (3)優先度の設定

#### • 優先度レベル

外部割り込みの優先度は、割り込み優先度レジスタで、それ以外の例外はシステムハンドラ優先度レジスタで該当する <PRI\_n> ビットに設定します。

<PRI\_n> は、構成を変更することが可能になっており、優先度設定のためのビット数は製品により 3 ビット~8 ビットのいずれかになります。このため、設定できる優先度の範囲も製品により異なります。

8 ビットの構成の場合、優先度は $0\sim255$  のレベルを設定できます。最も高い優先度は "0" です。複数の要因を同じ優先度に設定した場合、番号の小さい例外の優先度が高くなります。

注) 本製品では、<PRI n> ビットは3 ビットの構成になっています。

#### • 優先度のグループ化

優先度をグループ化することもできます。アプリケーション割り込みおよびリセット制御レジスタの <PRIGROUP> を設定することで、<PRI\_n> を横取り優先度とサブ優先度に分割することができます。

優先度はまず横取り優先度で判定され、横取り優先度が同じ場合サブ優先度で判定されます。サブ優先度も同じ場合は例外番号の小さいほうが優先度が高くなります。

表 6-2 に優先度のグループ化の設定についてまとめます。表中の横取り優先度数、サブ優先度数は、<PRI\_n>が8ビット構成の場合の数です。

| 表 6-2 | 優先度のグルー | プ化設定 |

|-------|---------|------|

|-------|---------|------|

| <prigroup[2:0]></prigroup[2:0]> | <pri_< th=""><th>n[7:0]&gt;</th><th></th><th colspan="2"></th></pri_<> | n[7:0]>        |         |        |  |

|---------------------------------|------------------------------------------------------------------------|----------------|---------|--------|--|

| で設定                             | 横取り<br>フィールド                                                           | サブ優先度<br>フィールド | 横取り優先度数 | サブ優先度数 |  |

| 000                             | [7:1]                                                                  | [0]            | 128     | 2      |  |

| 001                             | [7:2]                                                                  | [1:0]          | 64      | 4      |  |

| 010                             | [7:3]                                                                  | [2:0]          | 32      | 8      |  |

| 011                             | [7:4]                                                                  | [3:0]          | 16      | 16     |  |

| 100                             | [7:5]                                                                  | [4:0]          | 8       | 32     |  |

| 101                             | [7:6]                                                                  | [5:0]          | 4       | 64     |  |

| 110                             | [7]                                                                    | [6:0]          | 2       | 128    |  |

| 111                             | なし                                                                     | [7:0]          | 1       | 256    |  |

注) <PRI\_n>の構成が8ビットより小さい場合、下位ビットは"0"となります。 たとえば、3ビット構成の場合、<PRI\_n[7:5]>で優先度が設定され、<PRI\_n[4:0]>は"00000"になります。

#### 6.1.2.2 例外の処理と割り込み処理ルーチンへの分岐(横取り)

例外により、実行中の処理を中断して割り込み処理ルーチンへ分岐する動作を "横取り "と呼びます。

#### (1) レジスタの退避

例外を検出すると、CPU は 8 つのレジスタの内容を退避します。退避するレジスタと退避の順序は以下のとおりです。

- プログラムカウンタ (PC)

- プログラムステータスレジスタ (xPSR)

- r0 ~ r3

- r12

- リンクレジスタ(LR)

レジスタの退避が終了すると、SP は 8 ワード分減らされます。レジスタ退避終了後のスタックの状態は以下のようになっています。

#### (2) 割り込み処理ルーチンのフェッチ

レジスタの退避と同時に CPU は割り込み処理ルーチンの命令フェッチを行います。

各例外の割り込み処理ルーチンの先頭番地をベクタテーブルに準備しておきます。ベクタテーブルはリセット後、コード領域の  $0x0000_{-}0000$  番地に置かれます。ベクタテーブルは、ベクタテーブルオフセットレジスタを設定することでコード空間または SRAM 空間の任意のアドレスに置くことができます。

ベクタテーブルにはまた、メインスタックの初期値を設定します。

#### (3)後着

割り込み処理ルーチンの実行前に、検出した例外よりも優先度の高い例外を検出した場合、CPU は優先度の高い例外の処理に移行します。これを後着と呼びます。

Page49 2023/07/31

後着の場合、CPU は新たに検出された例外の割り込み処理ルーチンのフェッチを改めて行い、分岐しますが、再度レジスタの内容を退避することはありません。

#### (4) ベクタテーブルの構成

ベクタテーブルの構成は以下のとおりです。

最初の4ワード(スタックの先頭アドレス,リセット,NMI,ハードフォールトの割り込み処理ルーチンアドレス)は必ず設定する必要があります。その他の例外の割り込み処理ルーチンアドレスは、必要に応じて準備します。

| オフセット       | 例外        | 内容             | 備考 |

|-------------|-----------|----------------|----|

| 0x00        | リセット      | メインスタックの初期値    | 必須 |

| 0x04        | リセット      | 割り込み処理ルーチンアドレス | 必須 |

| 0x08        | マスク不能割り込み | 割り込み処理ルーチンアドレス | 必須 |

| 0x0C        | ハードフォールト  | 割り込み処理ルーチンアドレス | 必須 |

| 0x10        | メモリ管理     | 割り込み処理ルーチンアドレス | 任意 |

| 0x14        | バスフォールト   | 割り込み処理ルーチンアドレス | 任意 |

| 0x18        | 用法フォールト   | 割り込み処理ルーチンアドレス | 任意 |

| 0x1C ~ 0x28 | 予約        |                |    |

| 0x2C        | SVCall    | 割り込み処理ルーチンアドレス | 任意 |

| 0x30        | デバッグモニタ   | 割り込み処理ルーチンアドレス | 任意 |

| 0x34        | 予約        |                |    |

| 0x38        | PendSV    | 割り込み処理ルーチンアドレス | 任意 |

| 0x3C        | SysTick   | 割り込み処理ルーチンアドレス | 任意 |

| 0x40        | 外部割り込み    | 割り込み処理ルーチンアドレス | 任意 |

#### 6.1.2.3 割り込み処理ルーチンの発行

割り込み処理ルーチンでは、発生した例外に応じて必要な処理を行います。割り込み処理ルーチンはユーザが準備します。

割り込み処理ルーチンでは、通常の処理プログラムに戻ったときに再度同じ割り込みが発生しないよう、割り込み要求の取り下げなどの処理が必要になる場合があります。

割り込みについての詳細は「6.5割り込み」の節で説明します。

割り込み処理ルーチンの実行中に現在処理中の例外よりも優先度の高い例外を検出した場合、CPU は現在実行中の割り込み処理ルーチンを中断し新たに検出された例外の処理を行います。

#### 6.1.2.4 例外からの復帰

#### (1) 割り込み処理ルーチンからの復帰先

割り込み処理ルーチン終了時の状態により復帰先が決まります。

#### • テールチェイン

保留中の例外が存在し、中断されている例外処理がないかまたは中断されている どの例外よりも優先度が高い場合、保留中の例外の割り込み処理ルーチンへ復帰し ます。

このとき、スタックの退避と復帰は省略されます。この動作をテールチェインと呼びます。

• 処理が中断されている割り込み処理ルーチンへ復帰

保留中の例外がない場合、または存在しても処理が中断されている例外の優先度が高い場合、中断されている例外の割り込み処理ルーチンへ復帰します。

• 元のプログラムへ復帰

保留中の例外も処理が中断されている例外もない場合、元のプログラムへ復帰します。

#### (2) 復帰処理

CPU は、割り込み処理ルーチンから復帰する際に以下の処理を行います。

• レジスタの復帰

退避していた8つのレジスタ(PC, xPSR, r0~r3, r12, LR)を復帰しSPを調整します。

• 割り込み番号のロード

退避していた xPSR から現在有効な割り込み番号をロードします。この割り込み番号によって CPU はどの割り込みに復帰するかを制御します。

• SP の選択

例外 (ハンドラモード) へ復帰する場合、SP は SP \_ main です。スレッドモードへ 復帰する場合、SP は SP \_ main または SP \_ process です。

Page51 2023/07/31

## 6.2 リセット例外

リセット例外には、以下の6種類の要因があります。

リセットの要因を確認するためには、クロックジェネレータレジスタの CGRSTFLG を参照してください。

• 外部リセット端子

外部リセット端子を "Low" にしたのち、"High" にすることによりリセット例外が発生します。

• POR によるリセット例外

POR にリセットを発生する機能があります。詳細は「パワーオンリセット回路」の章をご覧ください。

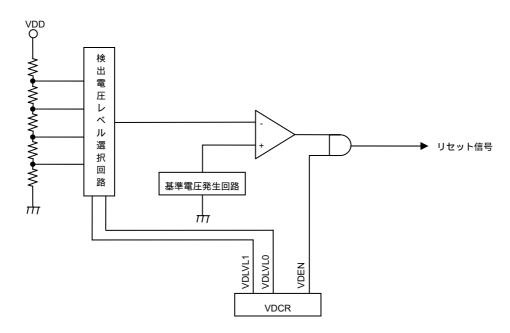

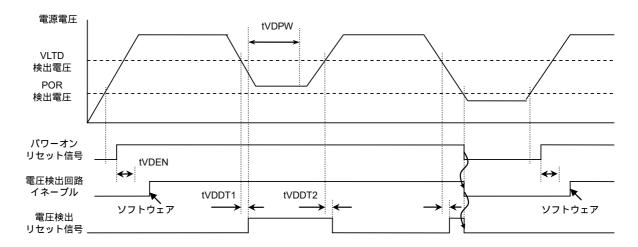

• VLTD によるリセット例外

VLTD にリセットを発生する機能があります。詳細は「電源検出回路」の章をご覧ください。

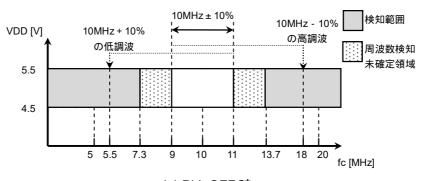

• OFD によるリセット例外

OFD にリセットを発生する機能があります。詳細は「周波数検知回路」の章をご覧ください。

• WDT によるリセット例外

WDT にリセットを発生する機能があります。詳細は「ウォッチドッグタイマ」の章をご覧ください。

• SYSRESETREQ によるリセット例外

NVIC レジスタの、アプリケーション割り込みおよびリセット制御レジスタの SYSRESETREQ ビットをセットすることで、リセットを発生させることができます。

# 6.3 マスク不能割り込み (NMI)

WDT にマスク不能割り込みを発生する機能があります。詳細は「ウォッチドッグタイマ」の章をご覧ください。

マスク不能割り込みの要因を確認するためには、クロックジェネレータレジスタの CGNMIFLG を参照してください。

## 6.4 SysTick

SysTick は、CPU の持つシステムタイマを使用した割り込み機能です。

SysTick リロード値レジスタに値を設定し、SysTick 制御およびステータスレジスタで機能をイネーブルにすると、リロード値レジスタに設定された値がカウンタへリロードされカウントダウンを開始します。カウンタが "0" になると SysTick 例外を発生します。また、例外を保留しフラグでタイマが "0" になったことを確認することもできます。

SysTick 較正値レジスタには、システムタイマで 10 ms を計測する際のリロード値が準備されています。 製品により、カウントクロックの周期は異なるため、較正値レジスタに設定されている値も異なります。

注) 本製品では外部参照クロックとして fosc( CGOSCCR<OSCSEL> で選択されるクロック) を 32 分周したクロック が使用されます。

Page53 2023/07/31

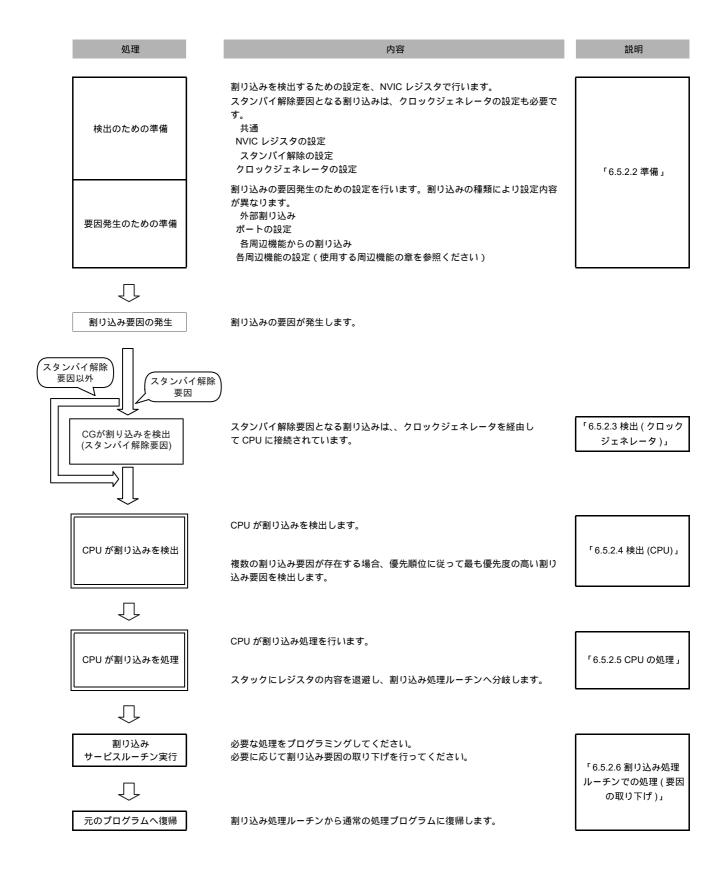

## 6.5 割り込み

この節では、割り込みの伝わる経路,要因,必要な設定について説明します。

割り込みは、割り込み要因ごとの信号により CPU へ通知されます。

CPU は、優先順位付けを行い最も優先度の高い割り込みを発生します。

スタンバイ解除に使用する割り込み要因は、クロックジェネレータを経由して CPU に要因が伝わるため、クロックジェネレータの設定も必要です。

## 6.5.1 要因

#### 6.5.1.1 経路

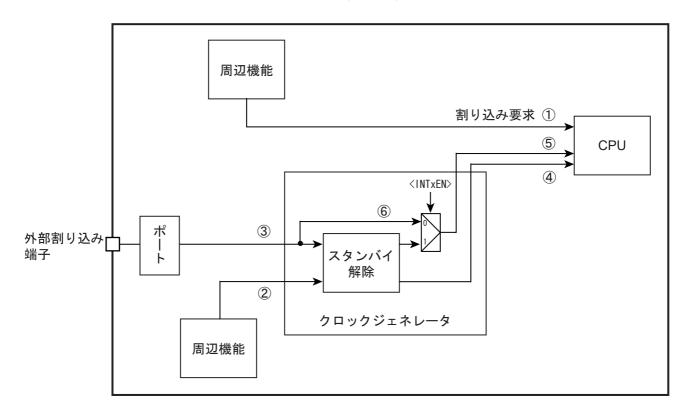

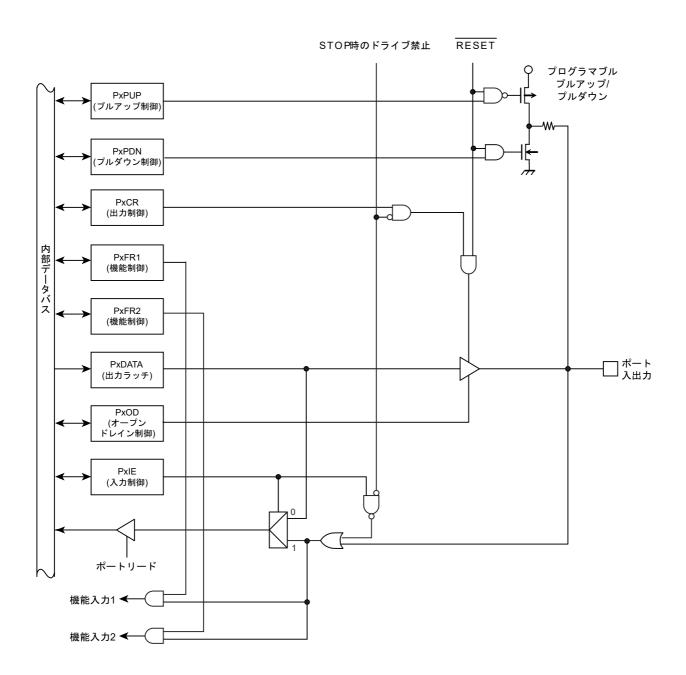

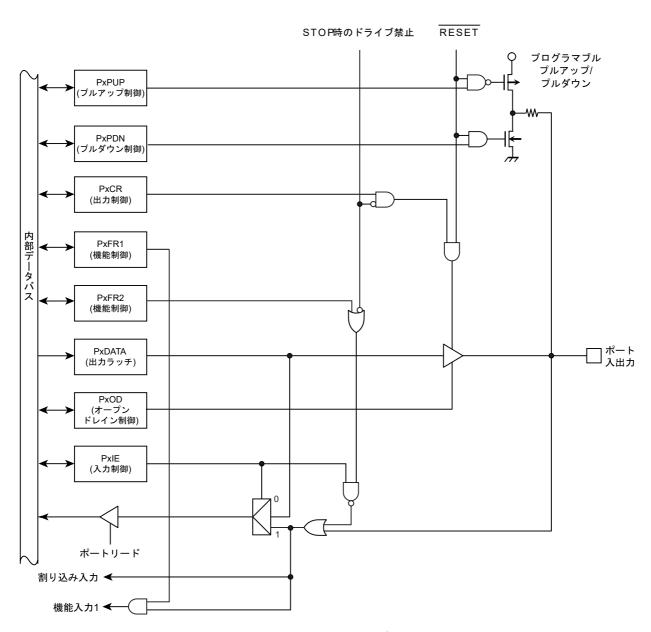

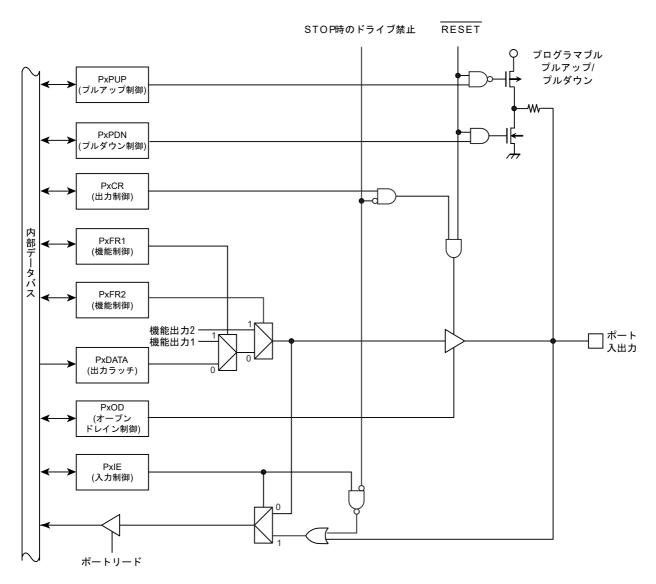

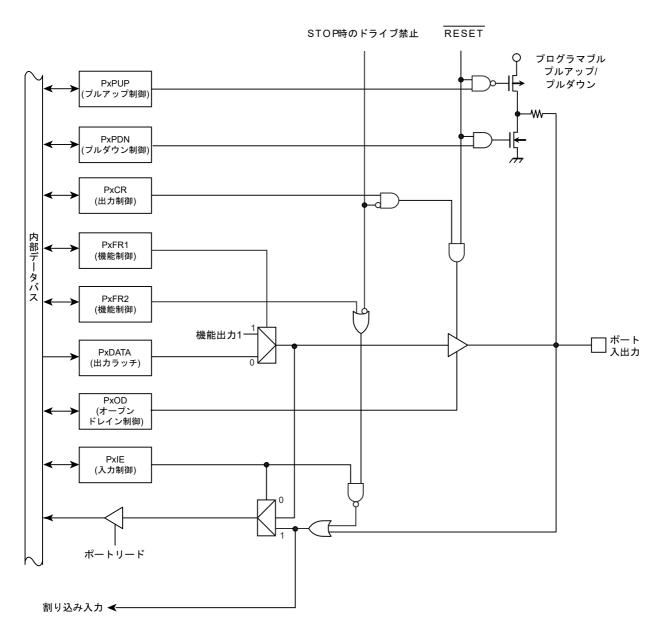

割り込み要求の経路を図 6-1 に示します。

周辺機能からの割り込み要求のうち、スタンバイ解除に使用されないものは直接 CPU に入力されます。(経路)

スタンバイ解除に使用される周辺機能割り込み (経路 ) および、外部割込み端子からの割り込み (経路 ) はクロックジェネレータに入力され、スタンバイ解除のロジックを経由して CPU に入力されます。 (経路 )

外部割込み端子からの割り込みは、スタンバイ解除に使用しない場合スタンバイ解除ロジックを経由せずに CPU に入力されます。(経路)

図 6-1 割り込みの経路

## 6.5.1.2 割り込み要因の発生

割り込み要求は、割り込み要因に割り当てられた外部端子,周辺機能,NVIC レジスタの割り込み保留セットレジスタの設定により発生します。

• 外部端子からの割り込み

外部割り込み端子を使用する場合、ポートの制御レジスタで端子を割り込み機能に 設定します。

• 周辺機能の割り込み

周辺機能の割り込みを使用する場合、使用する周辺機能で割り込みが出力されるよう設定する必要があります。

詳細は各章をご覧ください。

• 割り込みの強制的な保留

割り込み保留セットレジスタの該当する割り込みのビットをセットすることで、割り込み要因を発生させることができます。

#### 6.5.1.3 割り込み要因の伝達

外部端子/周辺機能から発生した割り込み要求のうち、スタンバイ解除要因にならないものは 直接 CPU に接続されます。

スタンバイ解除要因として使用できる割り込みは、クロックジェネレータを経由して CPU に接続されるため、クロックジェネレータの設定が必要です。ただし、外部割り込みについてはスタンバイ解除要因として使用しない場合はクロックジェネレータの設定なしで使用することもできます。この場合、次項の注意事項に留意して使用してください。

#### 6.5.1.4 外部割込み端子を使用する際の注意

外部割込みを使用する際には、予期しない割り込みが発生しないよう以下の点に留意してください。

外部割込み端子からの入力信号は、入力ディセーブル (PxIE < PxmIE >= "0") の場合 "High" となります。また、外部割込みをスタンバイ解除要因として使用しない場合 (「図 6-1 割り込みの経路」の の経路)、外部割込み端子からの入力信号がそのまま CPU に伝わります。CPU は "High" 入力を割り込みとして認識しますので、入力ディセーブルのまま CPU で該当する割り込みを有効にすると割り込みが発生します。

外部割込みをスタンバイ解除要因とせずに使用する際には、割り込み端子入力を "Low" レベルとして入力イネーブルにし、その後 CPU で割り込み許可設定を行ってください。

Page55 2023/07/31

## 6.5.1.5 要因一覧

割り込みの要因一覧を表 6-3 に示します。

表 6-3 割り込み要因一覧

| 番号 |           | 要因                           | アクティブレベル<br>(スタンバイ解除)          | CG 割り込みモード<br>コントロールレジスタ |

|----|-----------|------------------------------|--------------------------------|--------------------------|

| 0  | INT0      | 割り込み端子                       |                                |                          |

| 1  | INT1      | 割り込み端子                       | [H] / [L] レベル<br>[↑] / [↓] エッジ | CGIMCGA                  |

| 2  | INT2      | 割り込み端子                       | 選択可                            | OGINIOGA                 |

| 3  | INT3      | 割り込み端子                       |                                |                          |

| 4  | INT4      | 割り込み端子                       | [H]/ [L] レベル                   | CGIMCGB                  |

| 5  | INT5      | 割り込み端子                       | [↑] / [↓] エッジ選択可               |                          |

| 6  | INTRX0    | シリアル受信 (channel0)            |                                |                          |

| 7  | INTTX0    | シリアル送信 (channel0)            |                                |                          |

| 8  | INTRX1    | シリアル受信 (channel1)            |                                |                          |

| 9  | INTTX1    | シリアル送信 (channel1)            |                                |                          |

| 10 | INTVCNA   | ベクトルエンジン割り込み A               |                                |                          |

| 11 | INTVCNB   | ベクトルエンジン割り込み B               |                                |                          |

| 12 | INTEMG0   | PMD0 EMG 割り込み                |                                |                          |

| 13 | INTEMG1   | PMD1 EMG 割り込み                |                                |                          |

| 14 | INTOVV0   | PMD0 OVV 割り込み                |                                |                          |

| 15 | INTOVV1   | PMD1 OVV 割り込み                |                                |                          |

| 16 | INTADAPDA | ADCA PMD0 トリガ同期変換終了          |                                |                          |

| 17 | INTADBPDA | ADCB PMD0 トリガ同期変換終了          |                                |                          |

| 18 | INTADAPDB | ADCA PMD1 トリガ同期変換終了          |                                |                          |

| 19 | INTADBPDB | ADCB PMD1 トリガ同期変換終了          |                                |                          |

| 20 | INTTB00   | 16bitTMRB0 コンペア一致 0/ オーバーフロー |                                |                          |

| 21 | INTTB01   | 16bitTMRB0 コンペアー致 1          |                                |                          |

| 22 | INTTB10   | 16bitTMRB1 コンペア一致 0/ オーバーフロー |                                |                          |

| 23 | INTTB11   | 16bitTMRB1 コンペア一致 1          |                                |                          |

| 24 | INTTB40   | 16bitTMRB4 コンペア一致 0/ オーバーフロー |                                |                          |

| 25 | INTTB41   | 16bitTMRB4 コンペアー致 1          |                                |                          |

| 26 | INTTB50   | 16bitTMRB5 コンペア一致 0/ オーバーフロー |                                |                          |

| 27 | INTTB51   | 16bitTMRB5 コンペア一致 1          |                                |                          |

| 28 | INTPMD0   | PMD0 PWM 割り込み                |                                |                          |

| 29 | INTPMD1   | PMD1 PWM 割り込み                |                                |                          |

| 30 | INTCAP00  | 16-bit TMRB0 インプットキャプチャ 0    |                                |                          |

| 31 | INTCAP01  | 16-bit TMRB0 インプットキャプチャ 1    |                                |                          |

| 32 | INTCAP10  | 16-bit TMRB1 インプットキャプチャ 0    |                                |                          |

| 33 | INTCAP11  | 16-bit TMRB1 インプットキャプチャ 1    |                                |                          |

| 34 | INTCAP40  | 16-bit TMRB4 インプットキャプチャ 0    |                                |                          |

表 6-3 割り込み要因一覧

| 番号 |           | 要因                           | アクティブレベル<br>(スタンバイ解除) | CG 割り込みモード<br>コントロールレジスタ |

|----|-----------|------------------------------|-----------------------|--------------------------|

| 35 | INTCAP41  | 16-bit TMRB4 インプットキャプチャ 1    |                       |                          |

| 36 | INTCAP50  | 16-bit TMRB5 インプットキャプチャ 0    |                       |                          |

| 37 | INTCAP51  | 16-bit TMRB5 インプットキャプチャ 1    |                       |                          |

| 38 | INT6      | 割り込み端子                       | [H]/ [L] レベル          | CGIMCGB                  |

| 39 | INT7      | 割り込み端子                       | [↑] / [↓] エッジ選択可      | CGIIVICGB                |

| 40 | INTRX2    | シリアル受信 (channel2)            |                       |                          |

| 41 | INTTX2    | シリアル送信 (channel2)            |                       |                          |

| 42 | INTADACPA | ADCA 監視割り込み A                |                       |                          |

| 43 | INTADBCPA | ADCB 監視割り込み A                |                       |                          |

| 44 | INTADACPB | ADCA 監視割り込み B                |                       |                          |

| 45 | INTADBCPB | ADCB 監視割り込み B                |                       |                          |

| 46 | INTTB20   | 16bitTMRB2 コンペア一致 0/ オーバーフロー |                       |                          |

| 47 | INTTB21   | 16bitTMRB2 コンペア一致 1          |                       |                          |

| 48 | INTTB30   | 16bitTMRB3 コンペア一致 0/ オーバーフロー |                       |                          |

| 49 | INTTB31   | 16bitTMRB3 コンペア一致 1          |                       |                          |

| 50 | INTCAP20  | 16-bit TMRB2 インプットキャプチャ 0    |                       |                          |

| 51 | INTCAP21  | 16-bit TMRB2 インプットキャプチャ 1    |                       |                          |

| 52 | INTCAP30  | 16-bit TMRB3 インプットキャプチャ 0    |                       |                          |

| 53 | INTCAP31  | 16-bit TMRB3 インプットキャプチャ 1    |                       |                          |

| 54 | INTADASFT | ADCA ソフトスタート変換終了             |                       |                          |

| 55 | INTADBSFT | ADCB ソフトスタート変換終了             |                       |                          |

| 56 | INTADATMR | ADCA タイマ同期変換終了               |                       |                          |

| 57 | INTADBTMR | ADCB タイマ同期変換終了               |                       |                          |

Page 57 2023/07/31

表 6-3 割り込み要因一覧

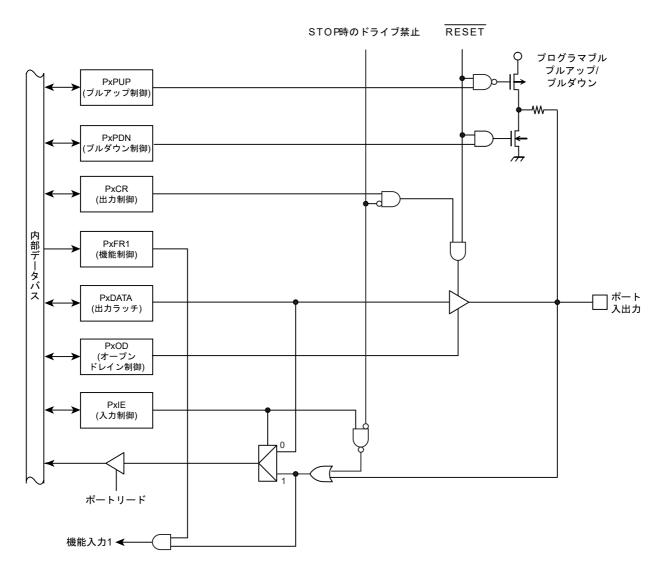

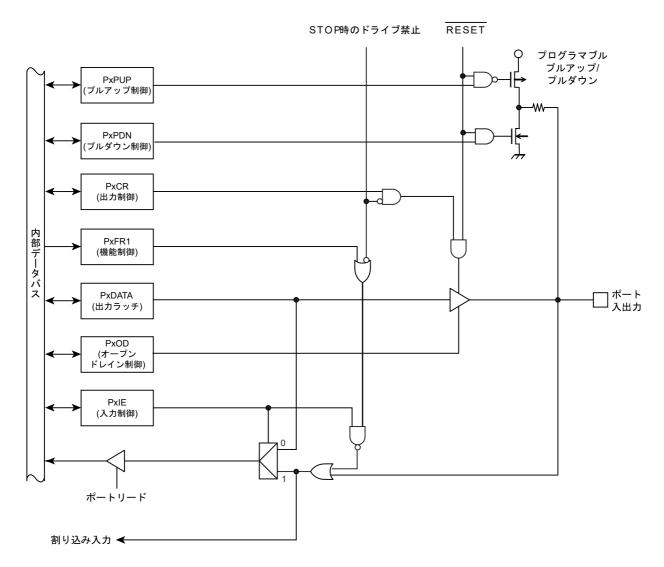

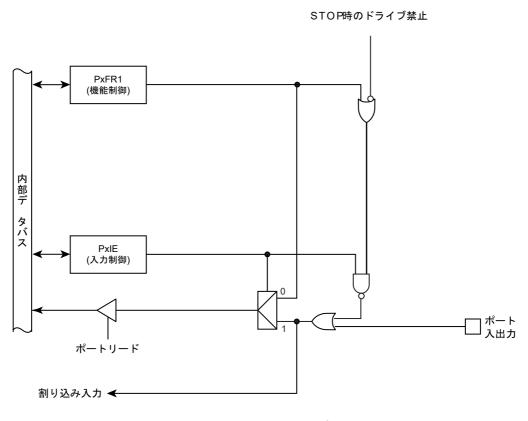

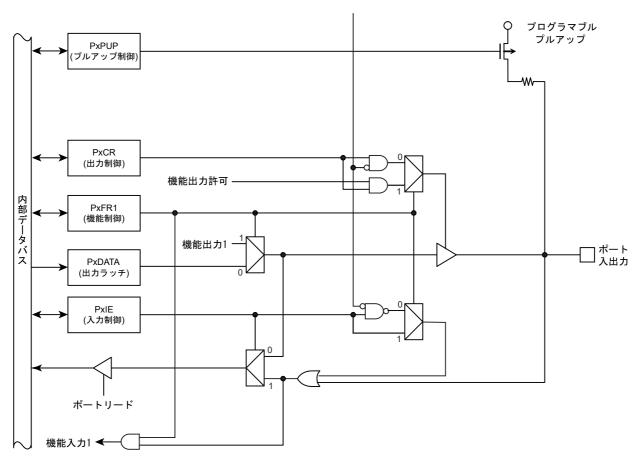

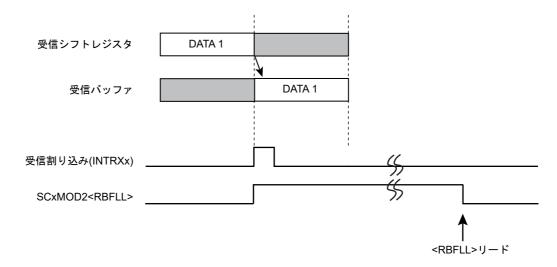

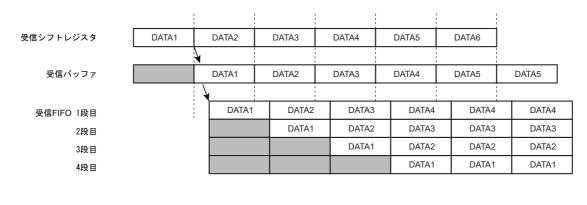

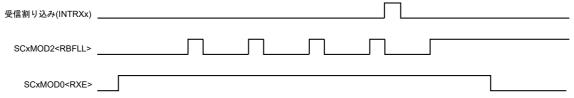

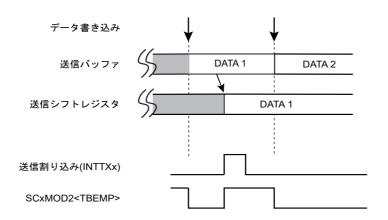

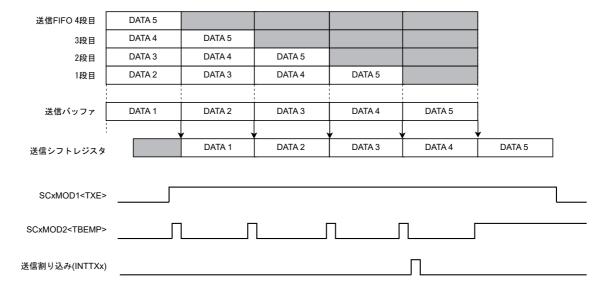

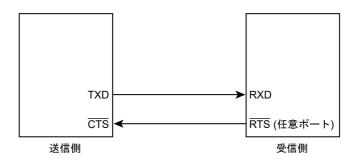

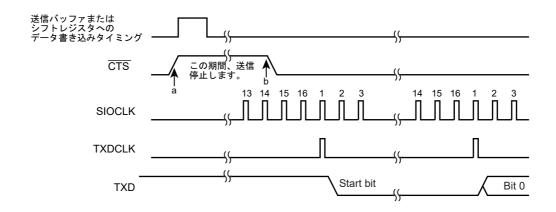

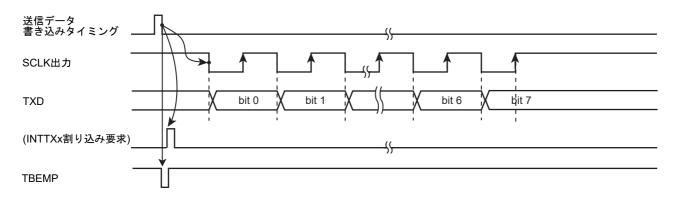

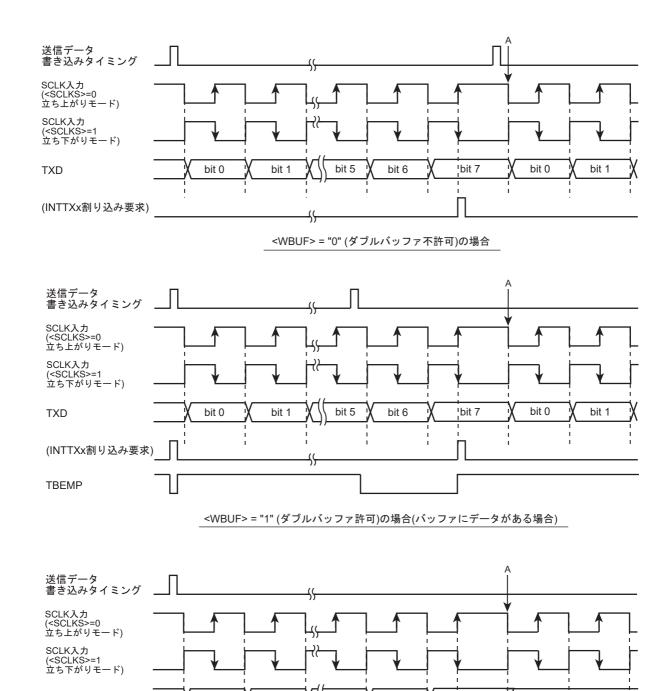

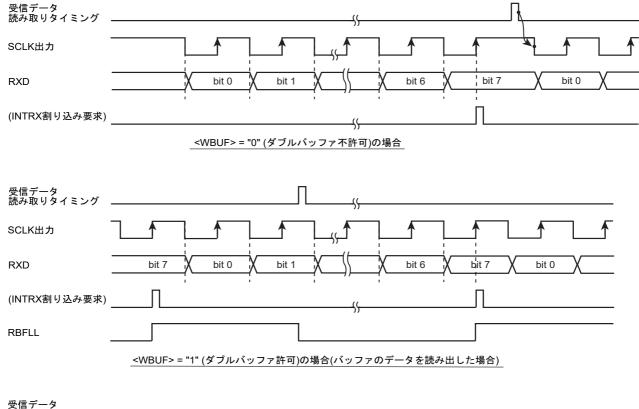

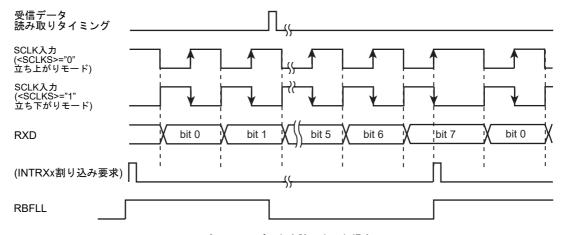

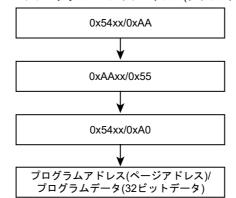

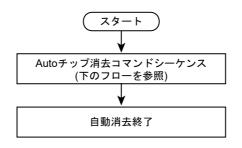

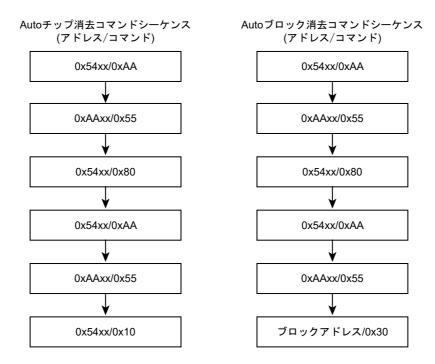

| 番号 |          | 要因                           | アクティブレベル<br>(スタンバイ解除) | CG 割り込みモード<br>コントロールレジスタ |  |  |