# **TOSHIBA**

東芝 オリジナル CMOS 8 ビット マイクロコントローラ

TLCS-870 シリーズ

TMP87CH29UG, TMP87CH29NG TMP87CK29UG, TMP87CK29NG TMP87CM29UG, TMP87CM29NG

# 改訂履歴

| 日付        | 版 | 改訂理由          |

|-----------|---|---------------|

| 2003/3/20 | 1 | First Release |

| 2008/3/6  | 2 | 内容改訂          |

| 2008/9/30 | 3 | 内容改訂          |

# UART ノイズ除去時間設定における注意事項

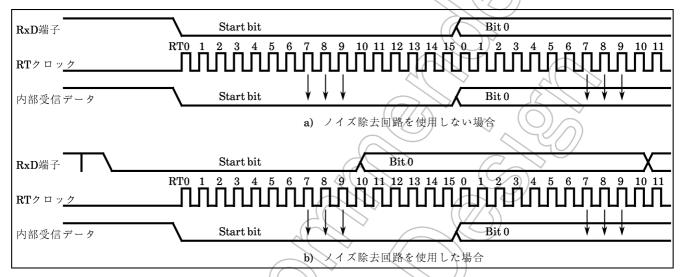

本製品に搭載されている UART を使用する場合、転送クロック選択 (BRG) により、ノイズ除去時間設定(RXDNC設定)には以下の制約があります。"〇"の箇所にて使用し、"一"の箇所は設定しないでください。

なお、転送クロックとしてタイマカウンタ割り込みを使用する場合、転送クロックはタイマカウンタソースクロック [Hz] ÷ TTREG 設定値で計算されます。

|                            |             |                 | <u> </u>                      | $\langle ( / / ) \rangle$     |                                |

|----------------------------|-------------|-----------------|-------------------------------|-------------------------------|--------------------------------|

|                            |             |                 | RXDN                          | IC 設定                         |                                |

| BRG 設定                     | 転送クロック [Hz] | 00<br>(ノイズ除去なし) | 01<br>(31/fc[s] 未満の<br>パルス除去) | 10<br>(63/fc[s] 未満の<br>パルス除去) | 11<br>(127/fc[s] 未満の<br>パルス除去) |

| 000                        | fc/13       | 0               | 000                           | → o                           | $A( \Rightarrow )$             |

| 110                        | fc/8        | 0               |                               | > - 52                        | -                              |

| (タイマカウンタ割り込<br>みでの転送クロックが右 | fc/16       | 0               | ( Ø/ )                        | <i>~</i> (€                   | ))~-                           |

| 記となる場合)                    | fc/32       | 0               | 0                             | 0                             | (())-                          |

| 上記以外                       |             | 0               | 4(0)                          | 0                             | , 0                            |

|                            |             |                 |                               |                               |                                |

# お知らせ

本マイコン製品の「はんだ無鉛化」に伴うデータシート変更は、変更内容のみを、旧データシートの先頭 に付加した形での御提供をさせていただいております。御理解を頂けます様、よろしくお願い申し上げます。

下記に修正項目と内容の説明を明記いたします。製品に応じて対象となる修正項目が異なりますので、御注意ください。

修正項目 1. 製品名称

例)TMPxxxxxxF TMPxxxxxxFG 等本文中には、旧名称のまま記述されておりますが、表紙及び付加ページ(ローマ数字の本文前のページを示す)内記述の名称が正式な名称となります。

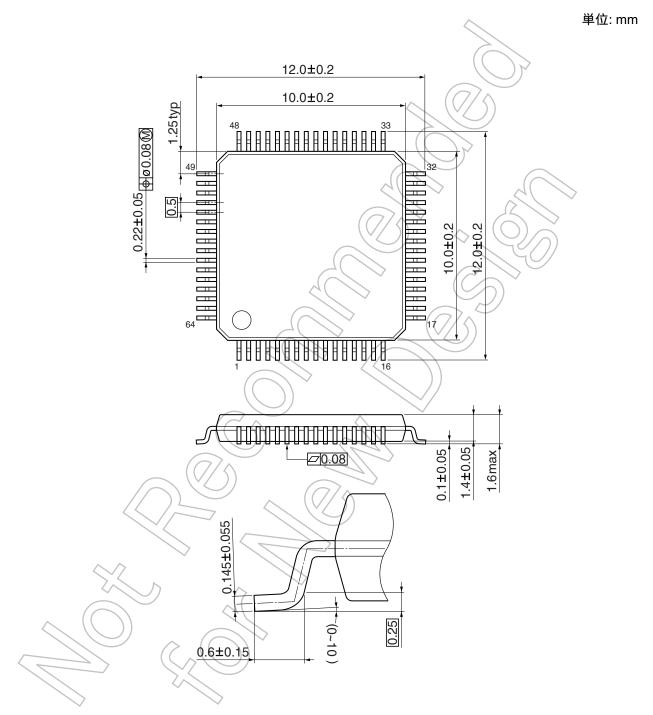

修正項目 2. パッケージ名称及び寸法

例) LQFP100-P-1414-0.50C LQFP100-P-1414-0.50F 本文中には、旧名称・旧寸法図のまま記述されておりますが、 付加ページの名称と寸法図が正式な名称及び寸法図となります。

修正項目 3. はんだ濡れ性の注意事項の追記 はんだ無鉛化に伴い、はんだ濡れ性に注意事項が追記されています。

修正項目 4. 「当社半導体製品取り扱い上のお願い」 旧製品には旧製品当時の文言が記述されている場合がありますが、 付加ページ内で最新の内容に更新しております。

修正項目 5. データシートの発行日付 付加ページ内のデータシート右下に記述されている発行日付が 本データシートの発行日付となります。

T

2008-03-06

### 修正対象項目 1. 製品名称

### 修正対象項目 2. パッケージ名称及び寸法

| 本文中製品名称<br>(旧名称) | 本文中パーケージ名称<br>(旧名称) |             |                     | OTP 製品名     |

|------------------|---------------------|-------------|---------------------|-------------|

| TMP87CH29U       | P-LQFP64-1010-0.50D | TMP87CH29UG | LQFP64-P-1010-0.50D | TMP87PM29UG |

| TMP87CH29N       | P-SDIP64-750-1.78   | TMP87CH29NG | SDIP64-P-750-1.78   | TMP87PM29NG |

| TMP87CK29U       | P-LQFP64-1010-0.50D | TMP87CK29UG | LQFP64-P-1010-0.50D | TMP87PM29UG |

| TMP87CK29N       | P-SDIP64-750-1.78   | TMP87CK29NG | SDIP64-P-750-1.78   | TMP87PM29NG |

| TMP87CM29U       | P-LQFP64-1010-0.50D | TMP87CM29UG | LQFP64-P-1010-0.50D | TMP87PM29UG |

| TMP87CM29N       | P-SDIP64-750-1.78   | TMP87CM29NG | SDIP64-P-750-1.78   | TMP87PM29NG |

<sup>\*:</sup> 正式パッケージでの実際の寸法図は別紙の「パッケージ外形寸法図」を参照してください。

# 修正項目 3. はんだ濡れ性の注意事項の追記

本製品では、 はんだの濡れ性について以下の注意事項が追加されます。

# 鉛フリー品 (G 付製品) へのはんだ濡れ性についての注意事項

| 試験項目   | 試験条件                                            |

|--------|-------------------------------------------------|

| はんだ付け性 | 230℃ 5秒間1回Rタイプフラックス使用(鉛はんだ使用時) フォーミングまでの半田付     |

|        | 245°C 5秒間1回Rタイプフラックス使用(鉛フリーはんだ使用時) 着率 95%を良品とする |

# 修正項目 4. 「当社半導体製品取り扱い上のお願い」

本製品では以下に示す、 最新の「当社半導体製品取り扱い上のお願い」が適用されます。

#### 当社半導体製品取り扱い上のお願い

- 当社は品質,信頼性の向上に努めておりますが,一般に半導体製品は誤作動したり故障することがあります。当社半導体製品をご使用いただく場合は,半導体製品の誤作動や故障により,生命・身体・財産が侵害されることのないように,購入者側の責任において,機器の安全設計を行うことをお願いします。 なお,設計に際しては,最新の製品仕様をご確認の上,製品保証範囲内でご使用いただくと共に,考慮されるべき注意事項や条件について「東芝半導体製品の取り扱い上のご注意とお願い」、「半導体信頼性ハンドブック」な どでご確認ください。

- 本資料に掲載されている製品は,一般的電子機器(コンピュータ,パーソナル機器,事務機器,計測機器,産業 用ロボット,家電機器など)に使用されることを意図しています。特別に高い品質・信頼性が要求され,その故 障や誤作動が直接人命を脅かしたり人体に危害を及ぼす恐れのある機器(原子力制御機器,航空宇宙機器,輸送 機器,交通信号機器,燃焼制御,医療機器,各種安全装置など)にこれらの製品を使用すること(以下"特定用途"という)は意図もされていませんし,また保証もされていません。本資料に掲載されている製品を当該特定用 途に使用することは、お客様の責任でなされることとなります。

- 本資料に掲載されている製品を,国内外の法令,規則及び命令により製造,使用,販売を禁止されている応用製 品に使用することはできません。

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 本資料に掲載されている製品の、RoHS 適合性など、詳細につきましては製品個別に必ず弊社営業窓口までお問合 せください。本資料に掲載されている製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令な どの法令を十分調査の上、かかる法令に適合するようご使用ください。お客様が適用される法令を遵守しないこ とにより生じた損害に関して、当社は一切の責任を負いかねます。 本資料の掲載内容は,技術の進歩などにより予告なしに変更されることがあります。

П

#### 修正項目 5. データシートの発行日付

本製品の発行日は、 付加ページ右下にも記入の「2008-03-06」です。

2008-03-06

(別紙)

# パッケージ外形寸法図

LQFP64-P-1010-0.50D

III 2008-03-06

# SDIP64-P-750-1.78

単位: mm

IV 2008-03-06

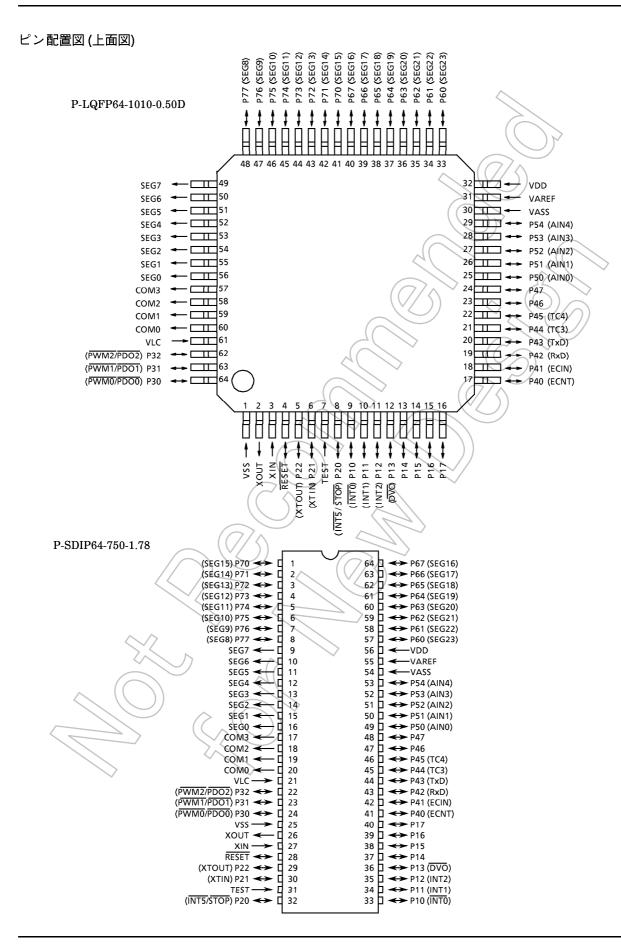

#### CMOS 8ビット マイクロコントローラ

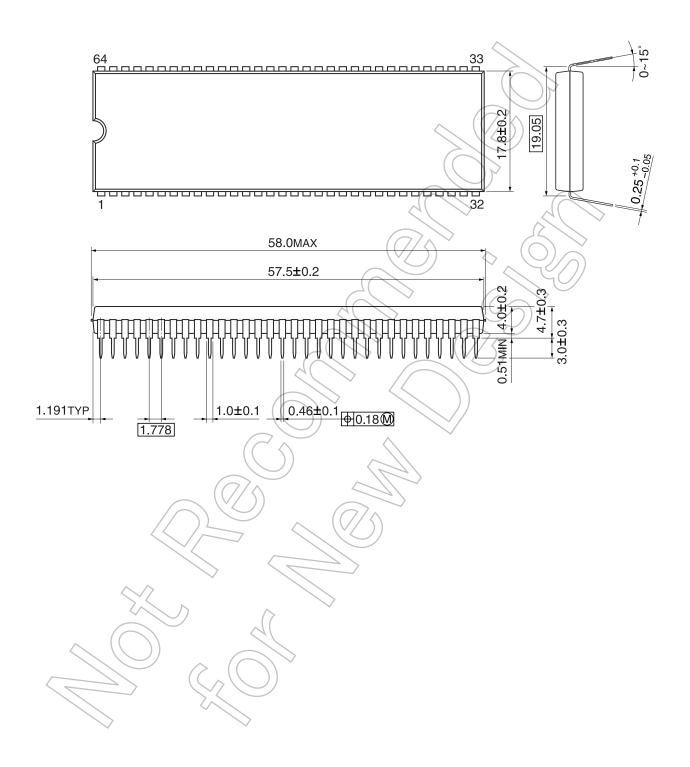

# TMP87CH29U/N, TMP87CK29U/N, TMP87CM29U/N

大容量ROM/RAM, LCDドライバ, 多機能タイマカウンタ, 非同期型シリアルインタフェース,8ビットAD コンバータおよび2系統の発振回路などを内蔵した高速、高機能8ビットシングルチップマイクロコンピュー 夕です。

| 製品形名       | ROM             | RAM   | パッケージ               | <b>OTP</b> 内蔵品 |  |  |  |

|------------|-----------------|-------|---------------------|----------------|--|--|--|

| TMP87CH29U | 1017 10 2 3     |       | P-LQFP64-1010-0.50D | TMP87PM29U     |  |  |  |

| TMP87CH29N | 16Kバイト          |       | P-SDIP64-750-1.78   | TMP87PM29N     |  |  |  |

| TMP87CK29U | 24Kバイト          | 1Κバイト | P-LQFP64-1010-0.50D | TMP87PM29U     |  |  |  |

| TMP87CK29N | 24 <b>K</b> /\7 | IKMAR | P-SDIP64-750-1.78   | TMP87PM29N     |  |  |  |

| TMP87CM29U | 32Kバイト          |       | P-LQFP64-1010-0.50D | TMP87PM29U     |  |  |  |

| TMP87CM29N | 32IX2 (2) 1     |       | P-SDIP64-750-1.78   | TMP87PM29N     |  |  |  |

#### 特長

◆ 8ビットシングルチップマイクロコンピュータ **TLCS-870**シリーズ

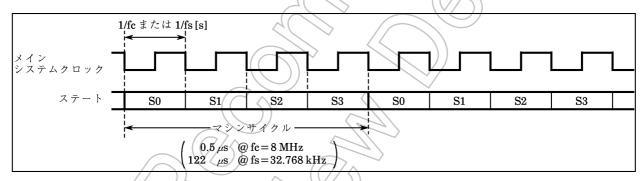

◆ 最小命令実行時間: 0.5 μs (8 MHz動作時), 122 μs (32.768 kHz動作時)

◆ 基本機械命令: 129種類 412命令

実行時間 ● 乗除算(8 bit×8 bit, 16 bit÷8 bit):

3.5 µs (8 MHz動作時)

ビット操作

(Set/Clear/Complement/Load/Store/Test/Exclusive OR)

- 16ビット演算/転送

- 1バイト長のジャンプ/コール (Short relative jump/Vector call)

- ◆ 割り込み13要因(外部 4, 内部:9)

- 全要因独立ラッチ付き、多重割り込み制御

- エッジ選択,ノイズ除去機能付き外部割り込み端子あり

- レジスタバンク切り替えによる高速タスクスイッチング

- ▶ 入出力ポート (43端子) (内16本はSEG端子と兼用)

- 大電流出力:3端子 (typ. 20 mA)

- ◆ 18ビットタイマカウンタ:1チャネル

- 周波数測定、パルス幅測定、イベントカウンタ、 タイマモード

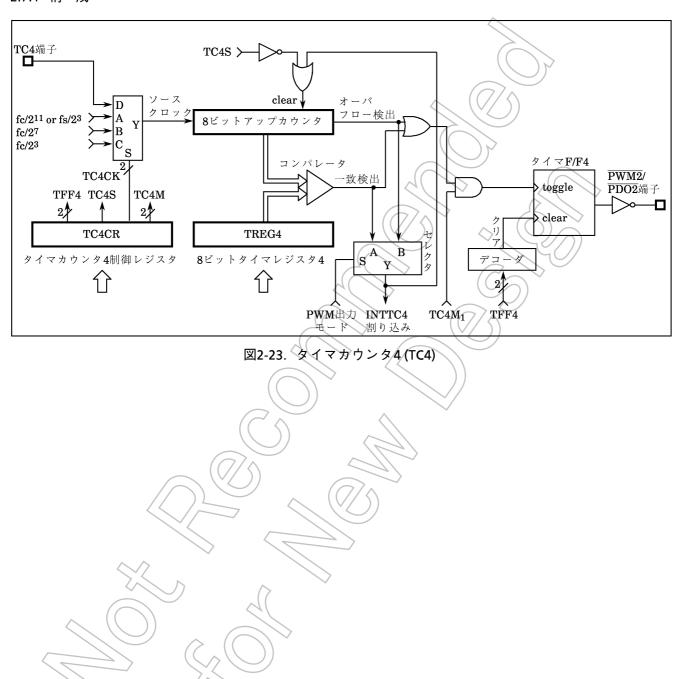

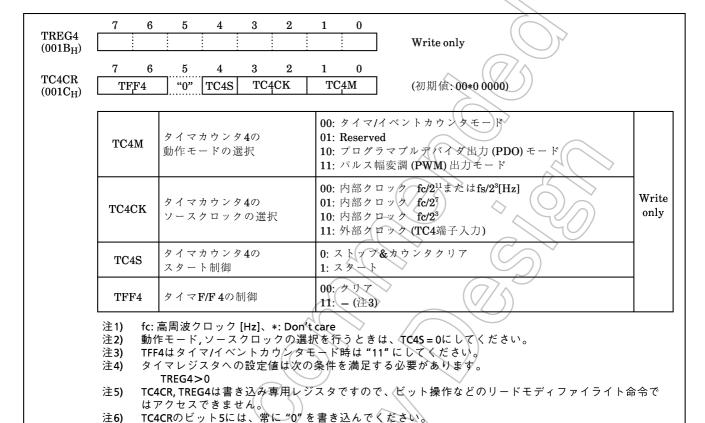

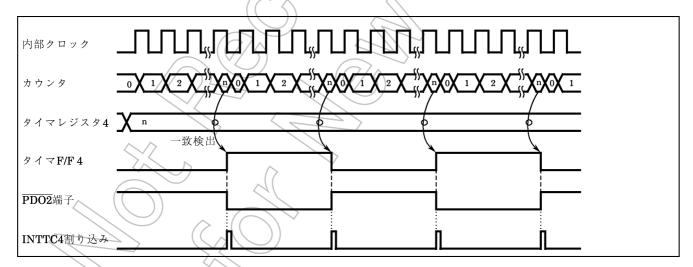

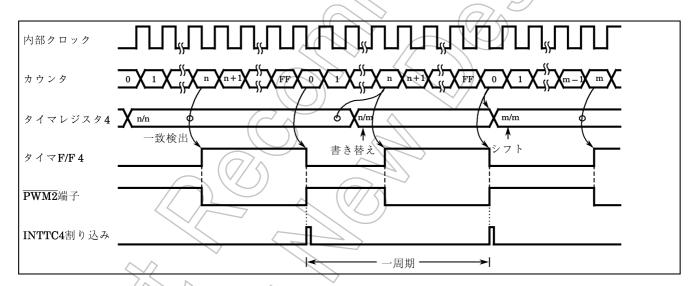

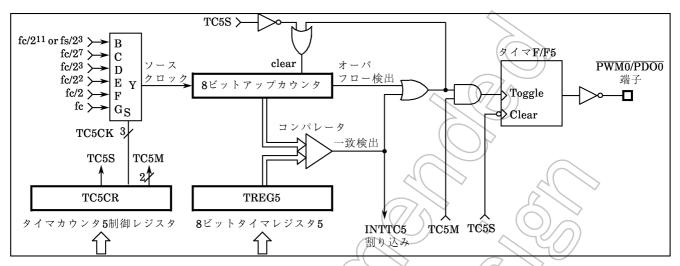

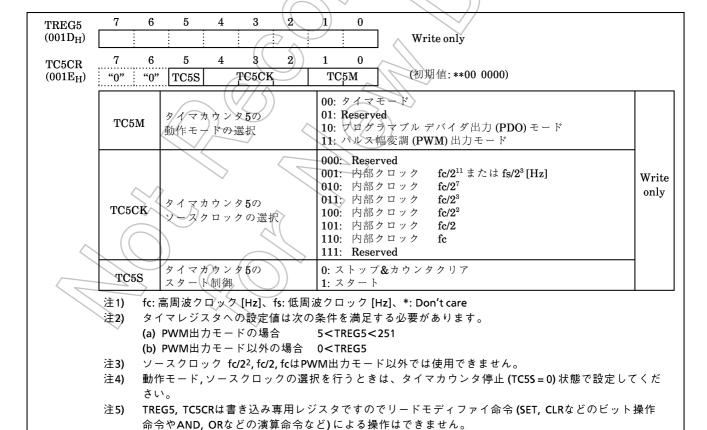

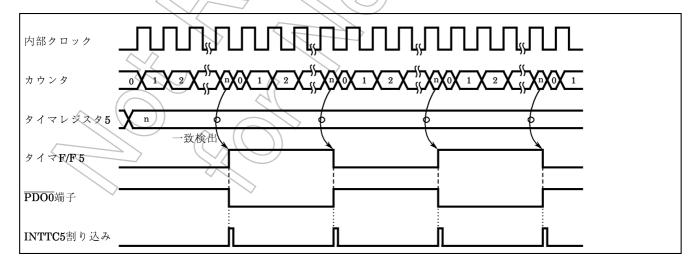

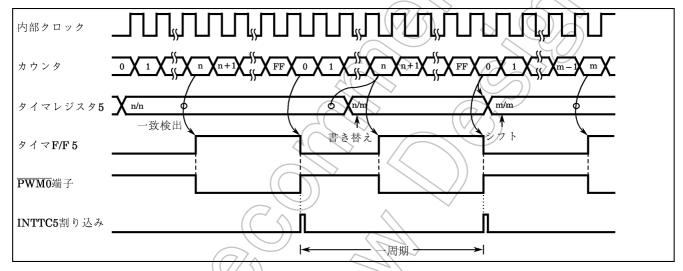

- ▶8ビットタイマカウンタ:4チャネル

- タイマ、イベントカウンタ、キャプチャ (パルス幅/デューティ測定), PWM (パルス幅変調) 出力, PDO (Programmable Divider Output)  $\exists - \vdash$

ジ外観図 P-LQFP64-1010-0.50D TMP87CH29U TMP87CK29U TMP87CM29U TMP87PM29U P-SDIP64-750-1.78 TMP87CH29N TMP87CK29N TMP87CM29N TMP87PM29N

- マイコン製品の信頼性予測については、「品質保証と信頼性/取り扱い上のご注意とお願い」の1.3項に記載されておりますのでかならずお読みください。

- 本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されているものです。

- 本資料に掲載されている技術情報は、製品の代表的動作·応用を説明するためのもので、その使用に際して当社および第三者の知的財産権その他の権利に 対する保証または実施権の許諾を行うものではありません

- 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

87CH29-1 2003-03-20

- **◆8**ビット**PWM/PDO**出力:**1**チャネル

- ◆ タイムベース タイマ (割り込み周波数: 1~16384Hz)

- ◆ デバイダ出力機能 (周波数: 1~8 kHz)

- ◆ ウォッチドッグ タイマ

- 割り込み/リセット出力の選択(プログラマブル)

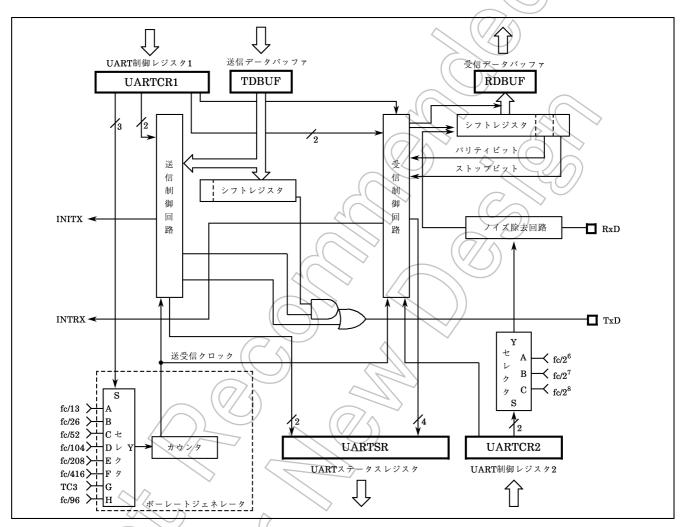

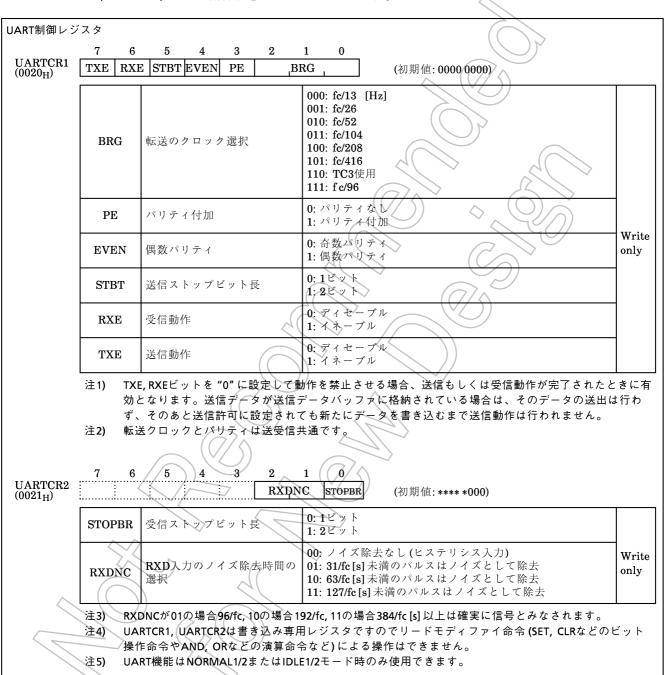

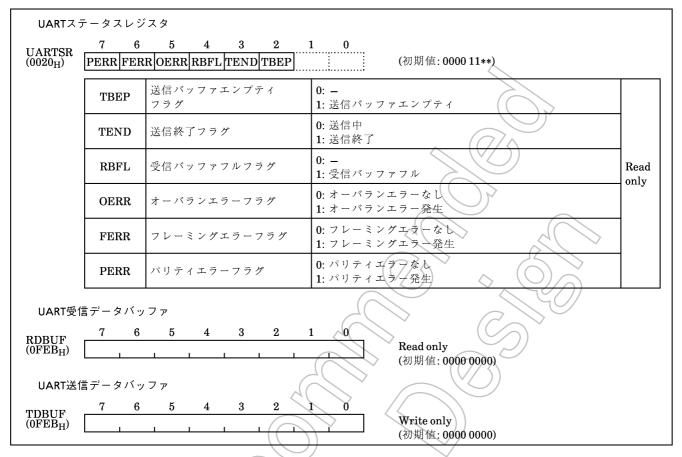

- ◆ 非同期型シリアル ンタフェース:1チャネル

- 8ビットの送受信データバッファ付き

- 転送クロック、パリティビット有無の選択

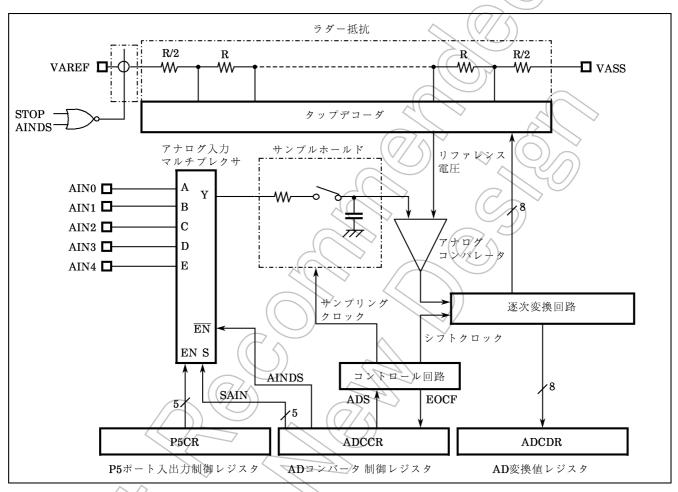

- ◆8ビット遂次比較方式ADコンバータ(サンプルホールド付き)

- アナログ入力:5チャネル

- 変換時間: 23/92 μs (8 MHz動作時)

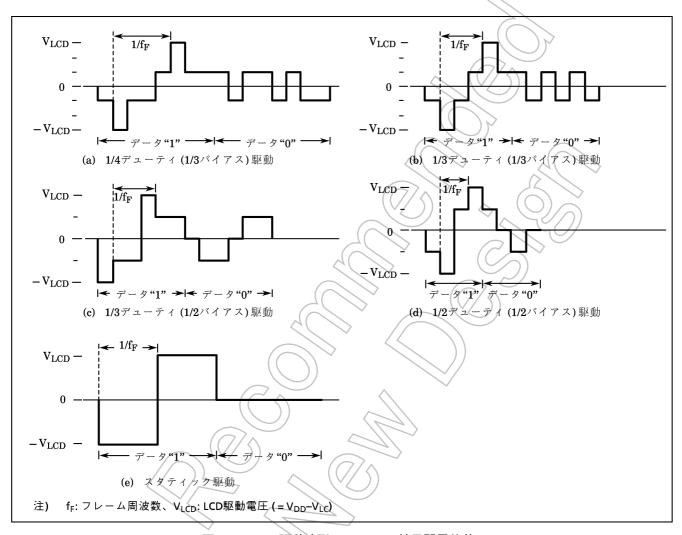

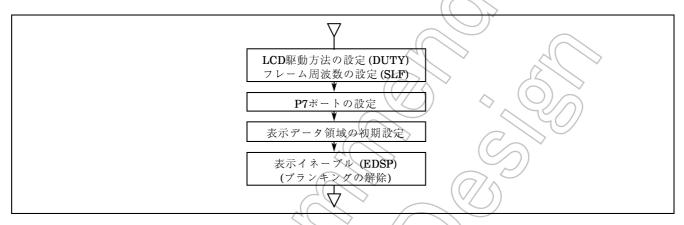

- ◆ LCDドライバ/コントローラ

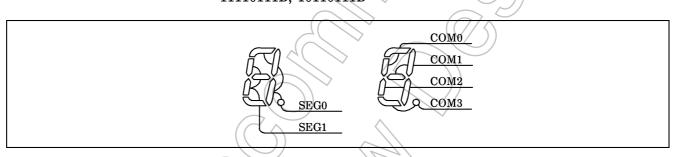

- LCD直接駆動可能 (24~8 segment×4 common)

- 1/4, 1/3, 1/2 デューティ,スタティック駆動の選択

- 表示専用メモリ付き(12バイト)

- ◆ クロック発振回路: 2回路

- シングル/デュアルクロックモードの選択(オプション)

- ◆ 低消費電力動作(5モード)

- **STOP**モード: 発振停止(バッテリー/コンデンサバックアップ)。ポート出力の保持/ハイインピーダンスの選択。

- SLOWモード: 低周波クロック (32.768 kHz) による低消費電力動作。

- IDLE1モード: CPU停止。周辺ハードウエアのみ動作(高周波クロック)継続し、割り込みで解除 (CPU再起動)。

- **IDLE2**モード: **CPU**停止。周辺バードウエアのみ動作(高周波/低周波クロック)継続し、割り込みで解除。

- SLEEPモード: CPU停止。周辺ハードウエアのみ動作(低周波クロック)継続し、割り込みで解除。

- ◆ 動作電圧: 2.7~5.5 V @ 4.19 MHz/32.768 kHz, 4.5~5.5 V @ 8 MHz/32.768 kHz

- ◆ エミュレーションポッド: BM87CM29U0A

87CH29-3 2003-03-20

ブロック図

87CH29-4 2003-03-20

# 端子機能

| 端 子 名                                     | 入 出 力         | 機                                                                            | 能                                                            |

|-------------------------------------------|---------------|------------------------------------------------------------------------------|--------------------------------------------------------------|

| P17~ P14                                  | 入出力           | 8ビットのプログラマブル入出力ポー                                                            |                                                              |

| P13 ( <del>DVO</del> )                    | 入出力(出力)       | 】ト(トライステート)。<br>┃1ビット単位で入力/出力の指定がで                                           | デバイダ出力                                                       |

| P12 (INT2)                                |               | きます。外部割り込み入力として用いる場合は入力モードにします。デ                                             | 外部割り込み2入力                                                    |

| P11 (INT1)                                | 入出力(入力)       | バイダ出力として用いる場合は、出力ラッチを"1"にセットして、出力                                            | 外部割り込み1入力                                                    |

| P10 ( <del>INT0</del> )                   |               | モードにします。                                                                     | 外部割り込み0入力                                                    |

| P22 (XTOUT)                               | 入出力(出力)       | 3ビット入出力ポート。<br>入力ポート,機能端子として使用する                                             | 低周波発振子接続端子 (32.768kHz)。<br>外部クロック入力の場合、XTINへ入                |

| P21 (XTIN)                                |               | 人刀ホート,機能蛹丁として使用する <br> 場合は、出力ラッチを"1" にセットし                                   | 力し、 <b>XTOUT</b> は開放します。                                     |

| P20 (INT5/STOP)                           | 入出力(入力)       | st.                                                                          | 外部割り込み <b>5</b> 入力 <b>/STOP</b> モード解除<br>入力                  |

| P32 ( <del>PWM2</del> / <del>PDO2</del> ) |               | 3ビット入出力ポート。                                                                  | \$ \Q\n                                                      |

| P31 ( <del>PWM1</del> / <del>PDO1</del> ) | 入出力(出力)       | 入力ポート,タイマカウンタ出力として使用する場合は、出力ラッチを"1"                                          | 8ビットPWM出力/8ビットプログラマ<br>ブル デバイダ出力 (大電流出力)                     |

| P30 ( <del>PWM0</del> / <del>PDO0</del> ) |               | にセットします。                                                                     |                                                              |

| P47                                       | 入出力           |                                                                              | 776                                                          |

| P46                                       | ДШЛ           |                                                                              |                                                              |

| P45 (TC4)                                 | 7 11 1 77 1 3 |                                                                              | タイマカウンタ4入力                                                   |

| P44 (TC3)                                 | 入出力(入力)       | 8ビット入出力ポート。<br> 入力ポート,タイマカウンタ入力/出力,                                          | タイマカウンタ <b>3</b> 入力                                          |

| P43 (TxD)                                 | 入出力 (出力)      | UART入出力として使用する場合は、<br>出力ラッチを"1"にセットします。                                      | <b>UART</b> 送信出力                                             |

| P42 (RxD)                                 |               |                                                                              | <b>UART</b> 受信入力                                             |

| P41 (ECIN)                                | 入出力(入力)       |                                                                              | b 2 - 4 - 4 - 3 / b 4 7 +                                    |

| P40 (ECNT)                                |               |                                                                              | タイマカウンタ1入力                                                   |

| P54 (AIN4) ~<br>P50 (AIN0)                | 入出为(入力)       | 5ビットのプロダラマブル入出力ポート(トライステート)。1ビット単位で入力/出力の指定ができます。アナログ入力として使用する場合は、入力モードにします。 | ADコンバータアナログ入力                                                |

| P67 (SEG16) ~<br>P60 (SEG23)              | 大出力(出力)       | 8ビット入出力ポート。<br>入力ポートとして使用する場合は、出<br>力ラッチを "1" にセットします。                       | LCDセグメント出力。セグメント出力<br>として使用する場合は、P6ポート制<br>御レジスタを"1"にセットします。 |

| P77 (SEG8) ~<br>P70 (SEG15)               | 入出力(出力)       | 8ビット入出力ポート。<br>入力ポートとして使用する場合は、出<br>力ラッチを"1"にセットします。                         | LCDセグメント出力。セグメント出力<br>として使用する場合は、P7ポート制<br>御レジスタを"1"にセットします。 |

| SEG7~SEG0                                 | 出力            | LCDセグメント出力                                                                   |                                                              |

| COM3~COM0                                 |               | LCDコモン出力<br>高周波発振子接続端子。                                                      |                                                              |

| XIN, XOUT                                 | 入力,出力         | 「高尚夜発振子接続端子。<br>  外部クロック入力の場合 XINへ入力し、<br>  リセット信号入力, ウォッチドッグタイ              | XOUTは開放します。                                                  |

| RESET                                     | 入出力           | リセット信号人刀, ワォッチドックダイ<br>力/システムクロックリセット出力                                      | ヾ山 <i>川1</i> , トレストフッノリセット出                                  |

| TEST                                      | 入力            | 出荷試験用端子。低レベルに固定します                                                           | •                                                            |

| VDD, VSS                                  |               | +5 V, 0 V (GND)                                                              |                                                              |

| VAREF, VASS                               | 電源            | AD変換用アナログ基準電圧。基準GNI                                                          | )                                                            |

| VLC                                       |               | LCD駆動用電源                                                                     |                                                              |

#### 動作説明

#### 1. CPUコア機能

CPUコアは、CPU,システムクロック制御回路,割り込み制御回路およびウォッチドッグタイマから構成されています。

本章では、CPUコア、プログラムメモリ、データメモリおよびリセット回路について説明します。

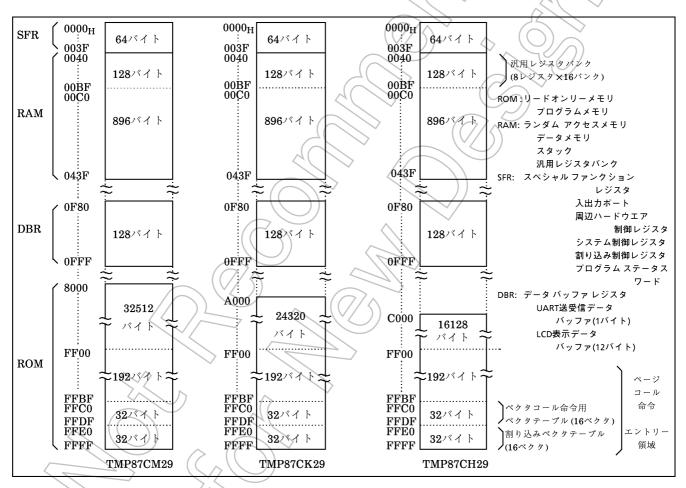

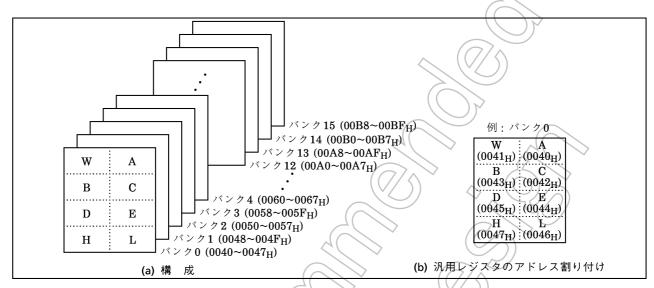

#### 1.1 メモリアドレスマップ

TLCS-870シリーズのメモリは、ROM, RAM, SFR (スペシャルファンクションレジスタ), DBR (データバッファレジスタ)の4つのブロックで構成され、それらは1つの64 Kバイトアドレス空間上にマッピングされています。図1-1にTMP87CH29/K29/M29のメモリアドレスマップを示します。また、汎用レジスタは16バンクあり、RAMアドレス空間上にマッピングされています。

図1-1. メモリアドレスマップ

87CH29-6 2003-03-20

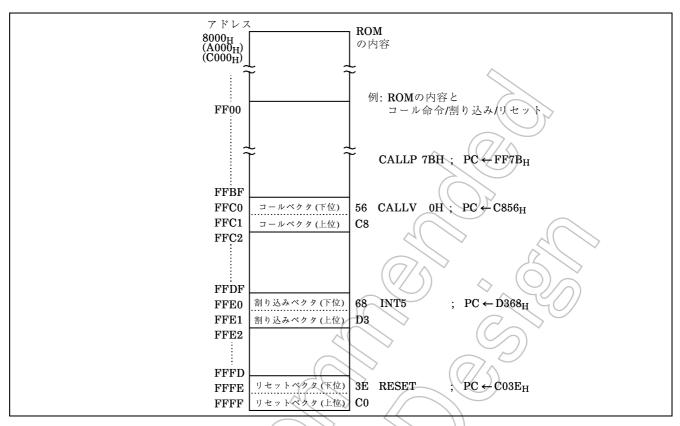

1.2 プログラムメモリ(ROM)

TMP87CH29は16 K バイト (アドレス  $C000 \sim FFFF_H$  番地) TMP87CK29は24 K バイト (アドレス  $A000 \sim FFFF_H$  番地), TMP87CM29は32 K バイト (アドレス  $8000 \sim FFFF_H$  番地) のプログラムメモリ(マスク ROM) を内蔵しています。図1-2にプログラムメモリマップを示します。

プログラムメモリのFF00~FFFFH番地は、特定の用途にも使用されます。

(1) 割り込みベクタテーブル (FFEO~FFFFH番地)

リセットおよび割り込みのベクタ(2バイト/ベクタ)を格納するテーブルで、16ベクタあります。ベクタには、リセット解除からのスタートアドレス,割り込みサービスルーチンのエントリーアドレスを格納します。

(2) ベクタコール命令用ベクタテーブル (FFCO~FFDFH番地)

ベクタコール命令[CALLV n]用のベクタ(サブルーチンエントリーアドレス, 2バイト/ベクタ)を格納するテーブルで、16ベクタあります。ベクタコール命令は1バイト長の命令で、使用頻度の高い(3ヶ所以上から呼び出される)サブルーチンコールに使うことによりメモリ効率を上げることができます。

(3) ページコール命令用エントリーエリア (FF00~FFFH番地)

ページコール命令 [CALLP a] 用のサブルーチンエントリーアドレスエリアです。 $FFC0 \sim FFFF_H$ 番地はベクタテーブルにもなっていますので、通常 $FF00 \sim FFBF_H$ 番地の範囲を使用します。ページコール命令は、2バイト長の命令です。

プログラムメモリには、プログラムおよび固定データが格納されます。次に実行すべき命令は、プログラムカウンタの内容が示すアドレスから読み出されます。ジャンプ命令は相対ジャンプまたは絶対ジャンプ命令で、ジャンプ命令に関してプログラムメモリにはページ,バンクといった境界概念はありません。

例: ジャンプ命令とプログラムカウンタの関係

① 5ビット相対ジャンプ命令[JRS cc, \$+2+d]

E8C4H: JRS T, \$+2+08H の場合

JF=1のとき、プログラムカウンタの内容に $08_H$ を加算した $E8CE_H$ にジャンプします(プログラムカウンタの内容は実行命令の置かれたアドレス +2になっています。従って、この場合プログラムカウンタの値は $E8C4_H+2=E8C6_H$ となります)。

② 8ビット相対ジャンプ命令[JR cc, \$+2+d]

E8C4H: JR Z, \$+2+80H の場合

$\mathbf{ZF} = \mathbf{1}$ のとき、プログラムカウンタの内容に $\mathbf{FF80}_{H}$ ( $-\mathbf{128}$ )を加算した $\mathbf{E846}_{H}$ にジャンプします。

③ **16**ビット絶対ジャンプ命令 [JP a]

E8C4H: JP 0C235H の場合

無条件に $C235_H$ 番地にジャンプします。絶対ジャンプ命令は64Kバイトの全空間内の任意のアドレスにジャンプできます。

87CH29-7 2003-03-20

図1-2. プログラムメモリ マップ

TLCS-870シリーズは、プログラムメモリに格納された固定データの読み出しに、データメモリをアクセスする命令と同じ命令を使用します。さらに、レジスタオフセット相対アドレッシングモード (PC+A) の命令も使用でき、コード変換、テーブルルックアップ、多方向分岐処理などが容易にプログラミングできます。

例1: HLレジスタペアで指定されるアドレスのROM内容をアキュムレータに読み出す処理 (HL≧8000H)

LD A, (HL) ; A $\leftarrow$ ROM (HL)

例2:  $BCD \rightarrow 7$ セグメントコード(アノードコモン)変換出力処理( $A=05_H$ のとき下記プログラムの実行で、P1ポートに $92_H$ が出力されます)。

ADD A, TABLE - \$ - 4;  $P1 \leftarrow ROM (TABLE + A)$

LD (P1), (PC+A)

JRS T. SNEXT

TABLE: DB 0C0H, 0F9H, 0A4H, 0B0H, 99H, 92H, 82H, 0D8H, 80H, 98H

SNEXT:

注) \$はADD命令の先頭アドレス。DBはバイトデータの定義命令。

例3: アキュムレータの内容  $(0 \le A \le 3)$  による多方向分岐処理

SHLC A ; if  $A = 00_H$  then  $PC \leftarrow C234_H$ JP (PC+A) if  $A = 01_H$  then  $PC \leftarrow C378_H$

$(PC+A) if A=01_H then PC←C378_H$  if A=02<sub>H</sub> then PC←DA37<sub>H</sub>

if  $A = 03_H$  then  $PC \leftarrow E1B0_H$

DW 0C234H, 0C378H, 0DA37H, 0E1B0H

|注) DWはワードデータの定義命令。ワード = 2バイト。

| SHLC A  - JP (PC+A) -  34  - C2  78 - C3  37 - DA  B0 - E1 |               |   |  |  |  |  |

|------------------------------------------------------------|---------------|---|--|--|--|--|

| 34<br>C2<br>78<br>C3<br>37<br>DA<br>B0                     | SHLC A        |   |  |  |  |  |

| C2<br>78<br>C3<br>37<br>DA<br>B0                           | - JP (PC+A) - |   |  |  |  |  |

| 78<br>C3<br>37<br>DA<br>B0                                 |               |   |  |  |  |  |

| C3<br>37<br>DA<br>B0                                       |               | ٦ |  |  |  |  |

| <u>37</u><br>DA<br>B0                                      | 78            |   |  |  |  |  |

| DA<br>B0                                                   | C3            |   |  |  |  |  |

| B0                                                         |               |   |  |  |  |  |

|                                                            | DA            |   |  |  |  |  |

| E1                                                         |               |   |  |  |  |  |

|                                                            | E1            |   |  |  |  |  |

|                                                            |               |   |  |  |  |  |

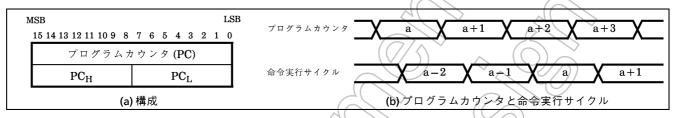

### 1.3 プログラムカウンタ(PC)

プログラムカウンタは、次に実行すべき命令の格納されているプログラムメモリのアドレスを指す 16ビットのレジスタです。

リセット解除時、ベクタテーブル (FFFF, FFFE $_H$ 番地) に格納されているリセット ベクタがプログラムカウンタにロードされますので、任意のアドレスからプログラムの実行を開始することができます。例えば、FFFF, FFFE $_H$ 番地にそれぞれ、 $_{\rm C0,3E_H}$ が格納されている場合、リセット解除後 $_{\rm C03E_H}$ 番地から実行開始します。

TLCS-870シリーズは、パイプライン処理(命令先行フェッチ)を行っていますので、プログラムカウンタは、常に2アドレス先を指します。例えば、 $C123_H$ 番地に格納されている1バイト命令の実行中、プログラムカウンタの内容は、 $C125_H$ です。

図1-3. プログラムカウンタ

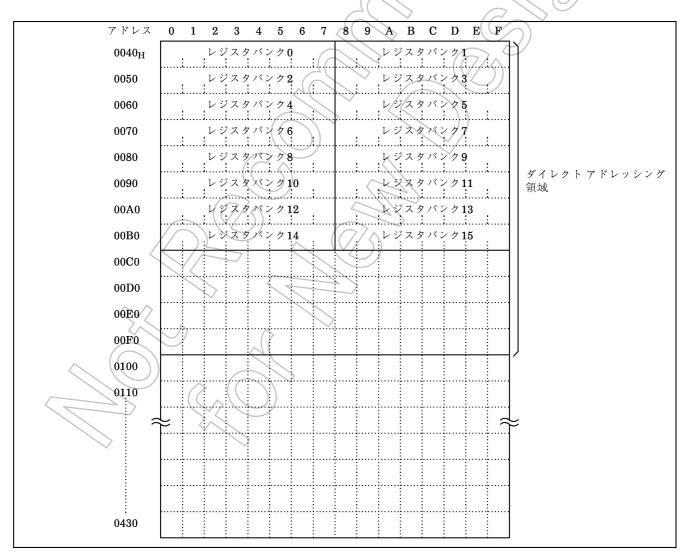

#### 1.4 データメモリ (RAM)

TMP87CH29/K29/M29は、 $1 \, \text{K}$ バイト (アドレス $0040 \sim 043 \, \text{F}_{\text{H}}$ 番地) のデータメモリ (スタティック RAM) を内蔵しています。図1-4にデータメモリマップを示します。

$0000\sim00 FF_H$ 番地は、ダイレクトアドレッシング領域になっており、このアドレッシング モードを用いる命令が強化されていますので、 $0040\sim00 FF_H$ 番地のデータメモリは、ユーザーフラグやユーザーカウンタとしても使用できます。

例1: データメモリの $00C0_H$ 番地のビット2が"1"なら $00E3_H$ 番地に $00_H$ を書き込み、"0"なら $FF_H$ を書き込む処理。

TEST (00C0H).2 ;

; if  $(00C0_{\rm H})_2=0$  then jump

JRS T,SZERO

CLR (00E3H);  $(00E3H) \leftarrow 00H$

JRS T,SNEXT

SZERO: LD (00E3H), 0FFH ;  $(00E3H) \leftarrow FFH$

SNEXT:

例2: データメモリの $00 extbf{F}5 extbf{H}$ 番地の内容をインクリメントし、 $10 extbf{H}$ 以上になると $00 extbf{H}$ にクリアする処理。

INC (00F5H)

AND (00F5H), 0FH

$0040 \sim 00BF_H$ 番地の128バイトには、汎用レジスタバンク (8レジスタ $\times 16$ バンク)が割り付けられています。レジスタとして使用中でも、データメモリとしてアクセスできます。例えば、 $0040_H$ 番地を読み出すとバンク0のアキュムレータの内容が読み出されます。

また、データメモリ上の任意の領域にスタックを設定できます。スタックについては、『1.7 スタック,スタックポインタ』を参照してください。

87CH29-9 2003-03-20

なお、TLCS-870シリーズは、データメモリ上に置かれたプログラムを実行することはできません。プログラムカウンタがデータメモリを指した場合、バスエラーによりアドレストラップリセットがかかります(RESET 端子出力が "L" レベルになります)。

<u>データメモリの内容は、電源投入時不定になりますので、イニシャライズルーチンで初期設定を</u> 行ってください。

例1: RAMのクリア (バンク0以外のRAMをすべてゼロクリア)

LD HL, 0048H ; スタートアドレス (HL) の設定

LD A, H ; 初期化データ (A) の設定

LD BC, 03F7H ; バイト数-1 (BC)の設定

SRAMCLR: LD (HL+), A

DEC BC

JRS F. SRAMCLR

注) 汎用レジスタはRAM上に存在しますので、カレントバンクのアドレスに対してRAMクリアしないでください。そのため、上記の例でバンク0を除いてRAMクリアしています。

図1-4. データメモリ マップ

87CH29-10 2003-03-20

### 1.5 汎用レジスタバンク

汎用レジスタは、データメモリの $0040\sim00BF_H$ 番地にマッピングされており、W, A, B, C, D, E, H, Lの8ビットレジスタ8本を1バンクとして16バンク内蔵しています。図1-5に汎用レジスタ バンクの構成を示します。なお、使用しないレジスタバンクは、データメモリとして使用できます。

図1-5. 汎用レジスタバンクの構成

各レジスタは、8ビット単位のアクセスのほか、WA, BC, DE, HLのレジスタペアとして16ビット単位のアクセスを行うことができます。また、汎用レジスタとしての機能のほかに、次の機能を有しています。

#### (1) A, WA

**A**は**8**ビット長のアキュムレータとして、**WA**は**16**ピット長のアキュムレータ (**W**が上位**, A**が下位) としての機能を有しています。

例: ① ADD A, B

**; A**の内容に**B**の内容を足して、結果を**A**に入れます。

2 SUB WA. 1234H

**, WA**の内容から即値**1234<sub>H</sub>を引き、結果をWA**に入れます。

# (2) HL, DE

HLは、データポインタ/インデックスレジスタ/ベースレジスタとして、DEは、データポインタとしての機能を有しており、メモリのアドレス指定に使われます。

また、HLにはオートポストインクリメント/プリデクリメント機能があり、多桁のデータ処理やソフトウエアLIFO(ラストインファーストアウト)処理が容易にできます。

例1: ① LD A, (HL)

: HLで指定されるアドレスのメモリ内容をAにロードします。

2 LD A, (HL+52H);

$\mathbf{HL}$ に即値 $\mathbf{52_H}$ を符号拡張加算した値で指定されるアドレスのメモリ内容を $\mathbf{A}$ にロードします。

3 LD A, (HL+C)

; HLにCレジスタの内容を符号拡張加算した値で指定されるアドレスのメモリ内容をAにロードします。

4 LD A, (HL+)

; HLで指定されるアドレスのメモリ内容をAにロード後、HLの 内容をインクリメントします。

⑤ LD A, (-HL)

; HLの内容をデクリメントし、その値で指定されるアドレスのメモリ内容をAにロードします。

87CH29-11 2003-03-20

TLCS-870シリーズは、メモリからメモリにデータを直接転送したり、メモリとメモリとの間で直接演算することができ、ブロック処理などを容易にプログラミングできます。

例2: ブロック 転送

LD B, m ; m=n-1(n: 転送バイト数)

LD HL, DSTA ; 転送先アドレス

LD DE, SRCA ; 転送元アドレス

SLOOP: LD (HL), (DE) ;  $(HL) \leftarrow (DE)$

INC HL ;  $HL \leftarrow HL+1$ INC DE :  $DE \leftarrow DE+1$

DEC B ;  $B \leftarrow B-1$

JRS F, SLOOP ; if  $B \ge 0$  then loop

#### (3) B, C, BC

B, Cは8ビットの、BCは16ビットのバッファ, カウンタなどに使用できます。Cは、レジスタインデックスアドレッシング (HL+C) におけるオフセットレジスタとして (前記の例1③)、また除算命令における除数レジスタとしての機能を有しています。

例1: リピート処理

LD B, n ; リピート回数の設定 (n+1回処理が行われます)

SREPEAT: 処 理

DEC B

JRS F, SREPEAT

例2: 除算(16ビット÷8ビット)

DIV WA, C ; WA  $\div$  C  $\circ$

WA÷Cの演算を行い、商をAに、余りをWに入れます。

汎用レジスタのバンク選択は、**4**ピットのレジスタバンクセレクタ(RBS)により行います。リセット時 RBSは"0"に初期化されますので、バンク0に初期設定されます。RBSで選択されているバンクをカレントバンクと呼びます。

RBSは、フラグとともにプログラム ステータス ワード (PSW) として、SFR内の $003F_H$ 番地に割り付けられており、メモリアクセス命令で操作します。なお、即値設定およびプッシュ/ポップのみ専用命令[LD RBS, n], [PUSH PSW], [POPPSW] が用意されています。

例1: RBSのインクリメント

INC (003FH) ; RBS  $\leftarrow$  RBS + 1

例2: RBSのリード

LD A, (003FH) ;  $A \leftarrow RBS$ (この命令ではフラグも同時に読み出されますので、実際は $A \leftarrow PSW$ となります)

割り込み処理におけるレジスタの退避,サブルーチン処理におけるパラメータの受け渡しにバンク切り替えを使うことにより、効率のよいプログラムを組むことができ、また、高速にタスクスイッチングができます。割り込み受け付け時、RBSは自動的にスタックに退避されます。なお、割り込みリターン命令[RETI], [RETN]の実行により、自動的に割り込み受け付け前のバンクに復帰しますので、RBSの退避/復帰のソフトウエア処理は必要ありません。

87CH29-12 2003-03-20

TLCS-870シリーズは最大15要因の割り込みをサポートしており、各要因に1バンクを割り当て、さらにメインタスクに1バンクのレジスタを割り当てることができます。また、メモリの使用効率を上げる場合、多重化しない割り込み要因には共通のバンクを割り当てて使用します。

例: バンク切り替えによる割り込みタスクにおける汎用レジスタの退避/復帰

PINT1: LD RBS, n : RBS←n(バンクnに切り替え)

割り込み処理

RETI ; マスカブル割り込みリターン (バンクは自動的に復帰)

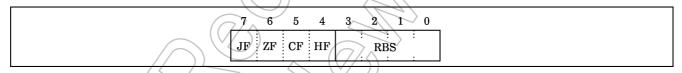

# 1.6 プログラム ステータス ワード (PSW)

プログラム ステータス ワードは、レジスタバンクセレクタ(RBS)とフラグから構成され、SFR内の $003F_{H}$ 番地に割り付けられています。

RBSは、メモリアクセス命令で読み出し/書き込みができ、フラグは読み出しのみできます。PSW に対して書き込みを行った場合、フラグにはデータは書き込まれず、その命令で定まった変化をします。例えば、[LD (003FH), 05H]命令を実行すると、RBSには"5"が書き込まれ、JFは"1"にセットされ、そのほかのフラグは変化しません。

割り込み受け付け時、PSWはプログラムカウンタとともにスタックに退避されます。また、PSWは割り込みリターン命令[RETI], [RETN] の実行によりスタックからリストアされ、割り込み受け付け直前の状態に戻ります。

PSWをアクセスする専用命令としてプッシュ [PUSH PSW]/ポップ [POP PSW] があります。

### 1.6.1 レジスタ バンク セレクタ (RBS)

汎用レジスタのバンクを選択する4ビットのレジスタです。例えば、RBS=2のとき、バンク2が現在選択されていることになります。

リセット時、RBSは"0"に初期化されます。

図1-6. PSW (フラグ, RBS) の構成

# 1.6.2 フラグ

ゼロフラグ、キャリーフラグ、ハーフキャリーフラグおよびジャンプステータスフラグの4ビットで構成され、命令で指定される条件に従いセット/クリアされます。ゼロフラグ、キャリーフラグおよびジャンプステータスフラグは、条件付きジャンプ命令[JR cc,\$+2+d]、[JRS cc,\$+2+d]のジャンプ条件ccとなります。

リセット解除時 ジャンプステータスフラグは、"1"に初期化されます (そのほかのフラグは初期化されません)。

#### (1) ゼロフラグ (ZF)

ゼロフラグは、演算結果または転送データが $00_H$ (8ビット演算/転送時)/ $0000_H$ (16ビット演算時)のとき "1" にセットされ、そのほかのときは "0" にクリアされます。ビット操作命令では、指定ビットの内容が "0" のとき **ZF**は "1" にセットされ、指定ビットの内容が"1" のとき **ZF**は "0" にクリアされます (ビットテスト)。乗算命令の場合 積の上位8ビットが $00_H$ のとき、除算命令の場合 剰余が $00_H$ のとき、**ZF**は "1" にセットされ、そのほかのときは"0" にクリアされます。

87CH29-13 2003-03-20

# (2) キャリーフラグ (CF)

演算時のキャリーまたはボローがセットされます。除算命令の場合、除数が $00_H$ のとき (Divided by zero Error)、または、商が100H以上のとき (Quotient Error)、"1"にセットされます。

シフト/ローテート命令では、レジスタからシフトアウトされるデータがセットされます。

ビット操作命令では、1ビット長のレジスタ(ブーリアンアキュムレータ)として機能します。ま た、キャリーフラグ操作命令によりセット/クリア/反転ができます。

例: ビット操作  $(07_H$ 番地のビット5の内容と $9A_H$ 番地のビット0の内容とで排他的論理和をとり、結 果を $01_H$ 番地のビット2に書き込みます)。

> LDCF, (0007H).5 ;  $(0001_{\rm H})_2 \leftarrow (0007_{\rm H})_5 \forall (009A_{\rm H})_0$

XOR CF, (009AH).0

LD(0001H).2, CF

DAA

### (3) ハーフキャリーフラグ (HF)

8ビット演算時、4ビット目へのキャリーまたは4ビット目からのボローがセットされます。HFは、 BCDデータの加減算の際の十進補正用のフラグです([DAA r], [DAS r]命令による十進補正)。

例: BCD演算(A=19<sub>H</sub>, B=28<sub>H</sub>のとき、次の命令を実行すると、Aは47<sub>H</sub>になります)。

ADD A, B

;  $A \leftarrow 41_H$ ,  $HF \leftarrow 1$ , CF = 0 $A \leftarrow 41_{H} + 06_{H} = 47_{H}$  (十進補正)

# (4) ジャンプ ステータス フラグ (JF)

通常、"1"にセットされるフラグで、命令に従いゼロまたはキャリー情報がセットされ、条件付き ジャンプ命令

[JR T/F, \$+2+d], [JRS T/F, \$+2+d] (T, Fは条件コードです) のジャンプ条件となります。

例: ジャンプステータスフラグと条件付きジャンプ命令

Α

INC

**JRS** T. SLABLE1 直前の演算命令で桁上げが発生した場合 ジャンプします。

A, (HL) LD

JRS T, SLABLE2 直前の命令でJFは"1"にセットされますので、 無条件ジャンプ命令と見なされます。

例: WAレジスタペア, HLレジスタペア, データメモリの00C5H番地, キャリーフラグ, ハーフ キャリーフラグの内容がそれぞれ "219AH", "00C5H", "D7H", "1", "0" のとき、下記命令を実 行するとアキュムレータおよび各フラグは次のようになります。

| 命    |         | 実行後の    | 実  | 行後0 | タフラ | グ  |

|------|---------|---------|----|-----|-----|----|

| /    |         | アキュムレータ | JF | ZF  | CF  | HF |

| ADDC | A, (HL) | 72      | 1  | 0   | 1   | 1  |

| SUBB | A, (HL) | C2      | 1  | 0   | 1   | 0  |

| СМР  | A, (HL) | 9A      | 0  | 0   | 1   | 0  |

| AND  | A, (HL) | 92      | 0  | 0   | 1   | 0  |

| LD   | A, (HL) | D7      | 1  | 0   | 1   | 0  |

| ADD  | A, 66H  | 00      | 1  | 1   | 1   | 1  |

| 命令             | 実行後の    | 実  | 行後0 | のフラグ |    |  |  |

|----------------|---------|----|-----|------|----|--|--|

| 1412 12        | アキュムレータ | JF | ZF  | CF   | HF |  |  |

| INC A          | 9B      | 0  | 0   | 1    | 0  |  |  |

| ROLC A         | 35      | 1  | 0   | 1    | 0  |  |  |

| RORC A         | CD      | 0  | 0   | 0    | 0  |  |  |

| ADD WA, 0F508H | 16A2    | 1  | 0   | 1    | 0  |  |  |

| MUL W, A       | 13DA    | 0  | 0   | 1    | 0  |  |  |

| SET A.5        | BA      | 1  | 1   | 1    | 0  |  |  |

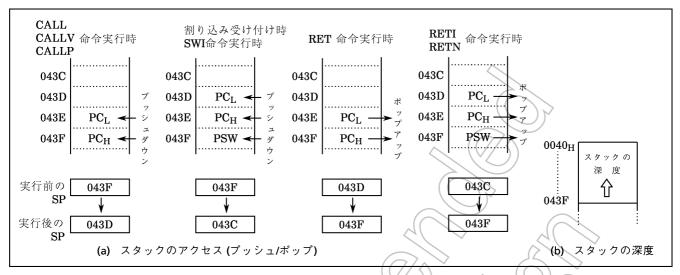

#### 1.7 スタック, スタックポインタ

#### 1.7.1 スタック

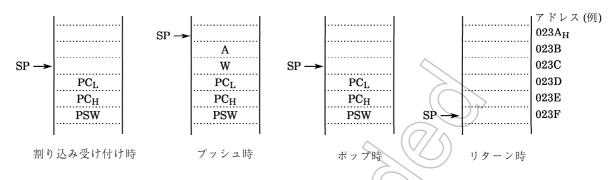

スタックは、サブルーチンコール命令実行時または割り込み受け付け時にその処理ルーチンへジャンプするに先立ってプログラムカウンタの内容(戻り番地)やプログラムステータスワードの内容などをセーブするエリアです。

サブルーチンコール命令[CALL a], [CALLP a], [CALLV n]実行時、戻り番地(上位バイト,下位バイトの順に)がスタックに退避(プッシュダウン)されます。ソフトウエア割り込み命令[SWI]実行時または割り込み受け付け時は、まずプログラムステータスワードの内容がスタックに退避され、次に戻り番地が退避されます。

処理ルーチンから復帰する場合、サブルーチンリターン命令[RET]を実行することによりスタックからプログラムカウンタへ、割り込みリターン命令[RETI]、[RETN]を実行することによりスタックからプログラムカウンタおよびプログラムステータスワードへ、それぞれの内容がリストア(ポップアップ)されます。

スタックは、データメモリ内の任意のエリアに設定できます。

#### 1.7.2 スタックポインタ (SP)

MSB 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 スタックポインタ (SP)

図1-7. スタックポインタ

スタックポインタは、スタックの先頭番地を指す16ビットのレジスタです。スタックポインタは、サブルーチンコール,プッシュ命令実行時および割り込み受け付け時にポストデクリメントされ、リターン,ポップ命令実行時にプリインクリメントされます。従って、スタックはアドレスの若い方に向かって深くなります。スタックのアクセスとスタックポインタの変化を図1-8に示します。

スタックポインタは、ハードウエア的には初期化されませんので、イニシャライズルーチンで初期化(スタックの最高位アドレスをセット)する必要があります。スタックポインタを操作する命令には、[LD SP, mn], [LD SP, gg] および

[LD gg, SP] (mnは16ビット即値、ggはレジスタペア) があります。

例1: スタックポインタのイニシャライズ

LD SP, 043FH

; SP←043F<sub>H</sub>

例2: スタックポインタのリード

LD HL, SP

; HL←SP

図1-8. スタック

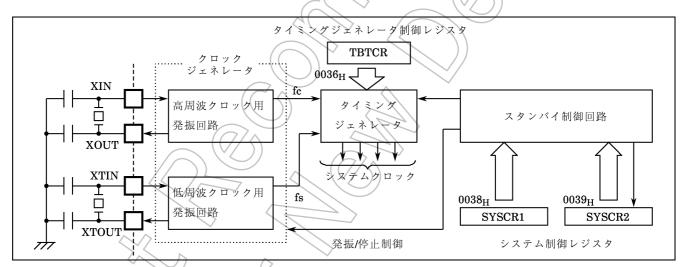

#### 1.8 システムクロック制御回路

システムクロック制御回路は、クロックジェネレータ,タイミングジェネレータおよびスタンバイ 制御回路から構成されています。

図1-9. システムクロック制御回路

87CH29-16 2003-03-20

#### 1.8.1 クロックジェネレータ

クロックジェネレータは、CPUコアおよび周辺ハードウエアに供給されるシステムクロックの基準となる基本クロックを発生する回路です。高周波クロック用と低周波クロック用の2つの発振回路を内蔵しており、スタンバイ制御回路で低周波クロックによる低速動作に切り替えて消費電力の低減を図ることもできます。

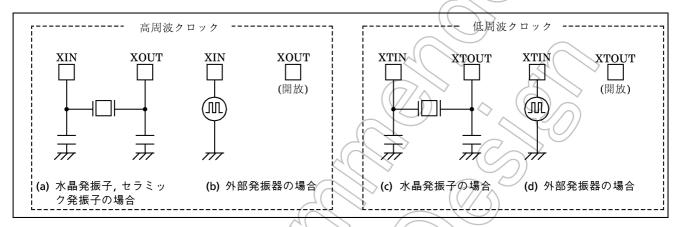

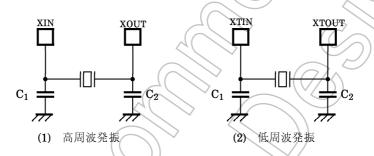

高周波クロック (周波数fc), 低周波クロック (周波数fs) は、それぞれXIN, XOUT端子, XTIN, XTOUT端子に発振子を接続することにより容易に得られます。また、外部発振器からのクロックを入力することもできます。

図1-10. 発振子の接続例

#### 注) 発振周波数の調整

基本クロックを外部にて直接モニタする機能はハードウエア的には用意されていませんが、割り込み禁止状態, ウォッチドッグタイマのディセーブル状態でプログラムによってポートに一定周波数のパルスを出力させ、これをモニタすることにより調節を行うことができます。発振周波数の調整が必要なシステムでは、あらかじめ調整用プログラムを作成しておく必要があります。

#### 1.8.2 タイミングジェネレータ

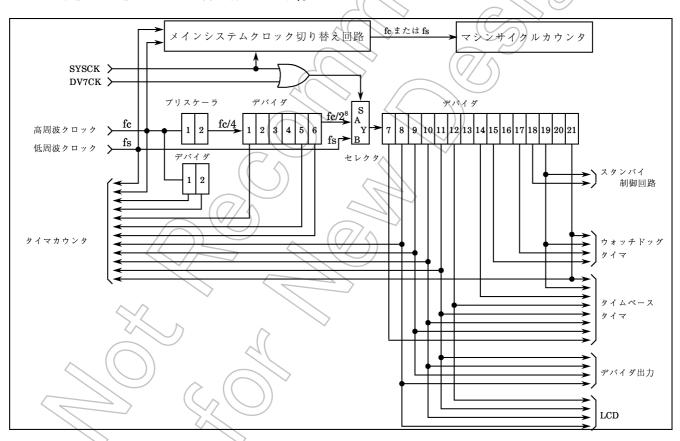

タイミング ジェネレータは、基本クロックからCPUコアおよび 周辺ハードウエアに供給する各種 システムクロックを発生する回路です。タイミング ジェネレータの機能は、次のとおりです。

- ① メインシステムクロック生成

- ② デバイダ出力 (**DVO**) パルス生成

- ③ タイマベースタイマのソースクロック生成

- 4 ウォッチドッグタイマのソースクロック生成

- ⑤ タイマカウンタの内部ソースクロック生成

- ⑥ STOPモード解除時のウォーミングアップクロック生成

- ⑦ LCDベース周波数生成

87CH29-17 2003-03-20

# (1) タイミングジェネレータの構成

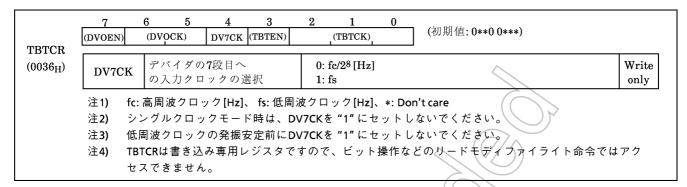

タイミングジェネレータは、2段のプリスケーラ、21段のデバイダ、メインシステムクロック切り替え回路およびマシンサイクルカウンタから構成されています。デバイダの7段目への入力クロックは動作モードおよびDV7CK (TBTCRのビット4) により次のようになります。なお、リセット時およびSTOPモード起動/解除時デバイダは"0"にクリアされます (ただし、プリスケーラはクリアされません)。

#### ① シングルクロックモード時

高周波クロック (周波数fc) を256分周したクロック (fc/28) がデバイダの7段目に入力されます。 なお、シングルクロックモード時DV7CKを"1" にセットしないでください。

#### ② デュアルクロックモード時

NORMAL2, IDLE2モード時 (SYSCK=0) は、DV7CK により、デバイダの7段目への入力クロックをfc/28かfsかのいずれかの選択ができます。SLOW, SLEEPモード時 (SYSCK=1) は、自動的にfsがデバイダの7段目に入力されます (なお、デバイダの初段への入力クロックは停止しますので、デバイダの初段からfs段目までの出力も停止します)。

図1-11. タイミングジェネレータの構成

87CH29-18 2003-03-20

図1-12. タイミング ジェネレータ制御レジスタ

# (2) マシンサイクル

命令の実行および内蔵ハードウエアの動作は、システムクロックに同期して行われます。

命令実行の最小単位を、『マシンサイクル』と呼びます。TLCS-870シリーズの命令には、1マシンサイクルで実行される1サイクル命令から最長10マシンサイクルを要する10サイクル命令までの10種類があります。

マシンサイクルは、4ステート ( $S0\sim S3$ ) で構成され、各ステートは1メインシステムクロックで構成されます。

図1-13. マシンサイクル

#### 1.8.3 スタンバイ制御回路

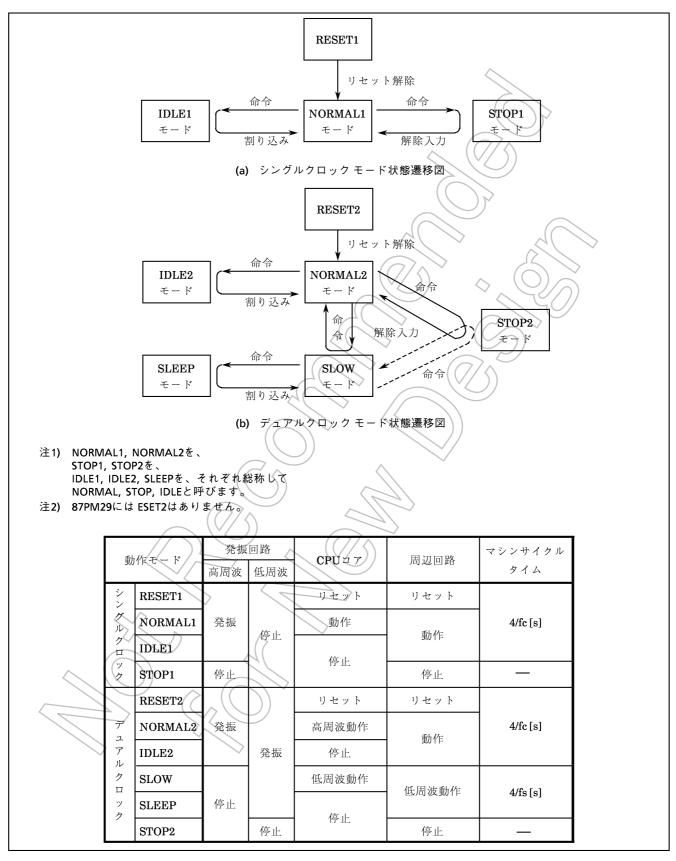

スタンバイ制御回路は、高周波クロック用、低周波クロック用の各発振回路の発振/停止およびメインシステムクロックの切り替えを行います。動作モードは、シングルクロックモードとデュアルクロックモードに大別され、各動作モードの制御はシステム制御レジスタ (SYSCR1, SYSCR2) で行います。図1-14に動作モード遷移図を、図1-15に制御レジスタを示します。

リセット解除時の動作モードは、シングルクロックモードかデュアルクロックモードかのいずれかをオプションで指定することができます。ただし、TMP87PM29はシングルクロックモード固定となります(デュアルクロックモードで使用する場合は、プログラムの先頭で低周波クロックを発振させてください)。

### (1) シングル クロック モード

高周波クロック用発振回路のみ使用し、P21 (XTIN), P22 (XTOUT) は、通常の入出力ポートとなります。メインシステムクロックは、高周波クロックから生成されますので、シングル クロック モードにおけるマシンサイクルタイムは 4/fc [s] (0.5  $\mu$ s @ fc = 8 MHz) となります。

87CH29-19 2003-03-20

#### ① NORMAL1モード

CPUコアおよび周辺ハードウエアを高周波クロックで動作させるモードです。シングルクロックモードをオプション選択した場合、リセット解除後このNORMAL1モードになります。

#### ② **IDLE1**モード

CPUおよび ウォッチドッグ タイマ を停止し、周辺ハードウエアを高周波クロックで動作させるモードです。IDLE1モードの起動は、システム制御レジスタ2で行います。周辺ハードウエアからの割り込みまたは外部割り込みにより解除され、NORMAL1モードに復帰します。IMF(割り込みマスタ許可フラグ)が "1"(割り込み許可状態)のときは、割り込み処理が行われたあと、通常の動作に戻ります。IMFが "0"(割り込み禁止状態)のときは、IDLE1モードを起動した命令の次の命令から実行再開します。

#### ③ **STOP1**モード

発振回路を含めシステムの動作をすべて停止し、停止直前の内部状態を低消費電力で保持するモードです。また、入出力ポートの出力状態は、プログラムで全ポート一括して出力保持/ハイインピーダンスの選択ができます。

STOP1モードの起動は、システム制御レジスタ1で行います。解除は、STOP端子入力(レベル/エッジの選択可能)で行い、ウォーミングアップ時間経過後、STOP1モードを起動した命令の次の命令から実行再開します。

#### (2) デュアル クロック モード

高周波, 低周波用の2つの発振回路を使用する動作モードで、P21 (XTIN), P22 (XTOUT) は入出力ポートとして使用することはできません。メインシステムクロックは、NORMAL2, IDLE2モード時、高周波クロックから生成され、SLOW, SLEEPモード時、低周波クロックから生成されています。従って、マシンサイクルタイムは、NORMAL2, IDLE2 モード時 4/fc [s], SLOW, SLEEP モード時 4/fc [s] (122  $\mu$ s @ fs = 32.768 kHz) となります。

#### ① **NORMAL2**モード

CPUコアを高周波クロックで動作させるモードで、周辺ハードウエアは高周波/低周波の両クロックで動作します。デュアルクロックモードをオプション選択した場合、リセット解除後このNORMAL2モードになります。

#### ② SLOWモード

高周波クロックの発振を停止させ、CPUコア,周辺ハードウエアを低周波クロックで動作させるモードで消費電力を低減できます。NORMAL2からSLOWへの切り替え,SLOWからNORMAL2への切り替えは、システム制御レジスタ2で行います。

# ③ IDLE2モード

**CPU**およびウォッチドックタイマを停止し、周辺ハードウエアを高周波/低周波の両クロックで動作させるモードです。**IDLE2**モードの起動/解除方法は、**IDLE1**モードと同じです。解除後、**NORMAL2**モードに戻ります。

#### ④ SLEEPモード

CPUおよびウォッチドッグタイマを停止し、周辺ハードウエアを低周波クロックで動作させるモードです。SLEEPモードの起動/解除方法は、IDLE1モードと同じです。解除後、SLOWモードに戻ります。なお、高周波クロックは発振しておりません。

# ⑤ **STOP2**モード

シングル クロック モードのSTOP1モードと同様、システムの動作をすべて停止するモードです。

87CH29-20 2003-03-20

図1-14. 動作モード 状態遷移図

87CH29-21 2003-03-20

システム制御レジスタ1

SYSCR1 (0038<sub>H</sub>)

| 7    | 6    | 5    | 4     | 3 | 2       | 1 | 0 |   |                  |

|------|------|------|-------|---|---------|---|---|---|------------------|

| STOP | RELM | RETM | OUTEN | w | UT<br>I |   |   | • | (初期値: 0000 00**) |

| STOP  | STOPモードの起動                 | 0: CPUコア, 周辺ハードウエア動作<br>1: CPUコア, 周辺ハードウエア停止 (STOPモード起動)                                                         |     |

|-------|----------------------------|------------------------------------------------------------------------------------------------------------------|-----|

| RELM  | STOPモードの解除方法の<br>選択        | 0: <u>STOP</u> 端子入力の立ち上がりエッジで解除<br>1: <u>STOP</u> 端子入力の"H" レベルで解除                                                |     |

| RETM  | STOPモード解除後の<br>動作モードの選択    | 0: NORMALモードへ戻る<br>1: SLOWモードへ戻る                                                                                 | R/W |

| OUTEN | STOPモード時の<br>ポート出力状態の選択    | 0: ハイインピーダンス<br>1: 出力保持                                                                                          |     |

| WUT   | STOPモード解除時の<br>ウォーミングアップ時間 | 00: 3×2 <sup>19</sup> /fcまたは3×2 <sup>13</sup> /fs [s] 01: 2 <sup>19</sup> /fcまたは2 <sup>13</sup> /fs 1*: Reserved |     |

- 注1) RETMは、NORMAL1モードからSTOP1モードに移す場合およびNOMAL2モードからSTOP2モードに移す場合は必ず "0" にしてください。SLOWモードからSTOP2モードに移す場合は必ず "1" にしてください。

- 注2) STOPモードをRESET端子入力で解除した場合は、RETMの値にかかわらずNORMAL1モードに戻ります。

- 注3) SYSCR1のビット1,0は、リードすると不定値が読み出されます。

- 注4) fc: 高周波クロック [Hz] fs: 低周波クロック [Hz]

- \*: Don't care

- 注5) OUTEN = "0" の指定でSTOP動作に入ると、内部入力は "0" に固定されますので、立ち下がりエッジの割り込みがセットされる恐れがあります。

### システム制御レジスタ2

$\begin{array}{c} {\rm SYSCR2} \\ {\rm (0039_H)} \end{array}$

| 7   | 6    | 5     | 4    | 3 | 2 | 1 | 0 |

|-----|------|-------|------|---|---|---|---|

| XEN | XTEN | SYSCK | IDLE |   |   |   |   |

(初期値: 10/100 \*\*\*\*)

| XEN   | 高周波発振器の制御                        | 0: 発振停止<br>1: 発振継続 または 発振開始                                        |     |

|-------|----------------------------------|--------------------------------------------------------------------|-----|

| XTEN  | 低周波発振器の制御                        | 0: 発振停止<br>1: 発振継続 または 発振開始                                        |     |

| SYSCK | システムクロックの<br>選択(write)/モニタ(read) | 0: 高周波クロック(NORMAL1/NORMAL2/IDLE1/IDLE2)<br>1: 低周波クロック (SLOW/SLEEP) | R/W |

| IDLE  | IDLE モードの起動                      | 0: CPU, WDT動作<br>1: CPU, WDT停止 (IDLE1/IDLE2/SLEEPモード起動)            |     |

- 注1) XEN, XTENをともに "0" にするとリセットがかかります(RESET 端子出力が"L"レベルとなります)。

- 注2) SYSCK = 0のときXENを "0" に、またSYSCK = 1のときXTENを "0" にしないでください。

- 注3) WDT: ウォッチドッグタイマ、\*: Don't care

- 注4) SYSCR2のビット3~0は、リードすると"1"が読み出されます。

- 注5) XTENは、初期値のオプション選択ができます。ES発注の際、マイクロコントローラエンジニアリングサンプル(ES)作成依頼書にてマスクオプションの指定を、必ず行ってください。記入の仕方については付録の"TLCS-870シリーズにおけるマスクオプション指定方法"を参照してください。

| XTEN | リセット解除後の動作モード                                  |

|------|------------------------------------------------|

| 0    | シングルクロックモード (NORMAL1)<br>デュアルクロックモード (NORMAL2) |

| 1    | デュアルクロックモード (NORMAL2)                          |

図1-15. システム制御レジスタ1,2

87CH29-22 2003-03-20

#### 1.8.4 動作モードの制御

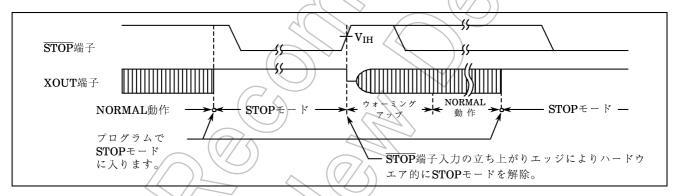

(1) STOPモード (STOP1, STOP2)

STOPモードは、システム制御レジスタ1(SYSCR1)とSTOP端子入力によって制御されます。STOP端子は、P20ポートならびにINT5 (外部割り込み入力5)端子と兼用です。STOPモードは、STOP(SYSCR1のビット7)を"1"にセットすることにより起動され、STOPモード中、次の状態を保持しています。

- ① 高周波, 低周波とも発振を停止し、内部の動作をすべて停止します。

- ② データメモリ、レジスタ (DBRを除く)、プログラムスデータスワード、ポートの出力ラッチ などはSTOPモードに入る直前の状態を保持します。なお、ポート出力はOUTEN (SYSCR1 のビット4) の設定により、出力保持/ハイインピーダンスの選択ができます。

- ③ タイミングジェネレータのデバイダを"0"にクリアします。

- ④ プログラムカウンタは、STOPモードを起動する命令(例えば、[SET(SYSCR1).7])の2つ先の命令のアドレスを保持します。

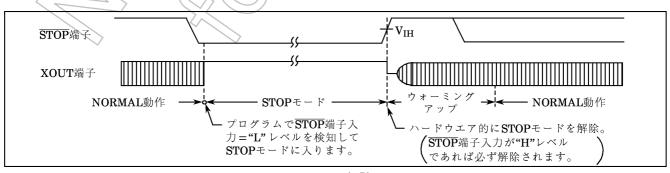

STOPモードには、レベル解除モードとエッジ解除モードがあり、システム制御レジスタ1のRELM (SYSCR1のビット6)で選択します。

a. レベル解除モード (RELM="1"のとき)

**STOP**端子への"H"レベル入力により**STOP**動作を解除するモードで、メイン電源遮断時のコンデンサバックアップや長時間のバッテリーバックアップなどに使用します。

$\overline{STOP}$ 端子入力が"H"レベルの状態で $\overline{STOP}$ 動作の起動を指示する命令を実行しても、 $\overline{STOP}$ 動作に入らず、直ちに解除シーケンス (ウォーミングアップ) に移ります。従って、レベル解除モードで $\overline{STOP}$ 動作で起動する場合、 $\overline{\overline{STOP}}$ 端子入力が"L"レベルになっていることをプログラム上で認識する必要があります。この認識を行うには、次の方法があります。

INT5割り込みによる方法(INT5端子入力の立ち下がりエッジで割り込みを発生します)

例: INT5割り込みにより、STOPモードを起動

SINT5:

PINT5: TEST (P2).0

RETL

JRS F, SINT5

LD (SYSCR1), 01000000B

SET (SYSCR1).7

LDW (IL), 11100111010101111B

; ノイズ 除去のため **P20**ポート入力

が"H"レベルならSTOPモードを

起動しない。

; レベル解除モードにセットアップ

; **STOP**モードを起動

; IL12, 11, 7, 5,  $3 \leftarrow 0$

(割り込みラッチのクリア)

図1-16. レベル解除モード

87CH29-23 2003-03-20

- 注1) ウォーミングアップ開始後、再びSTOP端子入力が "L" レベルになってもSTOPモードには戻りません。

- 注2) エッジ解除モードにセットアップ後にレベル解除モードに戻した場合は、STOP端子入力の立ち上がりエッジが検出されるまではモードは切り替わりません。

#### b. エッジ解除モード (RELM="0"のとき)

**STOP**端子入力の立ち上がりエッジで**STOP**動作を解除するモードです。比較的短時間のプログラム処理を一定周期で繰り返す応用などに使用し、この一定周期の信号(例えば、低消費電力の発振源からのクロック)を**STOP**端子に入力します。エッジ解除モードの場合、**STOP**端子入力が**"H"**レベルにあっても**STOP**動作に入ります。

例: エッジ解除モードのSTOP動作を起動

LD (SYSCR1), 00000000B

、(ハイインピーダンス指定) ; **IMF** ← 0

DI

SET (SYSCR1), STOP

: STOP ←1 (STOPモード起動)

LDW (IL), 1110011101010111B

IL12, 11, 7, 5,  $3 \leftarrow 0$

(割り込みラッチのクリア)

OUTEN  $\leftarrow 0$

$\mathbf{EI}$

; /IMF ← 1

図1-17. エッジ解除モード

STOPモードの解除は、次のシーケンスで行われます。

- ① 発振が開始されます。デュアルクロックモードの場合、NORMAL2へ戻るときは高周波/低周波発振器の両方が発振し、SLOWに戻るときは低周波発振器のみ発振します。シングルクロックモードの場合は、高周波発振器のみ発振します。

- ② 発振が安定するのに必要な時間の確保のため、ウォーミングアップを行います。ウォーミングアップ中、内部動作は停止したままです。ウォーミングアップ時間は、発振器の特性に合わせてWUT(SYSCR1のビット3.2)で2種類選択できます。

- ③ ウォーミングアップ時間経過後、STOPモードを起動する命令の次の命令から通常の動作が再開されます。このとき、タイミングジェネレータのデバイダは"0"にクリアされた状態から始まります。

87CH29-24 2003-03-20

| NOR                                                       | MALモードに戻る場合      | SLOWモードに戻る場合       |                                          |                 |

|-----------------------------------------------------------|------------------|--------------------|------------------------------------------|-----------------|

| WUT                                                       | fc=4.194304 MHz時 | fc=8 MHz 時         | WUT                                      | fs=32.768 kHz 時 |

| $3	imes 2^{19} / 	ext{fc}  	ext{[s]} \ 2^{19} / 	ext{fc}$ | 375 [ms]<br>125  | 196.6 [ms]<br>65.5 | $3 \times 2^{13} / fs$ [s] $2^{13} / fs$ | 750 [ms]<br>250 |

表1-1. ウォーミングアップ時間(例)

注) ウォーミングアップ時間は、基本クロックをデバイダにて分周して得ていますので、STOPモードの解除時に発振周波数にゆらぎがある場合は、ウォーミングアップ時間は誤差を含むことになります。従って、ウォーミングアップ時間は、概略値としてとらえる必要があります。

なお、STOPモードは、 $\overline{\text{RESET}}$ 端子を"L"レベルにすることによっても解除され、直ちに通常のリセット動作を行います。この場合、SLOWモードに戻る設定がされていても、NORMALモード (TMP87CH29/K29/M29の場合、マスクオプションにてXTEN (SYSCR2のビット6) の初期値が"1"のときはNORMAL2モード、TMP87PM29の場合はNORMAL1モード) から始まります。

注)低い保持電圧でSTOPモードの解除を行う場合には、次の注意が必要です。 STOPモードの解除に先立ち、電源電圧を動作電圧に上げる必要があります。その際、RESET端子も "H" レベルにあり、電源電圧とともに上昇します。この場合、外部に時定数回路などが付加されているときには、RESET端子入力の電圧上昇は電源電圧の上昇よりも立ち上がりが遅くなります。このとき、RESET端子の入力電圧レベルが、RESET端子入力(ヒステリシス入力)の非反転高レベル入力電圧を切るとリセット動作を行う恐れがあります。

87CH29-25 2003-03-20

87CH29-26 2003-03-20

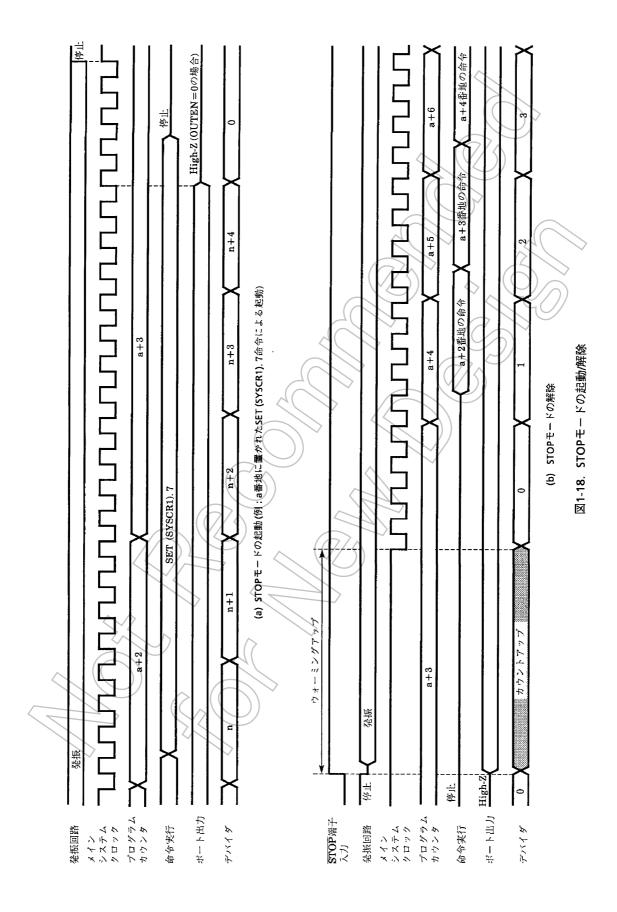

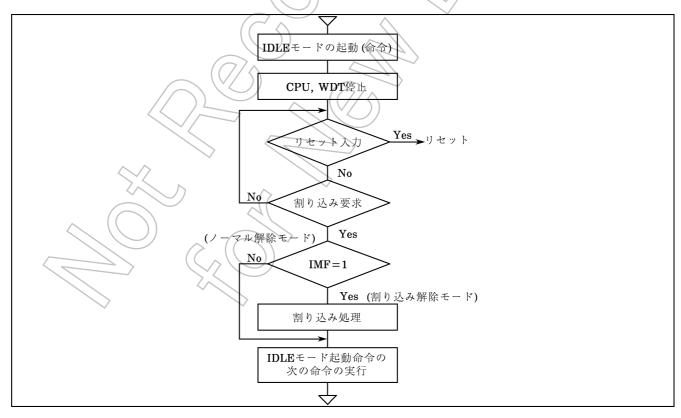

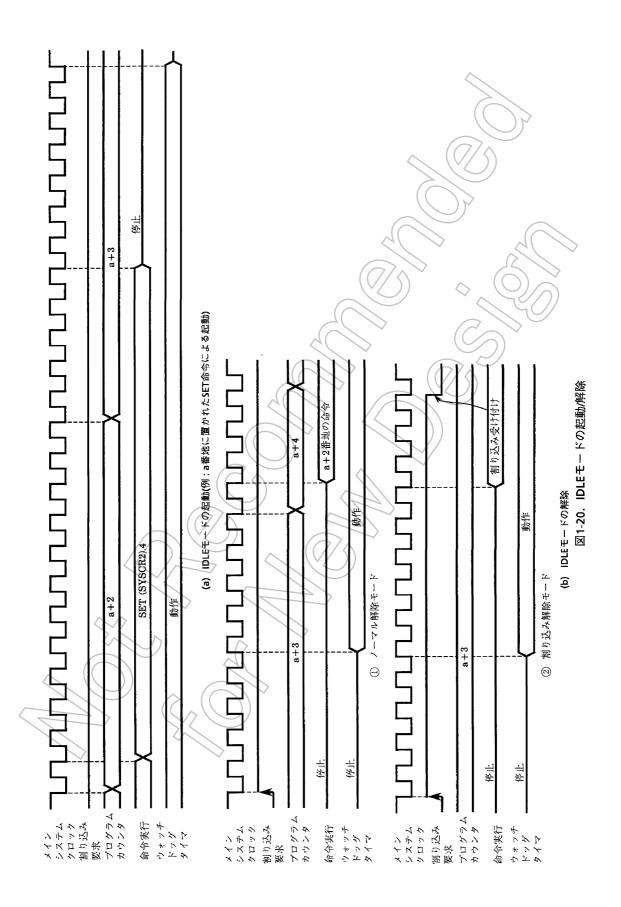

#### (2) IDLEモード (IDLE1, IDLE2, SLEEP)

IDLEモードは、システム制御レジスタ2(SYSCR2)とマスカブル割り込みによって制御されます。IDLEモード中、次の状態を保持しています。

- ① **CPU**およびウォッチドッグタイマは動作を停止します。 周辺ハードウエアは動作を継続します。

- ② データメモリ、レジスタ、プログラムステータスワード、ポートの出力ラッチなどは、 IDLEモードに入る直前の状態を保持します。

- ③ プログラムカウンタは、IDLEモードを起動する 命令の2つ先の命令のアドレスを保持します。

例: IDLEモードの起動

SET (SYSCR2).4

IDLEモードには、ノーマル解除モードと割り込み解除モードがあり、割り込みマスタ許可フラグ (IMF) で選択します。IDLEモード解除後、IDLE1モードのときはNORMAL1モードに、IDLE2モード のときはNORMAL2モードに、SLEEPモードのときはSLOWモードに戻ります。

# a. ノーマル解除モード (IMF="0"のとき)

割り込み個別許可フラグ (EF) で許可された割り込み要因または外部割り込み0 (INTO) の割り込み要求により、IDLEモードが解除され、IDLEモードを起動した命令の次の命令から実行を再開します。通常、解除に使用した割り込み要因の割り込みラッチ (IL) はロード命令で"0"にクリアする必要があります。

図1-19. IDLEモード

87CH29-27 2003-03-20

# <u>b.</u> 割り込み解除モード (IMF="1" のとき)

割り込み個別許可フラグ (EF) で許可された割り込み要因または外部割り込み0 (INTO) の割り込み要求によりIDLEモードが解除され、割り込み処理に入ります。割り込み処理後、IDLEモードで起動した命令の次の命令に戻ります。

なお、IDLEモードは、RESET端子を"L"レベルにすることによっても解除され、直ちに通常のリセット動作を行います。SLEEPモードでリセットをかけた場合は、リセット解除後NORMALモード(TMP87CH29/K29/M29の場合マスクオプションにてXTEN(SYSCR2のビット6)の初期値が"1"のときはNORMAL2モード、TMP87PM29の場合はNORMAL1モード)から始まります。

注)IDLEモード起動直前にウォッチドッグタイマ割り込みが発生した場合、IDLEモードは起動されずウォッチドッグタイマ割り込み処理が行われます。

87CH29-28 2003-03-20

87CH29-29 2003-03-20

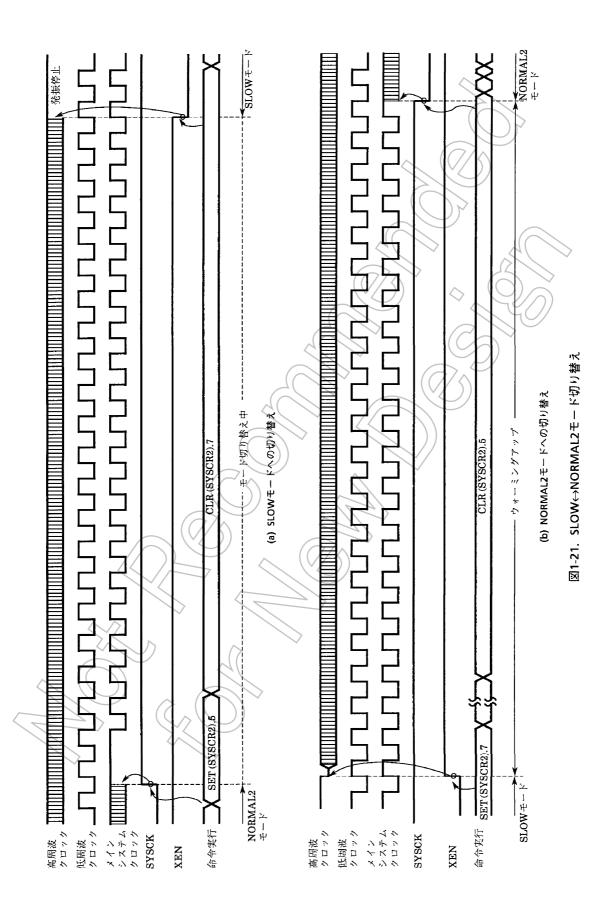

#### (3) SLOWモード

SLOWモードは、システム制御レジスタ2 (SYSCR2) および タイマカウンタ1 (TC1) によって制御されます。

a. NORMAL2モードからSLOWモードへの切り替え

まず、SYSCK (SYSCR2のビット5) に "1"を書き込み、システムクロックを低周波クロックに切り替えます。

次に、XEN (SYSCR2のビット7) を "0" にクリアして高周波発振器を停止します。

なお、低周波クロックが安定に発振していない場合は、安定発振するまで待ってから上記操作を行ってください。低周波クロックの安定発振を確認するのに、ダイマカウンタ1を使用すると便利です。

注) NORMAL2モードへ早く戻るために高周波クロックの発振を継続させることも可能です。 ただし、SLOWモードからSTOPモードを起動する場合は、必ず高周波クロックを停止し てください。

例1: NORMAL2モードからSLOWモードへの切り替え

SET (SYSCR2).5 ; SYSCK←1 (システムクロックを

低周波に切り替え)

CLR (SYSCR2).7 ; XEN←0 (高周波クロック停止)

例2: TC1で低周波クロックの発振安定の確認後、SLOWモードへ切り替え。

LD (TC1CR1),04H ; TC1のモードをセット

(タイマモード、ソースクロック:fs) ウォーミングアップ時間をセット

(発振子の特性で時間を決定します)

INTTC1割り込み許可

LDW (TREG1 $A_L$ ), 8000H

LD  $(TREG1A_H)$ , 00H

SET (EIRH). EF8

LD (TC1CR1), 44H ; TC1スタート

PINTTC1: LD (TC1CR1), 04H ; TC1ストップ

SET (SYSCR2).5 ; SYSCK←1 (システムクロックを

低周波に切り替え)

CLR (SYSCR2).7 ; XEN ← 0 (高周波クロック停止)

RETI

VINTTC1: DW PINTTC1 ; INTTC1ベクタテーブル

87CH29-30 2003-03-20

### b. SLOWモードからNORMAL2モードへの切り替え

まず、XEN (SYSCR2のビット7)を"1"にセットして高周波クロックを発振させます。発振の 安定時間(ウォーミングアップ)をタイマカウンタ1によって確保したあと、SYSCK (SYSCR2の ビット5)を"0"にクリアします。

- |注1) SYSCKを"0"にクリア後、低周波クロックと高周波クロックの同期をとっている期間は低周 波クロックで命令の実行を継続しています。

- SLOWモードは、リセットによってもNORMAL2モードへ戻ります (TMP87CH29/K29/M29の 場合、マスクオプションにてXTEN (SYSCR2のビット6) の初期値が"1"のときは NORMAL2モード、TMP87PM29の場合はNORMAL1モードへ戻ります)。

例: SLOWモードから NORMAL2モードへの切り替え (fc=8 MHz, ウォーミングアップ時間=7.9 ms)

SET (SYSCR2).7 LD(TC1CR1), 00H

LD(TREG1A<sub>L</sub>), 0F800H

LD(TREG1A<sub>H</sub>), 00H

SET (EIRH). EF8

LD(TC1CR1), 40H

:

(TC1CR1), 00H PINTTC1: LD

CLR (SYSCR2).5

RETI

VINTTC1: DW PINTTC1

**XEN←1** (高周波クロック発振開始)

TC1のモードをセット

(タイマモード, ソースクロック:fc)

ウォーミングアップ時間をセット

(周波数と発振子の特性で時間を決定

します)

INTTC1割り込み許可

TC1スタート

TC1ストップ

SYSCK←0 (システムクロックを

高周波に切り替え)

INTTC1ベクタテーブル

87CH29-31 2003-03-20

87CH29-32 2003-03-20

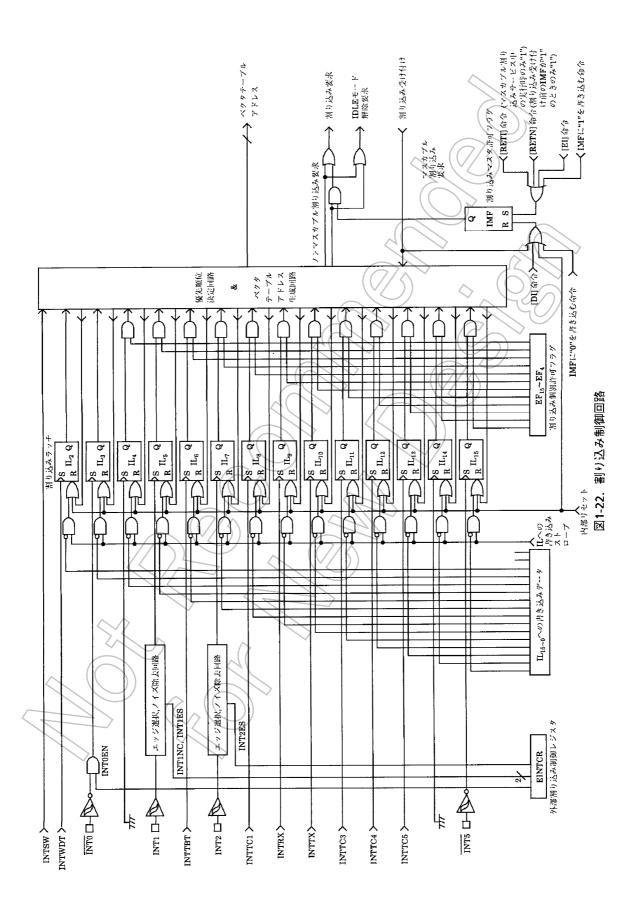

## 1.9 割り込み制御回路

TMP87CH29/K29/M29は、外部4種,内部9種の合計13種類の割り込み要因あり、優先順位付きの多重割り込みが可能です。内部要因のうち2種は擬似ノンマスカブル割り込みで、そのほかはすべてマスカブル割り込みです。

割り込み要因には、それぞれ割り込み要求を保持する割り込みラッチ (IL) が用意され、また、独立したベクタになっています。割り込みラッチは、割り込み要求の発生により"1"にセットされ、CPUに割り込みの受け付けを要求します。割り込みの受け付けは、割り込みマスタ許可フラグ (IMF) と各割り込み要因の個別許可フラグ (EF) によって、プログラムで選択的に許可/禁止できます。なお、複数の割り込みが同時に発生した場合は、ハードウエアで定められた優先順位の高いものから受け付けられます。

図1-22に割り込み制御回路を示します。

表1-2. 割り込み要因

|    |    | 割り        | 込 み 要 因                            | 許可象件                     | 割り込みラッチ           | ベクタ<br>アドレス       | 優 先月 | 順位 |

|----|----|-----------|------------------------------------|--------------------------|-------------------|-------------------|------|----|

| 内部 | 外部 | (リセット)    |                                    | ノンマスカブル                  | <u>-</u>          | $FFFE_H$          | 高位   | 0  |

| 内  | 部  | INTSW (   | ソフトウエア割り込み)                        | 167 (N) 1 (1 m m 1 m 1)  |                   | $FFFC_H$          |      | 1  |

| 内  | 部  | INTWDT (  | ウォッチドッグタイマ割り込み)                    | - 擬似ノンマスカブル              | $IL_2$            | FFFA <sub>H</sub> |      | 2  |

| 外  | 部  | INTO (3   | 外部割り込み0)                           | IMF=1, INT0EN=1          | $/$ $IL_3$        | FFF8 <sub>H</sub> |      | 3  |

|    |    |           | Reserved                           | $IMF \cdot EF_4 = 1$     | IL <sub>4</sub>   | FFF6 <sub>H</sub> |      | 4  |

| 外  | 部  | INT1 (3   | 外部割り込み1)                           | $IMF \cdot EF_5 = 1$     | $\mathrm{IL}_5$   | FFF4 <sub>H</sub> |      | 5  |

| 内  | 部  | INTTBT (: | タイムベースタイマ割り込み)                     | $IMF \cdot EF_6 = 1$     | $\mathrm{IL}_{6}$ | FFF2 <sub>H</sub> |      | 6  |

| 外  | 部  | INT2      | 外部割り込み2)                           | $IMF \cdot EF_7 = 1$     | $\mathrm{IL}_7$   | FFF0 <sub>H</sub> |      | 7  |

| 内  | 部  | INTTC1 (1 | 18ビットタイマカウンタ1割り込み)                 | $IMF \cdot EF_8 = 1$     | IL <sub>8</sub>   | FFEE <sub>H</sub> |      | 8  |

| 内  | 部  | INTRX (   | UART受信割り込み)                        | $IMF \cdot EF_9 = 1$     | IL <sub>9</sub>   | $FFEC_H$          |      | 9  |

| 内  | 部  | INTTX (   | UART送信割り込み)                        | $IMF \cdot EF_{10} = 1$  | ${ m IL}_{10}$    | FFEA <sub>H</sub> |      | 10 |

| 内  | 部  | INTTC3 (8 | <b>8</b> ビットタイマカウンタ <b>3</b> 割り込み) | IMF) EF <sub>11</sub> =1 | $IL_{11}$         | FFE8 <sub>H</sub> |      | 11 |

| 内  | 部  | INTTC4 (8 | 8ビットタイマカウンタ4割り込み)                  | $IMF \cdot EF_{12} = 1$  | ${ m IL}_{12}$    | FFE6 <sub>H</sub> |      | 12 |

| 内  | 部  | INTTC5 (8 | 8ビットタイマカウンタ5割り込み)                  | $IMF \cdot EF_{13} = 1$  | ${ m IL}_{13}$    | FFE4 <sub>H</sub> |      | 13 |

|    |    | <√7       | Reserved                           | $IMF \cdot EF_{14} = 1$  | $IL_{14}$         | FFE2 <sub>H</sub> |      | 14 |

| 外  | 部  | INT5      | 外部割り込み5)                           | $IMF \cdot EF_{15} = 1$  | ${ m IL}_{15}$    | FFE0 <sub>H</sub> | 低位   | 15 |

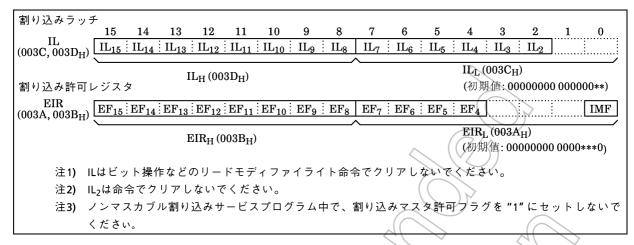

## (1) 割り込みラッチ (IL<sub>15</sub>~IL<sub>2</sub>)

割り込みラッチは、ソフトウエア割り込みを除いて各要因ごとに設けられており、割り込み要求の発生により"1"にセットされます。割り込み受け付けが許可されていると、CPUに割り込みの受け付けを要求します。割り込みが受け付けられた直後に割り込みラッチは"0"にクリアされます。リセット時、割り込みラッチはすべて"0"に初期化されます。

割り込みラッチは、SFR内の003C,003DH番地に割り付けられており、命令で個別にクリアすることができ (ただし、ビット操作命令や演算命令などのリードモディファイライト命令は使用できません)、プログラムで割り込み要求の取り消し/初期化ができます。ただし、 $IL_2$ は命令でクリアしないでください。なお、割り込みラッチを命令で直接セットすることはできません。また、割り込みラッチの内容を読み出すことができますので、割り込み要求のソフトウエアによるテストも可能です。

例1: 割り込みラッチのクリア

LDW (IL), 1110100000111111B

;  $\text{IL}_{12}$ ,  $\text{IL}_{10} \sim \text{IL}_6 \leftarrow 0$

例2: 割り込みラッチの読み出し

LD WA, (IL)

;  $W \leftarrow IL_H$ ,  $A \leftarrow IL_L$

例3: 割り込みラッチのテスト

TEST (IL).7

JR F, SSET

; IL7=1ならジャンプ

87CH29-35 2003-03-20

## (2) 割り込み許可レジスタ (EIR)

擬似ノンマスカブル割り込み (ソフトウエア割り込みとウォッチドッグタイマ割り込み) を除く割り込み要因に対して受け付けの許可/禁止を行うレジスタです。擬似ノンマスカブル割り込みは、割り込み許可レジスタの内容にかかわらず受け付けられます。ただし、擬似ノンマスカブル割り込み同士の多重化はできません。

割り込み許可レジスタは、割り込みマスタ許可フラグ(IMF)と割り込み個別許可フラグ(EF)で構成されています。割り込み許可レジスタは、SFR内の $003A_H$ ,  $003B_H$ 番地に割り付けられており、命令でリード/ライト(ビット操作命令などのリードモディファイライトも含む)できます。

### ① 割り込みマスタ許可フラグ (IMF)

すべてのマスカブル割り込みに対して受け付けの許可/禁止の制御を行うフラグです。"0" にクリアされていると、すべてのマスカブル割り込みの受け付けは禁止状態であり、"1" にセットされていると、割り込み受け付け許可状態です。

割り込みが受け付けられると割り込みマスタ許可フラグは"0"にクリアされ、そのあとのマスカブル割り込みの受け付けを一時的に禁止します。割り込みサービスプログラムを実行後、マスカブル割り込みリターン命令[RETI]により"1"にセットされ、再び受け付け許可状態となります。すなわち、すでに割り込み要求が来ている場合、[RETI]命令の実行直後から割り込み処理に入ります。

擬似ノンマスカブル割り込みの場合は、ノンマスカブル割り込みリターン命令[RETN] によりリターンします。この場合、割り込み受け付けの許可状態(IMF=1)で擬似ノンマスカブル割り込み処理に入ったときのみ、割り込みマスタ許可フラグは"1"にセットされます。ただし、割り込みサービスプログラム中で、割り込みマスタ許可フラグを"0"にクリアした場合は"0"のままです。

割り込みマスタ許可フラグは、 $\mathbf{EIR_L}$ ( $\mathbf{SFR}$ 内の $\mathbf{003A_H}$ 番地)のビット $\mathbf{0}$ に割り付けられており、命令でリード/ライトできます。通常、割り込みマスタ許可フラグのセット/クリアは、[ $\mathbf{EI}$ ]/[ $\mathbf{DI}$ ]命令で行います。なお、リセット時、割り込みマスタ許可フラグは" $\mathbf{0}$ "に初期化されます。

### ② 割り込み個別許可フラグ (EF<sub>15</sub>~EF<sub>5</sub>)

外部割り込み0を除く各マスカブル割り込み要因に対し、個々に割り込み受け付けの許可/禁止の指定を行うフラグです。割り込み個別許可フラグの該当ビットが"1"なら割り込み受け付けを許可し、"0"なら禁止します。

例1: 割り込みの個別許可とIMFのセット

LDW (EIR), 1010100010100001B;  $EF_{15}$ ,  $EF_{13}$ ,  $EF_{11}$ ,  $EF_{7}$ ,  $EF_{5}$ ,  $IMF \leftarrow 1$

例2: 割り込みの個別許可フラグのセット

SET (EIRH).4

;  $EF_{12}\leftarrow 1$

図1-23. 割り込みラッチ (IL), 割り込み許可レジスタ (EIR)

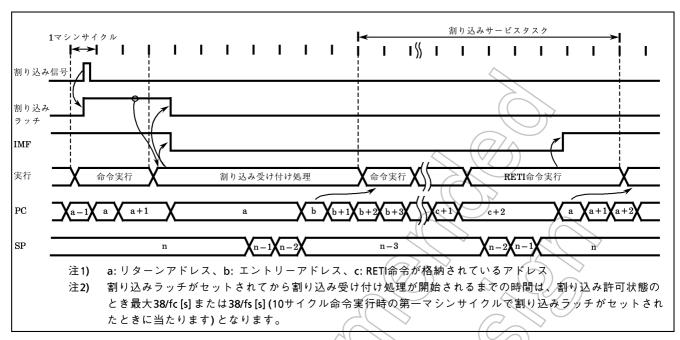

## 1.9.1 割り込み処理

割り込み要求は、割り込みが受け付けられるか、リセット動作または命令によって、割り込みラッチが"0"にクリアされるまで保持されます。割り込み受け付け処理は、実行中の命令が終了したあと、8マシンサイクル (4  $\mu$ s @ 8 MHz) を要して実行されます。割り込みサービスタスクは、割り込みリターン命令 [RETI] (マスカブル割り込みの場合)/[RETN] (擬似ノンマスカブル割り込みの場合)を実行して終了します。図1-24割り込み受け付け処理タイミングを示します。

## (1) 割り込み受け付け処理

割り込み受け付け処理は、次の動作を自動的に行います。

- ① 割り込みマスタ許可フラグ(IMF)を"0"にクリアし、そのあとのマスカブル割り込みの受け付けを一時的に禁止します。ノンマスカブル割り込み受け付けの場合は、そのあとのノンマスカブル割り込みの受け付けも一時的に禁止します。

- ② 受け付けた割り込み要因の割り込みラッチを"0"にクリアします。

- ③ プログラムカウシタ(PC) およびプログラム ステータス ワード(PSW) の内容をスタックに退避 します (PSW, PC $_{

m H}$ , PC $_{

m L}$ の順にプッシュダウンされます)。スタックポインタ (SP) は $_{

m SP}$  は $_{

m SP}$  によっます。

- ④ 割り込み要因に応じたベクタテーブルアドレスから割り込みサービスプログラムのエントリーアドレス(割り込みベクタ)を読み出し、プログラムカウンタにセットします。

- ⑤ 割り込みサービスプログラムのエントリーアドレスに格納されている命令の実行に移ります。

87CH29-37 2003-03-20

図1-24. 割り込み受け付け処理/割り込みリターン命令 タイミングチャート

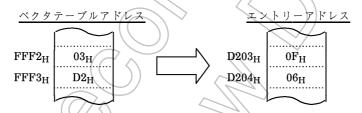

例: INTTBTの受け付け処理におけるベクタテーブルアドレスと割り込みサービスプログラムのエントリーアドレスの対応

割り込みサービス中に、その割り込み処理よりレベルの高いマスカブル割り込みが発生しても、割り込みマスタ許可フラグが"1"にセットされるまで受け付けられません。従って、多重割り込みを行う場合は、割り込みサービスプログラムの中で、割り込みマスタ許可フラグを"1"にセットします。その際、割り込み個別許可フラグにより、受け付けてよい割り込み要因を選択的に許可します。ただし、外部割り込みのは、割り込み個別許可フラグにより割り込み受け付け禁止ができませんので、必要なら外部割り込み制御レジスタ (INTOEN) により外部割り込み機能を禁止する (INTOEN=0の期間、割り込みラッチIL3はセットされませんので $\overline{\text{INTO}}$ 端子入力の立ち下がりエッジは検出できません)か、または、プログラムでソフトウエア的に割り込み処理を禁止します。

87CH29-38 2003-03-20

例1: 外部割り込み制御レジスタによる外部割り込み0の禁止

LD (EINTCR), 00000000B ; INT0EN $\leftarrow$ 0

例2: ソフトウエアによる外部割り込み0の割り込み処理禁止(割り込み処理禁止スイッチを $00F0_H$ 番 地のビット0とします)。

PINT0: TEST (00F0H).0

;  $(00F0_H)_0=1$ なら割り込み処理行わずに

リターン

JRS T, SINTO

RETI

SINTO: 割り込み処理

RETI

VINTO: DW PINTO

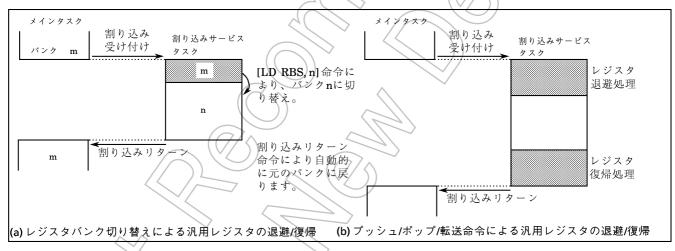

(2) 汎用レジスタ退避/復帰処理

割り込み受け付け処理で、プログラムカウンタとプログラムステータスワードは自動的にスタックに退避されますが、アキュムレータやそのほかのレジスタは自動的には退避されません。これらのレジスタ類の退避処理が必要な場合は、プログラムで行います。また、多重割り込みを行う場合、退避用のデータメモリ領域が重ならないようにする必要があります。

汎用レジスタの退避には、次の方法があります。

① レジスタバンク切り替えによる汎用レジスタの退避/復帰

使用していないレジスタバンクへ切り替えることで、高速に汎用レジスタを退避することができます。通常、バンク0はメインタスク用に、バンク1~15を各割り込みサービスタスクに割り当てます。データメモリの使用効率を上げるには、多重化されない割り込み要因に共通のバンクを割り当てます。

切り替えられたバンクは、割り込みリターン命令[RETI]/[RETN] の実行で自動的に復帰します。 従って、RBSを退避する必要はありません。

例: レジスタバンク切り替え

PINTxx: LD

RBS, n

; バンクnに切り替え (1μs @8MHz)

割り込み処理

RETI

; バンクの復帰とリターン

② プッシュ/ポップ命令による汎用レジスタの退避/復帰

特定のレジスタのみ退避する場合や同一の割り込み要因の多重化の場合には、プッシュ/ポップ命令により汎用レジスタの退避/復帰を行います。

例: プッシュ/ポップによるレジスタの退避/復帰

PINTxx: PUSH WA

; WAレジスタペアをスタックに退避

割り込み処理

POP WA

; WAレジスタペアをスタックから復帰

RETI

: リターン

87CH29-39 2003-03-20

③ 転送命令による汎用レジスタの退避/復帰

多重割り込みを行わない割り込み処理において、特定のレジスタのみ退避する場合は、データメモリとの転送命令により汎用レジスタの退避/復帰を行います。

例: データメモリとの転送命令によるレジスタの退避/復帰

PINTxx: LD (GSAVA), A

; Aレジスタの退避

割り込み処理

LD A, (GSAVA) ; Aレジスタの復帰

RETI ; 1) 9 -

図1-25. 割り込み処理における汎用レジスタの退避/復帰処理

87CH29-40 2003-03-20

### (3) 割り込みリターン

割り込みリターン命令は、次の動作を行います。

| [RETI] マスカブル割り込みリターン                                                          | [RETN] ノンマスカブル割り込みリターン                                                                                                              |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>① プログラムカウンタおよびプログラムス<br/>テータスワードの内容をスタックからそ<br/>れぞれリストアします。</li></ul> | <ul><li>① プログラムカウンタおよびプログラムステータスワードの内容をスタックからそれぞれリストアします。</li></ul>                                                                 |

| ② スタックポインタを3回インクリメントします。                                                      | ② スタックポインタを <b>3</b> 回インクリメントします。                                                                                                   |

| ③ 割り込みマスタ許可フラグを"1"にセットします。                                                    | ③ 割り込み許可状態でノンマスカブル割り<br>込みを受け付けた場合のみ割り込みマス<br>タ許可フラグを"1"にセットします。た<br>だし、割り込みサービスプログラム中<br>で、割り込みマスタ許可フラグを"0"に<br>クリアした場合は、"0"のままです。 |

割り込み要求は、実行中の命令の最終サイクルでサンプリングされます。従って、割り込みリターン命令の実行直後から次の割り込み処理を行うことができます。

注) 割り込み処理時間が、割り込み要求の発生時間よりも長いと、割り込みサービスタスクの実行のみ 行われ、メインタスクの実行が行われなくなります。

### 1.9.2 ソフトウエア割り込み (INTSW)

SWI命令を実行することにより、ノフトウエア割り込みが発生し直ちに割り込み処理に入ります(最優先割り込み)。ただし、すでにノンマスカブル割り込み処理に入っているときは、SWI命令を実行してもソフトウエア割り込みは発生せず、NOP命令と同一の動作を行います。

注) 開発ツールでは、SWI命令をソフトウエアブレークに使用できるように、ノンマスカブル割り込み処理中でも必ずソフトウエア割り込みが発生します。

SWI命令は、次に示すアドレスエラー検出またはデバッギング以外には使用しないでください。

#### ① アドレスエラー検出

**CPU**が何らかの原因(ノイズなど)により、メモリの存在しないアドレスから命令フェッチを行った場合、 $FF_H$ が読み込まれます。コード $FF_H$ は、SWI命令ですのでソフトウエア割り込みが発生し、これによりアドレスエラーの検出ができます。また、プログラムメモリの不使用領域をすべて $FF_H$ で埋めておくことで、アドレスエラー検出範囲がよりいっそう広がります。 なお、RAM領域 ( $0040\sim043F_H$ 番地) およびSFR領域( $0000\sim003F_H$ 番地) に対する命令フェッチのときは、アドレストラップリセットがかかります。

注) 7F80~7FFFH番地には、出荷テスト用ROMが内蔵されていますので、この領域からの命令フェッチの場合はFFHとなりません。

#### ② デバッギング

SWI命令をソフトウエアブレークポイント設定アドレスに置くことによって、デバッギング効率を 高めることができます。

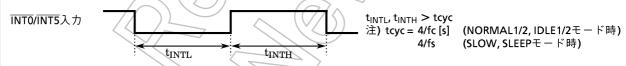

#### 1.9.3 外部割り込み

TMP87CH29/K29/M29には、4本の外部割り込み入力があり、うち2本はデジタルノイズ除去回路付き(一定時間未満のパルス入力をノイズとして除去します)となっています。

また、INT1,INT2端子は、エッジ選択可能です。なお、INTO/P10端子は、外部割り込み入力端子として使用するか入出力ポートとして使用するかの選択ができます。リセット時は、入力ポートとなります。

エッジの選択, ノイズ除去の制御 および INTO/P10端子の機能選択は、外部割り込み制御レジスタで行います。

| 要因   | 端 子 名 | 兼用端子     | 許 可 条 件                  | エッジ                         | デジタル ノイズ 除去回路                                                                     |

|------|-------|----------|--------------------------|-----------------------------|-----------------------------------------------------------------------------------|

| INT0 | ĪNT0  | P10      | IMF=1, INT0EN=1          | 立ち下がりエッジ                    | なし(ヒステリシス入力)                                                                      |

| INT1 | INT1  | P11      | IMF · EF <sub>5</sub> =1 | 立ち下がりエッジ<br>または<br>立ち上がりエッジ | 15/fe または 63/fc [s] 未満のパルスはノイズとして除去されます。<br>48/fe または 192/fc [s] 以上は確実に信号とみなされます。 |

| INT2 | INT2  | P12      | IMF · EF7=1              |                             | 7/fc[s] 未満のパルスはノイズとして除去されます。24/fc[s] 以上は確実に信号とみなされます。                             |

| INT5 | ĪNT5  | P20/STOP | $IMF \cdot EF_{15} = 1$  | 立ち下がりエッジ                    | なし(ヒステリシス入力)                                                                      |

表1-3. 外部割り込み

- 注1) SLOW/SLEEPモード時、ノイズ除去機能はオフします。なお、動作モード遷移中に入力されたパルスに対するノイ ズ除去時間は不定になります。

- 注2)  $\overline{\text{INTO}}$  および  $\overline{\text{INT5}}$ 端子への入力パルス幅は、"H", "L" レベルとも1マシンサイクル以上必要です。

- 注3) NORMAL 1/2またはIDLE 1/2 モード時、ノイズのない信号が外部割り込み端子に入力された場合、入力信号のエッジから割り込みラッチがセットされるまでの最大時間は次のとおりです。

- ① INT1 端子 49/fc [s] (INT1NC=1のとき), 193/fc [s] (INT1NC=0のとき)

- ② INT2 端子 25/fc [s]

- 注4) NTOEN = 0のとき、INTO端子入力の立ち下がりエッジが検出されても割り込みラッチIL3はセットされません。

- 注5) STOPモードでポート出力をハイインピーダンス指定 (OUTEN = 0) 時、ポート入力は内部で強制的に "L" レベルに固定されるため、ポートと兼用の外部割り込み入力 (INT5を除く) の割り込みラッチがセットされることがあります。 STOPモードでポート出力をハイインピーダンス指定にする場合、割り込み受け付けを一時禁止 (IMF = 0) にしてから STOPモードを起動し、STOPモード解除後に割り込みラッチをロード命令でクリアしてください。

例:STOPモードの起動

LD (SYSCR1), 01000000B ; OUTEN ← 0 (ハイインピーダンス指定)

DI ;  $IMF \leftarrow 0$

SET (SYSCR1). STOP ; STOP ← 1 (STOPモード起動)

LDW (IL), 1111111101010111B ; IL7, 5, 3 ← 0 (割り込みラッチのクリア)

EI ; IMF ← 1

87CH29-42 2003-03-20

| $\begin{array}{c} \rm EINTCR \\ (0037_{\rm H}) \end{array}$ | INT1 INTO                  | 0 INT2 ES        | INT1<br>ES (初期値: 00*0 000*)                                  |     |

|-------------------------------------------------------------|----------------------------|------------------|--------------------------------------------------------------|-----|

|                                                             | INT1NC INT1のノイズ除去時間の<br>選択 |                  | 0: 63/fc [s] 未満のパルスはノイズとして除去<br>1: 15/fc [s] 未満のパルスはノイズとして除去 |     |

|                                                             | INT0EN P10/ĪNT0の機能選択       |                  | 0: P10入出力ポート<br>1: INTO端子 (P10ポートは入力モードにしてください)              | R/W |

|                                                             | INT2ES<br>INT1ES           | INT2, INT1のエッジ選択 | 0: 立ち上がりエッジで割り込み要求発生<br>1: 立ち下がりエッジで割り込み要求発生                 |     |

注1) fc: 高周波クロック [Hz]、\*: Don't care

- 注2) 外部割り込み制御レジスタ (EINTCR) の設定/書き替えは、まず割り込みを禁止状態 (IMF = 0) にしてか ら外部割り込み制御レジスタを設定/書き替え、割り込みラッチをクリアした後、割り込み受け付けを

- 注3) INT2ESを、NORMAL1/2モード時に、外部割り込み入力信号のエッジを切り替える目的で書き替えた場 合には、書き替えてから8命令サイクル以上おいてから、外部割り込みラッチ (INT2) をクリアしてく ださい。SLOWモード時には、3命令サイクル必要です。

- INT1ESを書き替えたとき、NORMAL1/2モードの場合には、切り替えてから14命令サイクル 注4) (INT1NC=1のとき)または50命令サイクル (INT1NC=0のとき)おいてから、INT1の割り込みラッチをク リアしてください。SLOWモード時には、3命令サイクル必要です。

87CH29-43 2003-03-20

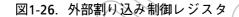

## 1.10 ウォッチドッグタイマ (WDT)

ウォッチドッグタイマは、ノイズなどの原因による誤動作(暴走)やデッドロック状態を速やかに検出し、正常な状態に戻すことを目的としたフェイルセーフ機能です。

ウォッチドッグタイマによる暴走検出信号は、リセット出力または擬似ノンマスカブル割り込み要求のいずれかにプログラムで選択することができます。ただし、選択は1回限りです。リセット解除時は、リセット出力に初期化されます。

なお、ウォッチドッグタイマを暴走検出用として使用しない場合、一定周期ごとに割り込みを発生するタイマとして利用できます。

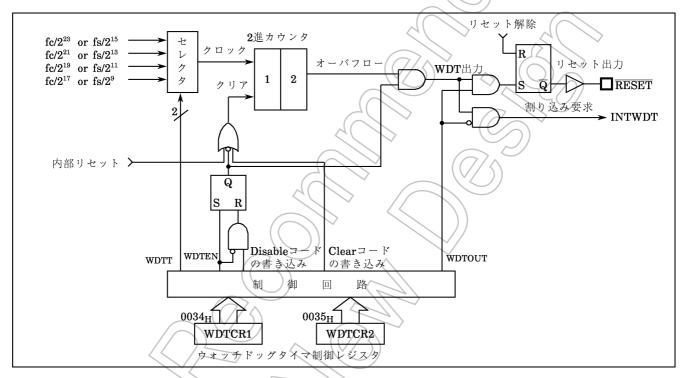

### 1.10.1 ウォッチドッグタイマの構成

図1-27 ウォッチドッグタイマの構成

87CH29-44 2003-03-20

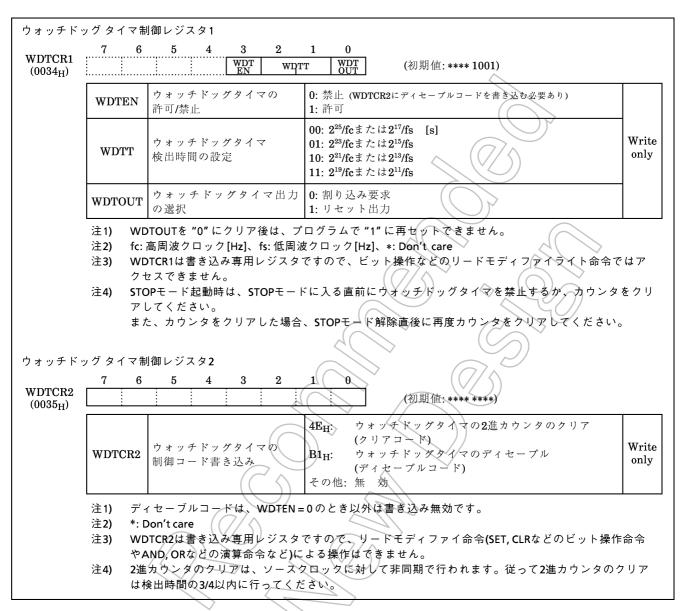

## 1.10.2 ウォッチドッグタイマの制御

ウォッチドッグタイマの制御レジスタを図1-28に示します。リセット解除後、ウォッチドッグタイマはイネーブルになります。

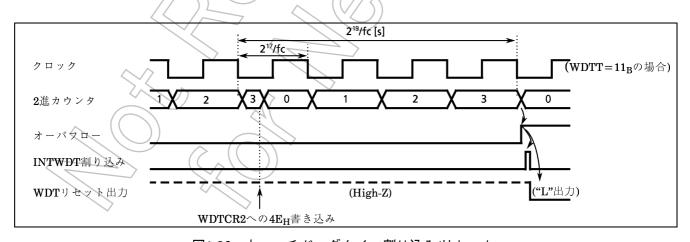

(1) ウォッチドッグタイマによる暴走検出の方法

CPUの暴走検出を行うには、次のようにします。

- ① 検出時間の設定、出力の選択 および 2進カウンタのクリア

- ② 設定した検出時間3/4以内ごとに2進カウンタのクリアを繰り返し行います。

- 注) 2進カウンタのクリアは、ソースクロックに対して非同期で行われます。従ってクリアタイミングによっては、検出時間が設定時間の3/4となる場合があります。

もし、何らかの原因で暴走またはデッドロック状態に陥り、2進カウンタのクリアが行われないと2 進カウンタのオーバフローでウォッチドッグタイマ出力がアクティブになります。このとき WDTOUT= "1" なら RESET 端子からリセット出力するとともに内蔵バードウエアをリセットします。また、WDTOUT= "0" なら、ウォッチドッグタイマ割り込み (INTWDT) を発生します。

なお、STOPモード(ウォーミングアップ中を含む)またはIDLEモード中ウォッチドッグタイマは、一時的にカウントアップ停止し、STOP/IDLEモード解除後、自動的に再起動(カウントアップ継続)します。

例: ウォッチドッグ タイマ検出時間を $2^{21}$ /fc [s] に設定し、暴走検出リセットを行う。

LD(WDTCR2), 4EH ;

2進カウンタのクリア

LD(WDTCR1), 00001101B ;

WDTT←10, WDTOUT←1

(WDTT変更直前直後は必ずクリアします)

LD(WDTCR2), 4EH

**, 2**進カウンタのクリア

WDT検出 時間3/4以内

LD(WDTCR2), 4EH

: **2**進カウンタのクリア

WDT検出 時間3/4以内

LD(WDTCR2), 4EH

: 2進カウンタのクリア

図1-28. ウォッチドッグ タイマ制御レジスタ

# (2) ウォッチドッグタイマのイネーブル

WDTEN (WDTCR1のビット3) を"1" にセットするとイネーブルになります。リセット時、WDTENは"1"に初期化されますので、リセット解除後ウォッチドッグタイマは直ちに動作します。

## (3) ウォッチドッグ タイマのディセーブル

WDTEN (WDTCR1のビット3) を "0" にクリア後、WDTCR2にディセーブルコード ( $B1_H$ ) を書き込むことによりディセーブルになります。なお、逆にWDTCR2にディセーブルコードを書き込んだ後、WDTENを "0" にクリアしてもディセーブルになりません。ディセーブル中は、ウォッチドッグタイマの2進カウンタはクリアされています。

例: ウォッチドッグタイマのディセーブル

LDW (WDTCR1), 0B101H ; WDTEN←0, WDTCR2←disable code

87CH29-46 2003-03-20

|                                                | 動作モード                                                                                |                                           | 検出                  | 時間                |

|------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------|---------------------|-------------------|

| NORMAL1                                        | NORMAL2                                                                              | SLOW                                      | fc = 8 MHz          | fs=32.768 kHz時    |

| 2 <sup>25</sup> /fc [s]<br>2 <sup>23</sup> /fc | 2 <sup>25</sup> /fc, 2 <sup>17</sup> /fs<br>2 <sup>23</sup> /fc, 2 <sup>15</sup> /fs | $2^{17}/\mathrm{fs}$ $2^{15}/\mathrm{fs}$ | 4.194 s<br>1.048 s  | 4 s               |

| $2^{21}/\mathrm{fc}$                           | 2 <sup>21</sup> /fc, 2 <sup>13</sup> /fs                                             |                                           | $262.1~\mathrm{ms}$ | $250~\mathrm{ms}$ |

| $2^{19}/{ m fc}$                               | 2 <sup>19</sup> /fc, 2 <sup>11</sup> /fs                                             |                                           | 65.5 ms             | 62,5 ms           |

表1-4. ウォッチドッグタイマ検出時間

## 1.10.3 ウォッチドッグタイマ割り込み (INTWDT)

擬似ノンマスカブル割り込みで、割り込み許可レジスタの内容にかかわらず割り込みを受け付けます。ただし、すでにウォッチドッグタイマ割り込み中もしくはソフトウエア割り込み中であれば、それらの処理が終了(RETN命令の実行終了)するまで受け付けは待たされます。

なお、ウォッチドッグタイマ出力をWDTOUTにより割り込み要因とする前にスタックポインタを 設定してください。

例: ウォッチドッグタイマ割り込みの設定例

LD SP, 023FH

; SPの設定

LD (WDTCR1), 00001000B

WDTOUT←0

1.10.4 ウォッチドッグタイマリセット

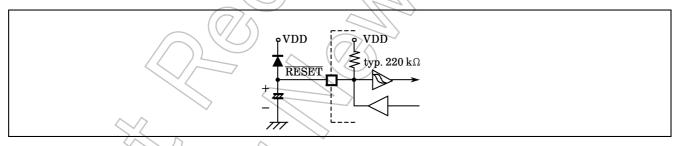

RESET端子より "L" レベルを出力するとともに内蔵ハードウエアをリセットします。リセット時間は、12/fc [s] (1.5  $\mu$ s @ 8 MHz) です。RESET端子は、プルアップ抵抗付きのシンクオープンドレイン入出力です。

注) SLOWモードでウォッチングタイマリセットが発生した場合も、高周波クロックが発振しますので、リセット時間は12/fc[s]となります。ただし、高周波クロックの発振開始時に発振周波数にゆらぎがある場合は、リセット時間は誤差を含むことになり、概略値としてとらえてください。

図1-29. ウォッチドッグタイマ割り込み/リセット

87CH29-47 2003-03-20

## 1.11 リセット回路

TMP87CH29/K29/M29には外部リセット入力, アドレストラップ リセット, ウォッチドッグタイマリセット, システムクロック リセットの4種類のリセット発生手段があります。表1-5にリセット動作による内蔵ハードウエアの初期化を示します。電源投入時、内部要因リセット回路(ウォッチドッグタイマリセット, アドレストラップリセットおよびシステムクロックリセット) は初期化されません。従って、電源投入時に $\overline{RESET}$ 端子出力が12/fc [s] (1.5  $\mu$ s @ 8 MHz) "L" レベルになることがあります。

| 内蔵ハードウエ       | ア     | 初 期 値                                                           | 内蔵ハードウエア              | 初 期 値               |

|---------------|-------|-----------------------------------------------------------------|-----------------------|---------------------|

| プログラムカウンタ     | (PC)  | $(\mathrm{FFFF}_{\mathrm{H}})\cdot(\mathrm{FFFE}_{\mathrm{H}})$ | タイミング ジェネレータの<br>デバイダ | 0                   |

| レジスタバンクセレクタ   | (RBS) | 0                                                               |                       |                     |

| ジャンプ ステータスフラグ | (JF)  | 1                                                               | ウォッチドッグ タイマ           | イネーブル               |

| 割り込みマスタ許可フラグ  | (IMF) | 0                                                               | 入出力ポートの出力ラッチ          | 各入出力ポートの説<br>明箇所を参照 |

| 割り込み個別許可フラグ   | (EF)  | 0                                                               |                       | 各制御レジスタの説           |

| 割り込みラッチ       | (IL)  | 0                                                               | 制御レジスタ                | 明箇所を参照              |

表1-5. リセット動作による内蔵ハードウエアの初期化

## 1.11.1 外部リセット入力

電源電圧が動作電圧範囲内にあり、発振が安定している条件のもとで最小3命令サイクル以上の間 RESET端子を"L"レベルに保つと、リセットがかかり内部状態が初期化されます。

**RESET**端子入力が "H" レベルに立ち上がるとリセット動作は解除され、**FFFE**, **FFFF**H番地に格納されたベクタアドレスからプログラムの実行を開始します。

RESET端子はプルアップ抵抗付きのヒステリシス入力となっており、コンデンサおよびダイオードを外付けすることにより簡易型パワーオンリセットを行うことができます。

図1-30. 簡易型パワーオンリセット回路

87CH29-48 2003-03-20

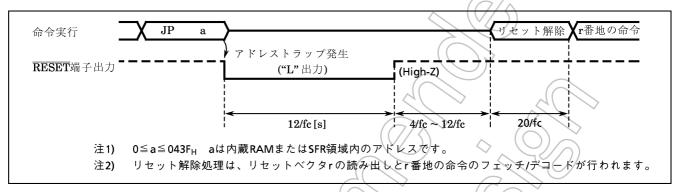

### 1.11.2 アドレストラップ リセット

**CPU**が何らかの原因(ノイズなど)により暴走していることを検出し、正常な状態に戻すことを目的としたフェイルセーフ機能の1つにアドレストラップリセットがあります。アドレストラップリセットとは、**SFR**および**RAM**領域から命令をフェッチしようとすると内部リセットを発生し、**RESET**端子よりリセット信号("L"レベル)が出力される機能です。リセット時間は、12/fc [s](1.5  $\mu$ s @ 8 MHz)です。

図1-31. アドレストラップリセット

### 1.11.3 ウォッチドッグタイマ リセット

『1.10ウォッチドッグタイマ』をご参照ください。

## 1.11.4 システムクロック リセット

XEN, XTEN (SYSCR2 のビット7,6) をともに"0"にクリアすると高周波, 低周波発振が停止し、MCUがデッドロック状態に陥ります。これを防ぐため、XEN=XTEN=0を検出すると自動的にリセット信号を発生し発振を継続させます。リセット信号は、RESET 端子より出力されます。リセット時間は、12/fc [s] (1.5  $\mu$ s @ 8 MHz) です。

87CH29-49 2003-03-20

#### 2. 周辺ハードウエア機能

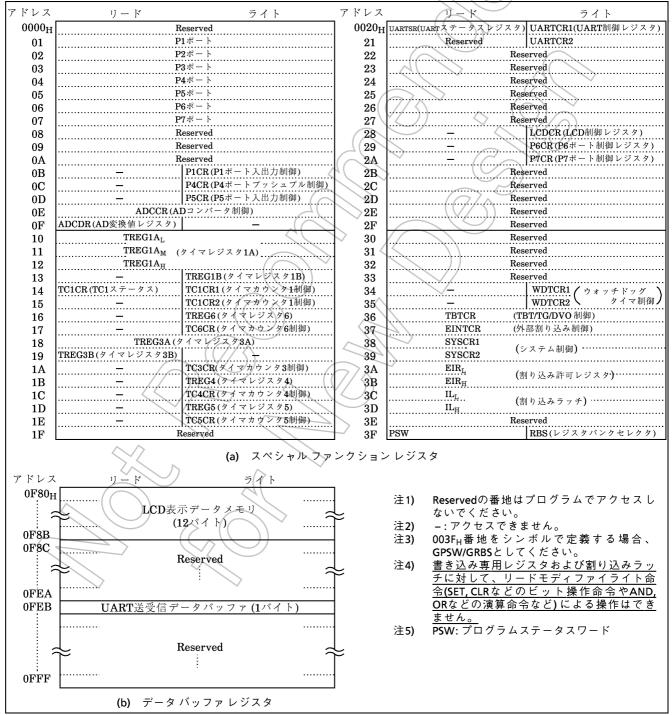

2.1 スペシャルファンクションレジスタ (SFR) とデータバッファレジスタ (DBR)

TLCS-870シリーズは、メモリマップドI/O方式で、周辺ハードウエアの制御/データ転送はすべてスペシャル ファンクション レジスタ (SFR) またはデータ バッファ レジスタ (DBR) をとおして行われます。

SFRは0000~003F<sub>H</sub>番地に、DBRは0F80~0FFF<sub>H</sub>番地にマッピングされています。図2-1にTMP87CH29/K29/M29のSFR、DBRの一覧を示します。

図2-1. SFR & DBR

87CH29-50 2003-03-20

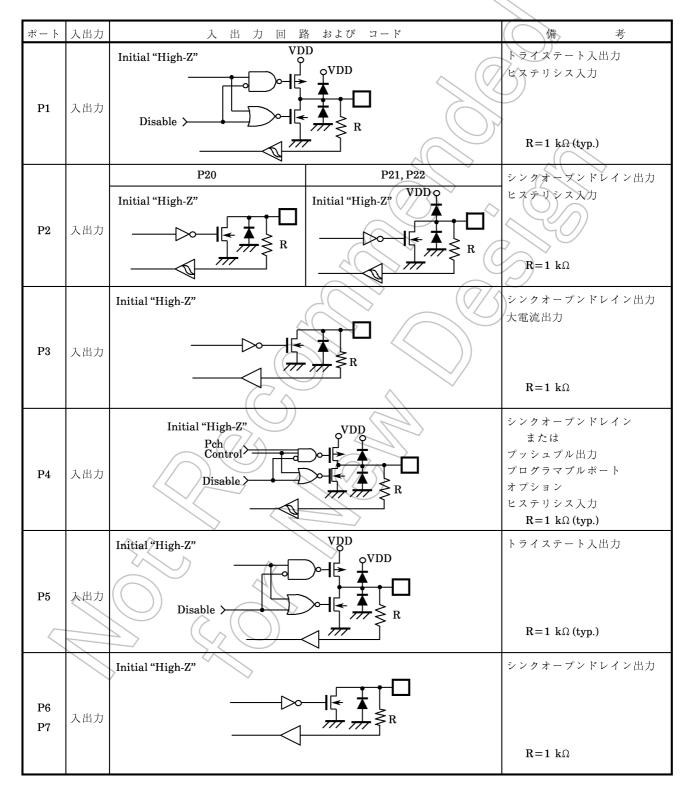

## 2.2 入出力ポート

**TMP87CH29/K29/M29**は、7ポート43端子の入出力ポートを内蔵しています。

- ① P1ポート: 8ビット入出力ポート (外部割り込み入力,デバイダ出力と兼用)

- ② P2ポート; 3ビット入出力ポート (低周波発振子接続端子, 外部割り込み入力, STOPモード解除信号入力と兼用)

- ③ P3ポート: 3ビット入出力ポート (タイマカウンタ出力と兼用)

- ④ P4ポート; 8ビット入出力ポート (UART入出力, タイマカウンタ入出力と兼用)

- ⑤ P5ポート: 5ビット入出力ポート (タイマカウンタ入力と兼用)

- ⑥ P6ポート: 8ビット入出力ポート (セグメント出力と兼用)

- ⑦ P7ポート: 8ビット入出力ポート (セグメント出力と兼用)

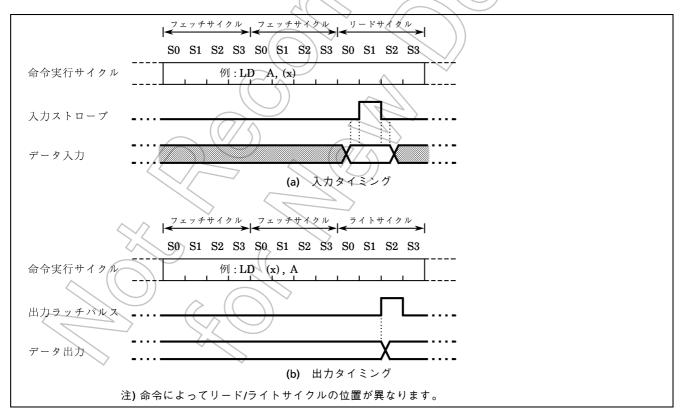

すべての出力ポートは、ラッチを内蔵していますので、出力データはラッチにより保持されます。 すべての入力ポートにはラッチがありませんので、外部から入力データを読み取るまでは外部でデー タを保持しておくか、複数回読み取ってから処理することが望まれます。図2-2に入出力タイミングを 示します。

入出力ポートから外部データを読み込むタイミングは、命令実行におけるリードサイクルの**S1**ステートです。外部からはこのタイミングを認識できませんので、チャタリングなどの過渡的な入力データはプログラムで対処する必要があります。人出力ポートへデータを出力するタイミングは、命令実行におけるライトサイクルの**S2**ステートです。

図2-2. 入出力タイミング (例)

プログラマブル入出力ポートを除く入出力ポートに対して、ポートからのリードを行った場合、端 子入力値を読み込むか出力ラッチの内容を読み込むかは、下記のとおり命令によって異なります。

87CH29-51 2003-03-20

### (1) 出力ラッチの内容を読み込む命令

- ① XCH r, (src)

- ② SET/CLR/CPL (src).b

- ③ SET/CLR/CPL (pp).g

- 4 LD (src).b, CF

- ⑤ LD (pp).b,CF

- 6 ADD/ADDC/SUB/SUBB/AND/OR/XOR (src), n

- ⑦ ADD/ADDC/SUB/SUBB/AND/OR/XOR (src), (HL) 命令の (src) 側

### (2) 端子入力値を読み込む命令

上記以外の命令およびADD/ADDC/SUB/SUBB/AND/OR/XOR (src), (HL) 命令の (HL) 側

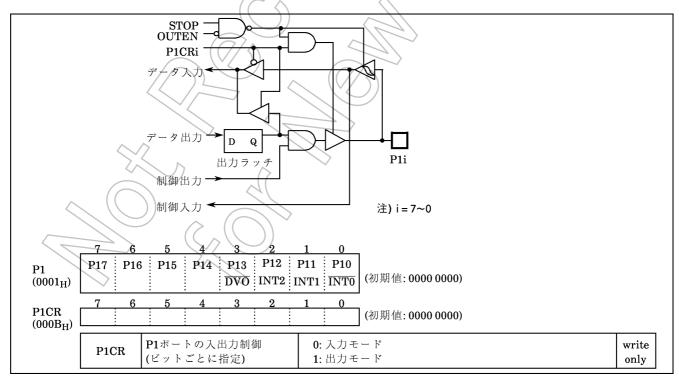

## 2.2.1 P1 (P17~P10) ポート

**P1**ポートは、1ビット単位で入出力の指定ができる8ビット入出力ポートです。入出力の指定は、**P1**ポート入出力制御レジスタ (**P1CR**) によって行います。サセット時、**P1CR**は"0"に 初期化され、**P1**ポートは入力モードとなります。また、**P1**ポート出力ラッチは"0"に初期化されます。

P1ポートは、外部割り込み入力、デバイダ出力と兼用になっています。これらの機能ピンとして使用する場合、入力ピンは入力モードに設定します。出力ピンはあらかじめ出力ラッチを"1"にセットし、出力モードに設定します。なお、P11,P12端子は、外部割り込み入力または入力ポートとして使用されることを推奨します(出力ポートとして使用すると立ち上がりまたは立ち下がりエッジで割り込みラッチがセットされます)。P10端子は、外部割り込み制御レジスタ(INTOEN)により入出力ポートとして使用するか外部割り込み入力として使用するかの選択ができます。リセット時、P10端子は入力ポートとなります。

図2-3. P1ポートとP1ポート入出力制御レジスタ

87CH29-52 2003-03-20

例: P17, P16を出力ポートに、P15, P14を入力ポートに、そのほかを機能ピンに設定し、P17ピンは "1"に、P16ピンは "0"を出力します。

LD (EINTCR), 01000000B ; INT0EN $\leftarrow$ 1

LD (P1), 101111111B ;  $P17 \leftarrow 1$ ,  $P16 \leftarrow 0$ ,  $P13 \leftarrow 1$

LD (P1CR), 11001000B

注1) 入力モードに設定されているポートは、端子入力の状態を読み込みますので、入力/出力を混在させて使用する場合、入力モードに設定されているポートの出力ラッチの内容は、ビット操作命令の実行により書き替わることがあります。

注2) P1CRは書き込み専用レジスタですのでリードモディファイライト命令(SET, CLRなどのビット操作命令やAND, ORなどの演算命令など)による操作はできません。

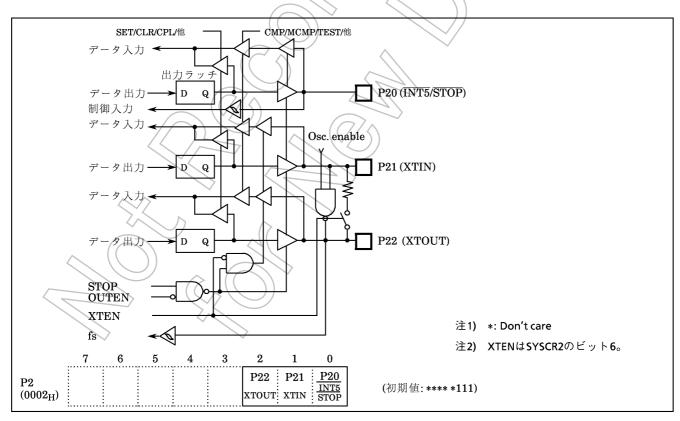

### 2.2.2 P2 (P22~P20) ポート

**P2**ポートは、**3**ビットの入出力ポートで、外部割り込み入力、**STOP**モード解除信号入力、低周波発振子接続端子と兼用になっています。これらの機能端子としてまたは入力ポートとして用いる場合は、出力ラッチを"1"にセットします(リセット時、出力ラッチは"1"に初期化されます)。

デュアルクロックモードで動作させる場合は、**P21 (XTIN)**, **P22 (XTOUT)** 端子には、低周波発振子 **(32.768 kHz)** を接続します。シングルクロックモードで動作させる場合、**P21**, **P22**端子は、通常の入出力ポートとして使用できます。

**P20**端子は外部割り込み入力, **STOP**モード解除信号入力, 入力ポートとして使用されることを推奨します (出力ポートとして使用すると立ち下がりエッジで割り込みラッチがセットされます)。

P2ポートに対してリード命令を実行した場合、ビット7~3は不定値が読み込まれます。

図2-4. P2ポート

87CH29-53 2003-03-20

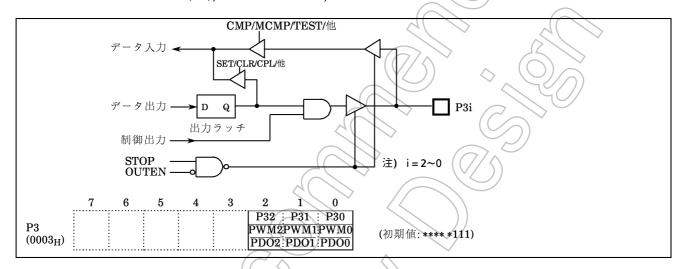

### 2.2.3 P3 (P32~P30) ポート

P3ポートは、3ビットの汎用入出力ポートで、タイマカウンタ出力と兼用です。P30, P31, P32がそれぞれ $\overline{PWM0}/\overline{PD00}$ ,  $\overline{PWM1}/\overline{PD01}$ ,  $\overline{PWM2}/\overline{PD02}$ 出力と兼用となっており、この3端子は大電流出力可能でLEDを直接駆動することができます。入力ポートまたはタイマカウンタ出力として使用する場合は出力ラッチを"1"にセットします (リセット時、出力ラッチは"1"に初期化されます)。

**例1: P3**ポートに即値 "**FA**<sub>H</sub>" を出力

LD (P3), 0FAH

;  $P3 \leftarrow FA_H$

例2: P3ポートの下位3ビット (P32~P30) の出力を反転する。

XOR (P3), 00000111B ;  $P32 \sim P30 \leftarrow \overline{P32} \sim \overline{P30}$

図2-5. P3ポート

87CH29-54 2003-03-20

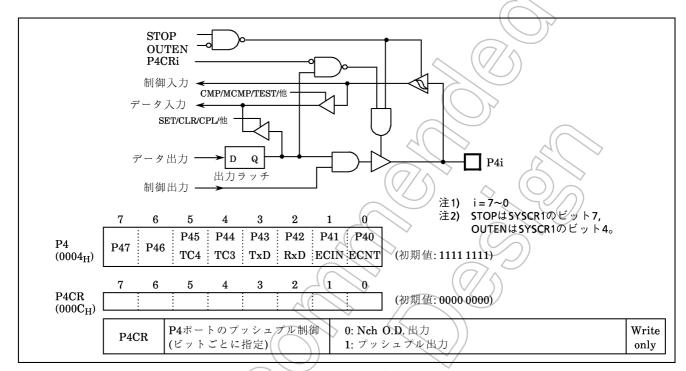

### 2.2.4 P4 (P47~P40) ポート

P4ポートは、1ビット単位で入出力の指定ができる8ビット汎用入出力ポートです。出力回路の指定は、P4ポート出力制御レジスタ (P4CR)によって行います。リセット時、P4CRは"0"に初期化され、P4ポートはNch O.D出力となります。また、P4ポート出力ラッチは"1"に初期化されます。

図2-6. P4ポートとP4ポート出力制御レジスタ

注) P4CRは書き込み専用レジスタですのでリードモディファイライト命令 (SET, CLRなどのビット 操作命令やAND, ORなどの演算命令など)による操作はできません。

87CH29-55 2003-03-20

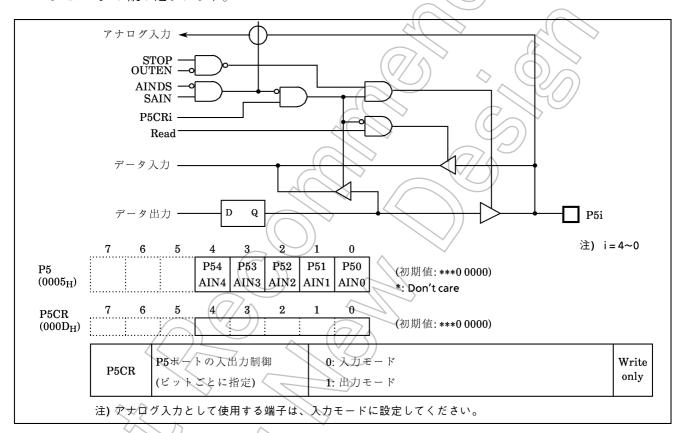

#### 2.2.5 P5 (P54~P50) ポート

P5ポートは、5ビットの入出力ポートでアナログ入力と兼用です。入出力の指定は、P5ポート入出力兼用レジスタ (P5CR) と AINDS (ADCCRのビット4) によって行います。 リセット時、P5CRは "0" にセットされ、AINDSは "0" にクリアされますので、P5ポートはアナログ入力となります。また、P5ポートの出力ラッチはリセット時 "0" に初期化されます。

なお、**P5CR**は書き込み専用レジスタです。アナログ入力として使用しない**P5**ポートは入出力ポートとして使用できますが、**AD**変換中は精度を保つ意味で出力命令は行わないようにしてください。

**AD**コンバータを使用している時**P5**ポートに対して入力命令を実行した場合、アナログ入力を選択している端子は"0"が読み込まれ、アナログ入力を選択していない端子は、端子の入力レベルにより"1"または"0"が読み込まれます。

図2-7. P5ポートとP5ポート入出力制御レジスタ

- 注1) 入力モードに設定されているポートは、端子入力の状態を読み込みますので、入力/出力モード を混在させて使用する場合、入力モードに設定されているポートの出力ラッチの内容は、ビット操作命令の実行により書き替わることがあります。出力モードに設定した端子は出力ラッチ の値が読み込まれます。

- 注2) P5CRは書き込み専用レジスタですのでリードモディファイライト命令 (SET, CLRなどのビット 操作命令やAND, ORなどの演算命令など) による操作はできません。

87CH29-56 2003-03-20

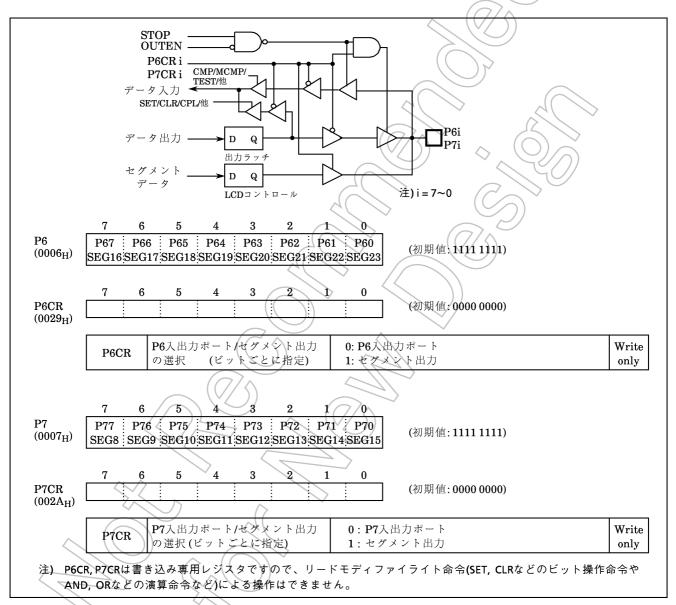

### 2.2.6 P6 (P67~P60), P7 (P77~P70) ポート

**P6**, **P7**ポートは、**8**ビットの入出力ポートで、**LCD**ドライバのセグメント出力と兼用です。入出力ポートとして使用するかセグメント出力として使用するかの指定は、各ポート制御レジスタ (**P6CR**, **P7CR**)によって行います。リセット時、各ポート制御レジスタは"0"にクリアされ、各ポートは入出力ポートとなります。入力ポートとして使用する場合は出力ラッチを"1"にセットします。リセット時、各ポートの出力ラッチは"1"に初期化されます。

図2-8. P6, P7ポートとP6, P7ポート制御レジスタ

例: P6ポートの上位2ビットとP7ポートの下位2ビットをセグメント出力に、そのほかを入出力ポートに設定します。

- LD (P6CR), 11000000B

- LD (P7CR), 00000011B

87CH29-57 2003-03-20

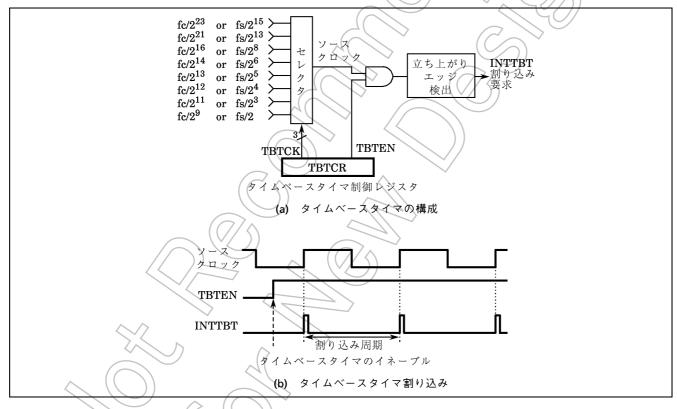

#### 2.3 タイムベース タイマ (TBT)

タイムベースタイマは、キースキャンやダイナミック表示処理などの基準時間生成用タイマで一定期ごとにタイムベースタイマ割り込み (INTTBT) を発生します。

タイムベースタイマ割り込みは、タイムベースタイマをイネーブルにした後、ソースクロック (タイミングジェネレータのデバイダ出力をTBTCKで選択) の最初の立ち上がりから発生します。なお、デバイダはプログラムでクリアされませんので、最初の割り込みに限り設定した割り込み周期よりも早く割り込みが発生することがあります (図2-9 (b) 参照)。

割り込み周波数の選択は、タイムベースタイマがディセーブルの状態で行ってください (イネーブル 状態からディセーブルにする際も割り込み周波数の設定を変更しないでください)。なお、周波数の選択とイネーブルを同時にすることはできます。

例: タイムベースタイマ割り込み周波数をfc/216 [Hz] にセットし、割り込みを許可します。

LD (TBTCR), 00001010B SET (EIRL). 6

図2-9. タイムベースタイマ

87CH29-58 2003-03-20

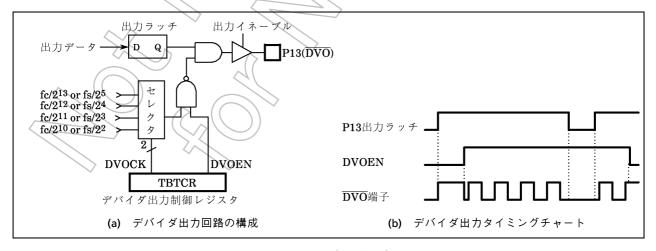

2 6 5 4 3 1 0 TBTCR (DVOEN) (DVOCK) (DV7CK) TBTEN TBTCK (初期値: 0\*\*0 0\*\*\*)  $(0036_{\rm H})$ タイムベースタイマ の許可/ 0: ディセーブル TBTEN 1: イネーブル 禁止 000:  $fc/2^{23}$   $\sharp$   $\hbar$   $\sharp$   $\hbar$ Write 010:  $fc/2^{16}$  \$\pi t \text{ts}/2^8\$ only 011:  $fc/2^{14}$  \$\pi t t if  $fs/2^6$ タイムベースタイマ割り込 TBTCK 100:  $fc/2^{13}$  または  $fs/2^5$ み周波数の選択 101:  $fc/2^{12}$  または  $fs/2^4$ 110:  $fc/2^{11}$  または  $fs/2^3$ 111: fc/2<sup>9</sup> または fs/2 注1) fc: 高周波クロック [Hz]、fs: 低周波クロック [Hz]、\*: Don't care 注2) TBTCRは書き込み専用レジスタですので、ビット操作などのリードモディファイライト命令ではアクセ スできません。

図2-10. タイムベースタイマ制御レジスタ

表2-1. タイムベースタイマ割り込み周波数

|       |                   |                   |                    | _ ~       | / /            |  |  |

|-------|-------------------|-------------------|--------------------|-----------|----------------|--|--|

| твтск | NORMAL1/2, I      | DLE1/2モード         | SLOW, SLEEP = - F  | 割り込み周波数   |                |  |  |

| IBICK | DV7CK = 0         | DV7CK=1           | SLOW, SLEEF C      | fc=8 MHz時 | fs=32.768 kHz時 |  |  |

| 000   | $fc/2^{23}$       | $fs/2^{15}$       | fs/2 <sup>15</sup> | 0.95 Hz   | 1 Hz           |  |  |

| 001   | $ m fc/2^{21}$    | $fs/2^{13}$       | $fs/2^{13}$        | 3.81      | 4              |  |  |

| 010   | $fc/2^{16}$       | $fs/2^8$          |                    | 122,07    | 128            |  |  |

| 011   | $fc/2^{14}$       | $\mathrm{fs}/2^6$ | ))) –              | 488.28    | 512            |  |  |

| 100   | $fc/2^{13}$       | $fs/2^5$          |                    | 976.56    | 1024           |  |  |

| 101   | $fc/2^{12}$       | $fs/2^4$          | - \                | 1953.12   | 2048           |  |  |

| 110   | $fc/2^{11}$       | fs/2 <sup>3</sup> | - ~ \\             | 3906.25   | 4096           |  |  |

| 111   | fc/2 <sup>9</sup> | fs/2              | - (2)              | 15625     | 16384          |  |  |

87CH29-59 2003-03-20

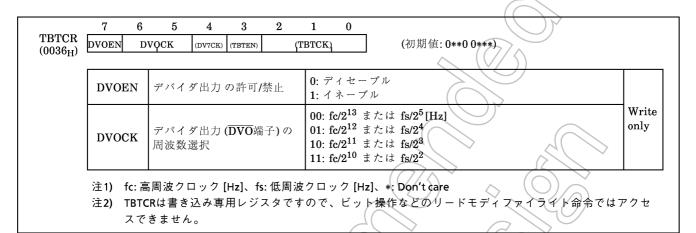

## 2.4 デバイダ出力 (DVO)

タイミング ジェネレータのデバイダによってデューティ50%のパルスを出力することができ、ブザーなどの駆動に利用できます。デバイダ出力は、P13 ( $\overline{DVO}$ ) 端子から出力されます。なお、P13ポートは出力ラッチを"1"にセットしたあと出力モードに設定します。

図2-11. デバイダ出力制御レジスタ

例: 1kHzのパルスを出力 (fc=8 MHz時)。

SET (P1).3

**; P13**出力ラッチ**←1**

LD (P1CR), 00001000B

; **P13**を出力モードに設定

LD (TBTCR), 10000000B

DVOEN←1, DVOCK←00

表2-2. デバイダ出力の周波数

| DVOCK | デバイダ出力の周波数                               | fc=4.194304 MHz時 | fc=8 MHz時   | fs=32.768 kHz時 |

|-------|------------------------------------------|------------------|-------------|----------------|

| 00    | fc/2 <sup>13</sup> または fs/2 <sup>5</sup> | 0.512 [kHz]      | 0.976 [kHz] | 1.024 [kHz]    |

| 01    | $fc/2^{12}$ $fs/2^4$                     | 1.024            | 1.953       | 2.048          |

| 10    | $fc/2^{11}$ $fs/2^3$                     | 2.048            | 3.906       | 4.096          |

| 11    | $fc/2^{10}$ $fs/2^2$                     | 4.096            | 7.812       | 8.192          |

図2-12. デバイダ出力

87CH29-60 2003-03-20

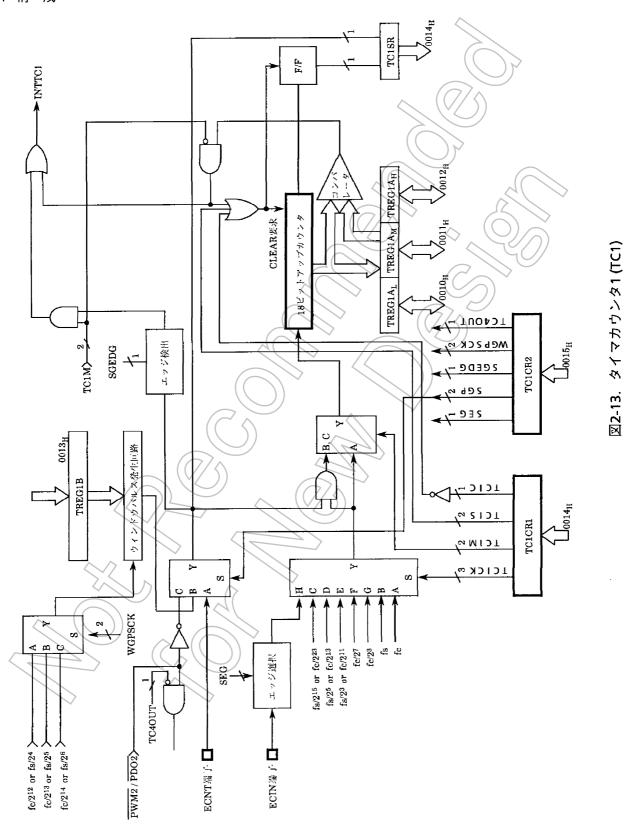

## 2.5 18ビットタイマカウンタ1 (TC1)

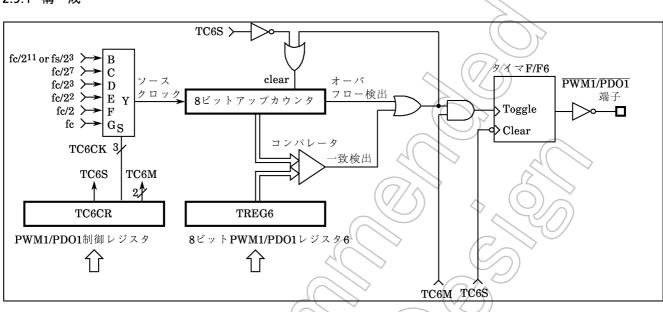

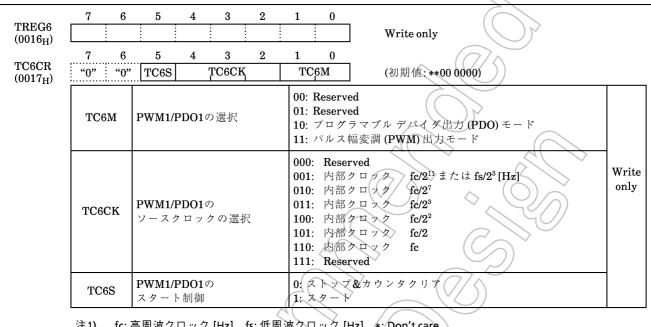

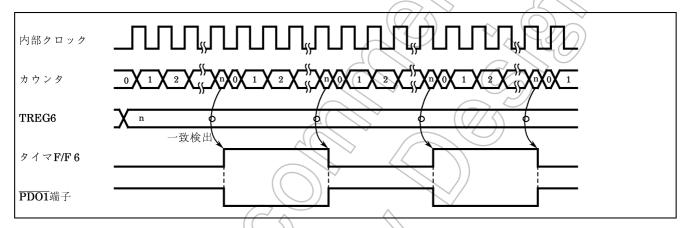

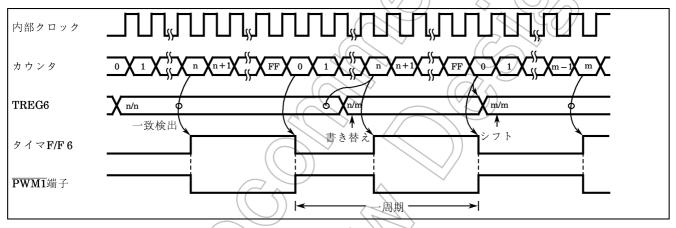

## 2.5.1 構 成

87CH29-61 2003-03-20

## 2.5.2 制 御

タイマカウンタ1は、タイマカウンタ1制御レジスタ (TC1CR1/TC1CR2), 18ビットタイマレジスタ (TREG1A) および8ビットの内部ウィンドウゲートパルス設定レジスタ (TREG1B) で制御されます。

| タイマ                           | レジス                | タ (社                     | 切期値             | : ** ***                                                                                                    | * ****)                                       |                                                    |                                                                                                                                                      |                            |                                           |                                                    |                                      |                                                                           |                          |                                                                                |                                 |             |                    |

|-------------------------------|--------------------|--------------------------|-----------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------|----------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------|---------------------------------|-------------|--------------------|

| _                             | 17                 | 16                       | 15              | 14                                                                                                          | 13                                            | 12                                                 | 11                                                                                                                                                   | 10                         | 9                                         | 8                                                  | 7                                    | 6                                                                         | 5                        | 4 3                                                                            | 2                               | 1           | 0                  |

| TF                            | REG1A <sub>H</sub> | (0012 <sub>H</sub> )     |                 |                                                                                                             | TF                                            | EG1A                                               | <sub>M</sub> (0011 <sub>վ</sub>                                                                                                                      | <sub>H</sub> )             |                                           | 1                                                  | <u> </u>                             |                                                                           | T                        | $ m REG1A_L$ (001                                                              | 0 <sub>H</sub> )                |             |                    |

| TREG1<br>(0010 <sub>H</sub>   |                    | <sub>[</sub> , 0012      | <sub>H,</sub> ) |                                                                                                             |                                               |                                                    |                                                                                                                                                      |                            |                                           |                                                    |                                      |                                                                           |                          |                                                                                | Read/W                          | Vrite       |                    |

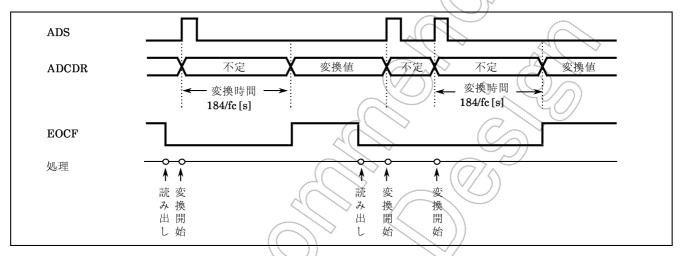

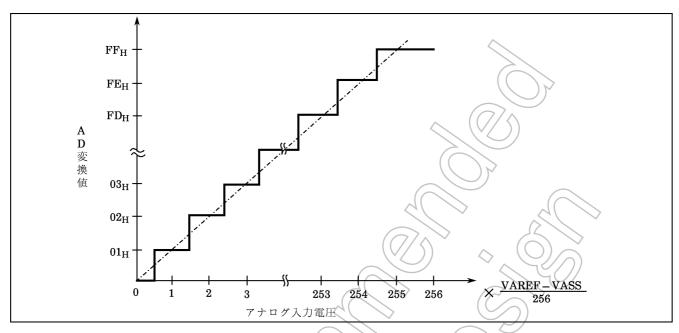

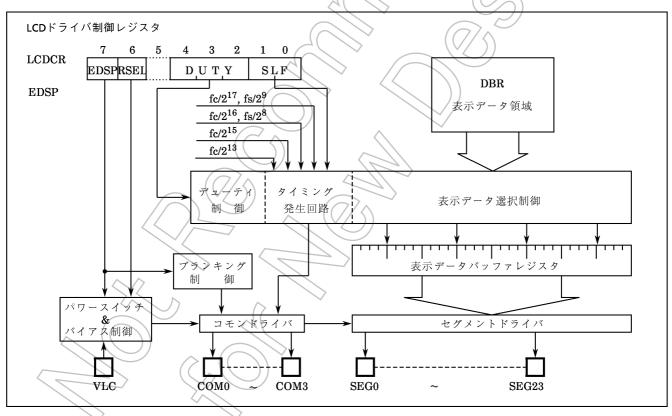

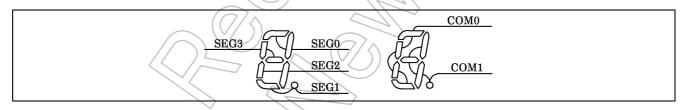

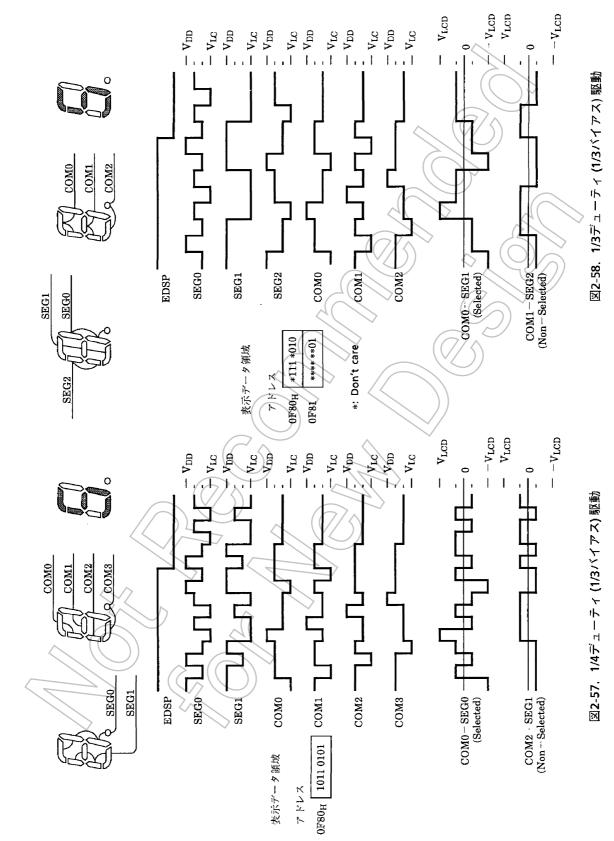

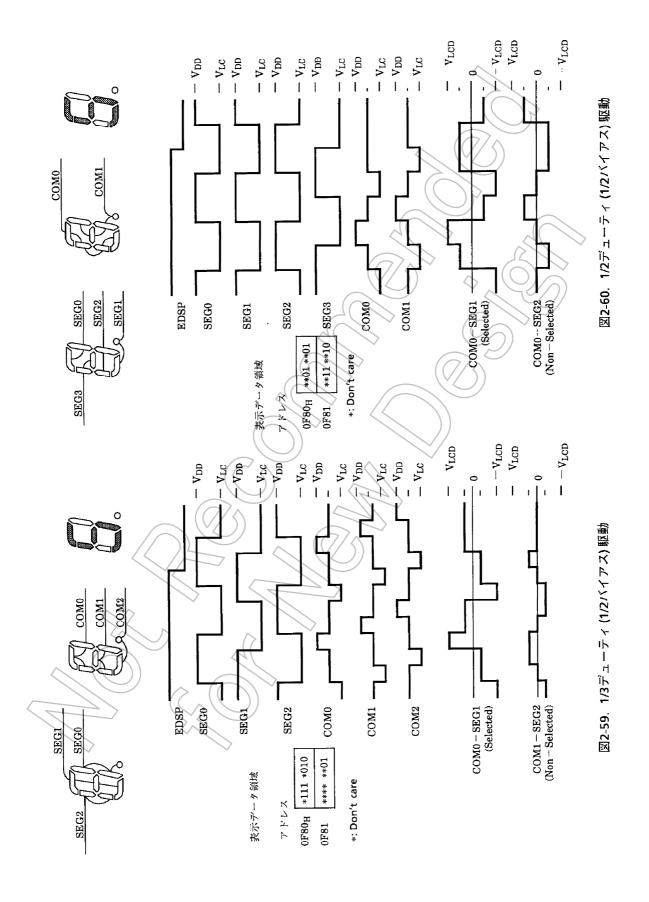

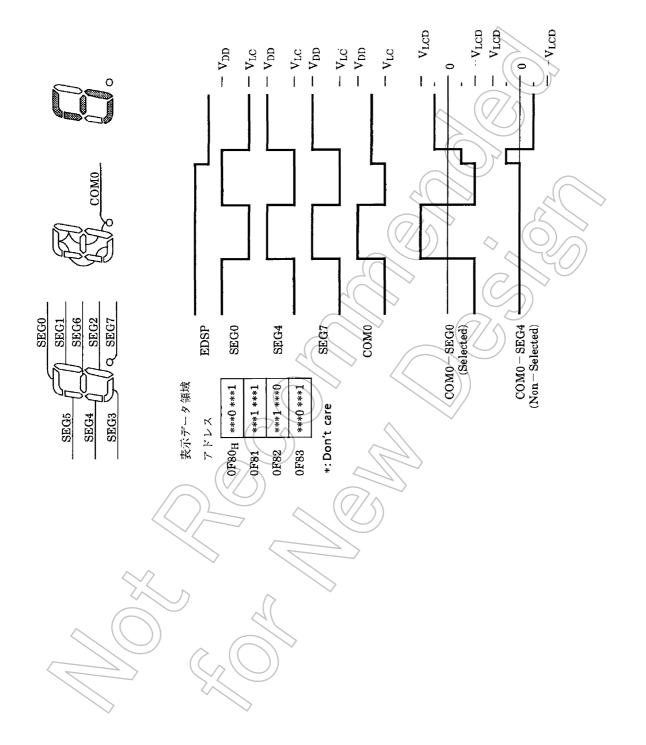

| 内部ウ                           | ィンド                | ウゲー                      | トパ              | ルス設定                                                                                                        | とレジス                                          | スタ                                                 | (初期値                                                                                                                                                 | : ****                     | ****)                                     |                                                    |                                      |                                                                           | $\mathcal{L}$            | >                                                                              |                                 |             |                    |