# **TOSHIBA**

TOSHIBA Original CMOS 8-Bit Microcontroller

TLCS-870 Series

TMP87PS68DFG

Semiconductor Company

# **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Pb free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a temporary substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

1. Part number

Example: TMPxxxxxxFG

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C

LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page.

5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

Ι

#### 1. Part number

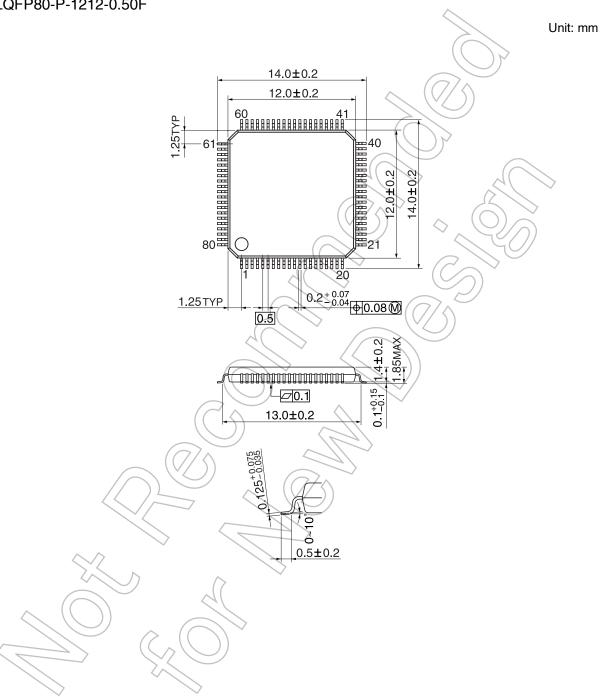

## 2. Package code and dimensions

| Previous Part Number (in Body Text) | Previous Package Code<br>(in Body Text) | New Part Number | New Package Code    | ОТР |

|-------------------------------------|-----------------------------------------|-----------------|---------------------|-----|

| TMP87PS68DF                         | LQFP80-P-1212-0.50A                     | TMP87PS68DFG    | LQFP80-P-1212-0.50F | _   |

<sup>\*:</sup> For the dimensions of the new package, see the attached Package Dimensions diagram.

#### 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

Lead solderability of Pb-free devices (with the G suffix)

| Test          | Test Conditions                                                                                                                                                                                                                                                      | Remark                                                                |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Solderability | (1) Use of Lead (Pb) -solder bath temperature = 230°C -dipping time = 5 seconds -the number of times = once -use of R-type flux (2) Use of Lead (Pb)-Free -solder bath temperature = 245°C -dipping time = 5 seconds -the number of times = once -use of R-type flux | Leads with over 95% solder coverage till lead forming are acceptable. |

#### 4. RESTRICTIONS ON PRODUCT USE

The following replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text.

#### RESTRICTIONS ON PRODUCT USE

20070701-EN

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations that

regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring

as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

#### 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

(Annex)

# Package Dimensions

LQFP80-P-1212-0.50F

III 2008-03-06

CMOS 8-Bit Microcontroller

## TMP87PS68DF

The 87PS68 is a One-Time PROM microcontroller with low-power 480 K bits electrically programmable read only memory for the 87CS68 system evaluation. The 87PS68 is pin compatible with the 87CS68. The operations possible with the 87CS68 can be performed by writing programs to PROM. The 87PS68 can write and verify in the same way as the TC571000D using an adaptor socket BM11105 and an EPROM programmer.

| Part No.   | OTP                                | RAM         | Package             | OTP Adapter |

|------------|------------------------------------|-------------|---------------------|-------------|

| TMP87PS68F | 61184 bytes<br>(60 Kbyte-256 byte) | 2 K × 8-bit | P-LQFP80-1212-0.50A | BM11105     |

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a quide for the applications of our products. No responsibility

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

3-68-109 1999-08-23

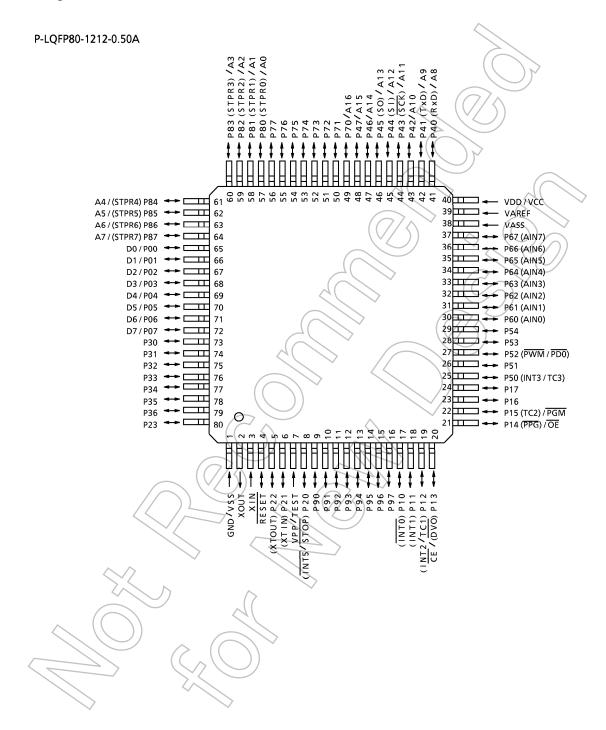

## Pin Assignments (Top View)

## **Pin Function**

The 87PS68 has two modes: MCU and PROM.

(1) MCU mode

In this mode, the 87PS68 is pin compatible with the 87CS68 (fix the TEST pin at low level.)

(2) PROM mode

| Pin Name (PROM mode)                           | Input/Output                           | Functions                                                                                     | Pin Name (MCU mode) |  |  |  |

|------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|---------------------|--|--|--|

| A16                                            |                                        |                                                                                               | P70                 |  |  |  |

| A15 to A8                                      | Input                                  | PROM address inputs                                                                           | P47 to P40          |  |  |  |

| A7 to A0                                       |                                        |                                                                                               | P87 to P80          |  |  |  |

| D7 to D0                                       | I/O                                    | PROM data input/outputs                                                                       | P07 to P00          |  |  |  |

| CE                                             |                                        | Chip enable signal input (active low)                                                         | P13                 |  |  |  |

| ŌĒ                                             | Input                                  | Output enable signal input (active low)                                                       | P14                 |  |  |  |

| PGM                                            |                                        | Program mode signal input                                                                     | P15                 |  |  |  |

| VPP                                            |                                        | + 12.75 V / 5 V (Program supply voltage)                                                      | TEST                |  |  |  |

| vcc                                            | Power supply                           | +6.25V/5V                                                                                     | VDD                 |  |  |  |

| GND                                            |                                        | 0(V                                                                                           | VSS                 |  |  |  |

| P36 to P30  P54 to P50  P67 to P60  P77 to P72 |                                        | Pull-up with resistance for input prod                                                        | essing.             |  |  |  |

| P11 P21 P71 P17, P16, P12, P10 P22, P20        | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | PROM mode setting pin. Be fixed at high level.  PROM mode setting pin. Be fixed at low level. |                     |  |  |  |

| RESET XIN                                      | Input                                  | Connect an 8MHz oscillator to stabilize the internal sta                                      | ate                 |  |  |  |

| XOUT                                           | Output                                 | Some of the internal su                                                                       |                     |  |  |  |

| VAREF                                          | Power supply                           | 0 V (GND)                                                                                     |                     |  |  |  |

| VASS                                           |                                        |                                                                                               |                     |  |  |  |

## **Operational Description**

The following explains the 87PS68 hardware configuration and operation. The configuration and functions of the 87PS68 are the same as 87CS68, except in that a one-time PROM is used instead of an on-chip mask ROM.

The 87PS68 is placed in the *single-clock* mode during reset. To use the dual-clock mode, the low-frequency oscillator should be turned on by executing [SET (SYSCR2). XTEN] instruction at the beginning of the program.

#### 1. Operating Mode

The 87PS68 has two modes: MCU and PROM.

#### 1.1 MCU Mode

The MCU mode is activated by fixing the TEST / VPP pin at low level.

In the MCU mode, operation is the same as with the 87CS68 (the TEST / VPP pin cannot be used open because it has no built-in pull-down resistance).

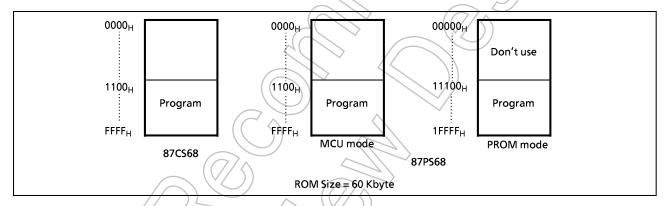

#### 1.1.1 Program Memory

The 87PS68 has a 60K × 8-bit (addresses 1100<sub>H</sub>-FFFF<sub>H</sub> in the MCU mode, addresses 11100<sub>H</sub>-1FFFF<sub>H</sub> in the PROM mode) of program memory (OTP).

When the 87PS68 is used as a system evaluation of the 87CS68, the data is written to the program storage area shown in Figure 1-1.

Figure 1.1 Program Memory Area

Note: Either write the data FF<sub>H</sub> to the unused area or set the PROM programmer to access only the program storage area.

3-68-112

1999-08-23

# 1.1.2 Data Memory

The 87PS68 has an on-chip 2K  $\times$  8-bit data memory (static RAM).

# 1.1.3 Input/Output Circuitry

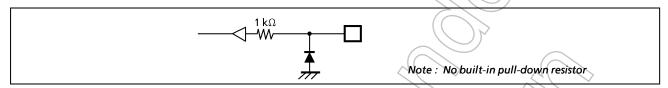

## (1) Control pins

The control pins of the 87PS68 are the same as 87CS68 except that the TEST pin has no built-in pull-down resistance.

Figure 1-2. TEST pin

# (2) I/O ports

The I/O circuits of 87PS68 I/O ports the are the same I/O circuitries of the 87CS68.

1999-08-23

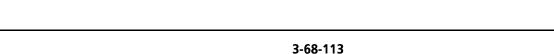

#### 1.2 PROM Mode

The PROM mode is activated by setting the TEST, RESET pin and the ports P17 to P10, P22 to P20 and P71, as shown in Figure 1-3. The PROM mode is used to write and verify programs with a general-purpose PROM programmer.

Note: The high-speed programming mode can be used for program operation.

The 87PS68 is not supported an electric signature mode, so the ROM type must be set to TC571000D. (The settings may differ depending on the type of PROM programmer is use. Refer to the PROM programmer operation manual.

Figure 1-3. Setting for PROM Mode

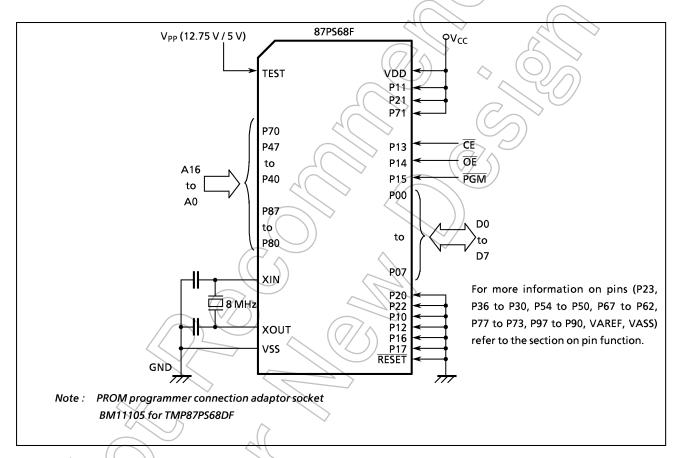

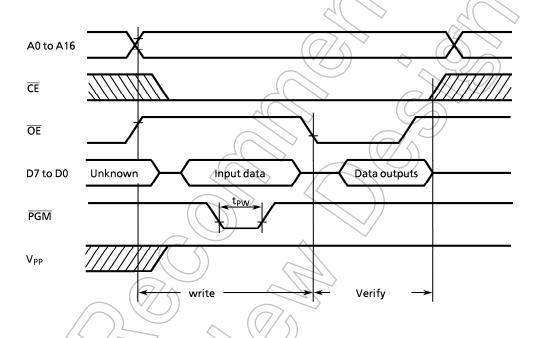

## 1.2.1 Programming Flowchart (High-speed Programming Mode)

The high-speed programming mode is achieved by applying the program voltage (+ 12.75 V) to the VPP pin when Vcc = 6.25 V. After the address and input data are stable, the data is programmed by applying a single 0.1ms program pulse to the  $\overline{PGM}$  input. The programmed data is verified. If incorrect, another 0.1 ms program pulse is applied. This process should be repeated (up to 25 times) until the program operates correctly. After that, change the address and input data, and program as before. When programming has been completed, the data in all addresses should be verified with Vcc = Vpp = 5 V.

Figure 1-4. Flow Chart of High-speed Programming

### 1.2.2 Writing Method for General-purpose PROM Program

(1) Adapters

BM11105: TMP87PS68DF

(2) Adapter setting Switch (SW1) is set to side N.

(3) PROM programmer specifying

i) PROM type is specified to TC571000D.

Writing voltage: 12.75 V (high-speed program mode)

ii) Data transfer (copy) (note 1)

In the TMP87PS68, EPROM is within the addresses 11100H to 1FFFFH. Data is required to be transferred (copied) to the addresses where it is possible to write. The program area in MCU mode and PROM mode is referred to "Program memory area" in Figure 1-1.

Ex. In the block transfer (copy) mode, executed as below.

ROM capacity of 60KB: transferred addresses 01100H to 0FFFFH to addresses 11100 to 1FFFFH

iii) Writing address is specified. (note 1)

Start address: 11100<sub>H</sub> End address: 1FFFF<sub>H</sub>

(4) Writing

Writing/Verifying is required to be executed in accordance with PROM programmer operating procedure.

- Note 1: The specifying method is referred to the PROM programmer description. Either write the data FF<sub>H</sub> to the unused area or set the PROM programmer to access only the program storage area.

- Note 2: When MCU is set to an adapter or the adapter is set to PROM programmer, a position of pin 1 must be adjusted. If the setting is reversed, MCU, the adapter and PROM program is damaged.

- Note 3: The TMP87PS68 does not support the electric signature mode (hereinafter referred to as "signature"). If the signature is used in PROM program, a device is damaged due to applying  $12 \text{ V} \pm 0.5 \text{ V}$  to the address pin 9 (A9). The signature must not be used.

# Input/Output Circuitry

## (1) Control pins

The input / output circuitries of the 87PS68 control pins are shown below.

| Control Pin               | I/O             | Input / Output Circuitry and Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Remarks                                                                                                                                           |

|---------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

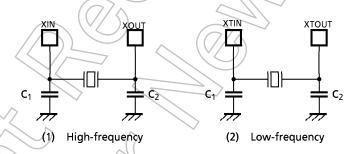

| XIN<br>XOUT               | Input<br>Output | Osc. enable VDD o VDD NR <sub>f</sub> R <sub>O</sub> XIN XOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Resonator connecting pins (high-frequency) $R_f = 1.2 \ M\Omega \ (typ.)$ $R_o = 1.5 \ k\Omega \ (typ.)$                                          |

| XTIN (P21)<br>XTOUT (P22) | Input<br>Output | NM1 NM2 Sc. enable VDD o | Resonator connecting pins (low-frequency) $R_f = 6 \ M\Omega \ (typ.)$ $R_o = 220 \ k\Omega \ (typ.)$ In only dual-clock mode                     |

| RESET                     | VO              | Address-trap-reset Watchdog timer reset System-clock-reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sink open drain output   Hysteresis input   Pull-up resistor $R_{IN} = 220 \text{ k}\Omega \text{ (typ.)}$ $R = 1 \text{ k}\Omega \text{ (typ.)}$ |

| STOP/INT5<br>(P20)        | Input           | P20 STOP/INT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Hysteresis input $R=1~k\Omega~(typ.)$                                                                                                             |

| TEST                      | Input           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R = 1 kΩ (typ.)                                                                                                                                   |

$Note 1: \quad \textit{The TEST pin of the 87PS68 does not have a pull-down resistor. Be sure to fix the \textit{TEST pin}}$

to low in MCU mode.

Note2: The 87PS68 is placed in the single-clock mode during reset. (NM1)

# (2) Input/output ports

The input/output circuitries of the 87PS68 input/output ports are shown below.

|          |     | ζ                                                            |                                                                                                               |

|----------|-----|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Port     | 1/0 | Input/Output Circuitry                                       | Remarks                                                                                                       |

| P0<br>P6 | I/O | disable disable                                              | Tri-state I/O $R = 1k\Omega \text{ (typ.)}$                                                                   |

| P1       | 1/0 | initial "Hi-Z"                                               | Tri-state I/O Hysteresis input $R = 1 k\Omega \text{ (typ.)}$                                                 |

| P2       | I/O | P20, P23  initial "Hi-Z"  oVDD  ritial "Hi-Z"  ritial "Hi-Z" | Sink open drain output Hysteresis input $R=1k\Omega \ \mbox{(typ.)}$                                          |

| P3       | I/O | initial "Hi-Z"                                               | Sink open drain output $\label{eq:R} \mbox{High current output}$ $\mbox{R = 1k}\Omega \mbox{ (typ.)}$         |

| P4<br>P5 | 1/0 | initial "Hi-Z" p-ch Control                                  | Sink open drain or Tri-state I/O (Programable port option) Hysterisis input $R = 1k\Omega$ (typ.)             |

| P7<br>P9 |     | initial "Hi-Z" p-ch Control                                  | Sink open drain or Tri-state I/O (Programable port option) $R = 1k\Omega \text{ (typ.)}$                      |

| P8       | I/O | initial "Hi-Z"  P.U Control  RIN  RIN  R                     | Tri-state I/O Programable Pull-up resistor $R_{IN} = 70k\Omega$ (typ.) $R = 1k\Omega$ (typ.) Hysterisis input |

#### **Electrical Characteristics**

(1) 87PS68

Absolute Maximum Ratings  $(V_{SS} = 0 V)$

| Parameter                       | Symbol              | Conditions                               | Ratings                        | Unit |

|---------------------------------|---------------------|------------------------------------------|--------------------------------|------|

| Supply Voltage                  | $V_{DD}$            |                                          | - 0.3 to 6.5                   | V    |

| Input Voltage                   | V <sub>IN</sub>     | \ ((//\langle                            | - 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output Voltage                  | V <sub>OUT</sub>    |                                          | – 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output Compant (Pan Inia)       | I <sub>OUT1</sub>   | Ports P0, P1, P2, P4, P5, P6, P7, P8, P9 | 3.2                            | ^    |

| Output Current (Per 1pin)       | I <sub>OUT2</sub>   | Port P3                                  | 30                             | mA   |

| Output Compant (Tatal)          | Σ l <sub>OUT1</sub> | Ports P0, P1, P2, P4, P5, P6, P7, P8, P9 | 160                            | 4    |

| Output Current (Total)          | Σ I <sub>OUT2</sub> | Port P3                                  | 120                            | mA   |

| Power Dissipation [Topr = 70°C] | PD                  |                                          | 350                            | mW   |

| Soldering Temperature (time)    | Tsld                | (V) \ \ \ .                              | 260 (10 s)                     | °C   |

| Storage Temperature             | Tstg                |                                          | -55 to 125                     | °C   |

| Operating Temperature           | Topr                |                                          | – 30 to 70                     | °C   |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

**Recommended Operating Conditions**

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter          | Symbol                  | Pins                    | Co                             | onditions                                                |                        | Min                    |                        | Max                  | Unit   |  |

|--------------------|-------------------------|-------------------------|--------------------------------|----------------------------------------------------------|------------------------|------------------------|------------------------|----------------------|--------|--|

|                    |                         | (( 5)                   | NORMAL1, 2 mode                |                                                          |                        |                        |                        |                      |        |  |

|                    |                         |                         | fc = 8 MHz                     | DLE1, 2 mode                                             | 4.5                    |                        |                        |                      |        |  |

|                    |                         | (7/4)                   | fc ≤ 4.2 MHz                   | NORMAL1, 2 mode                                          |                        |                        |                        |                      |        |  |

| Supply Voltage     | V <sub>D</sub> D        |                         | TC ≤ 4.2 WHZ                   | IDLE1, 2 mode                                            |                        | 2.7                    |                        | 5.5                  | V      |  |

|                    |                         |                         | fs =                           | SLOW mode                                                |                        | 2.7                    |                        |                      |        |  |

|                    |                         |                         | 32.768 kHz                     | SLEEP mode                                               | 1                      |                        |                        |                      |        |  |

|                    |                         |                         |                                | STOP mode                                                | 2.0                    |                        |                        |                      |        |  |

| <b>\</b>           | V <sub>IH1</sub> Except |                         | V >4.5V                        |                                                          | V >4 EV                |                        | V <sub>DD</sub> × 0.70 |                      |        |  |

| Input High Voltage | V <sub>IH2</sub>        | Hysteresis input        | V                              | $V_{DD} \ge 4.5 \text{ V}$ $V_{DD} \times 0.75$ $V_{DD}$ |                        | V <sub>DD</sub> × 0.75 |                        | $V_{DD}$             | V      |  |

|                    | V <sub>IH3</sub>        | $\lambda$ (             | V                              | <sub>DD</sub> <4.5 V                                     | V <sub>DD</sub> × 0.90 |                        | 90                     |                      |        |  |

|                    | V <sub>IL1</sub>        | Except hysteresis input | .,                             | > 4 5 1/                                                 | 0                      |                        | $V_{DD} \times 0.3$    |                      |        |  |

| Input Low Voltage  | V <sub>IL2</sub>        | Hysteresis input        | V                              | <sub>DD</sub> ≧ 4.5 V                                    |                        |                        |                        | $V_{DD} \times 0.25$ | v      |  |

|                    | V <sub>IL3</sub>        |                         | V <sub>DD</sub> <4.5 V         |                                                          | V <sub>DD</sub> <4.5 V |                        |                        | $V_{DD} \times 0.10$ |        |  |

|                    |                         |                         | \/                             | V <sub>DD</sub> = 4.5 to 5.5 V                           |                        | fc                     | 0.4                    | 8.0                  |        |  |

|                    | fc                      | XIN, XOUT               | VDD -                          | = 4.3 tO 3.3 V                                           | gear                   | fc/2                   | 0.8                    | 6.0                  | MHz    |  |

| Clock Frequency    | IC.                     | XIIV, XOOT              | V <sub>DD</sub> = 2.7 to 5.5 V |                                                          | ratio                  | fc/4                   | 1.6                    | 4.19                 | IVITIZ |  |

|                    |                         |                         |                                |                                                          |                        | fc/8                   | 3.2                    | 4.19                 |        |  |

|                    | fs                      | XTIN, XTOUT             |                                |                                                          |                        | 30.0                   |                        | 34.0                 | kHz    |  |

Note 1: The recommended operating Conditions for a device are operating Conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating Conditions other than the recommended operating Conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating Conditions for the device are always adhered to.

Note2: Clock frequency fc: The supply voltage range of the conditions shows the value in NORMAL1, 2 modes and IDLE 1,2 modes.

#### D.C. Characteristics

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -30 \text{ to } 70 \,^{\circ}\text{C})$

| Parameter                             | Symbol           | Pins                                    | Conditions                                                           | Min              | Тур.  | Max   | Unit |

|---------------------------------------|------------------|-----------------------------------------|----------------------------------------------------------------------|------------------|-------|-------|------|

| Hysteresis Voltage                    | V <sub>HS</sub>  | Hysteresis input                        |                                                                      | ) \              | 0.9   | _     | V    |

|                                       | I <sub>IN1</sub> | TEST                                    |                                                                      |                  |       |       |      |

| Input Current                         | I <sub>IN2</sub> | Sink open drain port and tri-state port | $V_{DD} = 5.5 V$<br>$V_{IN} = 5.5 V / 0 V$                           | -                | _     | ± 2   | μA   |

|                                       | I <sub>IN3</sub> | RESET, STOP                             | VIII = 3.3 V. V.                                                     |                  |       |       |      |

| Innut Posistance                      | R <sub>IN2</sub> | RESET                                   |                                                                      | 100              | 220   | 450   | kΩ   |

| Input Resistance                      | R <sub>IN</sub>  | P8 pull-up resistor                     |                                                                      | 30               | 70    | 150   | K77  |

| Output Leakage<br>Current             | I <sub>LO</sub>  | Sink open drain port and tri-state port | $V_{DD} = 5.5 \text{ V}, V_{OUT} = 5.5 \text{ V}$                    | ~4(              | //    | , 2   | μΑ   |

| Output High Voltage                   | V <sub>OH2</sub> | Tri-state port                          | $V_{DD} = 4.5 \text{ V}, I_{OH} = -0.7 \text{ mA}$                   | 4.1              | />    | -     | >    |

| Output Low Voltage                    | $V_{OL}$         | Except XOUT and P3                      | $V_{DD} = 4.5 \text{ V, } I_{OL} = 1.6 \text{ mA}$                   | ) <del>)</del> / | 6     | 0.4   | V    |

| Output Low Current                    | I <sub>OL3</sub> | Port P3                                 | $V_{DD} = 4.5 \text{ V}, V_{OL} = 1.0 \text{ V}$                     | 4                | /20   | _     | mA   |

| Supply Current in<br>NORMAL 1, 2 mode |                  |                                         | $V_{DD} = 5.5 V$<br>$V_{IN} = 5.3 V / 0.2 V$                         | \\ \             | 9     | 12    |      |

| Supply Currnt in IDLE<br>1, 2 mode    |                  |                                         | fc = 8 MHz<br>fs = 32.768 kHz                                        | _                | 4.5   | 6.5   |      |

| Supply Currnt in<br>NORMAL 1, 2 mode  | l <sub>DD</sub>  |                                         | $V_{DD} = 3.0 \text{ V}$<br>$V_{IN} = 2.8 \text{ V} / 0.2 \text{ V}$ | -                | T.B.D | T.B.D | mA   |

| Supply Currnt in IDLE<br>1, 2 mode    |                  |                                         | fc = 4.2 MHz<br>fs = 32.768 kHz                                      | _                | T.B.D | T.B.D |      |

| Supply Current in SLOW mode           |                  |                                         | V <sub>DD</sub> = 3.0 V                                              | _                | 30    | 60    | μΑ   |

| Supply Current in SLEEP mode          | I <sub>DD</sub>  |                                         | V <sub>IN</sub> = 2.8 V / 0.2 V<br>fs = 32.768 kHz                   | _                | 15    | 30    | μΑ   |

| Supply Current in STOP mode           |                  |                                         | V <sub>DD</sub> = 5.5 V<br>V <sub>IN</sub> = 5.3 V / 0.2 V           | -                | 0.5   | 10    | μΑ   |

Note 1: Typical values show those at Topr =  $25^{\circ}$ C,  $V_{DD}$  = 5V. Note 2: Input current: The current through pull-up or pull-down resistor is not included.

## A / D Conversion Characteristics

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, Topr = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter                | Symbol                       | Conditions                                                                | Min              | Тур. | Max               | Unit |  |

|--------------------------|------------------------------|---------------------------------------------------------------------------|------------------|------|-------------------|------|--|

| A                        | V <sub>AREF</sub>            | V > 2.5V                                                                  | 2.7              | _    | $V_{DD}$          | .,   |  |

| Analog Reference Voltage | $V_{ASS} = V_{ASS} \ge 2.5V$ |                                                                           | V <sub>SS</sub>  | _    | 1.5               | - V  |  |

| Analog Input Voltage     | VAIN                         | $V_{DD} = V_{AREF} = 5.0 \text{ V}$<br>$V_{SS} = V_{ASS} = 0.0 \text{ V}$ | V <sub>ASS</sub> | _    | V <sub>AREF</sub> | V    |  |

| Analog Supply Current    | I <sub>REF</sub>             | $V_{AREF} = 5.5 \text{ V}, \ V_{ASS} = 0.0 \text{ V}$                     | _                | 0.5  | 1.0               | ٧    |  |

| Nonlinearity Error       |                              | V 27+2 F F V                                                              | _                | _    | ± 1               |      |  |

| Zero Point Error         |                              | $V_{DD} = 2.7 \text{ to } 5.5 \text{ V}$<br>$V_{SS} = 0.0 \text{ V}$      | _                | _    | ± 1               | mA   |  |

| Full Scale Error         |                              | V <sub>AREF</sub> = 2.700 V, 5.000 V                                      | _                | _    | ± 1               | LCD  |  |

| Total Error              |                              | V <sub>ASS</sub> = 0.000 V                                                |                  | _    | ± 2               | LSB  |  |

Note: Total Error = total number of each type error excluding guantization error

#### A.C. Characteristics

( $V_{SS} = 0 \text{ V}, \ V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \ \text{Topr} = -30 \text{ to } 70 \,^{\circ}\text{C}$ )

| Parameter                    | Symbol           | Conditions                                | Min       | Тур. | Max          | Unit |

|------------------------------|------------------|-------------------------------------------|-----------|------|--------------|------|

|                              |                  | In NORMAL1, 2 mode (gear ratio)           | 0.5 (1/1) | ( )  | 40 (4 (0)    |      |

| Machine Cycle Time           | ١.               | In IDLE1, 2 mode (gear ratio)             |           |      | 10 (1/8)     |      |

|                              | t <sub>cy</sub>  | In SLOW mode                              |           | _    | 122.2        | μS   |

|                              |                  | In SLEEP mode                             | 117.6     |      | 133.3        |      |

| High Level Clock Pulse Width | t <sub>WCH</sub> | For external clock operation (XIN input)  | 7         |      |              |      |

| Low Level Clock Pulse Width  | t <sub>WCL</sub> | fc = 8 MHz                                | 50        | _    | _            | ns   |

| High Level Clock Pulse Width | t <sub>WSH</sub> | For external clock operation (XTIN input) | 14.7      | <(C  |              | _    |

| Low Level Clock Pulse Width  | t <sub>WSL</sub> | fs = 32.768 kHz                           | 14.7      |      | $\checkmark$ | μS   |

## **Recommended Oscillating Condition**

| Parameter      | Oscillator         | Frequency Recommended Oscillator |                  | Recommended Conditio  |                |  |

|----------------|--------------------|----------------------------------|------------------|-----------------------|----------------|--|

| rarameter      | Oscillator         |                                  |                  | <b>C</b> <sub>1</sub> | C <sub>2</sub> |  |

| High-frequency | Ceramic Resonator  | 8 MHz                            | KYOCERA KBR8.0M  |                       |                |  |

|                |                    |                                  | KYOCERA KBR4.0MS | 30 pF                 | 30 pF          |  |

|                |                    | 4 MHz                            | MURATA CSA4:00MG |                       |                |  |

| Low-frequency  | Crystal Oscillator | 32.768 kHz                       | NDK MX-38T       | 15 pF                 | 15 pF          |  |

Note: When it is used in high electrical field, an electrical shield of the package is recommended to retain normal operations

Note: To obtain an accurate oscillating frequency the condenser capacity must be adjusted on the sct.

# D.C./A.C. Characteristics (PROM mode)

$(V_{SS} = 0 V)$

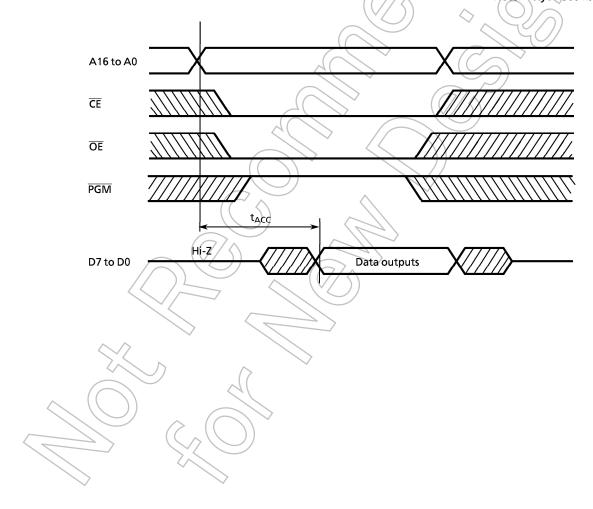

# (1) Read Operation

| Parameter                    | Symbol           | Conditions                        | Min   | Тур.                         | Max             | Unit |

|------------------------------|------------------|-----------------------------------|-------|------------------------------|-----------------|------|

| Input High Voltage           | V <sub>IH4</sub> |                                   | 2.2   | $\left( \frac{7}{5} \right)$ | V <sub>CC</sub> | ٧    |

| Input Low Voltage            | V <sub>IL4</sub> |                                   | 0     |                              | 0.8             | ٧    |

| Power Supply Voltage         | V <sub>CC</sub>  |                                   | 4.75  | 5.0                          | 5.25            | V    |

| Program Power Supply Voltage | $V_{PP}$         |                                   | 4.73  | 3.0                          | 3.23            | V    |

| Address Access Time          | t <sub>ACC</sub> | $V_{CC} = 5.0 \pm 0.25 \text{ V}$ | 4/- 2 | 1.5tcyc + 300                |                 | ns   |

Note: tcyc = 500 ns at 8 MHz

## (2) High-Speed Programming Operation (Topr = $25 \pm 5$ °C)

| Parameter                    | Symbol           | Conditions              | Min   | Тур.  | Max             | Unit |

|------------------------------|------------------|-------------------------|-------|-------|-----------------|------|

| Input High Voltage           | V <sub>IH4</sub> |                         | 2.2   |       | V <sub>CC</sub> | >    |

| Input Low Voltage            | V <sub>IL4</sub> |                         | 0     |       | 0.8             | >    |

| Power Supply Voltage         | V <sub>CC</sub>  |                         | 6.0   | 6.25  | 6.5             | >    |

| Program Power Supply Voltage | V <sub>PP</sub>  |                         | 12.5  | 12.75 | 13.0            | >    |

| Initial Program Pulse Width  | t <sub>PW</sub>  | V <sub>CC</sub> = 6.0 V | 0.095 | 0.1   | 0.105           | ms   |

Note1: When  $V_{cc}$  power supply is turned on or after,  $V_{pp}$  must be increased. When  $V_{cc}$  power supply is turned off or before,  $V_{pp}$  must be increased.

Note2: The device must not be set to the EPROM programmer or picked op from it under applying the program voltage (12.5 V  $\pm$  0.5 V  $\pm$  V) to the  $V_{pp}$  pin as the device is damaged.

Note3: Be sure to execute the recommended programing mode with the recommended programing adaptor. If a mode or an adaptor except the above, the misoperation sometimes occurs.

3-68-124 1999-08-23